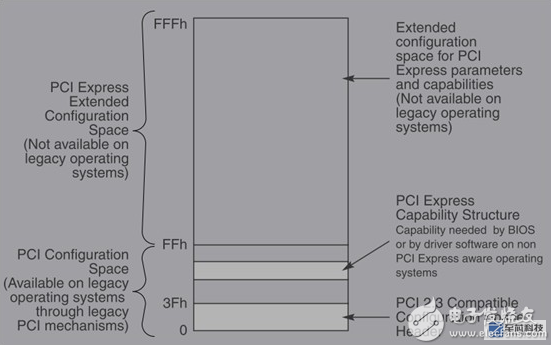

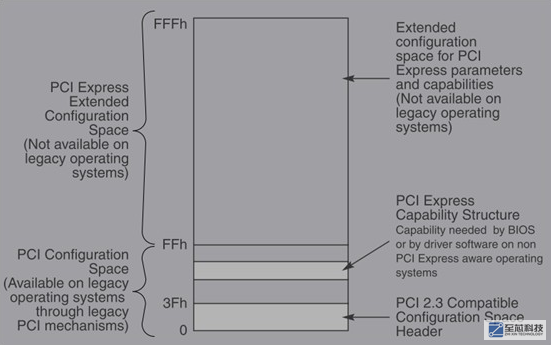

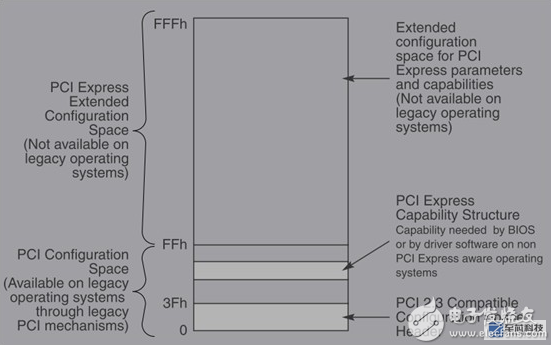

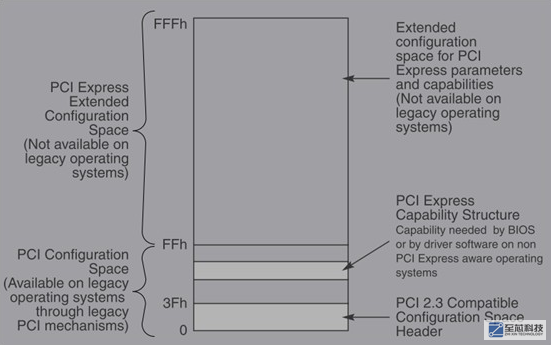

大家好,又到了每日學(xué)習(xí)的時間了,今天我們來聊一聊PCIe的軟件配置方式。 關(guān)于PCIe的軟件配置和初始化 PCIe設(shè)計出來考慮了和pci兼容問題。所以PCIe的軟件配置方式可以沿用PCI的配置方式

2019-07-29 09:26:32 7337

7337

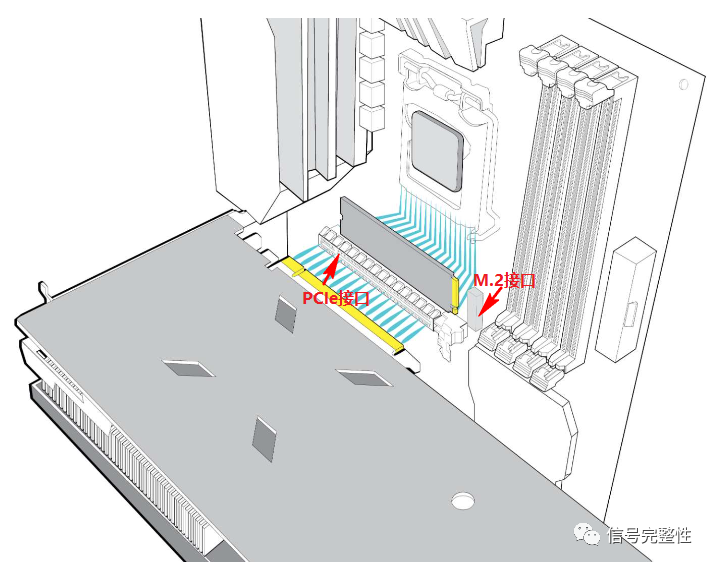

本文我們將向大家介紹PCIe引腳定義以及PCIe協(xié)議層。

2023-09-26 11:39:14 5659

5659

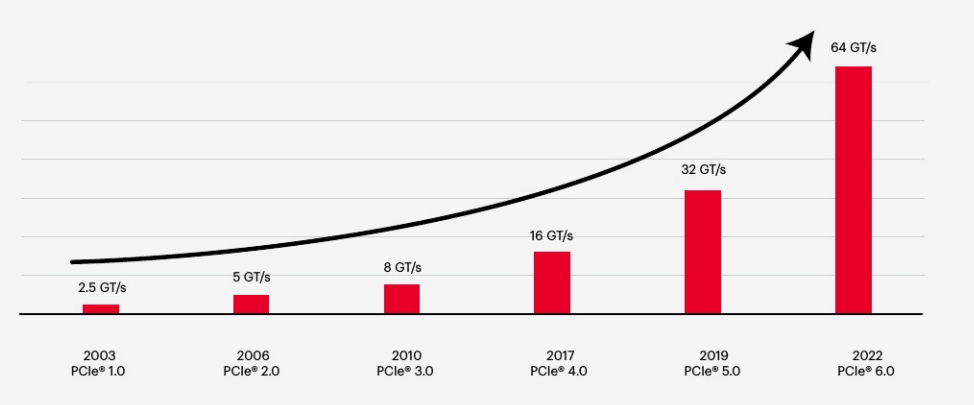

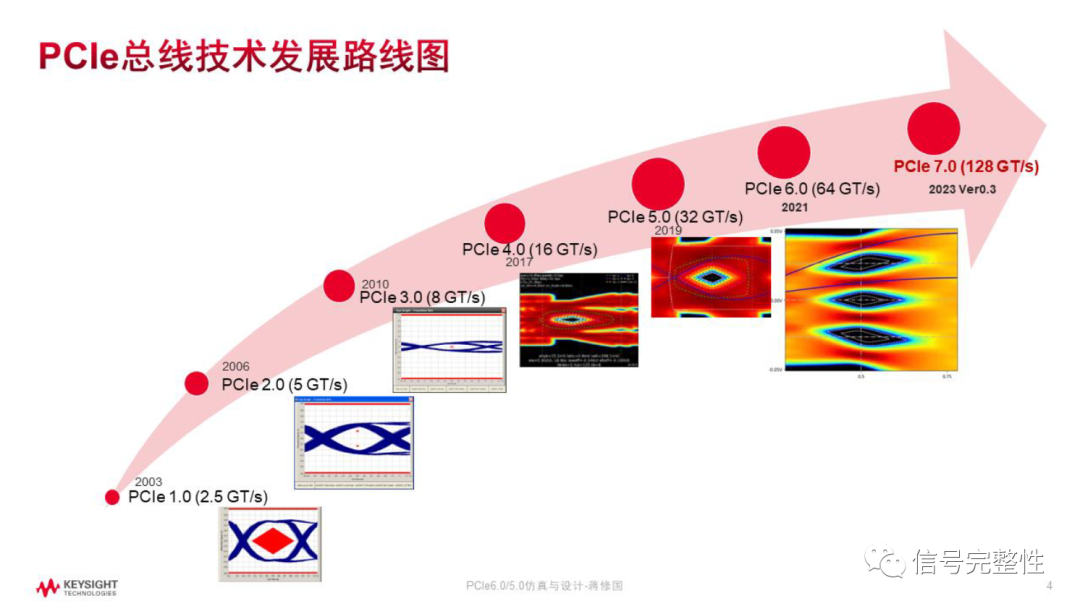

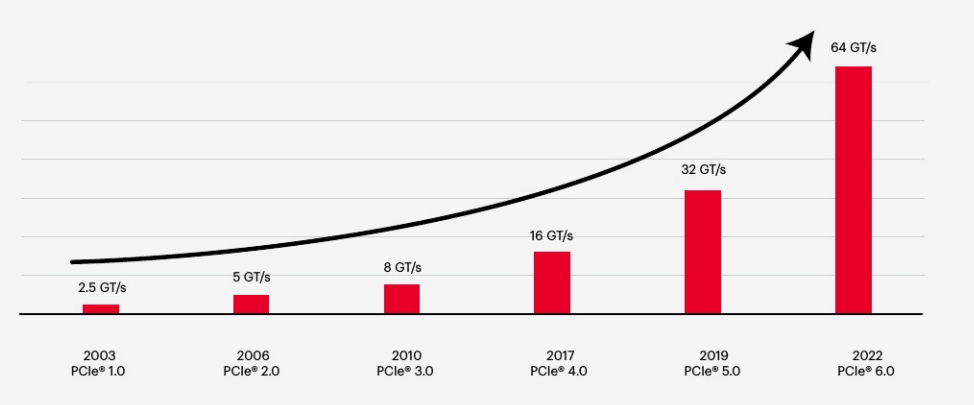

自2003年推出以來,PCIe發(fā)展至今已經(jīng)從最初的1.0升級到了6.0,本文則為大家簡單介紹一下PCIe標(biāo)準(zhǔn)的演進(jìn)歷史以及各代PCIe標(biāo)準(zhǔn)之間的主要差異。

2023-12-14 16:38:08 1535

1535

使用自己做的6678的板卡. PCIe參考時鐘100MHz. 運行例程中的PCIe測試.pcie_phy_loopback. 當(dāng)運行完 gpPCIE_app_regs->CMD_STATUS

2019-01-03 11:36:50

6678的pcie和fpga的pcie? TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

?

2018-06-21 15:49:12

有沒有研究PCIE的,求指導(dǎo)。{:4_100:}

2013-03-23 23:46:18

小弟學(xué)習(xí)K1_STK(從官網(wǎng)下的最新的例程keystone軟件開發(fā)包)里面的PCIE(例程),這個是例程里面RC端和EP端用的是MSI中斷。PCIE

2018-06-21 03:49:49

1.PCIE的發(fā)送和接收數(shù)據(jù)本工程的目的是在XC7K325tffg的平臺上實現(xiàn)pcie的數(shù)據(jù)發(fā)送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的結(jié)構(gòu):架構(gòu)各個模塊的作用PCIE部分

2019-12-26 10:46:09

開發(fā)環(huán)境:windows開發(fā)平臺:QT5.11.31.PCIE上位機(jī)測試過程FPGA將數(shù)據(jù)傳到芯片中,通過pcie再將芯片算完的數(shù)傳給上位機(jī)。目標(biāo):1.實現(xiàn)上位機(jī)的速度測試,經(jīng)測試pcie的傳輸速度

2019-12-26 10:27:19

開發(fā)環(huán)境:windows開發(fā)平臺:QT5.11.31、PCIE上位機(jī)測試過程FPGA將數(shù)據(jù)傳到芯片中,通過pcie再將芯片算完的數(shù)傳給上位機(jī)。目標(biāo):1.實現(xiàn)上位機(jī)的速度測試,經(jīng)測試pcie的傳輸速度

2022-01-13 16:44:54

8-CH RELAY & 8-CH IDI PCIE CARD

2024-03-14 20:33:38

M.2 NVME/M.2 SATA SSD PCIE X4

2024-03-14 22:02:08

M.2 NVME 80MM SSD PCIE X4 ADAPT

2024-03-14 22:02:08

M.2 NVMe SSD PCIe 4.0 Adapt w/HS

2024-03-14 22:02:08

M.2 NVME 110MM SSD PCIE X4

2024-03-14 22:02:08

大家好! 有問題想請教大家:我現(xiàn)在在做一個PCIe接口的數(shù)采。下位機(jī)是FPGA,pcie接口模塊調(diào)用的altera的硬核,DMA傳輸,使用QSYS系統(tǒng);上位機(jī)是工控機(jī)。現(xiàn)在被一個問題困惑:工控機(jī)

2014-11-13 14:26:16

1

PCIE基本概念1.1

PCIE拓?fù)浼軜?gòu)圖1.2

PCIE Switch內(nèi)部結(jié)構(gòu)圖1.3

PCIE協(xié)議結(jié)構(gòu)圖2

PCIE枚舉原理2.1 Type0&Type1配置頭空間2.2 拓?fù)涫纠?/div>

2022-02-16 06:08:26

我想用C6657的PCIE接口擴(kuò)展一個WIFI.

C6657的PCIE需要一個LVDS的參考時鐘(PCIECLKP, PCIECLKN),? WIFI芯片的PCIE需要一個HCSL的參考時鐘

2018-06-21 18:45:06

最近做PCIE的傳輸,廢了好大勁生成了PCIE-DMA的工程文件,然后用windriver生成了基本的PCI板卡驅(qū)動,卻發(fā)現(xiàn)不會寫上位機(jī)控制驅(qū)動程序,論壇里有做過PCIE的大神吧,指導(dǎo)下我吧(怎么寫

2015-07-28 15:51:36

PCIe 5.0的接口設(shè)計有多難?如何使用成熟的IP來克服這個問題?32 GT/s PCIe 5.0具有哪些主要功能?

2021-06-17 11:37:04

本文檔旨在提供關(guān)于將PCIe接口集成到基于AMBA的片上系統(tǒng)(SoC)的指導(dǎo)。

假設(shè)PCIe接口通過基于AXI或ACE協(xié)議的互連連接到SoC的其余部分。

讀者應(yīng)熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

描述 這款經(jīng)驗證的參考設(shè)計是一款 PCIe Gen-3 高速前端卡設(shè)計,旨在擴(kuò)展 PCIe 子系統(tǒng)的 PCB 線跡距離。該電路板適合安裝在主板與 PCIe Gen3 插卡之間的 x16 通道寬度

2022-09-21 07:43:27

PCIe提供了一種可裁減高速串行I/O點到點的總線連接。PCIe的LAN是一個全雙工的通道,由一對接收差分對和一對發(fā)送差分對構(gòu)成。PCIe的帶寬可以通過增減LANE數(shù)來調(diào)整。PCIe規(guī)范定義了x1

2019-06-03 07:09:56

一、PCIe基本知識1、PCI-Express(peripheral component interconnect express):是一種高速串行計算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),它原來的名稱為“3GIO

2021-11-11 08:05:11

PCIe機(jī)械及電氣規(guī)范

2016-07-14 14:50:40

硬盤是大家都很熟悉的設(shè)備,一路走來,從HDD到SSD,從SATA到NVMe,作為NVMeSSD的前端接口,PCIe再次進(jìn)入我們的視野。作為x86體系關(guān)鍵的一環(huán),PCIe標(biāo)準(zhǔn)歷經(jīng)PCI,PCI-X

2021-05-25 09:22:48

PCIe設(shè)備的低功耗狀態(tài)要求系統(tǒng)驅(qū)動程序顯式地將設(shè)備置于低功耗狀態(tài),從而PCIe鏈路則可以依次變?yōu)榈凸逆溌窢顟B(tài)。PCIe規(guī)范允許PCIe鏈路在沒有系統(tǒng)驅(qū)動的情況下進(jìn)入低功耗狀態(tài)。這個特性就是所謂

2021-12-28 06:18:35

pcie虛擬化技術(shù)中,一端pcie的虛擬通道又睡指定,是通過軟件配置嗎

2019-11-11 10:34:47

Hi ?各位管理好

咨詢下,我使用STK 6657 中的 PCIE_test 例程進(jìn)行PCIE通信測試, 6657作為RC端口, pcie外接設(shè)備

在代碼中有

2018-06-21 18:49:04

`EC20 Mini PCIe是采用 PCI Express? Mini Card標(biāo)準(zhǔn)接口的LTE模塊;采用LTE 3GPP Rel.9技術(shù),支持最大下行速率100Mbps和最大上行速率50Mbps

2018-06-05 17:38:23

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

PCIE BOARD 6 PORT DB-9

2023-03-22 20:41:28

MODULE CONV PCIE-SMA

2023-03-22 20:00:22

查過mini pcie的信號引腳定義,有52個信號(大多引腳無用),X1 LANE 的情況,查看飛思卡爾或INTEL處理器的設(shè)計資料,關(guān)于這個應(yīng)用除了主要 的差分收、發(fā)和差分時鐘信號之外還需要額外

2017-11-29 11:50:51

DEV SYSTEM P4080 PCIE

2023-03-22 19:55:54

PI2PCIE2412-EVALUATIONBOARD1

2023-03-30 11:41:15

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:30

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:25

IC CLOCK GENERATOR PCIE 42TQFN

2023-04-06 15:33:36

PI3PCIE2415EVALBOARD

2023-03-30 11:41:37

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:33:53

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

DEVELOPMENTSYSTEMT4240PCIE

2023-03-22 19:56:26

ZYNQ7045的PCIE電路設(shè)計,板卡使用插針式連接器,引出了PCIE信號,未使用金手指。為了插入機(jī)箱設(shè)計了擴(kuò)展版,插座與插針對應(yīng),帶有PCIE金手指。目前遇到的問題是,當(dāng)板卡連接擴(kuò)展板使用金手指

2023-05-16 11:07:40

紫光的logos系列的PGL50H/PGL100H、logos-2全系列都集成gen2×4的PCIE硬核,且官方也提供了例程。

紫光的PCIE用起來還是挺方便的,生成IP的同時生成了對應(yīng)的PCIE

2023-11-17 14:35:30

剛接觸PCIe,想用PCIe口與PC通信,EP模式。把板子插到PC上之后,通過windriver能查看到TI設(shè)備,但是用PCItree不能看到,這樣正常嗎?我運行的程序

2018-08-07 08:28:19

我們可以將多個 PCIe 設(shè)備 (IC) 連接到一般的單個 PCIe 控制器(在我們的案例中更具體地說是 NXP LS20xxA 處理器)嗎?

例如,將四個不同的 PCIe x1 設(shè)備 (IC

2023-05-05 07:35:41

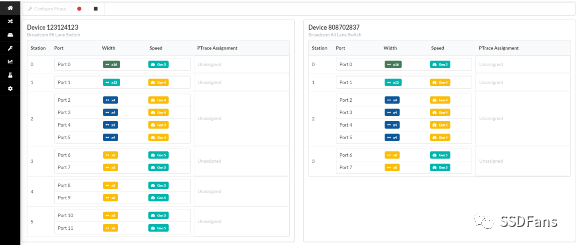

[tr=transparent]12槽PCIe擴(kuò)展塢PCIE3-1612擴(kuò)展系統(tǒng)是12槽位擴(kuò)展系統(tǒng),采用PCIe Gen3 Multi-Root Switch,系統(tǒng)支持12個PCIe X8 插槽

2018-07-09 09:24:53

[tr=transparent]12槽PCIe擴(kuò)展塢PCIE3-1612擴(kuò)展系統(tǒng)是12槽位擴(kuò)展系統(tǒng),采用PCIe Gen3 Multi-Root Switch,系統(tǒng)支持12個PCIe X8 插槽

2018-07-03 09:37:11

我試圖從xapp1052識別PCIe BMD示例中的主要數(shù)據(jù)端口,以便我可以在其中添加我的設(shè)計。我試圖為PCIe接收數(shù)據(jù)[63:0] trn_rd添加一些常量值。但是在我給出一個ReadData

2019-03-20 15:09:18

如何提高PCIe數(shù)據(jù)速率?

2021-05-20 06:17:09

我是一名PCIe新手,想了解以下問題:

1、如何測試PCIe?

2、如何讀寫PCIe(兩塊開發(fā)板通過PCIe線互連,分別配置為RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

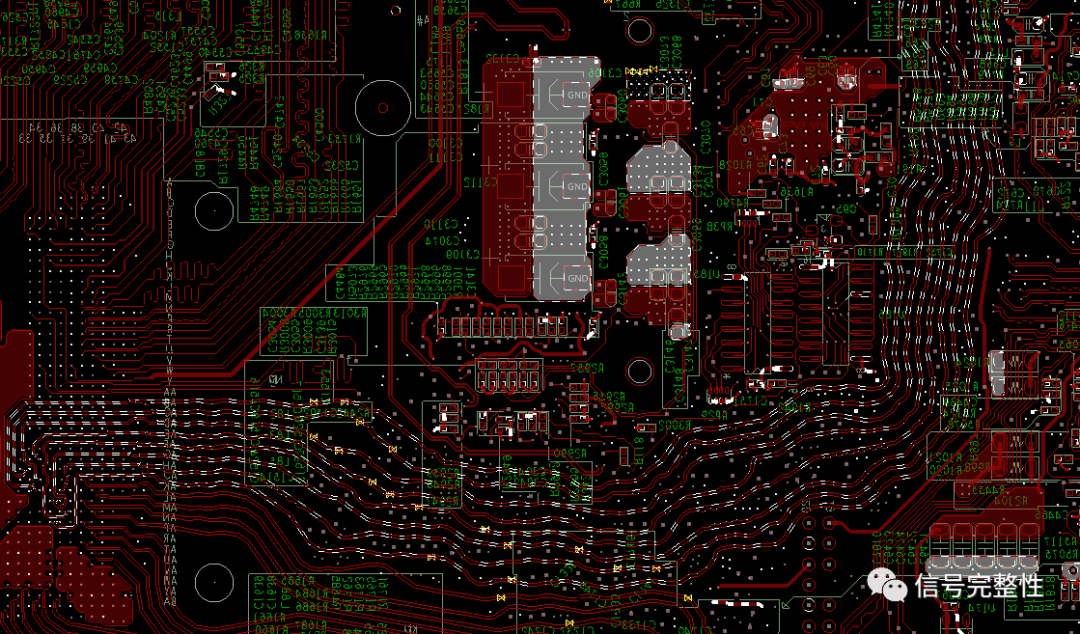

PCIe Switch IDT-89HPES24T6G2,下游端口接了4路PCIe x1,第4路(PE5,pcb中紅色標(biāo)識)無法識別,請教大神們,會是什么原因,設(shè)計有沒有什么問題?差分阻抗都按100Ω設(shè)計的,第4路走線最短反而識別不到。。。相關(guān)設(shè)計請見附件。感謝大佬們!!!

2020-01-08 15:02:27

各位大神好,TI專家好!本人使用自己畫的DSP6678板卡,將PCIe接口通過轉(zhuǎn)接板卡直接連接到機(jī)箱的PCIe插槽中,(沒有使用官方的那種AMC轉(zhuǎn)PCIe卡)初始化PCIe接口后,上位機(jī)PCIe

2018-08-02 07:16:05

請問Intel PCIE怎么使用?

2021-06-21 06:16:59

PCI Express是一種高性能互連協(xié)議,被廣泛應(yīng)用于網(wǎng)絡(luò)適配、圖形加速器、網(wǎng)絡(luò)存儲、大數(shù)據(jù)傳輸以及嵌入式系統(tǒng)等領(lǐng)域。文中介紹了PCIe的體系結(jié)構(gòu),以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收發(fā)器IP提供了一系列完整的PCIe 2.1基本應(yīng)用程序。它符合PIPE 3.0規(guī)范。該IP集成了高速混合信號電路,以支持

2023-04-03 19:47:28

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本應(yīng)

2023-04-03 19:50:56

M31 PCIe 5.0 PHY IP,用于存儲和高帶寬連接 M31 PCIe 5.0 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

PCIE總線基本資料 與PCI總線不同,PCIe總線使用端到端的連接方式,在一條PCIe鏈路的兩端只能各連接一個設(shè)備,這兩個設(shè)備互為是數(shù)據(jù)發(fā)送端和數(shù)據(jù)接收端。PCIe總線除了總線鏈路外,還具

2012-05-10 14:45:47 0

0 近日,北京泛華恒興發(fā)布了PS PCIe-3811轉(zhuǎn)接板。PS PCIe-3811可實現(xiàn)PXIe總線到PCIe總線的無源轉(zhuǎn)接,支持×4寬度的PCIe鏈路,適用于PCIe系統(tǒng)。

2013-06-07 11:05:38 7590

7590 PCIe總線規(guī)范與總線頻率和編碼

2016-12-13 21:06:49 8

8 本文檔內(nèi)容介紹了基于SIM7100-PCIE4G模塊PCIE封裝硬件資料,供參考

2018-03-15 11:26:13 137

137 該文檔給出了KeyStone中PCIE使用的例子,包括地址轉(zhuǎn)換、多設(shè)備連接和編程示例。它還包含PCIE特征的詳細(xì)描述,這些特征補充了PCIE用戶指南中的信息。

2018-04-28 10:32:22 9

9 ? ? ? ?大家好,又到了每日學(xué)習(xí)的時間了,今天我們來聊一聊PCIe的軟件配置方式。? ? ? ?關(guān)于PCIe的軟件配置和初始化? ? ? ?PCIe設(shè)計出來考慮了和pci兼容問題。所以PCIe

2018-07-27 19:16:08 3355

3355

該信號為全局復(fù)位信號,由處理器系統(tǒng)提供(RC),處理器系統(tǒng)需要為PCIe插槽和PCIe設(shè)備提供該復(fù)位信號。PCIe設(shè)備使用該信號復(fù)位內(nèi)部邏輯。當(dāng)該信號有效時,PCIe設(shè)備將進(jìn)行復(fù)位操作。

2018-12-22 14:45:41 22377

22377 M-PCIe即Mobile PCIe,主要應(yīng)用對象是智能手機(jī)等嵌入式設(shè)備。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于標(biāo)準(zhǔn)的PCIe總線

2020-11-24 14:51:48 6996

6996 2021年4月6日 Broadcom最新的PCIe Gen 5 switch芯片內(nèi)置了SerialTek PCIe抓包分析功能,可以大大方便服務(wù)器、存儲系統(tǒng)廠商調(diào)試PCIe Gen 5在初始化

2021-04-13 15:30:47 4797

4797

SerialTek是PCIe,NVMe和SAS/SATA協(xié)議測試解決方案的全球領(lǐng)先提供商,今天推出的PCIe測試和分析市場的最新技術(shù)和產(chǎn)品BusXpertiTAP,支持Broadcom的PCIe嵌入式分析儀技術(shù),這是Broadcom新的PEX89000 Gen5 PCIe交換芯片的一項突破性功能。

2021-04-13 15:34:21 5505

5505

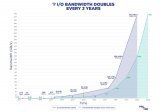

/秒(PCIE5.0 X16),增長了480倍。 PCIe 5.0 第5代PCIe技術(shù) PCIe5.0速度是 PCIe 4.0 的兩倍,并具有向下兼容性。PCIe 5.0 協(xié)議分析儀能夠支持 32GT

2021-06-19 11:04:51 33055

33055 隨著英特爾的十一代酷睿發(fā)布,PC硬件已經(jīng)實現(xiàn)了對PCIe 4.0固態(tài)硬盤的全面支持。PCIe 4.0接口的全面普及推動了固態(tài)硬盤提速潮,PCIe 4.0逐漸走進(jìn)了大眾的視野,成為購買者選購固態(tài)硬盤

2021-09-14 18:09:49 22294

22294 英特爾第12代酷睿處理器都來了,第13代還會遠(yuǎn)嗎?早在官宣之初,英特爾便公布了第12代酷睿處理器的創(chuàng)新優(yōu)勢——不僅是第一款支持大小核的x86平臺,還做到了升級支持DDR5和PCIe 5.0的可觀突破

2021-10-29 17:30:10 2659

2659 此前,英特爾宣布推出了第12代酷睿處理器,這款處理器是首款支持大小核的x86平臺,同時升級支持DDR5和PCIe 5.0。新品上市帶給了我們很多驚喜的同時,也讓不少人產(chǎn)生了疑惑,PCIe 5.0

2021-10-29 17:36:19 3456

3456 電子發(fā)燒友網(wǎng)站提供《PCIe 9110I PCIe 9210I PCIe 9410I EMC證書.pdf》資料免費下載

2022-10-14 10:05:14 1

1 電子發(fā)燒友網(wǎng)站提供《PCIe 9110IM PCIe總線轉(zhuǎn)CAN設(shè)備手冊.pdf》資料免費下載

2022-10-17 10:59:17 1

1 由于最新PCIe標(biāo)準(zhǔn)必須支持以前各代PCIe標(biāo)準(zhǔn),所以對驗證團(tuán)隊來說,每一代新的PCIe標(biāo)準(zhǔn)的測試矩陣都會呈指數(shù)級增長。再加上標(biāo)準(zhǔn)發(fā)展導(dǎo)致的測試復(fù)雜度增加,這明顯提高了實現(xiàn)最新PCIe標(biāo)準(zhǔn)所用的整體測試時間。

2022-11-29 14:08:33 826

826 PCIe接口從2001年發(fā)展至今,在協(xié)議的完整性上已經(jīng)建立足夠高的"護(hù)城河",重新定義一個接口協(xié)議在性能上超越PCIe,短期內(nèi)一方面沒有企業(yè)會有這個動力,另一方面技術(shù)的維度,也沒有可預(yù)期的雛形創(chuàng)新。

2023-04-13 11:10:00 2900

2900 差分探頭是一種常用的測試儀器,在PCIE測試中也有廣泛的應(yīng)用。本文將介紹差分探頭在PCIE測試上的應(yīng)用及其優(yōu)勢。

2023-05-11 10:54:14 451

451 PCI Express? 6.0 (PCIe? 6.0) 規(guī)范由 PCI-SIG? 于 2022 年 1 月發(fā)布。最新一代的 PCIe 標(biāo)準(zhǔn)帶來了許多激動人心的新功能,旨在提高計算密集型工作負(fù)載的性能,包括數(shù)據(jù)中心、 AI/ML 和 HPC 應(yīng)用程序

2023-05-22 17:27:51 4407

4407

PCIe 7.0規(guī)范的數(shù)據(jù)傳輸速率將再次倍增,達(dá)到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個PCIe 7.0 x16通道可以支持512 GB

2023-06-25 10:48:38 506

506

PCIe是一種高速串行計算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),自2003年推出以來,已經(jīng)成為服務(wù)器(Server)和PC上的重要接口。今天為大家簡單介紹一下PCIe的發(fā)展歷史以及它的工作原理。 一、PCIe的由來

2023-07-04 18:15:03 9791

9791 自2003年推出以來,PCIe發(fā)展至今已經(jīng)從最初的1.0升級到了6.0,在上一篇文章中為大家介紹了PCIe基礎(chǔ)知識:《什么是PCIe?》 ,本文則為大家簡單介紹一下 PCIe 標(biāo)準(zhǔn)的演進(jìn)歷史以及

2023-07-26 08:05:01 867

867

? 我們在進(jìn)行PCIe RTL仿真時,由于PCIe ltssm協(xié)商過程比較復(fù)雜,導(dǎo)致PCIe ltssm進(jìn)入L0狀態(tài)所花費的時間比較長(大概在20~60分鐘,因代碼復(fù)雜度、服務(wù)器性能、PCIe速率

2023-08-17 09:42:22 725

725

隨著英特爾Alder Lake CPU的發(fā)布,以及AMD 7000 Ryzen CPU的即將發(fā)布,PCIe 5.0 硬件終于成為現(xiàn)實。但什么是 PCIe 5.0?

2023-11-18 16:48:14 1300

1300

什么是PCIe?PCIe有什么用途?什么是PCIe通道,x1、x4、x8和x16是什么意思?PCIe 5.0有何不同? PCI-Express(peripheral component

2024-01-30 16:09:25 503

503

電子發(fā)燒友App

電子發(fā)燒友App

評論