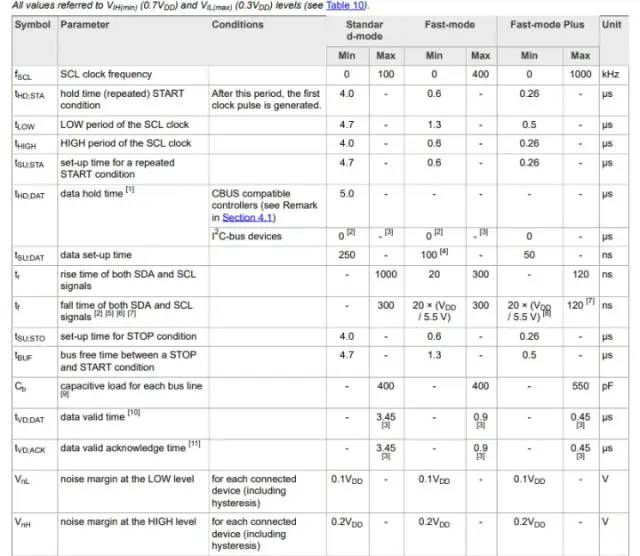

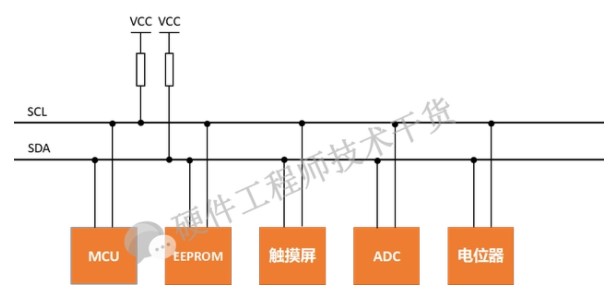

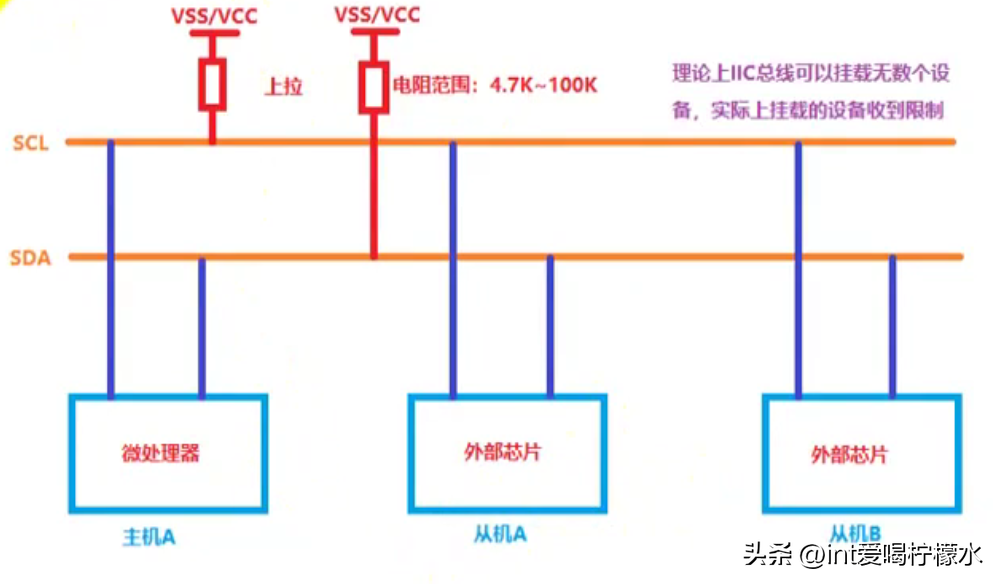

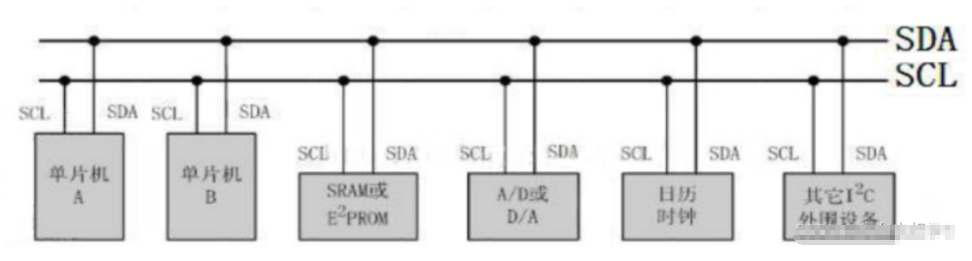

IIC是飛利浦提出的一種通信總線(xiàn)結(jié)構(gòu),其硬件架構(gòu)比較簡(jiǎn)單,僅包含SCL和SDA兩條線(xiàn)。根據(jù)最新的IIC總線(xiàn)標(biāo)準(zhǔn),IIC總線(xiàn)包含Standard-mode(100kbit/s)、Fast-mode(400kbit/s)、Fast-mode Plus(1Mbit/s)、High-speed mode(3.4Mbit/s)以及Ultra-Fast-mode(5Mbit/s)5種不同速率的模式,圖一給出了前三種模式的相關(guān)參數(shù)。

圖1 IIC總線(xiàn)幾種模式的相關(guān)參數(shù)

根據(jù)圖1,可以提出以下幾個(gè)問(wèn)題:

1、幾種不同模式的硬件架構(gòu)有何區(qū)別?

2、不同模式所定義的速率上限是怎么來(lái)的?大于規(guī)定速率的話(huà)會(huì)怎樣?

3、總線(xiàn)電容400pf的要求是怎么確定的,為什么Fast-mode Plus速率更快,

總線(xiàn)電容卻可以更大?

4、為什么會(huì)有上升、下降時(shí)間的限制?Fast-mode和Fast-mode Plus的下降

時(shí)間為什么還有最小值的限制?

5、建立、保持時(shí)間為什么需要限制?

另外,關(guān)于IIC總線(xiàn),還有一些問(wèn)題需要記錄:

- IIC總線(xiàn)的通信協(xié)議?

- 什么是時(shí)鐘延展?

- IIC總線(xiàn)的是怎么仲裁的?

本文將針對(duì)以上問(wèn)題進(jìn)行討論。

幾種不同模式的硬件架構(gòu)有何區(qū)別?

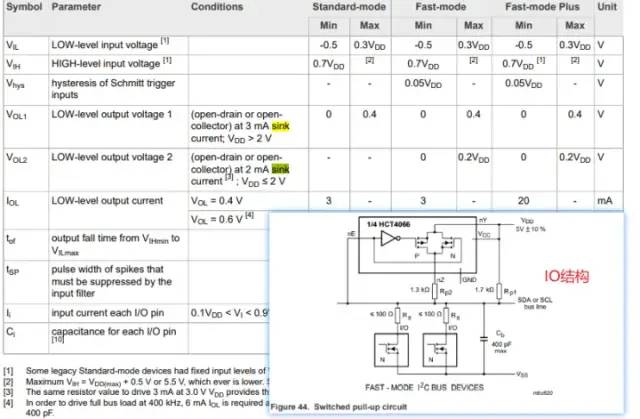

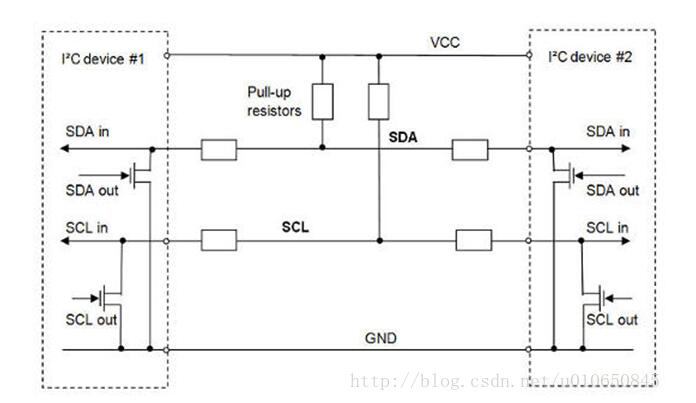

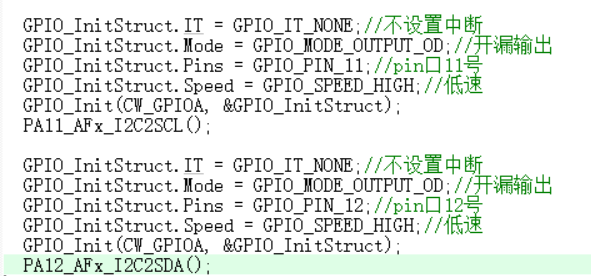

IIC支持五種不同的模式,速率從100k到5M不等,其硬件結(jié)構(gòu)必然有優(yōu)化,才能支持更高的速率,這一點(diǎn)在IIC的標(biāo)準(zhǔn)中也可窺見(jiàn)一二。Standard-mode下,SCL和SDA是普通的OC門(mén),其高電平的輸出依賴(lài)于外部上拉,這一架構(gòu)能使多個(gè)IIC設(shè)備掛在同一條IIC總線(xiàn)上,但是這也限制了IIC總線(xiàn)的上升時(shí)間,從而限制了其通信速率。Fast-mode下,IIC的輸入結(jié)構(gòu)中增加了施密特觸發(fā)器,使得輸入的邊沿可以變得更快,從而獲取更高的通信速率。相應(yīng)在輸出結(jié)構(gòu)中,雖然上升沿的速率依舊取決于外部上拉電阻和總線(xiàn)電容的大小,但在下降沿增加的斜率控制可以減小下降時(shí)間,通過(guò)對(duì)IO結(jié)構(gòu)的改造,F(xiàn)ast-mode獲得了比Standard-mode更高的速率。圖2 給出了Fast-mode下IIC的IO結(jié)構(gòu)及電平特性,F(xiàn)ast-mode Plus在IO結(jié)構(gòu)上和Fast-mode并無(wú)二致,但從圖2可以看出,其驅(qū)動(dòng)電流最大為20mA(Fast-mode下為3mA),這意味著Fast-mode Plus下可以有更快的下降沿和更小的上拉電阻(上升沿也可以更快),從而獲得更高的速率。需要注意的是,從IO結(jié)構(gòu)上看,MOS管是有串接電阻的(標(biāo)準(zhǔn)里說(shuō)該電阻可選),為的是抑制總線(xiàn)的尖峰和串?dāng)_,但是這個(gè)電阻的存在會(huì)讓低電平不為0,在Fast-mode Plus下,由于驅(qū)動(dòng)電流更大,輸出的低電平的值也就更高,部分IIC電平轉(zhuǎn)換芯片輸出低電平可達(dá)到0.6V左右,此時(shí)需要注意輸出低電平是否超門(mén)限。相比于Fast-mode Plus,在Hs-mode下,主機(jī)設(shè)備具有一個(gè)用于SDAH信號(hào)的開(kāi)漏輸出緩沖器(從機(jī)設(shè)備也有),并在SCLH輸出端集成了開(kāi)漏下拉和電流源上拉電路,并且在傳輸期間不執(zhí)行仲裁或時(shí)鐘同步,從而提高了數(shù)據(jù)傳輸速率。Ultra Fast-mode則采用了推挽的輸出結(jié)構(gòu),因此Ultra Fast-mode和其他模式不兼容,也不支持線(xiàn)與(由于推挽輸出結(jié)構(gòu),多設(shè)備并聯(lián)時(shí),如果有不同設(shè)備同時(shí)輸出高電平和低電平,則會(huì)發(fā)生短路),但是推挽的結(jié)構(gòu)進(jìn)一步提升了通信速率。

圖2 Fast-mode下IIC的IO結(jié)構(gòu)及電平特性

不同模式所定義的速率上限是怎么來(lái)的?大于規(guī)定速率的話(huà)會(huì)怎樣?

IIC的不同模式之間速率差異極大,且每種模式的速率提升都伴有硬件架構(gòu)上的改進(jìn)和升級(jí)。那么,各種模式所規(guī)定的速率上限是嚴(yán)謹(jǐn)計(jì)算而來(lái)的嗎?假設(shè)在Standard-mode下,VCC為3.3V(電壓越高,通信速率理論上限應(yīng)該更低,因?yàn)樵谄渌麠l件一定時(shí),越高的電壓等級(jí)意味著越長(zhǎng)的上升時(shí)間),灌電流為3mA,最大輸出電壓為0.4V,那么上拉電阻的最小值為:

在總線(xiàn)電容400pf的情況下,電壓從0上升到0.3VCC所需要的時(shí)間為:

電壓從0上升到0.7VCC所需要的時(shí)間為:

故上升時(shí)間為:

假設(shè)上升沿是線(xiàn)性的,那么,電平從0到Vcc所需的時(shí)間為:

IIC的下降時(shí)間遠(yuǎn)小于上升時(shí)間,這里假設(shè)兩者相等,則上升下降時(shí)間總和為:

假設(shè)上升下降時(shí)間占整個(gè)周期的20%,則Standard-mode下,IIC的最大頻率為:

可見(jiàn),即使在各項(xiàng)都放大的情況下,算出來(lái)的最大頻率都要比Standard-mode所規(guī)定的頻率最大值要大。所以,各種模式下所規(guī)定的的速率是否為硬性要求就值得考慮了。

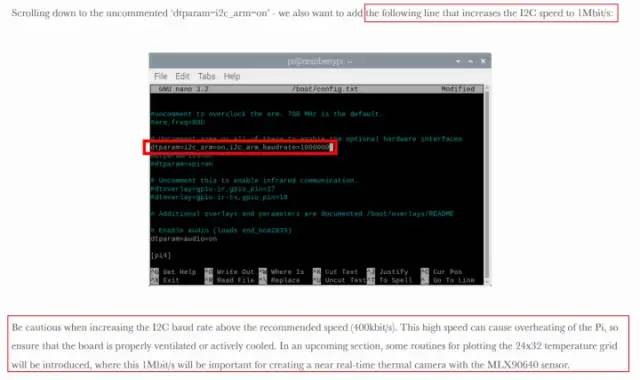

圖3 IIC超推薦頻率使用實(shí)例

圖3給出了一個(gè)IIC超推薦頻率使用的實(shí)例,在《 High Resolution Thermal Camera with Raspberry Pi and MLX90640》 中,作者將IIC的速率提高到1Mbit/s(推薦為400kbit/s),而需要擔(dān)心的僅僅是散熱,當(dāng)然,再高的速率可能導(dǎo)致誤碼。所以,IIC各種模式規(guī)定的速率只是一個(gè)推薦值,但超規(guī)格使用一般是不建議的。

總線(xiàn)電容400pf的要求是怎么確定的,為什么Fast-mode Plus速率更快,總線(xiàn)電容卻可以更大?

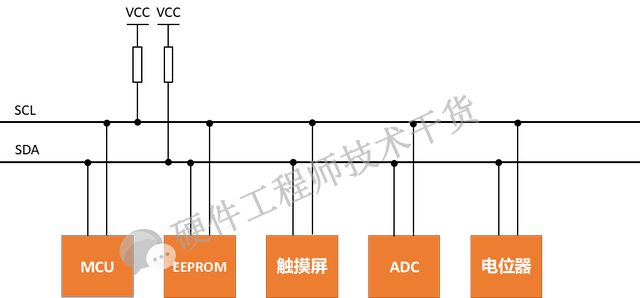

IIC的設(shè)備地址是7位,所以理論上IIC總線(xiàn)上可以?huà)?27個(gè)設(shè)備(地址0x0不使用),但是IIC總線(xiàn)有400pf的限制,所以一般而言,IIC總線(xiàn)上的設(shè)備數(shù)是達(dá)不到127的。那么,400pf這個(gè)限制是怎么來(lái)的呢?要討論這個(gè)問(wèn)題,首先要明確總線(xiàn)電容會(huì)影響什么參數(shù)。首先,電容的的大小會(huì)影響總線(xiàn)電壓的充放電速度,從而影響上升/下降沿的斜率,這對(duì)通信速率形成了限制;其次,總線(xiàn)電容和電阻形成了一個(gè)濾波器,當(dāng)頻率高時(shí),信號(hào)會(huì)產(chǎn)生衰減,當(dāng)信號(hào)衰減幅度超過(guò)電平判決門(mén)限時(shí),就會(huì)導(dǎo)致誤碼,因此其對(duì)通信頻率也是一個(gè)限制。這兩點(diǎn)在我的 《串口通信》 一文中已經(jīng)展開(kāi)討論過(guò),在正常情況下,這兩點(diǎn)所確認(rèn)的總線(xiàn)電容上限都比400pf要大得多,而且充放電速度的大小不僅取決于總線(xiàn)電容的大小,對(duì)IIC總線(xiàn)而言,還和上拉電阻的大小以及驅(qū)動(dòng)電流的上限相關(guān)。根據(jù)IIC的標(biāo)準(zhǔn),F(xiàn)ast-mode Plus的總線(xiàn)電容上限為550pf,相較于Fast-mode,其擁有更高的通信速率但卻可以容忍更大的總線(xiàn)電容,其原因就是因?yàn)镕ast-mode plus的灌電流能力能達(dá)到20mA(實(shí)際看部分芯片的數(shù)據(jù)手冊(cè),30mA的也有),所以無(wú)論是總線(xiàn)電容400pf的限制還是灌電流能力,這些我個(gè)人都傾向于認(rèn)為是標(biāo)準(zhǔn)給出的一個(gè)建議值,而各半導(dǎo)體廠(chǎng)商在設(shè)計(jì)芯片時(shí),首先會(huì)滿(mǎn)足標(biāo)準(zhǔn)的要求,保證各廠(chǎng)家芯片對(duì)接的通用性,這是標(biāo)準(zhǔn)存在的意義。當(dāng)然,在滿(mǎn)足標(biāo)準(zhǔn)的前提下,如果成本上滿(mǎn)足要求或基于產(chǎn)品競(jìng)爭(zhēng)力的考慮,廠(chǎng)家也可以將芯片設(shè)計(jì)得更強(qiáng)大(例如30mA的灌電流能力),這就是芯片手冊(cè)的參數(shù)和標(biāo)準(zhǔn)不盡一致的原因。

為什么會(huì)有上升、下降時(shí)間的限制?Fast-mode和Fast-mode Plus的下降

時(shí)間為什么還有最小值的限制?

圖1給出了幾種模式下上升、下降時(shí)間的要求,根據(jù)相關(guān)參數(shù)可以看出,上升/下降時(shí)間最大值占整個(gè)周期時(shí)間的12%左右,即使將標(biāo)準(zhǔn)放寬一倍,其時(shí)間占比也不足整個(gè)周期的50%。那么,緩慢的上升/下降時(shí)間到底會(huì)帶來(lái)什么不好的影響呢?

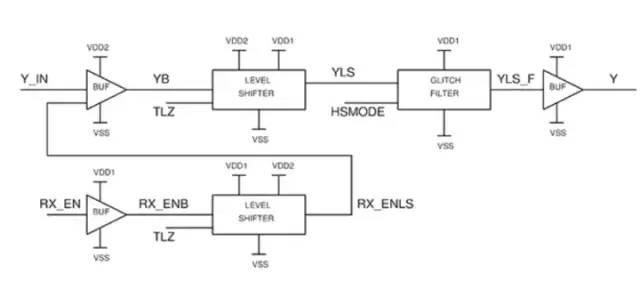

上升/下降時(shí)間所規(guī)定的都屬輸入端的要求,所以要討論這個(gè)問(wèn)題,首先要弄清楚IIC輸入結(jié)構(gòu)是什么樣子, 《Designing I/O Drivers for Integrated Circuit IIC Modules》 一文中給出了IIC模塊輸入結(jié)構(gòu)的框圖,如圖3所示。

圖4 IIC的輸入結(jié)構(gòu)框圖

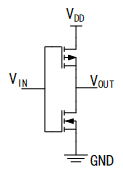

由圖4可以看到,IIC輸入經(jīng)過(guò)buffer緩沖,在移位寄存器處實(shí)現(xiàn)電平轉(zhuǎn)換,過(guò)濾毛刺后再輸出給后級(jí)的處理邏輯。緩沖器的結(jié)構(gòu)示意圖如圖4所示,可以看做是兩個(gè)反相器的串聯(lián),而反相器的則是由CMOS電路組成的,即IIC信號(hào)輸入首先到達(dá)的是一個(gè)CMOS反相器。

圖5 CMOS反相器

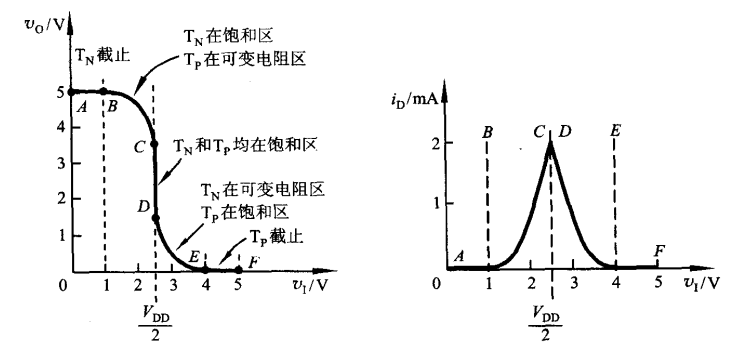

CMOS反相器由一個(gè)NMOS和一個(gè)PMOS組成,其電路結(jié)構(gòu)如圖5所示。其原理也比較簡(jiǎn)單,在輸入為高時(shí),NMOS導(dǎo)通,輸出為0;輸入為低時(shí),PMOS導(dǎo)通,輸出為1。在華科的 《電子技術(shù)基礎(chǔ)——數(shù)字部分》 一書(shū)中,還給出了其電壓、電流傳輸特性如圖5所示。從其電壓、電流的傳輸特性可以看出,CMOS電路的兩個(gè)MOS管可能存在直通的現(xiàn)象,雖然書(shū)中理想化地將該電壓標(biāo)注為VDD/2,但從MOS管的工作原理上看,兩個(gè)MOS同時(shí)導(dǎo)通必然對(duì)應(yīng)的是一個(gè)電壓范圍。也就是說(shuō),過(guò)長(zhǎng)的上升/下降時(shí)間會(huì)使CMOS電路直通的時(shí)間變長(zhǎng),從而增加電路損耗甚至可能導(dǎo)致器件損壞。

圖6 CMOS電壓電流傳輸特性

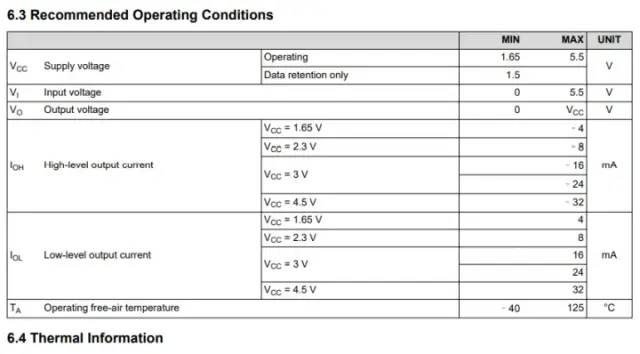

但在圖1中,上升/下降時(shí)間不僅有最大值的限制,在Fast-mode和Fast-mode plus下,下降時(shí)間的最小值也存在限制。前述,相較于Standard-mode,F(xiàn)ast-mode的硬件結(jié)構(gòu)在輸入端增加了施密特觸發(fā)器和尖峰抑制,輸出端增加了斜率控制電路,但是,查看施密特觸發(fā)器的datasheet(以SN74LVC1G17為參考),上升時(shí)間并沒(méi)有相關(guān)的規(guī)格要求。

圖7 SN74LVC1G17的參數(shù)要求

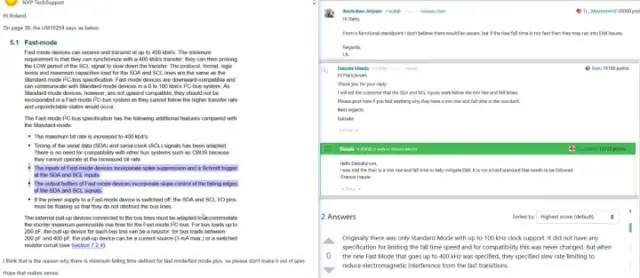

在NXP和TI的社區(qū)中,關(guān)于這個(gè)問(wèn)題的解釋見(jiàn)圖8,NXP的解釋是可能和Fast-mode的輸入輸出結(jié)構(gòu)相關(guān),但并未給出具體的原因;TI給出的回答是在Fast-mode以及更高速率的模式下,上升/下降時(shí)間太快可能帶來(lái)EMI問(wèn)題,但這一規(guī)定并不是強(qiáng)制要求的(根據(jù)經(jīng)驗(yàn),下降時(shí)間一般都小于20ns,且我本人尚未碰到過(guò)應(yīng)用問(wèn)題)。

圖8 NXP和TI社區(qū)中關(guān)于上升時(shí)間最低值限制的問(wèn)題

建立、保持時(shí)間的要求從何而來(lái)?

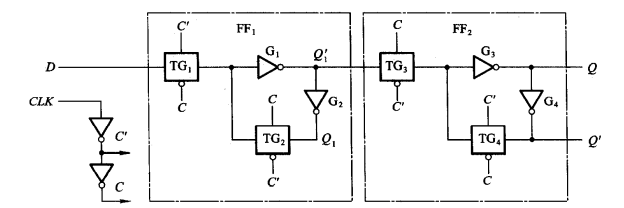

由圖3可知,從機(jī)接收到輸入信號(hào)后,會(huì)將其保存到寄存器中,在輸入到后級(jí)進(jìn)行處理。寄存器由觸發(fā)器構(gòu)成,以D觸發(fā)器為例,其結(jié)構(gòu)如圖8所示。

圖9 D觸發(fā)器的電路結(jié)構(gòu)

根據(jù)圖9可以看出,D觸發(fā)器實(shí)際是由兩個(gè)鎖存器串聯(lián)而成,當(dāng)CLK為低電平時(shí),傳輸門(mén)TG1、TG4打開(kāi),TG2、TG3關(guān)閉,觸發(fā)器的輸入信號(hào)經(jīng)過(guò)G1輸出到Q1’,并經(jīng)過(guò)Q1輸出到TG2的輸入端,當(dāng)CLK變高瞬間,TG1、TG4關(guān)閉,TG2、TG3打開(kāi),主鎖存器的輸出通過(guò)TG3輸出,在這個(gè)過(guò)程中,需要確保TG2有關(guān)閉到打開(kāi)時(shí),傳輸門(mén)兩邊的電平一致,這樣Q1’才能輸出穩(wěn)定的信號(hào),建立時(shí)間指的便是TG1、G1、G2的延時(shí),即:

保持時(shí)間要求的來(lái)源也類(lèi)似,為保證輸出Q穩(wěn)定,則在CLK變高時(shí),Q1’的電平要保持穩(wěn)定,而TG1的關(guān)閉需要時(shí)間,所以保持時(shí)間為:

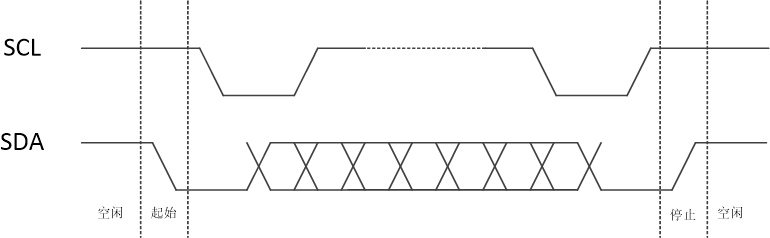

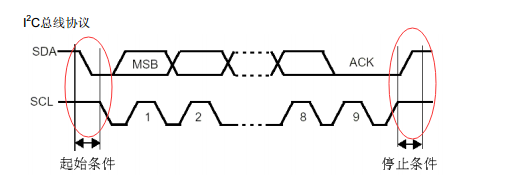

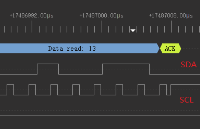

IIC總線(xiàn)的通信協(xié)議

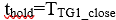

IIC的一幀數(shù)據(jù)包含9個(gè)bit,主要包括起始位、停止位、讀寫(xiě)標(biāo)志位、應(yīng)答位、設(shè)備地址、寄存器地址以及數(shù)據(jù)幾項(xiàng)內(nèi)容。其中, SCL為高時(shí),SDA拉低為起始標(biāo)志位;SCL為高時(shí),SDA拉高為停止標(biāo)志位;讀寫(xiě)標(biāo)志位只有一位,0表示寫(xiě),1表示讀;應(yīng)答位低有效,應(yīng)答位為高表示非應(yīng)答。另外,IIC的讀寫(xiě)幀格式不太一樣,下面分別描述。

- 寫(xiě)操作

IIC寫(xiě)操作時(shí)的幀格式如圖10所示,陰影部分為主機(jī)發(fā)出,空白部分則為從機(jī)發(fā)出。首先由主機(jī)發(fā)出起始位,由于IIC可能有多個(gè)設(shè)備,所以在起始位發(fā)出后,第一幀數(shù)據(jù)會(huì)發(fā)送設(shè)備地址對(duì)從機(jī)進(jìn)行尋址(設(shè)備地址一般為7bit),第8位數(shù)據(jù)則是讀寫(xiě)標(biāo)志位,在寫(xiě)操作時(shí),該bit為0,第9位則為從機(jī)發(fā)出的應(yīng)答位。完成尋址后,需要指定要寫(xiě)入寄存器的地址,隨后寫(xiě)入數(shù)據(jù)。完成以上步驟,主機(jī)發(fā)出停止位,即完成了一次讀操作。

圖10 IIC寫(xiě)操作的幀格式

讀操作

讀操作稍微比較復(fù)雜,有讀當(dāng)前地址數(shù)據(jù)和隨機(jī)讀兩種不同場(chǎng)景。讀當(dāng)前地址數(shù)據(jù)的幀格式如圖11 所示。在主機(jī)選擇相應(yīng)的從機(jī)設(shè)備后,從機(jī)會(huì)將數(shù)據(jù)發(fā)送給主機(jī),數(shù)據(jù)傳輸完成后,主機(jī)發(fā)出NACK后發(fā)出停止位即完成一次數(shù)據(jù)傳輸。

圖11 IIC讀當(dāng)前地址的幀格式

隨機(jī)讀模式較為復(fù)雜,其幀格式如圖12所示。由于要指定特定寄存器地址,所以IIC首先要進(jìn)行一次寫(xiě)操作(無(wú)需寫(xiě)入數(shù)據(jù),只是為了定位到需要讀取的寄存器地址),隨后再按讀當(dāng)前地址的幀格式操作即可完成隨機(jī)地址寄存器信息的讀取。

圖12 IIC讀隨機(jī)地址的幀格式

關(guān)于IIC的幀格式這一塊,網(wǎng)上的資料眾多,相關(guān)芯片的數(shù)據(jù)手冊(cè)里對(duì)此也有很多描述,IIC的讀寫(xiě)操作還有單次讀寫(xiě)和頁(yè)讀寫(xiě)的操作,其幀格式在此不再贅述。

關(guān)于時(shí)鐘延展

時(shí)鐘延展在IIC標(biāo)準(zhǔn)的High-speed mode的章節(jié)中有所提及,這一功能是為了解決系統(tǒng)中存在使用不同速率的IIC總線(xiàn)設(shè)備的通信問(wèn)題,它允許從機(jī)在來(lái)不及處理數(shù)據(jù)的時(shí)候拉低SCL,從而有更多的時(shí)間處理接收到的數(shù)據(jù)。這一功能讓IIC變得更加靈活,因?yàn)閺臋C(jī)可以控制SCL意味著給了從機(jī)設(shè)備發(fā)出中斷的能力,那么在通信或者其他功能的控制上就可以更加方便。這一功能在實(shí)際的應(yīng)用中也比較常見(jiàn)。

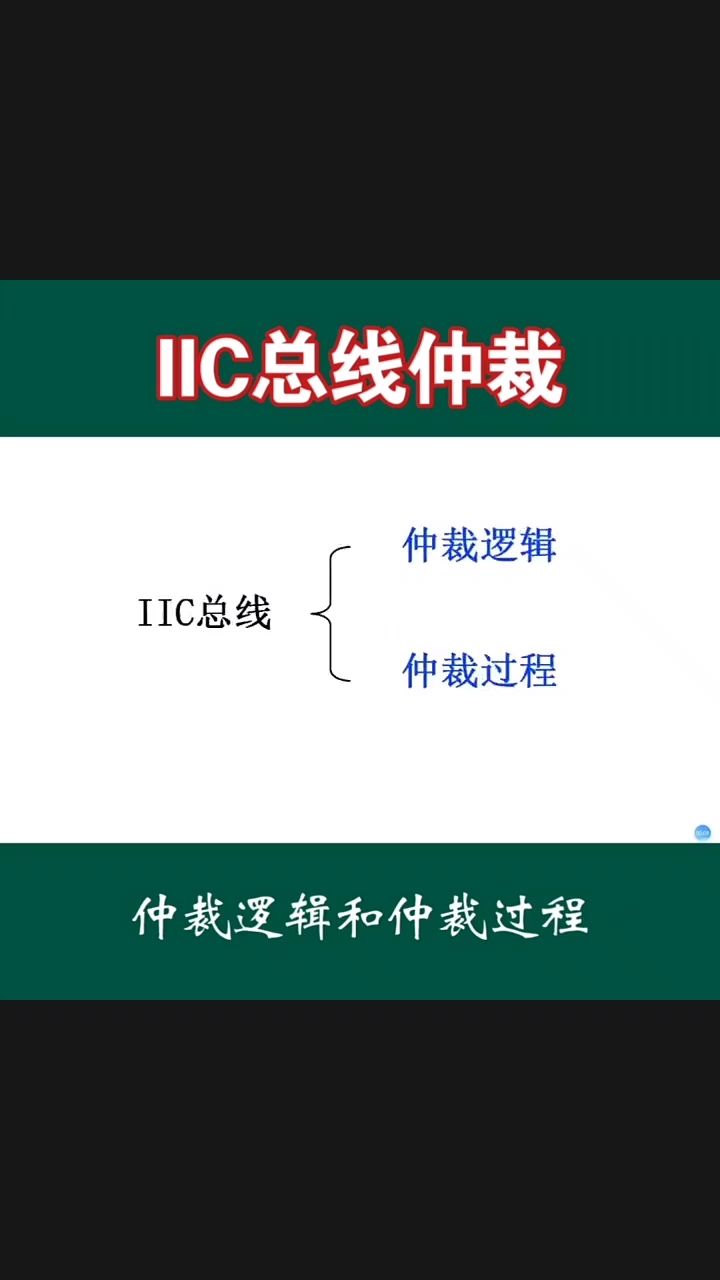

關(guān)于仲裁

IIC總線(xiàn)允許在同一條主線(xiàn)上有多個(gè)主機(jī)和多個(gè)從機(jī),那么在多個(gè)主機(jī)同時(shí)發(fā)起通信的時(shí)候,就會(huì)產(chǎn)生沖突,而解決這個(gè)沖突的過(guò)程就是仲裁。IIC的仲裁機(jī)制由其OC/OD門(mén)輸出結(jié)構(gòu)實(shí)現(xiàn),多個(gè)設(shè)備掛在同一條IIC總線(xiàn)上時(shí)時(shí)線(xiàn)與的關(guān)系,那么其時(shí)鐘速率必然由速率最低的主機(jī)決定(假設(shè)占空比為50%,由于線(xiàn)與的特性,SCL的波形決定于低電平最長(zhǎng)的主機(jī)的SCL)。但是,SCL和SDA是同時(shí)發(fā)出的,且SCL和SDA互相感知不到對(duì)方是否正常,在多主機(jī)沖突的時(shí)候,即使SCL的波形已經(jīng)由頻率最低的主機(jī)決定了,其他主機(jī)的SDA也依然在繼續(xù)發(fā)送數(shù)據(jù)。所以,在SCL為高時(shí),每個(gè)主機(jī)會(huì)探測(cè)SDA上的數(shù)據(jù)是否與自己發(fā)送的數(shù)據(jù)一致,不一致則退出總線(xiàn)控制權(quán)的競(jìng)爭(zhēng),在這個(gè)過(guò)程當(dāng)中,IIC數(shù)據(jù)不會(huì)丟失,且最后剩下的主機(jī)即使有超過(guò)一個(gè),那么對(duì)應(yīng)從機(jī)收到的數(shù)據(jù)也是正確的。通過(guò)以上描述可以知道,IIC總線(xiàn)控制權(quán)的競(jìng)爭(zhēng)僅取決于SDA,多個(gè)主機(jī)無(wú)法排優(yōu)先級(jí)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論