0電阻 上拉電阻 下拉電阻

2012-08-06 13:38:12

如圖,像這種IIC的電路為什么要加這些4.7kΩ、100Ω的上拉電阻?

2019-02-15 09:58:53

I2C信號(hào)一般需要外接上拉電阻,如果主控內(nèi)部有上拉電阻,是否可以省略外部上拉?這個(gè)是否需要上拉根據(jù)什么來決定?是根據(jù)從器件的輸入電流來決定的嗎?芯片的輸入電流參數(shù)(Ii 即input current)怎么理解,設(shè)計(jì)電路時(shí)針對(duì)這個(gè)參數(shù)需要注意什么?

2018-06-07 10:01:00

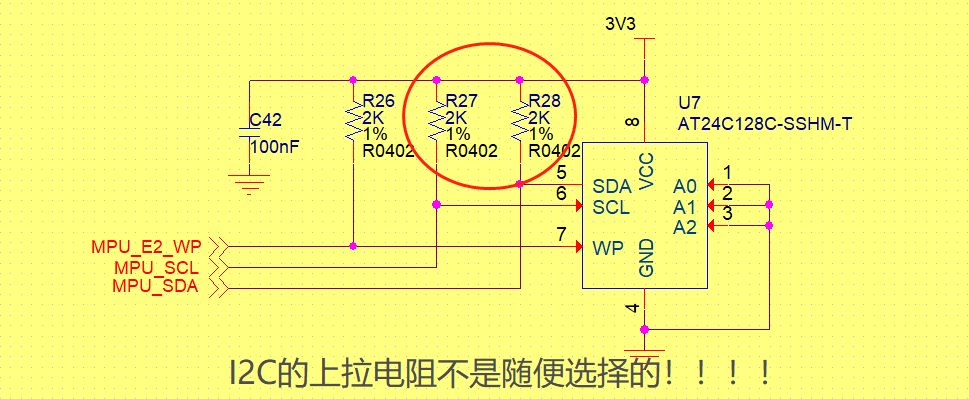

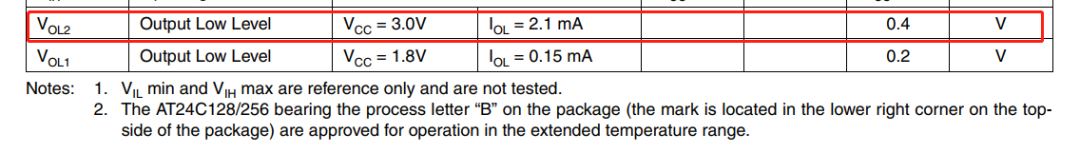

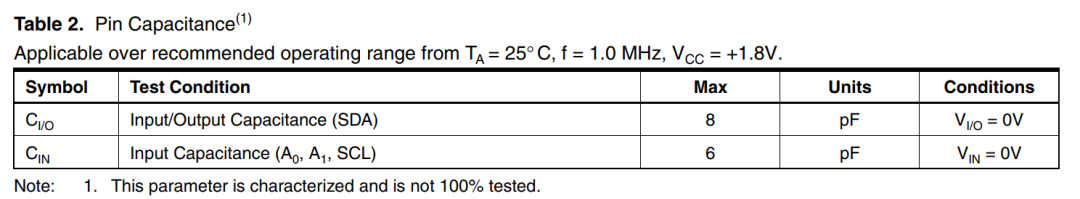

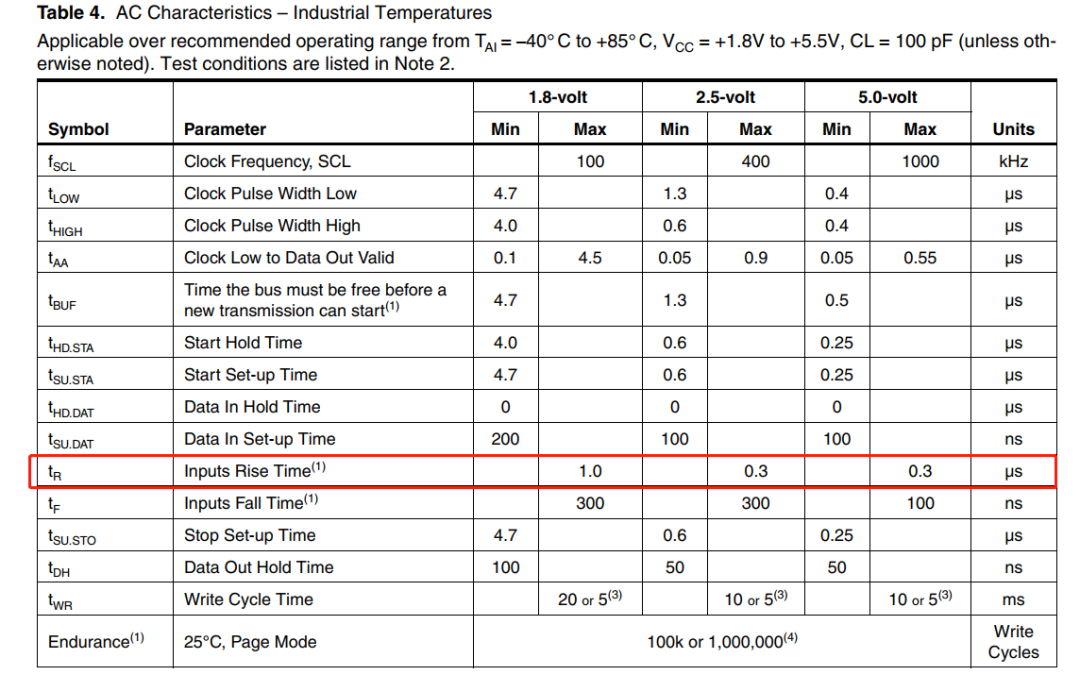

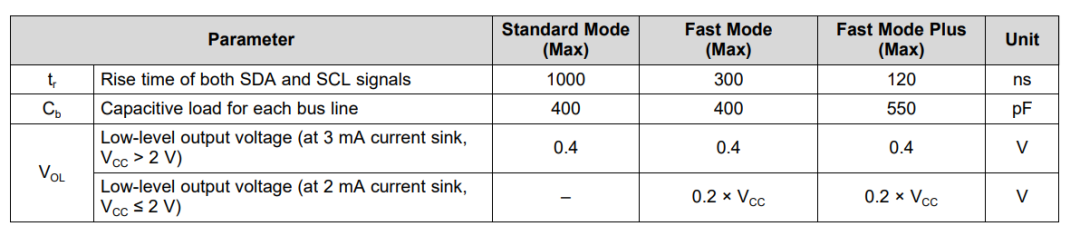

了VoL具體值的,參見圖4。而廠家測(cè)試Vol值時(shí)也會(huì)有個(gè)測(cè)試條件即IoL和Vcc。所以這兩個(gè)值確定好后就可以計(jì)算出I2C上拉電阻的最小值了。圖4 AT24CM02數(shù)據(jù)手冊(cè)DC特征中的VoL(這里如

2022-11-29 08:00:00

V和V 邏輯高 = 1.2 V 的任意值,并假設(shè)總線電容為150 pF,我們具有以下幾點(diǎn):摘要I2C上拉電阻的值必須足夠大以減少不必要的電流消耗,并且必須足夠小以產(chǎn)生可接受的上升時(shí)間。本文介紹的計(jì)算

2020-09-21 09:00:00

我的I2C通信需要被拉到3.3V,但是我不知道我應(yīng)該使用什么尺寸的上拉電阻。我讀過的其他論壇的帖子,建議2.7k歐姆或4.7K歐姆,但這似乎只是讓高可以在3.3V和是在3.0V低。這是正常的嗎?我用

2019-04-03 15:13:49

TQ144封裝的XC3S200。據(jù)我所知,HSWAP_EN上的2.5V構(gòu)成1邏輯電平,應(yīng)禁用上拉電阻,使LED亮。無論出于何種原因,引腳44和47似乎都激活了上拉電阻,而引腳46使它們無效。而且我說

2019-05-16 14:05:51

,其上拉電流要由上拉電阻來提供,設(shè)輸入端每端口不大 于100uA,設(shè)輸出口駔動(dòng)電流約500uA,標(biāo)準(zhǔn)工作電壓5V.輸入口的高低電平門限為 0.8V(低于此值為低電平);2V(高電平門限值)。選上拉電阻

2017-08-28 09:27:18

,其上拉電流要由上拉電阻來提供,設(shè)輸入端每端口不大 于100uA,設(shè)輸出口駔動(dòng)電流約500uA,標(biāo)準(zhǔn)工作電壓5V.輸入口的高低電平門限為 0.8V(低于此值為低電平);2V(高電平門限值)。選上拉電阻

2017-11-16 17:14:38

上拉電阻:1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2、OC門電路必須

2011-09-19 08:55:51

(上拉下拉電阻)所謂上拉電阻就是:將一個(gè)不確定信號(hào)(高或低電平),通過一個(gè)電阻與電源VCC相連,固定在高電平;同理下拉電阻就是:將一個(gè)不確定信號(hào)(高或低電平),通過一個(gè)電阻與地GND相連,固定

2022-01-14 08:44:01

上拉電阻與下拉電阻上拉(Pull Up )或下拉(Pull Down)電阻(兩者統(tǒng)稱為“拉電阻”)最基本的作用是:將狀態(tài)不確定的信號(hào)線通過一個(gè)電阻將其箝位至高電平(上拉)或低電平(下拉),無論它

2021-12-13 07:08:22

上拉電阻與下拉電阻用在什么場(chǎng)合? 答:用在數(shù)字電路中,存在高低電平的場(chǎng)合。 上拉電阻與下拉電阻怎么接線? 上拉電阻:電阻一端接VCC,一端接邏輯電平接入引腳(如單片機(jī)引腳) 下拉電阻:電阻一端接GND,一端接邏輯電平接入引腳(如單片機(jī)引腳)

2019-05-20 13:48:41

:一般說法是上拉增大電流,下拉電阻是用來吸收電流。1、當(dāng) TTL 電路驅(qū)動(dòng) CMOS 電路時(shí),如果電路輸出的高電平低于 CMOS 電路的最低高電平 (一般為 3.5V), 這時(shí)就需要在 TTL 的輸出端接上拉電阻,以提高輸出高電平的值。2、OC 門電路必須使用上拉電阻,以提高輸出的高電平值。

2021-12-13 06:05:27

上拉電阻與下拉電阻是如何定義的?拉電阻的作用有哪些?上拉電阻的應(yīng)用原則有哪些?

2021-10-14 07:20:37

一句話:上拉電阻的目的是為了保證GPIO無信號(hào)輸入時(shí)輸入端的電平為高電平,相反的,下拉電阻是為了保證GPIO無信號(hào)輸入時(shí)輸入端的電平為低電平。不懂的具體可以看下面一、概念上拉電阻就是:將一個(gè)不確定

2022-01-14 09:16:39

硬件電路中的上拉電阻為什么能上拉?

2021-01-28 07:50:20

一般IIC和SPI接口建議加上拉電阻

但有時(shí)(比如SPI)不上拉,或使用內(nèi)部上拉也能正常運(yùn)行。

請(qǐng)問,上拉主要與什么有關(guān)?是否高波特率必須強(qiáng)上拉?

一般上拉電阻選取多大阻值?

2023-10-28 06:23:36

上拉電阻到底是咋完成上拉的啊

2023-10-31 06:52:32

經(jīng)常看到芯片設(shè)計(jì)手冊(cè)時(shí),芯片外圍會(huì)有上拉或者下拉電阻還有一些無源器件。如何選擇正確值的上拉電阻和下拉電阻?上拉電阻和下拉電阻是如何確定?還是在選擇此類電阻的時(shí)候,有個(gè)特定的范圍?對(duì)上拉電阻和下拉電阻

2021-11-12 07:28:55

上拉電阻和下拉電阻的區(qū)別及案列分析上拉電阻在一個(gè)信號(hào)未過來之前、默認(rèn)(保證)該電位的電平信號(hào)是高電平,在信號(hào)過來后如果是高電平、那么保持高電平。如果過來低電平信號(hào)、那么輸出的信號(hào)就會(huì)變成低電平。改圖

2022-01-14 06:30:35

上拉電阻:1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2、OC門電路必須

2008-05-22 08:46:35

TTL電路驅(qū)動(dòng)CMOS電路時(shí),如果電路輸出的高電平低于CMOS電路的最低高電平(一般為 3.5V), 這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2.OC門電路必須使用上拉電阻,以提高輸出的高電平值。3.為增強(qiáng)輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。4.在CMO

2022-01-25 07:23:49

上拉電阻和下拉電阻

2022-01-14 08:02:00

接口的輸出端是漏極開路或集電極開路,所以必須在接口外接上拉。上拉電阻的取值和I2C總線的頻率有關(guān),工作在standard mode時(shí),其典型值為10K。在FAST mode時(shí),為減少時(shí)鐘上升時(shí)間,滿足

2018-10-19 16:30:19

高電平的值。 2、OC門電路必須加上拉電阻,才能使用。 3、為加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。 4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉

2019-06-27 05:55:08

上拉電阻: 1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。 2、OC

2021-12-07 08:27:59

上拉電阻:1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2、OC門電路必須

2021-11-25 08:33:42

,TTL)或OD(漏極開路,CMOS)輸出,那么不用上拉電阻是不能工作的, 這個(gè)很容易理解,管子沒有電源就不能輸出高電平了。2、如果輸出電流比較大,輸出的電平就會(huì)降低(電路中已經(jīng)有了一個(gè)上拉電阻,但是

2021-12-01 11:15:35

上拉電阻有什么作用?如何去計(jì)算上拉電阻的阻值?51型單片機(jī)IO口有什么特點(diǎn)?AVR單片機(jī)IO口的輸入狀態(tài)有哪幾種?

2021-07-07 07:29:25

,考慮到這個(gè)項(xiàng)目是帶模擬電視芯片的,以前就出現(xiàn)過模擬電視芯片的I2C地址沒有去配,導(dǎo)致出現(xiàn)漏電情況,遂立馬去看是不是這個(gè)問題,結(jié)果是遺憾的,配了!那再仔細(xì)檢查了基帶的GPIO口和其他的I2C,發(fā)現(xiàn)都配

2011-12-15 18:34:39

上拉電阻的計(jì)算(一)上拉電阻:1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值

2014-05-12 08:24:37

上拉電阻的作用

2021-01-29 07:18:20

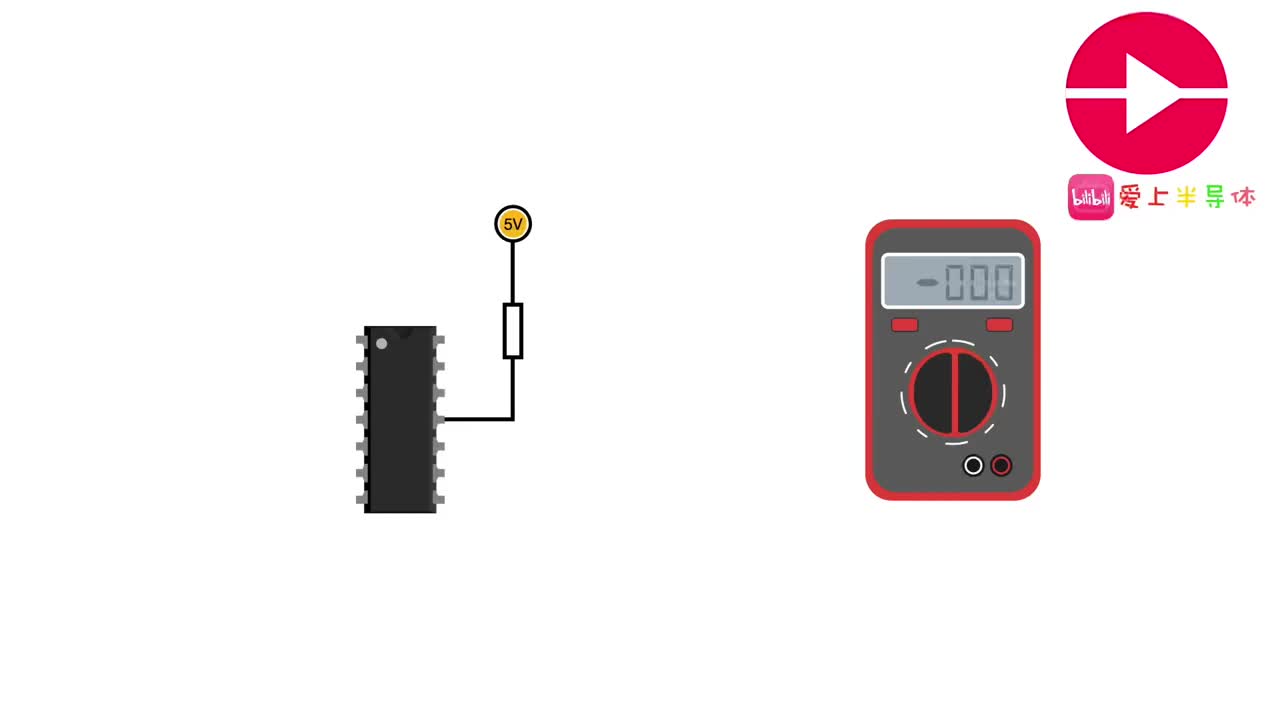

1、介紹使用微控制器(MCUs) 或任何數(shù)字邏輯設(shè)備時(shí),上拉電阻器非常常見。本教程將解釋何時(shí)何地使用上拉電阻器,然后我們將做一個(gè)簡(jiǎn)單的計(jì)算,以顯示為什么上拉很重要。2、上拉電阻是什么?假...

2022-02-09 06:35:16

stc89c52單片機(jī)除了p0口其他io口都沒有集成上拉電阻。上拉電阻的作用:?jiǎn)纹瑱C(jī)內(nèi)部控制io口高低電平是通過類似場(chǎng)效應(yīng)管或三極管的裝置進(jìn)行控制的,以三極管為例,三極管的集電極連接電源負(fù)極集電極

2022-01-14 07:14:42

。2、OC 門電路必須加上拉電阻,以提高輸出的搞電平值。3、為加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。4、在COMS 芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉...

2021-07-27 06:52:51

上拉、下拉電阻的作用

2012-08-20 14:53:59

2中的低電平由VL變?yōu)閂L+ΔV時(shí),產(chǎn)生了從低電平到高電平的跳變,有可能使后級(jí)電路誤動(dòng)作的風(fēng)險(xiǎn)。 下一個(gè)問題就是,確定了用上拉電阻后,是不是上拉電阻就可以隨便選了呢?答案當(dāng)然是“no”。(如圖3) A

2018-10-08 15:44:08

/ q& {$ a/ o$ U9 w+ S+ Y* ?電阻在選用時(shí),選用經(jīng)過計(jì)算后與標(biāo)準(zhǔn)值最相近的一個(gè)! 為什么要上拉電阻原因有: 1. P0口片內(nèi)無上拉電阻 2. P0為I/O口工作狀態(tài)時(shí),上方FET

2014-11-17 10:24:15

默認(rèn)值為高電平,你要控制它必須用低電平才能控制如三態(tài)門電路三極管的集電極,或二極管正極去控制把上拉電阻的電流拉下來成為低電平。反之, C、尤其用在接口電路中,為了得到確定的電平,一般采用這種方法,以保證

2020-12-14 17:21:30

! -------一般說的是I/O端口,有的可以設(shè)置,有的不可以設(shè)置,有的是內(nèi)置,有的是需要外接,I/O端口的輸出類似與一個(gè)三極管的C,當(dāng)C接通過一個(gè)電阻和電源連接在一起的時(shí)候,該電阻成為上C拉電阻

2018-06-28 06:21:54

AVR微控制器的I/O口是雙向口。具有如下的特點(diǎn):AVR IO具備多種IO模式:1 高阻態(tài),多用于高阻模擬信號(hào)輸入,例如ADC數(shù)模轉(zhuǎn)換器輸入,模擬比較器輸入2 弱上拉狀態(tài)(Rup=20K~50K

2011-11-15 14:10:42

GPIO上有上拉電阻嗎?

如果不是,那么當(dāng)您釋放按鈕時(shí),GPIO 基本上只是浮動(dòng)的,可以是任何值。

要么從 GPIO 上拉 10K 到 3.3V,要么將 pinMode 更改為 INPUT_PULLUP。后者將使用大約 36K 的內(nèi)部上拉電阻,只要到按鈕的引線相當(dāng)短就可以了

2023-05-22 06:54:06

如題!最近設(shè)計(jì)I2C的時(shí)候,考慮上拉電阻的位置有這個(gè)疑問

2019-02-19 15:39:49

我現(xiàn)在遇到一個(gè)問題HDC1080 SDA引腳與STM32F031F6 PA7相連,頻率從1k到100K,上拉電阻為1K和10K時(shí),STM32F031F6檢測(cè)的數(shù)據(jù)都是滿偏AD值,在SDA總線上加一個(gè)

2018-09-26 17:03:56

按下時(shí),由于干擾,可能高也可能是低信號(hào)輸入。根據(jù)實(shí)際需要,為保證WK_UP不被按下時(shí),STM32能夠確定檢測(cè)到IO口是低電平,所以設(shè)置接入下拉電阻。2、上拉電阻和下拉電阻上拉電阻...

2021-08-18 06:27:20

下拉電阻使電阻匹配,能有效的抑制反射波干擾。5、預(yù)設(shè)空間狀態(tài)/默認(rèn)電位在一些CMOS輸入端接上拉或下拉電阻是為了預(yù)設(shè)默認(rèn)電位。當(dāng)不用這些引腳時(shí),這些輸入端下拉接低電平或上拉接高電平。在I2C等總線

2019-10-08 07:00:00

上拉下拉電阻的定義以及用法為什么要使用拉電阻上拉電阻阻值的選擇原則

2021-04-06 06:06:42

CMOS 輸入端接上或下拉電阻是為了預(yù)設(shè)缺省電位。當(dāng)你不用這些引腳的時(shí)候,這些輸入端下拉接 0 或上拉接 1。在I2C總線等總線上,空閑時(shí)的狀態(tài)是由上下拉電阻獲得。

6. 提高芯片輸入信號(hào)的噪聲容限

2023-05-18 17:30:56

我現(xiàn)在有一個(gè)驅(qū)動(dòng)芯片BD169,資料上說他的輸入端口最大高電平電流是100uA,正常值是50UA,本來正常使用應(yīng)該是用單片機(jī)來驅(qū)動(dòng)的,但是我現(xiàn)在想手動(dòng),就是自己接一個(gè)5V的電壓當(dāng)做高電平,我問下我可以接個(gè)100K的電阻來作為上拉電阻嗎?

2013-06-13 10:27:33

仿真電路如圖,感覺上拉電阻沒起作用,試著刪除上拉電阻發(fā)現(xiàn)對(duì)的仿真還是這個(gè)結(jié)果,說明這上拉電阻根本沒用啊。上拉電阻難道不是這么連的嗎,而且為什么只有P1口的數(shù)碼管成功驅(qū)動(dòng)了?大神們快來幫幫我吧!

2016-06-30 11:15:11

一概而論的。但是可能存在一種情況,比如I2C的上拉電阻,他的選取范圍是比較寬的。(不考慮功耗的條件下)作者回復(fù):功耗與速度及初試化需求,一個(gè)熱情大哥的總結(jié).

2015-10-19 18:06:17

與標(biāo)準(zhǔn)值最相近的一個(gè)!P0為什么要上拉電阻原因有:1。 P0口片內(nèi)無上拉電阻2。 P0為I/O口工作狀態(tài)時(shí),上方FET被關(guān)斷,從而輸出腳浮空,因此P0用于輸出線時(shí)為開漏輸出。3。 由于片內(nèi)無上拉電阻

2018-11-30 11:55:14

上拉電阻: 1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。 2

2019-09-06 15:19:36

(低于此值為低電平);2V(高電平門限值)。 本文從選擇與設(shè)定兩個(gè)方面為大家介紹了上拉電阻的選擇,詳細(xì)在通過本文的介紹之后大家將對(duì)上拉電阻的使用與選擇技巧有更深一步的理解與認(rèn)識(shí),從而通過這些基礎(chǔ)知識(shí)的積累來逐步完善豐富自身的設(shè)計(jì)知識(shí)與經(jīng)驗(yàn)。

2016-01-20 10:39:09

I2C上拉電阻 在一些PCB的layout中,大家往往會(huì)看到在I2C通信的接口處,往往會(huì)接入一個(gè)4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對(duì)于

2022-01-14 07:22:21

斷開RESET信號(hào),用一 個(gè)延時(shí)復(fù)位計(jì)數(shù)器替代,一切0K,問題被明確下來。上拉電阻怎么選,選多少?計(jì)算不復(fù)雜,用到的是基礎(chǔ)知識(shí),首先明確TTL電平:VH=2.4V,VL=0.4。上拉電阻—般是接電源VCC的。那么被上拉的信號(hào)電壓 VI=VCC-R*I:其中R是上拉電阻, i是流過上拉電阻的電流,當(dāng)VI

2017-08-28 09:29:41

計(jì)數(shù),于是注意意到復(fù)位線,先在FPGA內(nèi)部斷開RESET信號(hào),用一 個(gè)延時(shí)復(fù)位計(jì)數(shù)器替代,一切0K,問題被明確下來。上拉電阻怎么選,選多少?計(jì)算不復(fù)雜,用到的是基礎(chǔ)知識(shí),首先明確TTL電平:VH

2017-11-16 17:16:04

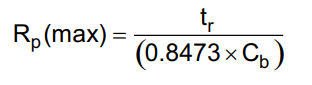

漏應(yīng)用來說,時(shí)序常數(shù)比較大會(huì)對(duì)I2C總線產(chǎn)生負(fù)面影響,從而使其串行數(shù)據(jù)線(SDA)和串行時(shí)鐘線(SCL)達(dá)到所需的波特率。從數(shù)學(xué)上講以下是計(jì)算電阻值的方法:Rp(min)為可接受的最小電阻值,由下面

2018-11-30 09:12:02

上拉就是將不確定的信號(hào)通過一個(gè)電阻鉗位在高電平,電阻同時(shí)起限流作用。下拉同理,也是將不確定的信號(hào)通過一個(gè)電阻鉗位在低電平。

2020-08-14 06:35:49

引起的功耗同樣適用于輸出拉電阻,因此拉電阻不宜太小,但在輸出信號(hào)速度比較快的電路下,拉電阻也不宜太大,如下圖所示為I2C總線上拉電阻的參考最大值(來自ST存儲(chǔ)芯片 AT24C02數(shù)據(jù)手冊(cè))。在總線上總會(huì)有

2020-08-19 09:00:00

已知上下拉電阻,怎么計(jì)算出AD值,下拉電阻是10k,上拉接NTC

2018-07-18 14:39:51

效的抑制反射波干擾。5、預(yù)設(shè)空間狀態(tài)/默認(rèn)電位在一些CMOS輸入端接上拉或下拉電阻是為了預(yù)設(shè)默認(rèn)電位。當(dāng)不用這些引腳時(shí),這些輸入端下拉接低電平或上拉接高電平。在I2C等總線上空閑時(shí)的狀態(tài)是由上下拉電阻

2019-10-11 08:30:00

開發(fā)板I2C連接到RTC(RX8010)芯片,I2C總線上沒有接上拉電阻,LS1012A手冊(cè)上說它的I2C是open drain輸出的,為什么沒有上拉電阻? 哪位能幫助解釋一下,謝謝

2022-01-05 06:28:48

及時(shí)作出回應(yīng)。2 C串行通信協(xié)議,大的時(shí)序常數(shù)會(huì)對(duì)I 2 C總線產(chǎn)生負(fù)面影響,以在其串行數(shù)據(jù)線(SDA)和串行時(shí)鐘線(SCL)線上實(shí)現(xiàn)所需的波特率。從數(shù)學(xué)上講,這是計(jì)算電阻值的方法:R p(min

2018-11-09 09:14:56

成為上拉電阻,也就是說,該端口正常時(shí)為高電平;C通過一個(gè)電阻和地連接在一起的時(shí)候,該電阻稱為下拉電阻。上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的問題的。一般說法是上拉增大電流,下拉電阻是用來吸收

2021-08-12 13:35:38

輸出高電平時(shí)是一個(gè)高阻態(tài),其上拉電流要由上拉電阻來提供,設(shè)輸入端每端口不大于100uA,設(shè)輸出口驅(qū)動(dòng)電流約500uA,標(biāo)準(zhǔn)工作電壓是5V,輸入口的高低電平門限為0.8V(低于此值為低電平);2V(高電平

2014-08-21 09:56:08

TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2、OC門電路必須加上拉電阻,才能

2011-06-02 16:03:48

電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2、OC門電路必須加上拉電阻,才能使用。3

2012-06-10 21:25:15

前言:在一張?jiān)韴D中無論時(shí)上拉還是下拉都是非常普遍的,轉(zhuǎn)載此文章,可以很快的理解上拉電阻與下拉電阻的原理與作用。如果還沒有理解,可以參考上拉與下拉的原理與應(yīng)用2者共同的作用是:避免電壓的“懸浮

2022-01-14 08:28:26

確定上拉電阻值時(shí)需要考慮哪些注意事項(xiàng)?穩(wěn)定可靠的I2C通信的設(shè)計(jì)計(jì)算公式

2021-05-25 06:35:11

狀態(tài)。防止直通!電阻在選用時(shí),選用經(jīng)過計(jì)算后與標(biāo)準(zhǔn)值最相近的一個(gè)!P0為什么要上拉電阻原因有:1。 P0口片內(nèi)無上拉電阻2。 P0為I/O口工作狀態(tài)時(shí),上方FET被關(guān)斷,從而輸出腳浮空,因此P0用于輸出

2015-06-26 14:26:17

請(qǐng)問用TMS320C5515的GPIO口模擬I2C是否需要加上拉電阻?

2018-07-31 07:48:20

為了避免出現(xiàn)任何不受控制的I/O電平,STM32F10xxx在JTAG輸入引腳內(nèi)部嵌入了上拉和下拉電阻: ●JNTRST:內(nèi)部上拉 ●JTDI:內(nèi)部上拉 ●JTMS/SWDIO:內(nèi)部上拉 ●TCK

2019-04-23 19:01:31

stm32f051的i2c需要外接上拉電阻嗎,直接用內(nèi)部上拉行不行,還有庫中的I2C_Init函數(shù)中有這么一句/* Enable I2Cx Peripheral */I2Cx->CR1 |= I2C_CR1_PE;為什么初始化有些i2c寄存器需要使能i2c。最后附上波形,希望哪位大哥幫幫忙,看看是什么問題。

2019-03-12 07:14:31

請(qǐng)問為什么有時(shí)在I2C中將SDA和SCL 上加各加個(gè)上拉電阻呢?

2023-05-08 18:01:37

請(qǐng)問用TMS320C5515的GPIO口模擬I2C總線需要接外部上拉電阻嗎?需要的話阻值為多少比較合適呢?

2019-10-28 09:37:43

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論