一、概述

??? 在許多領域中廣泛應用的嵌入式計算系統(簡稱為嵌入式系統),是在更大的電子器件中嵌入的重復完成特定功能的計算系統,它經常不被器件的使用者所識別,但在各種常用的電子器件中能夠找到這些嵌入式系統。例如,消費類電子產品中的手機、尋呼機、數字相機、攝像機、錄像機、個人數字助理等,家用電器中的微波爐、洗衣機、烤箱、門禁系統、照明系統等,商用裝置中的卡片讀入器、掃描儀、打印機等。這些嵌入式系統具有幾個共同的特性:

1.單一的功能:一個嵌入式系統通常重復地執行一個特定的程序,除非嵌入式系統的程序被新的版本更新,或者由于尺寸的限制幾個程序在一個系統中被調進或調出,但即使這些例外也表示系統具有特定的功能。

2.嚴緊的限制:所有的計算系統在設計時都有許多約束的要求,但是對嵌入式系統的約束特別嚴緊,諸如成本、尺寸、性能和功耗等設計的限制條件可以評定系統實現的特性,而嵌入式系統還有特別高的設計技術要求。

3.實時的反應:許多嵌入式系統必須連續地對系統環境的變化做出反應,并且無延誤地實時計算出確定的結果。

4.軟硬件共存:一般嵌入式系統由嵌入式處理器、系統的外圍硬件設備、嵌入式操作系統和系統應用軟件等四部分組成,是一個以微處理器為核心的數字系統,涉及到硬件和軟件兩方面的技術,嵌入式系統的微處理器可以是通用處理器或微處理器、單片機或DSP 的專用處理器、單用途處理器等。

由于設計的度量標準是對嵌入式系統實現可測量的特性,嵌入式系統的設計必須構造全部預期功能的實現,但面臨的挑戰是同時對大量設計的度量標準進行優化。

除去不可回收的工程(NRE)成本外,對設計系統的要求還包括單元成本、尺寸、性能功耗、靈活性、樣機時間、上市時間、可維護性、故障率和安全性等。

二、FPGA實現嵌入式系統的優勢

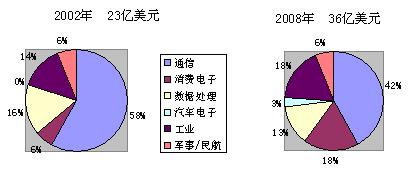

從系統對上市時間的要求、可編程的特性以及集成度等方面考慮,以可編程門陣列(FPGA)來實現可配置的嵌入式系統已越來越廣泛。圖1表示FPGA實現嵌入式系統的市場預測,估計從2002年的23億美元,將增長到2008年的63億美元。

圖1 FPGA實現嵌入式系統的市場預測

采用90納米工藝生產FPGA器件之后,FPGA器件進一步降低成本,減少功耗和提高性能,低成本使FPGA成為中小批量生產的應用器件,應用范圍從早期的軍事、通信系統等擴展到低成本消費電子類等產品。目前在實現嵌入式系統的各個領域得到廣泛的應用,并進一步帶來設計方法的變化。表1列出主要的FPGA產品在成本、功耗和性能上的改進。

表1 主要FPGA成本、功耗、性能介紹

|

結構 |

廠家 |

低成本 |

低功耗 |

高性能 |

|

S R A M 查 找 表 |

Xillinx |

EasyPath:霧任何轉換工作,與標準FPGA無本質區別,以專利測試技術用戶規定測試模式測試 |

Spantan3L:利用獨特的“冬眠模式”靜態功耗Virtex4;節能配置電路和90nm三柵極氧化層技術 |

Virtex4多平臺FPGA:用戶按需選LX SX FX Spartan3E有SPI接口MicroBiaze軟核含FPU |

|

PowerPlay可編程邏輯功率分析和優化軟件 |

NiosII嵌入式處理器內核可采用快速、標準和經濟等三種版本 |

|||

|

專注于FPGA,使可編輯器件的成本下降 |

使用基于ASIC的I/O和硬IP,降低高速功能功耗 |

LFXP系列非易失性能由片內閃存上電配置 |

||

|

多路開關反熔絲 |

ProASIC3/E:利用第三方閃存工藝技術,3萬門FPGA<1.5美元低價 |

ProASIC3:基于閃存技術器件本身具有低功耗特性 |

新系列將提供32位ARMTMThumb系列微處理器軟內核 |

|

|

ESP:芯片內由ViaLink金屬線技術固化通用IP,又留可編程邏輯的空間,由用戶自有開發 |

Eclipsell超低功耗系列:待機功耗14μA |

QL58xO系列QuickPCI產品具有低功耗、高性能、上電即用,符合PCI2.3標準 |

三、基于模型的設計方法

當今許多高集成度的嵌入硬件和軟件系統具有靈活的信號處理和通信。這些系統中硅密度和算法復雜性有驚人的增長,引起設計和校驗成本的上升。

嵌入系統的市場預測發現,大于50%的嵌入系統項目不能按時完成,1/3的項目僅達到50%的性能而失敗。

即使采用新的校驗技術或在傳統設計工具和流程中擴展語言也不足以改善開發進程,這些增量的改進不能消除傳統流程的問題:如模糊的基于文本的技術要求,人工的實現和后期的測試,這些問題都會產生擴充的錯誤并危及產品的交貨時間。

與傳統設計流程對比,采用Simulink的基于模塊的設計技術在開發時間、成本和風險等方面有驚人的改善。在應用實時信號處理、通信和控制邏輯的航天、汽車、通訊和半導體工業已經有大量文獻資料證明這些好處和優點。

基于模型的設計技術由以下四部分組成:

1.來自模型的可執行技術條件

由Simulink模塊集中的模塊作為系統和部件行為的可執行技術要求,代替了傳統設計流程中模糊的文本文件。

這些模塊可以覆蓋數字和模擬的硬件及軟件,它們便于在工程隊伍之間清晰“無模糊”地交流和通信。

2.帶有仿真的設計

Simulink是一個為多領域動態系統仿真的平臺,它提供交互的圖形化方框圖環境,帶有為信號處理、通訊和控制等可定制的模塊庫集合,也可以產生綜合性系統技術條件、模型通道和其它的環境效應。這些工具簡化了利用定量測量的系統分析,如信/噪比和位誤差率等。

Simulnk模塊是層次化的,可以很容易把它們分成子系統或元件,同時還可以定義所有為實現軟一件和硬件需要的全部信息,利用仿真來證明由模型定義的可執行技術條件是完全的和正確工作的。

3.由自動代碼生成進行實現

設計一旦被認為已經完善和通過校驗,就可以自動地從模型產生代碼,消除手工編碼的要求和人工編碼引入的錯誤。在實現設計的目標系統中可以利用這個代碼作為實時的樣機和推廣應用。

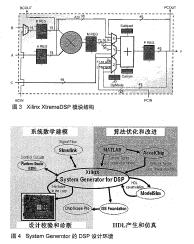

安裝在Simulink中的Xilinx/AI-tera的System Generator/DSP Builder可以對Xilinx/Altera的FPGA自動產生硬件代碼的能力。

4.持續的測試和校驗

可以確保整個開發過程的質量,集成化的測試在任何級的模型中進行,覆蓋模型的定量測試。持續的校驗和仿真可以及早發現錯誤,由于是及時發現,修正錯誤代價就得到降低。系統模型或稱為“golden reference”可看作硬件或軟件實現的測試床,可以在協同仿真的軟件或硬件環路中驗證。

四、FPGA DSP 嵌入式系統

為什么利用FPGA來實現DSP系統,概括地說,因為FPGA是極高并行度的信號處理引擎,能夠滿足算法復雜度不斷增加的應用要求,通過并行方式提供極高性能的信號處理能力。Xilinx的XtrerneDSP模塊,如圖3所示,使得Virtex4/Sparten3系列廠PGA可以為高性能的數字信號處理提供理想的解決方案,達到傳統上由ASIC或ASSP完成的高性能信號處理能力。可以針對數字通信和視頻圖象處理等應用開發高性能的DSP引擎,也可在可編程DSP系統中作為預處理器或協處理器等。Vir-tex4 SX系列中DSP48模塊最多達到512個,工作頻率達到500MHz,成為算術密集應用的理想器件。

DSP48模塊是一個18×18位二進制補碼乘法器,跟隨一個48位符號擴展的加法器/減法器/累加器,適應DSP應用中的眾多的功能。提高了操作數輸入、中間積和累加器輸出的可編程流水線操作,以及48位內部總線等的吞吐量和適應性,無需一般的結構布線就可以實現前一個DSP48的輸出與后一個DSP48輸入的級聯,增強了它的功能。

在復雜算法的數字處理系統中,系統要求的不斷提高和集成規模的不斷擴大,使得系統結構在設計的開始階段是不明確的,不可能直接用RTL(寄存器轉移級)設計方法進行描述,所以將系統集成到數字芯片中。

采用數字技術對復雜算法進行硬件實現時,首先遇到的向題是在結構上并沒有預先的規定,因此需要首先對算法建模和仿真進行優化。與基于RTL針對結構清晰的設計方法不同,算法設計把焦點從針對結構的細節轉移到對設計的整體要求和行為,在最高的算法層次上考慮如何進行設計,對系統的行為描述定義了設計要執行的算法,不涉及或很少涉及實現細節,因此行為描述比RTL描述要簡潔的多。

Xilinx公司與MathWork和TI公司等許多技術上世界領先的公司合作,在設計技術上提供許多基于模型的系統設計新方法。

圖4所示的DSP設計環境可以進行系統的數學建模,算法優化和改進,設計校驗和診斷,以及日DL產生和仿真等。涉及Xilinx的ISE硬件實現工具和嵌入系統開發包EDK,以及片內邏輯分析工具(CChipScope Pro)等。第三方的工具包括MATLAB/SimuLink和ModeISim等,可以進行HDL協同仿真和硬件在環路的協同仿真等,一旦設計優化完成和仿真通過,可以直接利用IP核的網表文件進行硬件實現,設計的效率和可靠性大大提高。

DSP48可以高效地實現許多基本的算術功能,包括加法器、減法器、累加器、乘法累加、乘法多路復用、計數器、除法器、平方根函數和桶式移位器等。

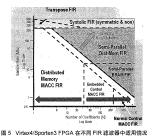

圖5表示在Virtex4/Sparten3 FPGA在高性能DSP應用中,各種不同FIR濾波器技術的適用情況,FIR濾波器的算法為:

公式中n個系數與n個相應的數據采樣相乘,再對內積求和產生單個結果。系數數值將確定濾波器的低通/高通/帶通特性,可以利用不同的架構和不同的方法來實現濾波器的功能。在利用器件內雙端口塊RAM實現輸入數據的緩存時,讀地址端口的時鐘速度要比輸入采樣數據寫入速度快n倍。乘法累加(MAC)的FIR濾波器最高的輸入采樣率將受到與系數個數有關的抽頭數影響,對單一的結構降為時鐘頻率的1/n倍。圖5中在對數坐標的情況下,隨系數數目增加,采樣率的變化呈直線下降。FPGA中可以利用眾多的嵌入乘法器或DSP48模塊實現完全并行的FIR濾波器,以增加硬件資源來換取使輸入數據采樣率達到系統的時鐘頻率。由于FPGA具有非常靈活的“液體硬件”性質,可以在其上實現各種結構的濾波器,圖5表示了按照不同的結構和參數選擇濾波器實現技術的原則。

五、FPGA嵌入微處理器系統

Xilinx FPGA的Virtex4和Virtexll -Pro系列嵌入7IBM PowerPC405的RISC微處理器硬核,而Virtex和Spanten II之后的所有系列都可以嵌入MicroBlaze軟核。

嵌入的PPC405硬核和MicroBlaze軟核都是32位的哈佛結構微處理器。

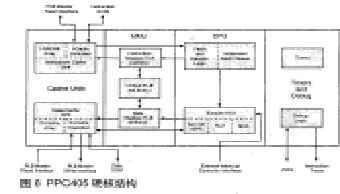

PPC405硬核包括cache單元、存儲器管理單元(MMU)、指令獲取譯碼單元、執行單元、定時器和診斷邏輯單元等,如圖6所示。指令的操作包括獲取、譯碼、執行、寫回和加載回寫五級流水組成。包括加載和存儲等大多數指令都是一個時鐘周期內執行。

PPC405處理器模塊是與CoreConnect總線結構相兼容的,包括Xilinx IP軟核在內的任何CoreConnect兼容核都可以通過這個高性能總線結構與處理器模塊集成。CoreConnect結構提供處理器局部總線(PLB)、片內外設總線(OPB)和器件控制寄存器(DCR)總線,利用這三個總線來互聯處理器模塊、Xilinx I戶軟核、第三方IP核和定制的邏輯。高性能外設連接到高帶寬低滯后的PCB總線,較慢速的外設連接到OPB總線,可以減少PLB總線的流量,提高整個系統性能。圖7給出PPC405和MicroBlaze的總線例子。

FPGA嵌入微處理器可以有三種不同的使用模式:

1.狀態機模式:可以無外設、無總線結構和無實時操作系統,達到最低的成本,應用于VGA和LCD控制等,達到可高或可低的性能。

2.單片機模式:包括一定的外設,可以利用實時操作系統和總線結構,以中等的成本,應用于控制和儀表,達到中等的性能。

3.定制嵌入模式:高度集成擴充的外設,實時操作系統和總線結構,達到高性能,應用于網絡和無線通信等。

隨著FPGA的成本不斷降低,FPGA實現嵌入式系統達到片上系統(SOC)的特性和可編程的要求具有明顯的優越性,市場潛力很大。

電子發燒友App

電子發燒友App

評論