??? 關鍵詞:嵌入式系統,MPC850,硬件開發平臺

1 MPC850簡介

Motorola公司的MPC850通信控制器芯片基于PowerPC內核,以精簡指令集計算RISC的體系結構為基礎,集成了32位微處理器和多種外設接口,具有強大的通信和網絡協議處理能力,可廣泛應用于各種通信和網絡產品,如ADSL modem、SOHO路由器、低速ISDN、T1/E1終端、ATM線卡控制、局端交換、無線接入等。

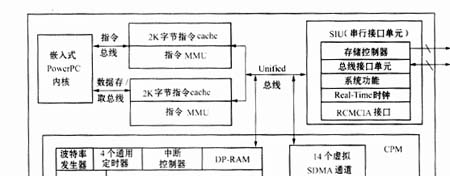

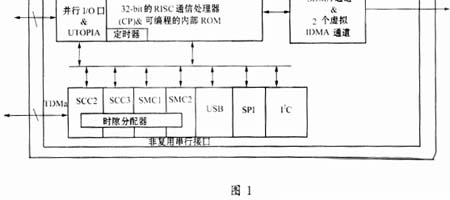

MPC850的功能結構主要包括:嵌入式PowerPC內核,系統接口單元(System InterfaceUnit,SIU)和通信處理器模塊(Communications Processor Module,CPM)。其體系結構的框圖如圖1所示。

從圖中可以看出,通信處理器模塊CPM支持7個串行信道,包括:2個串行通信控制器SCC,2個串行管理控制器SMC,1個USB接口,1個I2C和1個串行外設接口SPI。因此,MPC850通過靈活的編程方式可實現對Ethernet、USB、T1/E1等的支持,以及對IEEE802.3/Ethern-et、UART(同步/異步)、HDLC、Transparent、App-leTalk、IrDA等多種通信模式/協議的支持。

另外,MPC850還具有增強型在片仿真調試功能,功能齊全的接口單元,可進行優先級編程的中斷控制等特征。本系統正是基于MPC850的這些特點來進行通信開發平臺的硬件設計的。

2 系統硬件總體設計

設計MPC850多功能通信開發平臺的底層,在硬件方面需要提供全面的通信接口、足夠的內存容量、調試功能以及測試顯示功能。根據設計,本系統主要由CPU、存儲器、通信接口、調試以及測試顯示等幾部分組成。

CPU部分的設計包括了系統的硬件啟動與復位、MPC850總線信號分配與定義等。存儲器部分包括SDRAM、FLASH ROM和E2PROM。通信接口部分提供了2個Ethernet接口、2個RS232接口、1個RS485接口、1個USB接口、ISDN用戶開發板接口以及ATM UTOPIA接口。另外,還提供了MPC850 BDM調試口以及測試口、LED顯示等。

3 系統的硬件啟動與復位

MPC850的復位方式包括:上電復位、外部/內部Hard Reset、外部/內部Soft Reset、調試口的Hard Reset等。這些方式都由Reset控制器處理。本系統采用了上電復位和外部Hard Reset的方式。

上電復位的過程由芯片內部完成,MPC850需要確認

MPC850在從數據總線上采樣硬件復位配置字信息的過程中,

4 存儲器設計

MPC850中存儲器管理器負責控制管理GPCM和UPMs兩種存儲器控制機制,針對不同的存儲器提供靈活的時序支持和無縫連接。其中,GPCM提供了一種簡單的、不支持突發方式的低層次的存儲器資源和內存映射接口,因此,GPCM控制的內存槽主要用于系統的啟動和不支持突發方式的數據存取。而UPM方式支持突發方式,同時包括外部總線的地址復用、周期定時以及DRAM器件可編程的行列地址選通信號的產生,因此,UPM多用于支持高性能的實時存儲器。

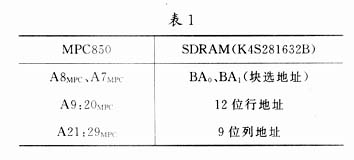

在本系統的存儲器設計中,采用了1片Intel公司的FLASH ROM 28F320J5,2片SAMSUNG公司的SDRAM K4S281632B。其中,BANK0用于FLASH ROM,對應于

FLASH ROM的容量設計為32Mbit,用來存放實時操作系統和用戶應用程序。對BYTE#(ByteEnable)管腳的設置,可以使28F320J5工作在×8或×16模式。

SDRAM的讀寫以及突發模式的時序控制通過對MPC850

MPC850

5 各種通信接口的硬件設計

CPM通過以下途徑減少core的計算任務,包括:減少中斷產生率;執行一些OSI第2層處理;支持多緩存存儲器數據結構等。

在CPM功能基礎上,外圍通信電路只需提供物理層收發器和驅動器。在本系統的設計中,Ethernet收發器采用Intel Level One公司的LXT905,RS232與RS485收發器分別采用MAXIM公司的MAX232與MAX488,USB收發器采用Philips公司的PDIUSBP11A。其中,2個Ethernet收發器分別使用與MPC850的SCC2、SCC3兩個串行通信控制器接口,2個RS232收發器分別使用與MPC850的SMC1、SMC2兩個串行管理控制器接口,RS485復用了SMC2接口,USB收發器使用與MPC850的USB接口。

由于LXT905本身提供了與MPC850的無縫接口能力,于是通過RJ45實現與外界的通信主要集中在協議的實現和數據收發的控制上。其數據接口信號包括:

·RCLK與TCLK:接收與發送時鐘信號。由LXT905提供,連接到MPC850的時鐘信號CLKx。

????? ·RXD與TXD:接收與發送數據信號。由MPC850提供,連接到LXT905的RXD與TXD。

·TEN:發送使能信號,同時啟動LXT905看門狗定時器。

·CD:載波監聽信號,監聽LAN是否正在使用。

·COL:沖突監測信號,驅動控制器的沖突監測輸入。

??? 本系統設計的ISDN端口總線使用了MPC850串行接口TDMa和SPI接口,用戶可以在此基礎上設計開發自己的ISDN接入系統。其中,SPI接口提供了SPII/O數據信號SPIMOSI與SPIMISO、SPI時鐘信號SPICLK、SPI從設備選擇信號;TDMa接口提供的信號包括收發數據、時鐘、同步等。

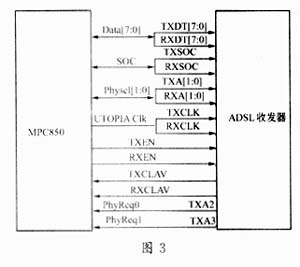

MPC850的ATM控制器支持兩種接口模式:UTOPIA接口和串行ATM接口。本系統以支持ADSL收發器為目的,采用了目前ADSL收發器通常使用的ATM UTOPIA LEVEL1/LEVEL2接口。這種接口允許不同速率和性能的傳輸媒質以一種統一的物理層接口到ATM子系統中,并且有利于向支持多用戶的ADSL局端設備擴展。

一個UTOPIA接口包括收發數據端口、控制信號和地址信號。UTOPIALEVEL1和LEVEL2主要在地址信號的定義上有所不同。其中LEVEL1未定義地址信號,主要針對single-PHY的情況;LEVEL2針對multi-PHY的情況,比LEVEL1多了兩組地址信號。MPC850的UTOPIA接口支持LEVEL 1標準,加上外部控制邏輯即可實現LEVEL2的multi-PHY接口(最多支持4個物理層設備),因此,本系統的設計實現了兼容UTOPIALEVEL1/LEVEL2的接口電路,如圖3所示。關于調試與測試部分的敘述這里從略。

MPC850的多功能通信開發平臺在底層設計的基礎上,選擇相應的嵌入式操作系統,再進行相關驅動程序和上層應用程序的開發,通過所需接口與用戶各自的開發系統相連,最終可設計實現各種通信與網絡產品。

參考文獻

2 Wayne Wolf.嵌入式計算機系統設計原理.北京:機械工業出版社,2002,2

電子發燒友App

電子發燒友App

評論