針對嵌入式系統的低功耗要求,采用位線分割結構和存儲陣列分塊譯碼結構,完成了64 kb低功耗SRAM模塊的設計。 與一般布局的存儲器相比,采用這兩種技術使存儲器的功耗降低了43% ,而面積僅增加了18%。??

關鍵詞:存儲器;SRAM;位線分割;分塊譯碼

????????嵌入式存儲器的容量及其在系統芯片中所占的面積越來越大,對其操作所帶來的動態功耗成為系統芯片功耗中重要的組成部分,因此,必須尋求有效的低功耗設計技術,以降低嵌入式存儲器對整個系統的影響。為了降低存儲器的功耗,人們采用了字線分割、分級字線譯碼以及字線脈沖產生等技術,大大降低了存儲器的動態功耗。 另外一種能有效降低存儲器動態功耗的技術就是位線分割(DBL)。 針對系統要求,筆者采用DBL結構以及一種存儲陣列分塊譯碼結構,完成了64 kb嵌入式存儲器模塊的設計。?

????????參數的修正與公式的重新推導?

????????DBL結構的原理

?

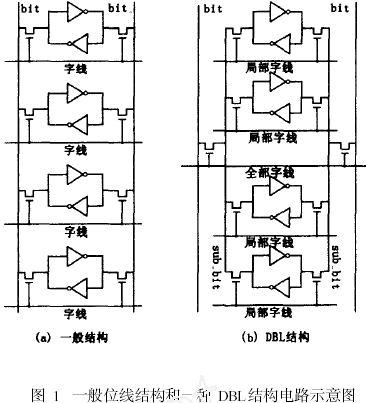

????????DBL結構就是通過將兩個或者多個SRAM存儲單元進行合并,以減少連接到位線上的晶體管數目,從而減小位線電容,達到降低存儲器動態功耗的目的。 圖1w給出了將4個SRAM單元連接在一起并通過傳輸管連接到位線上的電路示意圖。 與一般布局的位線結構相比,圖1w所示的DBL結構中連接到位線上的傳輸管數目減少了3 /4。?

????????DBL結構有兩個關鍵:第1,確定存儲陣列行數N 與合并的單元個數M 之間的最優關系。 所謂最優是指合并后存儲器的動態功耗最小。 對于這個關系,文獻[ 1 ]中給出了相應的公式:

pnor = (1 /M + 0.1) + 2 ×( (M + 1) / (N (ΔV /V ) ) ) , (1)

Mop t = ( (N /2) ×(ΔV /V ) ) 1 /2 , (2)

式中ΔV 表示位線上電壓的擺幅, V 表示電源電壓。第2,確定合并后各個管子的寬長比。下面,針對這兩個問題進行討論。  ?

?

????????DBL功耗公式的修正?

????????公式(1) , ( 2)是在下述假設下得出的:在SRAM中,位線的電容主要是由存儲單元中傳輸晶體管的漏極電容和位線的金屬連線電容構成,并且金屬線的寄生電容是與位線相連管子漏極總電容C的10% ,則圖2中寄生電容C1 和C2 可表示為

C1 = C M /N , C2 = C /M + 0.1C 。

????????然而,上述假設并沒有真正反映位線電容的構成,因為位線電容的組成包括存儲單元中傳輸晶體管的源/漏電容CBS ,位線間的耦合電容CBB ,位線與橫向字線之間的耦合電容CWW ,位線與地線的耦合電容CBSS ,位線與電源線的耦合電容CBDD ,位線的金屬連線電容CW 等。 隨著深亞微米技術的發展,在位線總電容中,傳輸晶體管的源/ 漏電容CBS 所占的比例只有60% ~ 70% ,其他的電容分量共占30% ~40%,在這種情況下公式設計電路會帶來較大的誤差。 另外,對C1 的舍入過大,由此也引入了很大的誤差,必須進行修正。 筆者對公式的重新推導如下。?

????????假設存儲陣列的行數為N, DBL 結構中合并的存儲單元數為M,一般布局結構(N 行) 中, 與位線相連的所有傳輸管漏極的總電容為C,并假定位線上其他的寄生電容是此漏極總電容的30% , 則圖2中電容C1 和C2 可表示為

C1 = C (1.3M + 1) /N , C2 = (C /M ) + 0.3C 。?

????????假設讀寫操作時子位線不進行預充電,并且其電壓值能夠達到電源電壓,用ΔV 表示位線上電壓的擺幅,那么,圖2中DBL存儲器的動態功耗可表示為?

????????p =f (M ) = (C2 ×ΔV ×V + 2 ×C1 ×V2 ) ×f = [ (C /M + 0.3 ×C) ×ΔV ×V + 2 ×C ( (1.3M + 1) /N ) ×V2 ] ×f (3)?

????????根據標準存儲單元的功耗表達式pstan = (C ×ΔV ×V ) ×f , (4)?

????????對式(3) 歸一化得pnor = (1 /M + 0.3) + 2 ×( (1.3M + 1) / (N ×ΔV /V ) ) , (5)?

????????因此可求得功耗最小時的M 值Mop t = ( (N /2. 6) ×(ΔV /V ) ) 1 /2 。 (6)

如果存儲陣列的行數N = 1 024,位線電壓變化率ΔV /V = 011,則Mop t ≈ 6, pnor ≈ 0164。 但是如果按照公式(1) , (2) 計算,則Mop t ≈ 8, pnor ≈ 0140,后面的設計均基于修正后的公式(5) , (6)。?

????????管子寬長比的選擇?

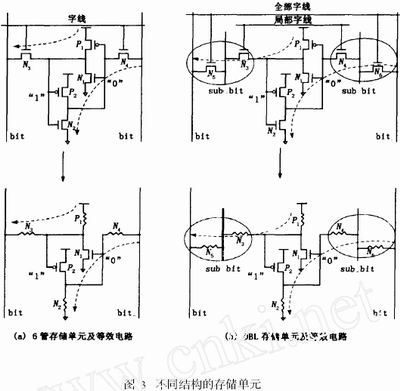

????????在6管存儲單元中,為了完成正常的讀寫操作,各個管子的寬長比必須滿足一定的約束條件,這種約束條件通常用上拉比PR 和單元比CR 來刻畫。 對于圖3@ 所示的存儲單元,有CR = (WN 2 / LN 2 ) / (WN 4 /LN 4 ) PR = (WP1 / LP1 ) / (WN 3 /LN 3 ) 。 為了完成正常的讀出操作,不發生“讀翻轉”,要求CR 大于1.8 (VDD = 3.3V, Vt = 0.5V) [ 7 ] ,因此N2 比 N4 有更好的導通性。 為了完成正常的寫入操作, 要求PR 小于1 (VDD = 3.3V, Vtp = 0.5V 和μP /?μN =0.5) ,也就是說, N3 應該比P1 有更好的導通性。 在DBL結構中,如果存儲單元中各個管子的W /L 與 一般結構中的相同,顯然,由于N4 和N6 (N3 和N5 ) 的串聯等效關系,使得CR 的條件更容易滿足,而PR 的條件更不容易滿足,從而使寫入操作變得更加困難。 因此, 為了完成正常的讀寫操作, 應合理確定管子N4 和N6 (N3 和N5 ) 的寬長比。N4 和N6 寬長比的選擇,可以通過將N4 和N6 (N3 和N5 ) 近似成串聯電阻來估算,如圖3w 所示。 為了方便分析,假設N4 和N6 的結構相同。 顯然,為了保持原先存儲單元正常的讀寫功能,應該將N4 和N6 的寬長比都加倍,而其他管子的寬長比保持不變。

????????分塊譯碼的DBL 結構?

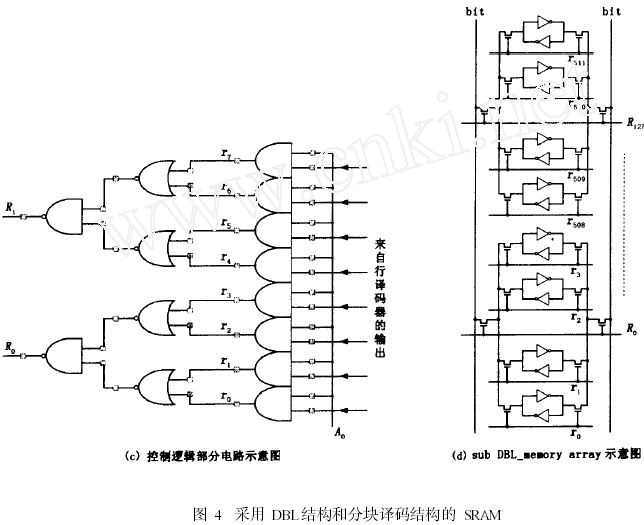

????????通過前面的分析可以看出,對于位線很長的存儲陣列,通過采用DBL技術,選取合理的M 值,動態功耗會有所減小。 然而,以上的分析并沒有考慮不同尺寸的管子以及不同的版圖布局風格等因素的影響。 另外,在DBL結構中,由于還附加了其他的控制邏輯電路,其本身也有功耗,因此,實際功耗并不能完全按照公式(5)計算。為了進一步降低存儲器的功耗,筆者在DBL結構的基礎上,設計了存儲陣列的分塊譯碼結構。首先,為了使版圖形狀滿足要求,將64kb SRAM劃分成8個8kb的子陣列,并利用地址信號A1 , A2 , A3 譯碼后對8個8kb子陣列進行選擇。 這不僅滿足了版圖的布局要求,也降低了存儲器的功耗,整個布局如圖4v所示。分塊譯碼的DBL結構主要是針對每個8kb的存儲子陣列設計的,如圖4w所示,每個8kb的子陣列由左右兩個存儲陣列模塊構成。 其工作原理為:利用列地址線A0 和A0 控制行譯碼器的輸出,使得在任何讀寫周期,左右兩個存儲陣列只有一個被選中,這樣整個64kb的SRAM就有1 /16子陣列處于活動狀態,從而減小了由于字線充放電引起的動態功耗。?

????????圖4w中,控制邏輯的具體結構如圖4x 所示,子陣列sub DBLàmemroy arrayi ( i = 0~7)的結構如圖4y所示,每個子陣列有512行,即N =512,根據公式(6) ,合并后的存儲單元數M =4

?

????????按照分塊譯碼的DBL結構,采用chartered 0.35μm雙層多晶三層鋁布線的n阱CMOS工藝,完成了嵌入式64kb SRAM模塊的設計,版圖面積1。 4mm ×4. 7mm (一般結構的版圖面積1.3mm ×4. 3mm)。 Starsim仿真結果表明,采用分塊譯碼DBL結構的存儲器的平均電流約為37mA,一般結構存儲器的平均電流約為65mA。?

????????結束語?

????????以上討論了嵌入式64kb SRAM的低功耗設計,通過采用DBL結構以及存儲陣列分塊譯碼結構,使得存儲器的功耗降低了43%,而面積僅增加了18%。 仿真結果表明兩者的最小訪問周期都約為15 ns。 因此,根據A T2 P (A 是面積, T是訪問周期, P是功耗)來衡量,這種低功耗設計方法是可行的。隨著嵌入式存儲器容量的加大以及深亞微米技術的發展,亞閾值漏電流所造成的靜態功耗已經不可忽略,尋求有效的低功耗設計技術仍然是值得探討的課題。

基于DBL結構的嵌入式64kb SRAM的低功耗設計

- sram(113778)

相關推薦

32位嵌入式處理器的市場

嵌入式系統以各種類型的嵌入式處理器為核心,而隨著技術的發展,對于嵌入式處理器的性能及功耗的要求愈加嚴苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩定

2019-07-19 08:29:10

低功耗嵌入式系統該怎么設計?

嵌入式系統的應用隨著各種智能控制系統、智能玩具、工業控制、掌上設備(Portable)等的需求而不斷擴大和流行。特別是近幾年來,隨著手機、PDA、MP3等掌上系統的流行,使得系統功耗成為產品

2019-09-02 07:55:40

低功耗小尺寸的存儲解決方案選擇SPI SRAM

而產生的總體效果,早在1965年,摩爾定律就預測了電路越來越小的趨勢,但是這個趨勢并不是發生在所有類型的產品電路中,例如,邏輯電路比SRAM的電路變小了很多倍,所以新產生的問題是嵌入式SRAM開始占據

2017-12-04 11:04:58

嵌入式低功耗電源管理框架的設計資料分享

概述目標本篇的目標是介紹低功耗電源管理框架設計的概念理解低功耗管理的重要性理解如何開發適合的低功耗管理框架理解如何去管理產品的功耗形勢大多數的嵌入式產品非常注重低功耗設計,尤其近年來,硬件不斷

2021-12-21 07:39:29

嵌入式FPGA的相關資料下載

不需要的部分裁去(可裁剪)。所以嵌入式系統一般都具有便攜、低功耗、性能單一等特性。嵌入式FPGA(eFPGA)是指將一個或多個FPGA以IP的形式嵌入ASIC,ASSP或SoC等芯片中。換句話說,eF...

2021-10-28 07:32:48

嵌入式外圍設備有哪些?

選擇填空判斷嵌入式系統的定義和特點定義:以應用為中心,計算機技術為基礎,軟硬件高度定制,適用于對功能、能耗、成本、體積、可靠性有嚴格要求的專用計算機系統特點:專用性可靠性實時性低功耗可裁剪嵌入式系統

2021-10-27 08:43:52

嵌入式技術基礎知識

應用設計的專用計算機系統; 3, 使用低功耗的X86級別的CPU,采用模塊化的設計,配置了最基本的計算機周邊配備而制成。這種計算機通常采用Windows操作系統; 4、 嵌入式系統的軟件包

2019-07-03 06:09:15

嵌入式是如何定義的

不需要的部分裁去。所以嵌入式系統一般都具有便攜、低功耗、性能單一等特性。然后,MCU、DSP、FPGA這些都屬于嵌入式系統的范疇,是為了實現某一目的而使用的工具。MCU俗稱”單片機“經過這么多年的發展

2021-07-13 08:48:28

嵌入式的定義是什么

不需要的部分裁去。所以嵌入式系統一般都具有便攜、低功耗、性能單一等特性。然后,MCU、DSP、FPGA這些都屬于嵌入式系統的范疇,是為了實現某一目的而使用的工具。MCU俗稱”單片機“經過這么多年的發展,早已不單單只有普林斯頓結構的51了,性能也已得到了很大的提升。因為MCU必須順序執行程序,所以適...

2021-07-13 07:06:51

嵌入式的那些事兒

嵌入式系統。典型代表:智能手機、工業機器人、汽車電子、航空航天(四軸飛行器)、安防監控(IPC)等。嵌入式系統的技術特點低功耗(BLE、zigbee、低功耗Wifi)聯網化(4G、BT、zigbee

2017-02-22 13:38:36

嵌入式系統中的低功耗設計

隨著手機、智能穿戴、醫療電子等新興產品的興起,嵌入式系統的設計也成為各位軟硬件工程師越來越關心的話題。 在嵌入式系統設計中,Low Power Design(低功耗設計)是許多設計人員必須面對

2014-01-21 11:22:57

嵌入式系統和嵌入式電腦有什么區別?

,586,486,386等!其中又分低功耗和常規兩類!相對來說,低功耗CPU的產品價格高一些,可以無風扇工作!這些指標都是根據產品的實際應用來選擇的。同時X86架構的嵌入式板卡基本可以等同于普通

2020-06-23 11:02:33

嵌入式系統如何降低功耗

山東科技大學 張煒韓進引 言隨著嵌入式系統應用的迅速發展,PDA和移動電話等便攜式裝置深入到生產生活的各個角落,嵌入式系統市場有迅速增長趨勢。嵌入式系統一般是由電池來供給電能的,而且大多數嵌入式設備

2019-07-19 06:17:21

嵌入式系統有什么特性

不需要的部分裁去。所以嵌入式系統一般都具有便攜、低功耗、性能單一等特性。然后,MCU、DSP、FPGA這些都屬于嵌入式系統的范疇,是為了實現某一目的而使用的工具。MCU俗稱”單片機“經過這么多年的發展

2021-07-13 08:36:01

嵌入式系統有何特性

不需要的部分裁去。所以嵌入式系統一般都具有便攜、低功耗、性能單一等特性。然后,MCU、DSP、FPGA這些都屬于嵌入式系統的范疇,是為了實現某一目的而使用的工具。MCU經過這么多年的發展,早已不單單只有普

2021-11-03 06:07:16

嵌入式系統有哪些特性

系統是個專用系統,結構精簡,在硬件和軟件上都只保留需要的部分,而將不需要的部分裁去(可裁剪)。所以嵌入式系統一般都具有便攜、低功耗、性能單一等特性。然后,MCU、DSP、FPGA這些都屬于嵌入式系...

2021-07-13 09:22:44

嵌入式系統概論與嵌入式系統的特點

嵌入式系統概論嵌入式系統的特點:專用性:與具體應用緊密結合,具有很強的專用性隱蔽性:嵌入式系統是被包裝在內部資源受限:要求小型化、輕型化、低功耗及低成本,因此軟硬件資源受到限制高可靠性:任何誤動作

2021-12-21 08:21:23

嵌入式系統降低功耗介紹

山東科技大學 張煒韓進引 言 隨著嵌入式系統應用的迅速發展,PDA和移動電話等便攜式裝置深入到生產生活的各個角落,嵌入式系統市場有迅速增長趨勢。嵌入式系統一般是由電池來供給電能的,而且大多數嵌入式

2019-07-19 06:30:26

嵌入式計算機系統怎么降低功耗?

綠色環保節能是全球化的熱潮,而嵌入式計算機系統被廣泛應用于便攜式和移動性較強的產品,低功耗設計不僅是綠色環保的要求,也是嵌入式計算機系統體積和質量的約束。隨著市場對嵌入式計算機系統在體積和性能方面

2020-03-31 07:39:43

ASR6601的相關資料推薦

Arm Cortex M4架構的32位MCU。多種內存選擇包括最大256KB的閃存和64KB的SRAM等,內置嵌入式LCD驅動程序,支持AES、DES、RSA、ECC、SHA、SM2/3/4硬件加密

2021-12-10 07:02:42

CMS32L051 64KB Flash,主頻64MHz

:1.8V-5.5V> 工作溫度:-40℃ - 105℃> 64KB Flash> 8KB SRAM> 1.5KB Data Flash> 多達45個GPIOs> 靈活配置的系統

2023-03-11 16:39:42

CW32L031產品介紹

CW32L031是一款基于eFlash的單芯片低功耗微控制器,集成了ARM?Cortex?-M0+

核心,主頻高達48MHz,高速嵌入式存儲器(高達64KB的FLASH和

高達8K字節的SRAM

2023-09-14 06:02:27

PHY6252超低功耗物聯網藍牙無線通信芯片

PHY6252是一款超低功耗物聯網藍牙無線通信芯片,搭載 32 位 ,配備 64KSRAM/Retention SRAM,512KFLASH,96KROM/256bit efuse;具有超低功耗

2022-04-14 14:14:31

PSOC3中的64KB代碼大小限制

在PSoC3中有一個限制:代碼地址空間被限制到64KB,另一方面,我們可以看到外部存儲器的存取空間達到8MB。我的問題是:有沒有辦法克服代碼空間的限制,比如說256KB? 以上來自于百度翻譯 以下

2019-04-02 15:17:41

STM32L5超低功耗微控制器

微控制器是要求更高安全性和更低功耗的嵌入式應用的答案。它使用一流的超低功耗技術,通過ArmCortex-M33及其TrustZone和ST安全實施方案提高了安全性。STM32L5提供最大512KB的閃存

2020-06-30 16:51:34

STM32不同的封裝

包括64KB到256KB閃存和 20KB到64KB嵌入式SRAM。新系列采用LQFP64、LQFP100和LFBGA100三種封裝,不同的封裝保持引腳排列一致性,結合STM32平臺的設計理念,開發人員通過

2021-08-06 06:01:47

STM32系列有哪些基本型式

、USB基本型系列、互補型系列;沿用增強型系列的72兆赫茲處理頻率。內存包括64KB到256KB閃存和 20KB到64KB嵌入式SRAM。采用LQFP64、LQFP100和LFBGA100三種封裝

2021-08-02 07:35:11

STM32芯片是如何進行命名的

意法半導體已經推出STM32基本型系列、增強型系列、USB基本型系列、增強型系列;新系列產品沿用增強型系列的72MHz處理頻率。內存包括64KB到256KB閃存和 20KB到64KB嵌入式SRAM。新系列采用LQFP64、LQFP100和LFBGA100三種封裝,不同的封裝保持引腳排列一...

2022-01-26 06:39:20

TMS320F28034的FLASH是64kb為什么讀出的數據是128kb,請教

我用西爾特6100的編程器讀出的數據是128kb,但芯片手冊上FLASH是64kb,想請教一下,是怎么回事

2021-08-27 12:55:43

stm32ad7606 spi串行

基本型系列、互補型系列;新系列產品沿用增強型系列的72MHz處理頻率。內存包括64KB到256KB閃存和 20KB到64KB嵌入式SRAM。新系列采用LQFP64、LQFP100和LFBGA100三種封裝,不同的封裝保持引腳排列一致性,...

2021-08-05 07:03:12

一種符合ITU-T指標要求的嵌入式立體聲語音頻編碼方法

Transform,MLT)編碼技術對輸入信號的中值與邊帶信息進行分層編碼,形成具有嵌入式結構的碼流.編碼器可處理寬帶和超寬帶的立體聲信號,寬帶立體聲信號編碼的最大碼率為48kb/s,超寬帶立體聲

2011-03-09 20:25:23

中微BAT32G135 /基于 ARM? Cortex?-M0+的超低功耗 32 位微控制器

系列MCU是中微基于ARM-Cortex M0+ 推出的超低功耗系列MCU,主頻64MHz,工作電壓2.0V-5.5V,64KB Flash,8KB SRAM,1.5KB Data Flash ,多達

2021-09-18 12:05:04

中微代理BAT32G135系列 高功能低功耗血氧議

系列MCU是中微基于ARM-Cortex M0+ 推出的超低功耗系列MCU,主頻64MHz,工作電壓2.0V-5.5V,64KB Flash,8KB SRAM,1.5KB Data Flash ,多達

2022-01-04 15:11:00

中微原廠代理BAT32G179高性能低功耗 智能門鎖、無線監控設備、BMS電池管理、智能電器等…領域

?-M0+的超低功耗32位微控制器,主頻最高支持64MHz,512KB Flash、20KB專用數據Flash存儲器、64KB SRAM存儲器,多達93個GPIO,支持比較器,ADC,RTC,LCD

2022-02-16 12:03:29

中微愛芯AiP32L1032/64 32KB/64KB Flash ROM 32位 低功耗 20pin MCU

不變。這顆芯片優點在哪呢?1:有低電壓、低功耗、低待機電流、高集成度外設、高效率操作、快速喚醒及高性價比等優勢2:具有較高的溫控標準,-40-105℃3:24MHz,內置32K/64K字節的嵌入式

2023-01-11 15:46:05

什么是嵌入式主板

什么是嵌入式主板? 嵌入式主板在設備里面做控制、數據處理使用的CPU板,一般會對主板的體積以及功耗有較高的要求。所以一般來講嵌入式主板會具備 尺寸小、高集成度、低功耗等特性! 嵌入式主板分類

2021-12-16 08:06:41

什么是嵌入式系統低功耗設計?

經過近幾年的快速發展,嵌入式系統(EmbeddedSystem)已經成為電子信息產業中最具增長力的一個分支。隨著手機、PDA,GPS、機頂盒等新興產品的大量應用,嵌入式系統的市場正在以每年30%的速度遞增(IDC預測),嵌入式系統的設計也成為軟硬件工程師越來越關心的話題。

2019-10-29 06:38:46

什么是嵌入式系統面向低功耗的協同設計系統?

對于當今的各種電子設備尤其是嵌入式系統來說,功耗是一個非常重要的問題。系統部件產生的熱量和功耗成比例,為解決散熱問題而采取的冷卻措施進一步增加了整個系統的功耗。為了得到最好的結果,在設計初級階段就要盡可能地考慮低功耗問題。

2019-09-19 06:18:34

什么是嵌入式軟件

的自控軟件等等。嵌入式系統因其低成本、體積小、低功耗、穩定性和實時性強等特點將會越來越被人們所應用。什么是嵌入式測試?依托于質量保證,安全可靠的軟件產品會給我們帶來無窮的便利,同樣如果產品質量一般甚...

2021-10-28 08:45:05

你怎么看8位、16位、32位及64位嵌入式處理器?

嵌入式系統以各種類型的嵌入式處理器為核心,而隨著技術的發展,對于嵌入式處理器的性能及功耗的要求愈加嚴苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩定

2019-07-05 07:52:22

國產大容量單片機CV060 64kb存儲空間

/64K 字節的嵌入式 Flash,4K 字節 的 SRAM,集成了 12 位 1Msps 高精度 SAR 型 ADC、RTC、比較器、多路 UART、SPI、I2C和 PWM 等豐富的外設接口,具有

2022-08-04 12:27:14

國產超低功耗 BAT32G135GE48FA M0+內核 主頻64MHz 高性能MCU 替代CMS32F030C8T6

BAT32G135系列MCU是中微基于ARM-Cortex M0+ 推出的超低功耗系列MCU,主頻64MHz,工作電壓2.0V-5.5V,64KB Flash,8KB SRAM,1.5KB Data

2022-08-18 11:38:16

在嵌入式Linux平臺下的功耗管理技術

產品的設計瓶頸,嵌入式功耗管理技術成為解決這一問題的有效手段.本文基于自主設計的嵌入式低功耗硬件平臺,通過系統休眠和系統運行兩方面重點探討了在嵌入式Linux平臺下的功耗管理技術.本文首先介紹和分析了Li...

2021-11-05 08:01:11

基于嵌入式 ARM 處理器的BLE SoC 一個典型示例

,包括一個 ARM Cortex-M0 處理器、低功耗藍牙無線電、8 Mb 閃存、64 kB OTP ROM、128 kB 數據 SRAM、128 kB ROM、片上電源管理和其他一些外設(圖 4)。 圖

2018-07-12 09:46:20

基于嵌入式DSP系統的低功耗優化設計

節省的空間可以用來增加能夠提高系統性能的組件,尤其是設計小組希望添加一個以上處理器時,這一點非常重要。設計嵌入式DSP處理器或系統功耗要求嚴格的系統時,采用DSP專用技術、操作系統及其支持軟件可以降低功耗

2016-08-20 11:26:46

基于FPGA的嵌入式塊SRAM該怎么設計?

對于邏輯芯片的嵌入存儲器來說,嵌入式SRAM是最常用的一種,其典型的應用包括片上緩沖器、高速緩沖存儲器、寄存器堆等。除非用到某些特殊的結構,標準的六管單元(6T)SRAM對于邏輯工藝有著很好的兼容性。對于小于2Mb存儲器的應用,嵌入式SRAM可能有更好的成本效率并通常首先考慮。

2019-08-28 08:18:27

如何開發基于OSEK/VDX平臺的汽車嵌入式系統?

嵌入式系統是以應用為中心,以計算機技術為基礎,適用于對功能、可靠性、成本、體積、功耗、實時性等有嚴格要求的場合。眾所周知嵌入式系統有體積小、低功耗、集成度高、子系統間能通信融合的優點,這就決定了它非常適合應用于汽車工業領域。

2019-11-01 08:02:40

如何設計低功耗嵌入式系統

設計低能耗系統時,我們需要關注一些非傳統因素,這些因素涉及范圍從硅芯片生產工藝技術,到基于單片機的嵌入式平臺上所運行的軟件。通過對系統層面的深入分析,本文討論決定 MCU 能效的三個關鍵參數:工作

2019-11-11 20:07:23

尺寸小低功耗外置SRAM首選SPI SRAM

而產生的總體效果,早在1965年,摩爾定律就預測了電路越來越小的趨勢,但是這個趨勢并不是發生在所有類型的產品電路中,例如,邏輯電路比SRAM的電路變小了很多倍,所以新產生的問題是嵌入式SRAM開始占據

2017-10-19 10:51:42

怎么才能在嵌入式設計中降低CPLD的功耗?

從事便攜式或手持產品設計的工程師都明白對于如今的設計,最大限度地降低功耗是必不可少的要求。但是,只有經驗豐富的工程師理解盡可能地延長系統的電池壽命的那些微妙但又重要的細節。本文中我們的重點是,如何使用超低功耗的復雜可編程邏輯器件(CPLD)?如何在嵌入式設計中降低CPLD的功耗?

2019-08-01 08:19:42

怎么降低嵌入式芯片的功耗?

從當前嵌入式消費電子產品來看,媒體處理與無線通信、3D游戲逐漸融合,其強大的功能帶來了芯片處理能力的增加,在復雜的移動應用環境中,功耗正在大幅度增加。比如手機,用戶往往希望待機時間、聽音樂時間,以及看MPEG4時間能更長。在這樣的背景下,如何降低嵌入式芯片的功耗已迫在眉睫。

2019-09-18 06:22:27

意法STM32 L0系列Cortex-M0+超低功耗MCU簡介及相關資料!

的USB、超低功耗模式中的短喚醒時間及低功耗模式下仍可工作的通信外設,實現了集成特性、高性能與超低能耗之間的完美平衡。STM32 L0微控制器具有高達64KB閃存、8 KB RAM及高達2 KB的嵌入式

2020-09-03 15:37:49

汽車嵌入式系統的發展如何?

嵌入式系統是泛計算領域的重要組成部分,是嵌入式對象宿主體系中完成某種特定功能的專用計算機系統。嵌入式系統有體積小、低功耗、集成度高、子系統間能通信融合的優點。隨著汽車技術的發展以及微處理器技術

2019-08-02 07:35:56

設計超低功耗的嵌入式應用

考慮到我們今天所生活的時代,嵌入式系統的便攜性是十分關鍵的設計考慮因素。便攜式系統通常用電池供電,而電池使用壽命取決于系統的功耗。在提倡“綠色環保”計劃的今天,即便是市電供電的應用也要把功耗作為一項

2016-07-29 15:25:00

請問有什么方法可以量化嵌入式器件的實際功耗?

各類內置嵌入式處理器的電子產品的功耗目前已經成為系統設計領域的前沿問題。那么有什么方法可以量化嵌入式器件的實際功耗呢?

2021-04-15 06:34:14

超低功耗嵌入式的隱患怎么消除?

目前,工程師的任務之一是開發基于低成本微控制器 (MCU) 的超低功耗嵌入式應用,此類應用通常要求用一顆電池維持數年的工作。在從家用自動調溫器到個人醫療設備等此類超低功耗應用中,設計人員必須仔細考慮

2020-03-09 08:32:38

超低功耗藍牙芯片

ROM

138KB/64KB SRAM 睡眠模式下所有數據保存

33/19通用V/0引腳

支持PGA的8通道12位ADC

4通道24位時鐘,1個監視時鐘

實時計數器(RTC)

供電電壓范圍

2023-06-27 17:30:17

基于嵌入式系統的低功耗設計

本文研究了針對嵌入式系統的低功耗設計,通過采用動態改變系統運行頻率的方法,降低系統中的微處理器功耗,并且針對算法對系統性能的影響進行了研究,并給出了實驗結果,證

2009-05-25 11:35:22 11

11

11

11DS1986,pdf datasheet (64Kb Add

The DS1986 64Kb Add-Only iButton is a rugged read/write data carrier that identifies and stores

2009-09-18 09:07:23 31

31

31

31基于μCOS-II嵌入式系統的低功耗開發

基于μCOS-II嵌入式系統的低功耗開發

隨著嵌入式系統應用的日益廣泛,如何實現嵌入式系統的低功耗開發已經成為嵌入式應用發展的關鍵技術之一,是近幾年來人們在

2009-12-23 11:06:54 682

682

682

682

基于FPGA的嵌入式塊SRAM的設計

嵌入式SRAM 是最常用的一種,其典型的應用包括片上緩沖器、高速緩沖存儲器、寄存器堆等。除非用到某些特殊的結構,標準的六管單元(6T)SRAM 對于邏輯工藝有著很好的兼容性。

2011-03-04 09:58:16 2011

2011

2011

2011

嵌入式系統設計中的低功耗技術

為了探討嵌入式系統的低功耗技術降低嵌入式系統的功率消耗, 文中從硬件和軟件兩個方面對嵌入式系統設計的低功耗問題進行了分析和研究。

2011-10-12 15:31:40 1172

1172

1172

1172嵌入式系統的組成及其低功耗的設計

,對嵌入式系統的低功耗問題進行了 分析,并對嵌入式系統的硬件設計以及軟件設計提出了一些切實有效的措施,有利于更好的解決嵌入式系統的功耗問題。 嵌入式系統主要包括軟件設計以及硬件設計。為了降低功耗,就需要對這中設計

2017-12-06 14:09:43 9

9

9

9英特爾推出了一款全新的64位低功耗嵌入式處理器

Intel推出了一款全新的64位低功耗四核處理器——Atom x5-E8000。這款芯片并不是面向消費級PC或是筆記本、平板等設備研制,而是專門針對物聯網和其他嵌入式應用場景打造。

2019-09-24 14:31:44 1980

1980

1980

1980關于STM32單片機的介紹

、USB基本型系列、互補型系列;沿用增強型系列的72兆赫茲處理頻率。內存包括64KB到256KB閃存和 20KB到64KB嵌入式SRAM。采用LQFP64、LQFP100和LFBGA100三種封裝

2021-03-31 15:10:37 5177

5177

5177

5177

使用PLCC封裝中通用64kb OTP Eprom替換C64系統PLA功能

電子發燒友網站提供《使用PLCC封裝中通用64kb OTP Eprom替換C64系統PLA功能.zip》資料免費下載

2022-07-28 10:57:37 3

3

3

3DS13293_多協議 LPWAN 雙核 32 位 Arm? Cortex?-M4/M0+ LoRa?、(G)FSK、(G)MSK、BPSK、高達 256KB 閃存、64KB SRAM

DS13293_多協議 LPWAN 雙核 32 位 Arm? Cortex?-M4/M0+ LoRa?、(G)FSK、(G)MSK、BPSK、高達 256KB 閃存、64KB SRAM

2022-11-23 08:29:00 0

0

0

0DS10287_超低功耗 32 位 MCU 基于 Arm? 的 Cortex?-M3、256KB 閃存、32KB SRAM、8KB EEPROM、LCD、USB、ADC、DAC、AES

DS10287_超低功耗 32 位 MCU 基于 Arm? 的 Cortex?-M3、256KB 閃存、32KB SRAM、8KB EEPROM、LCD、USB、ADC、DAC、AES

2022-11-23 08:32:02 2

2

2

2DS10262_超低功耗 32 位 MCU 基于 Arm? 的 Cortex?-M3、256KB 閃存、32KB SRAM、8KB EEPROM、LCD、USB、ADC、DAC

DS10262_超低功耗 32 位 MCU 基于 Arm? 的 Cortex?-M3、256KB 閃存、32KB SRAM、8KB EEPROM、LCD、USB、ADC、DAC

2022-11-23 08:32:09 0

0

0

0DS8669_超低功耗 32 位 MCU Arm? Cortex?-M3、384KB 閃存、48KB SRAM、12KB EEPROM、LCD、USB、ADC、存儲器 I/F、AES

DS8669_超低功耗 32 位 MCU Arm? Cortex?-M3、384KB 閃存、48KB SRAM、12KB EEPROM、LCD、USB、ADC、存儲器 I/F、AES

2022-11-23 08:32:23 0

0

0

0DS13105_多協議 LPWAN 32 位 Arm? Cortex?-M4 MCU、LoRa?、(G)FSK、(G)MSK、BPSK、高達 256KB 閃存、64KB SRAM

DS13105_多協議 LPWAN 32 位 Arm? Cortex?-M4 MCU、LoRa?、(G)FSK、(G)MSK、BPSK、高達 256KB 閃存、64KB SRAM

2022-11-23 20:26:53 0

0

0

0靈動微低功耗單片機MM32L0136C6P可替換STM32L053C8

ST超低功耗STM32L053C8微控制器采用高性能Arm?Cortex?-M0+32位RISC內核、頻率32MHZ,高速嵌入式存儲器(高達64KB的閃存程序存儲器、2KB的數據EEPROM和8KB

2022-12-08 16:08:29 347

347

347

347AiP32L1032/64 32KB/64KB Flash ROM 的低功耗 M0+核微控制器

AiP32L1032/64系列具有低電壓、低功耗、低待機電流、高集成度外設、高效率操作、快速喚醒及高性價比等優勢,可廣泛適用與工業控制、消費電子設備、可穿戴設備等應用。

2023-01-11 17:14:33 1

1

1

1PT32L00x32KB/64KB Flash ROM 的低功耗

PT32L00x系列使用高性能低功耗的CortexM-M032位內核工作頻率48Mhz內置高速存儲器(高達32K字節的Flash和最大2K字節的SRAM),多功能復用的增強I/O端口和連接到APB

2023-02-17 17:03:52 0

0

0

0列拓科技推出高性能、低功耗微控制器芯片LTM32F103ZET6

Card外部存儲器。LTM32F103ZET6芯片支持多種省電模式,使其能夠滿足各種低功耗應用的要求,其內部框架圖如下: LTM32F103ZET6芯片主要特性: ARM 32位Cortex-M3內核 512KB閃存、64KB SRAM高

2023-06-26 14:12:19 798

798

798

798

電子發燒友App

電子發燒友App

評論