基于cPCI總線的嵌入式遙測前端處理器系統設計

遙測數據處理系統在航空、航天等軍工試驗領域有著廣泛的應用。在航空飛行試驗中.遙測數據處理系統為各類試飛測試數據的實時處理提供了手段和平臺,試飛員、試飛指揮員及試飛工程師協同完成新機試飛必不可少的重要設施,是確保現代飛機試飛安全、提高試飛效率、縮短試飛周期、實現綜合試飛的重要手段。

遙測數據處理系統中的核心設備——遙測前端處理器,技術上經歷了從分立式、智能式到嵌入式的快速發展。我遙測前端處理器的研發經歷了從引進、合作研制到完全自行研制的歷程。

遙測前端處理器是一套嵌入式實時計算機系統,承擔著遙測PCM數據的同步、分路、工程單位轉換、數據計算、數據分配等實時處理任務。它和遙測系統管理服務器、工作站等設備通過網絡聯接和系統集成,組成當前流行的基于C/S結構的遙測數據處理系統。可以說,遙測前端處理器的技術水平代表了遙測數據處理系統的技術水平。

1? 系統功能和主要技術指標

遙測前端處理器的功能簡單地說,就是把來自遙測接收設備送來的多路串行PCM(Pulse Code Modulation)數據流進行同步、分路、合并、存儲,并對轉換后的并行數據進行工程單位轉換、導出數計算等實時處理,通過網絡把數據傳送給顯示工作站。再通過遙測記錄數據重放,為用戶提供同實時方式一樣的處理功能和更為詳細的數據分析功能。

遙測前端處理器主要技術指標為:

(1)可同時完成2路PCM數據流的同步和分路,每路PCM速率不大于20Mbps。

(2)實時數據處理速率:20Mbps。

(3)數據傳輸:交換式以太網、網絡帶寬1000Mbps、廣播方式和“點對點”方式。

(4)數據存儲:滿足在最大速率下數據存儲不丟失,磁盤容量滿足不小于4小時的記錄時間。

2 系統組成和體系結構設計

二十世紀90年代,因受當時的計算機技術限制,國內外大多數嵌入式遙測前端處理器都采用了基于VME總線的計算機平臺和雙總線、多CPU、百兆以太網接口的體系結構,其技術復雜、成本高、軟件開發難度大、系統研制周期。

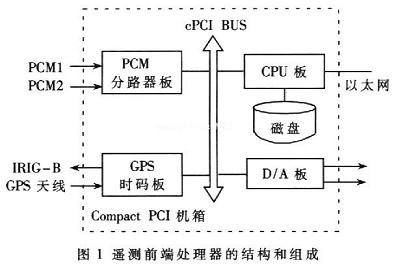

當前計算機技術的發展,使得CPU速度和總線速率已不再是新一代嵌入式遙測前端處理器的瓶頸,基于單CPU、單總線和千兆以太網接口的體系結構成為新一代嵌入式遙測前端處理器的主流設計。板卡化后的遙測前端設備,如碼同步器、分路器、時碼發生器等作為計算機的一個插件板,嵌到工業計算機系統中,其組成已簡化為:19英寸計算機箱、CPU板、多功能PCM分路器板、時碼板、D/A板和存儲設備,其典型結構與組成見圖1所示。新一代嵌入式遙測前端處理器體系結構簡化,性能和可靠性提高,成本降低,研制周期縮短,更容易集成為基于C/S結構的多數據流遙測數據處理系統。

3 硬件設計

3.1 總線平臺和OEM板卡的選擇

計算機總線平臺是嵌入式遙測前端處理器的關鍵,當前國外嵌入式遙測前端處理器均選用了目前流行的Compact PCI計算機總線平臺。該平臺吸收了PC機商用技術的最新成果,數據傳輸速率滿足新一代嵌入式遙測前端處理器實時處理多條PCM數據流時的傳輸要求,環境條件、可靠性等都滿足運輸類飛機機載、地面活動車載等環境使用要求。

遙測前端處理器中的其他硬件,除PCM分路器板外,均選用了OEM產品。機箱選用12槽Compact PCI機箱(包括電源組件和磁盤);根據處理要求,本設計的CPU板選用了美國SBS公司的C7系列,CPU PⅢ1GHz,RAM 1GB,2個1000Mb以太網口,1個SCSI口。時碼板選用了美國DATUM公司帶GPS授時的BC637;D/A板選用了美國NI公司的N16713系列,每板8通道.每通道lMSps,D/A分辨率為12位.

考慮到單片式全數字碼同步器在國外已有使用,因此在多功能雙PCM分路器板設計時已預留了單片碼同步器的芯片位置。本設計碼同步器選用外置式碼同步器。

3.2 多功能雙PCM分路器板的設計與實現

PCM分路器板是嵌入式遙測前端處理器的關鍵插件,國外也有不少單板、單PCM分路的OEM產品。但高端產品的購置受到西方國家諸多限制,因此,選取了自行設計的技術途經,研制成功了基于Compact PCI總線的多功能雙路。PCM分路器板,其技術水平達到當前國際先進水平。

3.2.1 PCM分路器板的硬件邏輯設計

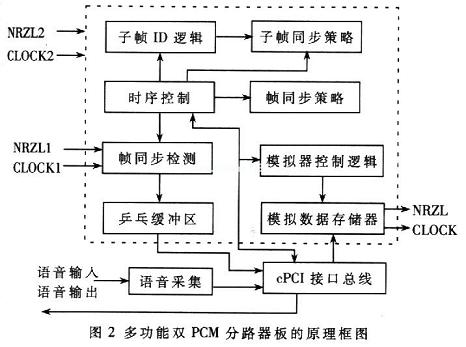

多功能雙PCM分路器的原理框圖如圖2所示,由雙PCM分路器(包括幀同步檢測、幀/子幀同步策略及相應的時序控制邏輯等)、PCM模擬器、語音采集等功能模塊組成。主要功能均由大規模集成電路CPLD可編程邏輯芯片實現。

CPLD選用了Latfice公司的ISP 4512V系統在線可編程器件。由于ISP便于現場更改,降低了研發成本,縮短了系統調試時間。

在眾多通用的PCI接口芯片中,選用了目前業界設計選用的主流芯片:PLX公司的PLX9054。PLX9054是一種功能強、使用靈活并符合PCIV2.2規范的32位、33MHz的。PCI總線接口控制器,它可以作為PCI總線的主控設備去控制總線,也可以作為目標設備去響應總線。PIX9054提供了PCI總線、EWROM、IDCAL總線3個接口,作為一種“橋”芯片,在PCI總線和LOCAL總線之間有3種直接的數據傳輸模式。本設計選用了DMA數據傳輸模式。PLX9054以其強大的功能和簡單的用戶接口,為PCI總線接口的開發提供了一種簡潔的方法,設計者只需設計本地總線接口控制電路,即可實現與PCI總線的高速數據傳輸。

3.2.2 幀、子幀同步及同步策略的實現

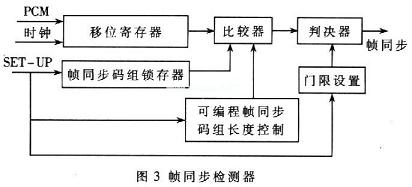

PCM數據一個參數是以一個字或多個字的方式表達的,每個字由若干碼元組成,而在一個PCM采集系統中,所有測試參數組成一個參數群,該參數群稱為幀/子幀結構。怎樣才能準確地區分每個字的起始位置.正確地恢復采集參數的并行數據,也就是獲取幀/子幀以及表示各參數的數據字的起始時刻相一致的脈沖序列,其過程即稱為幀/子幀同步。幀,子幀同步信號的作用在于在一串信號群中,給出一個起始時間標志,以便對每個參數字進行正確地分路,其特點是:它本身的信息量不大,但對傳輸的可靠性要求很高。幀同步檢測器是PCM分路器板的關鍵部分,其他工作都是在幀同步檢測器完成正確的檢測后進行的,因此,幀同步檢測器起著至關重要的作用。其框圖如圖3所示。

按照數據采集方案的格式要求,預先由處理器進行初始化設置,包括幀同步碼組、同步碼組的長度和允許同步碼組的錯誤位數。隨著時間的推移,PCM數據在CLDCK信號的控制下,逐位進入移位寄存器,移位寄存器的輸出數據進入比較器,隨時與幀同步碼組進行比較,在同步碼組長度邏輯的控制下,一旦檢測到可能的同步碼組,則比較器輸出同步信號,該同步信號還必須由判決器來進行判決才能決定其是否有效。其方法是:預先設置允許的錯誤容限也就是允許的錯誤位數,然后根據比較器的輸出信號是否滿足錯誤容限的要求來決定真正的同步信號的輸出。幀同步信號的產生為整個PCM分路器板提供了最基本、最重要的時序依據。

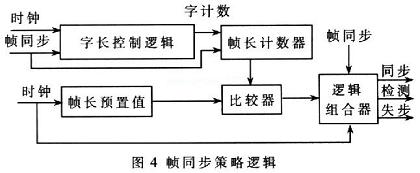

幀同步策略是PCM分路的關鍵技術之一,其意義在于最大限度地解決數據傳輸過程中造成的“漏同步”和“假同步”現象,以降低誤碼率,進一步提高數據檢測的可靠性和有效性。一種基本的且經實踐檢驗行之有效的幀同步策略是:在幀同步檢測完成后,按照PCM格式定義的PCM字長和幀長,連續找到幾個(一般為3個)相匹配的同步碼組后,即認為幀確為同步。

幀同步策略的邏輯實現如圖4所示。由圖4可以看出,幀同步的正確性可以依據以下條件:

(1)同步碼組的正確性。

(2)幀長的正確性(通過幀長計數器與幀長預置值的比較實現)。

(3)同步、檢測和失步的判別。不同的設計者可采用不同的方法,目的是消除假同步和漏同步的影響。可以采取以下方法:若比較器連續出現3個相等值時同步,當有一個不等值時,進入檢測狀態;而當出現連續3個不等值或檢測一定時間后不能同步時,則進入失步狀態。

以上解決了幀同步的問題,也就是找到了每一幀的起止位置。然而,每一幀的各數據字在特定的測試方案中又不可能相同,如何來確定某個參數字在哪一幀的哪個位置?幀同步以后,數據傳輸的正確位置是否可靠?就是子幀同步要解決的問題。多年來,國內外廣泛采用的于幀同步方式為ID同步方式。

子幀同步策略是PCM分路的另一關鍵技術,其意義在于:在幀同步的基礎上,對數據的可靠性作進一步的容錯檢測。一種常用的且經實踐檢驗較為可靠的子幀同步策略是:連續檢查幾個子幀數據(一般為3個),其子幀同一位置的ID字如果相同或相鄰子幀相應的ID字連續,則判決為子幀同步,否則子幀不同步。

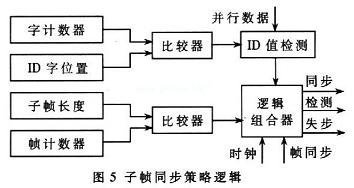

子幀同步策略邏輯實現如圖5所示。由圖5可以看出,子幀同步與策略的正確性依據以下條件:

(1)ID字位置及其值的正確性(如過零檢測)。

(2)子幀長的正確性(通過子幀長與幀計數器值的比較判斷)。

(3)同步、檢測和失步的判別,方法與幀同步策略類似。

在本設計中,雙PCM幀同步檢測、幀/子幀同步策略均通過CPLD邏輯器件實現,不僅提高了設計的集成度,而且提高了系統的可靠性及其性能,使每路PCM分路速率達到20Mbps的國際先進水平。

4 軟件平臺選擇及軟件組成

目前常用的遙測前端處理器操作系統有Windows2000和VxWorks二種。Windows2000通用、軟件資源豐富、易于使用和擴展;而VxWorks是一個用途廣泛的實時操作系統,具有良好的實時性、可靠性和可裁減性。根據遙測數據處理的實際需求,本設計選用了Windows2000,程序設計語言選用C++。

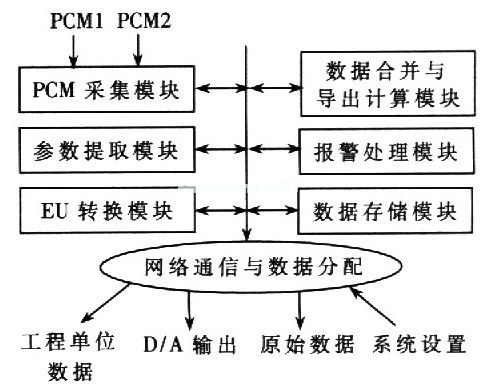

遙測前端處理器軟件組成與實時數據處理流程框圖如圖6所示。

圖6? 遙測前端處理器軟件組成與實際工資時數據處理流程

遙測前端處理器中的軟件由PCM數據采集、參數提取、工程單位轉換、數據合并與導參數計算、報警參數處理、數據存儲、網絡通信與數據分配等模塊組成。其中,采集、參數提取、工程單位轉換模塊與數據流相對應,每個數據流單獨一套。PCM數據經采集后,接事先定義對參數進行提取、工程單位轉換和必要的處理、存儲。按事先設置,需要模擬輸出的數據直接由D/A板輸出,通過網絡把工程單位數據和原始數據傳輸給工作站,由工作站完成遙測數據的各種方式的可視化顯示和飛行試驗專用數據分析與處理。

基于cPCI總線的新一代嵌入式遙測前端處理器的設計和實現,使遙測數據處理系統的集成更加容易。其20Mbps的速率、雙路PCM數據的分路和實時處理能力。可滿足現代軍、民機飛行試驗遙測數據處理要求。它的應用使我國的飛行試驗遙測數據處理技術水平得到很大的提升。同時,cPCI總線的加固特性,使以嵌人式遙測前端處理器為核心而組成的實時遙測數據處理系統,滿足了運輸類飛機機載要求和地面車載環境要求,拓寬了遙測前端處理器在軍工試驗和民用工業試驗等領域內的應用范圍,有著廣闊的應用前景。

電子發燒友App

電子發燒友App

評論