threadx系統介紹

ThreadX是優秀的硬實時操作系統(RTOS),適用于深嵌入式應用中,具有規模小、實時性強、可靠性高、無產品版權費、易于使用等特點,并且支持大量的處理器和SoC,包括ARM、PowerPC、SH 4、MIPS、ADI DSP、TI DPS、Nios II等,因此廣泛應用于消費電子、汽車電子、工業自動化、網絡解決方案、軍事與航空航天等領域中。 ThreadX RTOS和中間件支持Tensilica最新產品Diamond Standard 106Micro 32位微控制器IP核。

ThreadX RTOS支持全線Tensilica Xtensa可配置處理器IP核以及Diamond標準系列處理器IP核產品。新添加106Micro延續ThreadX 對全部Tensilica處理器系列支持。 ThreadX是Express Logic針對高要求實時應用小面積速度快免版稅的RTOS。免版稅的業務模式令ThreadX對于高容量器件來說極具吸引力。ThreadX的簡單易用也使帶ThreadX的器件既能按時面市又不超預算,這些都是ThreadX在市場上成功并被大量使用的原因所在。

ThreadX已被廣泛的用戶接納,并且目前在超過4億5千萬電子產品中得到廣泛應用。ThreadX配有Express LogicTCP/IP協議棧NetX、文件系統FileX、USB協議棧USBX以及GUI開發包PEGX,所有這些都支持Tensilica最新的Diamond Standard 106Micro產品。 低功耗Diamond Standard 106Micro是針對SoC(片上系統)設計中簡單控制器應用而設計,為那些將產品從8位/16位控制器移植到32位處理器上的設計工程師理想選擇。所有鉆石標準系列處理器都擁有優化鉆石系列軟件工具支持和廣泛產業基礎架構合作伙伴,這些合作伙伴將提供操作系統、設計服務、硬件原型和模擬仿真、庫和存儲器、EDA工具和外設等支持。

Tensilica為其鉆石標準系列處理器IP核提供了一個已經通過驗證的基礎架構,該架構包括由Tensilica直接提供軟件開發工具,以及由Bytetools公司、FS2公司、Macraigor Systems公司和Sophia Systems公司提供的JTAG探針支持、由ARM(Artisan)公司和Virage Logic公司提供的存儲器和庫、由Cadence公司、CoWare公司、Magma公司和Synopsys公司提供的流行的EDA工具支持和CoWare公司的CoWare Platform Architect上Diamond 106Micro模型。

threadx系統源碼分享

用來處理初始化過程中的匯編語言,它是面向處理器和開發工具的。

Void_tx_initialize_low_level{

1、CPSCR|= FIQ_ MODE,SET SP_fiq;

2、CPSCR|=IRQ_MODE,SET SP_irp;

3、CPSCR|=SVC_MODE,SET SP_svc;

4、設置中斷向量表IRQ_TABLE;

5、設置內部TIMER線程的堆棧起始地址,堆棧大小和優先級::tx_timer_stack_start,_tx_timer_stack_size,_tx_timer_priorit;

6、設置初始化后未使用內存地址的初始值_tx_initialize_unused_memory; }

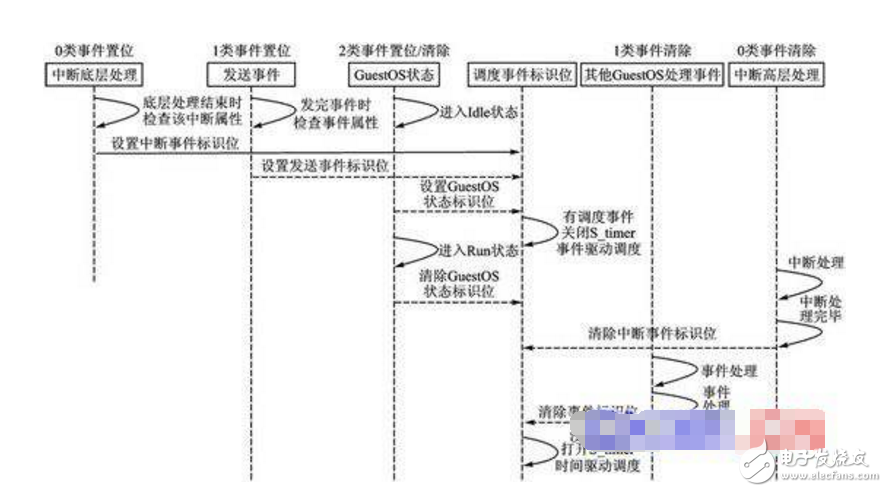

Tx_tcs.s負責在中斷發生時對上次的運行現場進行保存,它保存中斷上下文,為了不覆蓋R14_irq離得中斷返回地址,TCS的返回是通過跳到__tx_irq_processing_return地址做到的。Tx_TCR.S負責中斷處理程序執行完后的處理。

Void _tx_thread_context_save{

1、把表示中斷嵌套個數的變量_tx_thread_system_state++;

2、if _tx_thread_system_state》1,PUSH R0-R3,CPSR,R14 in IRQ stack,B __tx_irq_processing_return;

3、else if _tx_thread_current_ptr=0判斷是否有線程正在運行,if not ,B _tx_irq_processing_return;

4、else,PUSH Context_irq in thread’s stack,SP_thread=new SP,B _tx_irq_processing_return; }

由于R13和R14在不同的CPU模式下對應的是不同的物理寄存器,所以若要得到中斷前的線程堆棧指針,需要先返回到該線程的運行模式,同時禁止中斷,取值后再返回到終端模式。R14_irq保存的是終端發生時PC值+8,R14_svc保存得失中斷前線程自己的返回地址。所以在中段上下文中,(R14_irq-4)應該存在中斷地址,而R14_svc存在R14的位置。

Void _tx_thread_context_restore{

1、_tx_thread_system_state--,if _tx_thread_system_state》0,POP R0-R3,CPSR,R14 from IRQ stack,BX R14;

2、else if _tx_thread_current_ptr=0?if =0 CPSR|=VC_MODE,CPSR|=TX_INT_ENABLE,跳到線程調度程序B _tx_thread_schedule;

3、if!=0,則判斷線程搶占是否禁止if _tx_thread_preempt_disable=0?if!=0,POP Context_irq from thread’s stack,BX R14;

4、if=0,_tx_timer_time_slice=newvalue,_tx_thread_current_ptr=0,CPSR|=SVC_MODE,設置堆棧指針為系統指針SP=SP_svc,CPSR|=TX_INT_ENABLE;

5、B _tx_thread_schedule;}

Tx_tsr.s用于從線程退回到系統態,負責保存線程的最小語境并退回到Threadx的調度循環狀態。它保存的上下文是請求上下文。

Void _tx_thread_system_return{

1、 PUSH Context_request:in thread’s stack,CPSR|=TX_INT_DISABLE;

2、 _tx_thread_current_ptr-》SP=SP,CPSR|=SVC_MODE;

3、 設置堆棧指針為系統指針SP=SP_svc,_tx_thread_current_ptr=0,CPSR|=TX_INT_ENABLE;

4、 B _tx_thread_schedule;}

由于用戶模式不能直接更改CPSR來關斷的,所以要通過SWI指令進入特權模式,而且特權模式和用戶模式的SP對應不同的物理寄存器,所以要在轉入系統模式取得用戶模式下SP,最后再回到特權模式。 TX_TS.S負責調度和恢復就緒的優先級最高的線程的最后語境。

Void _tx_thread_schedule{

1、 while(_tx_thread_execute_ptr=0);

2、 CPSR|=TX_INT_DISABLE,_tx_threadx_current_ptr=_tx返回值;}

移植該函數時,針對不同的處理器,應蓋根據準熱愛寄存器CPSR的中斷禁止未來設置開關中斷向量,主要修改TX_PORT.H中的TX_INT_ENABLE和TX_INT_DISABLE.R0用來傳遞的參數和結果。

Tx_tsb.s負責創建每個線程的初始堆棧結構,這個初始的結構

在線程創建時會引起中斷上下文返回到_tx_thread_shell_entry函數的開頭。然后這個函數調用指定線程入口函數。其中斷類型設置為1,表示中斷上下文。

Void _tx_thread_stack_build(TXTHREAD *thread_ptr,void(*function)(void)){

1、 保證堆棧起始地址八字節對齊;

2、 中斷地址存入線程調用的入口地址PUSH function_ptr;

3、 R0-R12,R14的初始值都設置為0,PUSH初始值;

4、 要存入堆棧的CPSR值設置為用戶模式,開中斷,標志位清零,R1=USER_MODE,PUSH R1;

5、 Thread_ptr-》sp=new SP; }

當處理一個低級的中斷時,tx_tpc.s決定是否發生搶占,它是可選的,大多數端口都用不到。TX_TIMIN.S負責處理定時中斷。這兩個函數只要將它們翻譯成相應ARM匯編語言就可以了。

電子發燒友App

電子發燒友App

評論