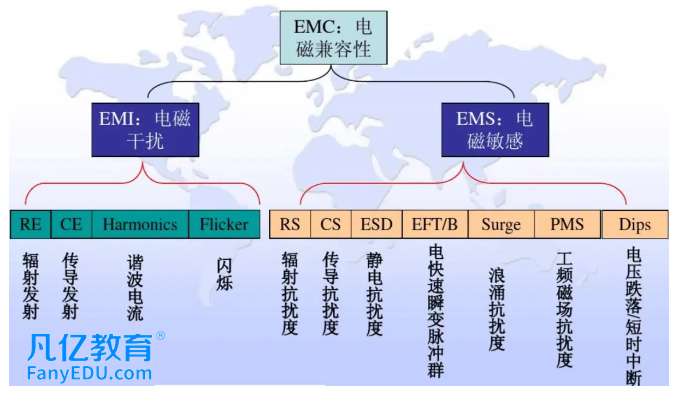

下面列舉出四項很重要卻常常被忽略的EMC設計指南。 設計指南1 設計指南1:最小化高頻信號和電源環路面積 最小化高頻信號和電源的環路面積幾乎在所有的EMC設計指南中都有提到,但卻常常被忽略。部分新手

2020-05-21 16:00:05 2172

2172 PCB環路對EMC的影響非常重要,比如反激主功率環路,如果太大的話輻射會很差。

濾波器走線效果,濾波器是用來濾掉干擾的,但若是PCB走線不好的話,濾波器就可能失去應該有的效果。

結構部分,散熱器設計接地不好會影響,屏蔽版的接地等;

2023-08-24 10:39:00 1523

1523

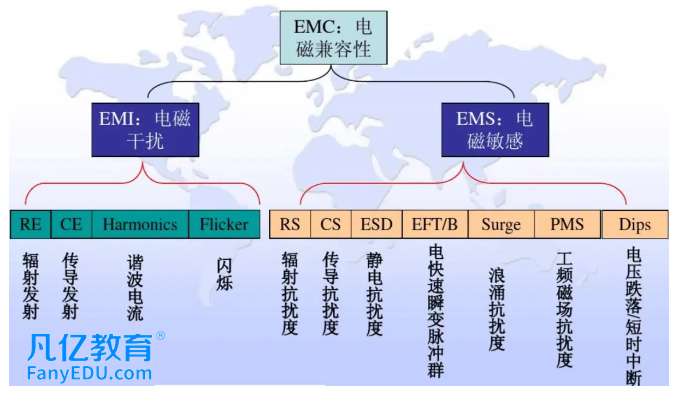

規律一、EMC費效比關系規律: EMC問題越早考慮、越早解決,費用越小、效果越好。規律二、高頻電流環路面積S越大, EMI輻射越嚴重。

2012-01-26 14:47:55 1559

1559 上市。 規律二、高頻電流環路面積S越大, EMI輻射越嚴重。 高頻信號電流流經電感最小路徑。當頻率較高時, 一般走線電抗大于電阻,連線對高頻信號就是電感,串聯電感引起輻射。電磁輻射大多是EUT被測設備上的高頻

2011-04-11 09:53:35

先從最簡單的模型理解EMC: EMC的路徑,當然空間輻射是跟環路有關,環路也是路徑構造成的;分析出反激高頻等效模型,幫助理解EMC形成的機理;我們的測試接收設備會從L,N端接收傳導,為了減小接收

2020-09-24 07:25:55

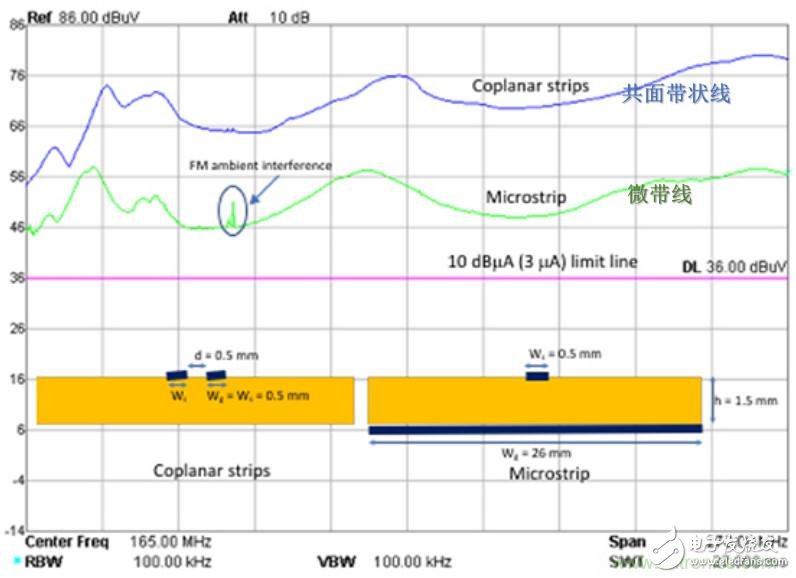

是FFT的數學表達,我們在觀測EMC的頻譜時要注意這一點。 我們很直觀的看到,同一個高頻信號,在PCB電路板上不同的路徑造成不同的環路面積的情況下,截然不同的EMI電磁干擾強度。我們不僅僅驗證信號

2022-04-13 11:02:42

的EMC設計應遵循以下內容:a) 盡量減小所有的高速信號及時鐘信號線構成的環路面積,連接線要盡可能短,并使信號線緊鄰地回路;b) 使用小型化器件和多層線路板,多層印制板可緊縮布線空間,高頻特性好,容易

2020-10-21 10:48:34

的缺陷,無法實施改進措施,導致產品不能上市。規律二、高頻電流環路面積S越大,EMI輻射越嚴重。高頻信號電流流經電感最小路徑。當頻率較高時,一般走線電抗大于電阻,連線對高頻信號就是電感,串聯電感引起輻射

2017-03-17 08:44:36

本帖最后由 eehome 于 2013-1-5 10:03 編輯

EMC磁珠特性

2012-08-14 09:47:10

選型,尋找一種優化電路、機械結構和PCB的設計解決方案,提高產品的設計質量,確保達到功能和性能指標的情況下,兼顧成本效益,避免EMC問題。為抑制和消除騷擾源,減小高頻信號頻率、減小高頻電流回路面積

2010-03-30 11:52:32

傳統上,EMC一直被視為「黑色魔術(black magic)」。其實,EMC是可以藉由數學公式來理解的。不過,縱使有數學分析方法可以利用,但那些數學方程式對實際的EMC電路設計而言,仍然太過復雜了

2017-11-10 12:35:06

以下幾點: (1)根據不同的電源電壓,數字電路和模擬電路分別設置地線。 (2)公共地線盡可能加粗。在采用多層厚膜工藝時,可專門設置地線面,這樣有助于減小環路面積,同時也降低了接受天線的效率。并且可作

2017-04-19 09:47:56

摘要近場測量探棒是在電磁兼容性(EMC)和信號完整性分析(SI)常用的設計工具,在應用方面,我們使用數值模擬和實驗分析比對了傳統金屬近場探棒跟新型的微光子主動近場探棒。數據顯示傳統探頭在近場區域很

2019-05-31 07:08:27

要使用multisim分析串并連諧振電路的頻率特性,電抗特性以及選頻特性分別需要什么儀器才能做到啊???

2015-09-14 21:27:37

路面檢測方案比較及可行性分析 環境圖像采集部分可以采用陣列紅外探頭和CCD或CMOS圖像傳感器來實現,前者的特點是價格低廉、電路簡單、應用方便,缺點是性能有限,對復雜環境的適應能力較弱,效果較差

2011-07-12 15:26:33

, 投產以后發現EMC 不合格才進行改進,非但技術上帶來很大難度,而且返工必然帶來費用和時間的大大浪費,甚至由于涉及到結構設計,PCB設計的缺陷,無法實施改進措施,導致產品不能上市。 規律二、 高頻電流環路面積S越大, EMI輻射越嚴重(圖文詳解見附件)

2019-10-30 11:31:41

線,你若是畫得很亂,很多PCB工程師對電路理解得布透徹可能就容易布錯板。 另外:原邊有一個重要的環路,PFC電容與MOS管以及變壓器,諧振電感,諧振電容構成的環路面積小; 副邊整流濾波環路同樣重要

2020-09-15 13:55:32

最近看了TL431內部電路圖,奈何自己水平有限,只能看懂個大概,不能詳細的分析內部工作原理,目前只能按照等效電路來推導環路傳遞函數。想在這個平臺上想大家請教,還請大家賜教!在這個帖子上看見了諧振

2020-04-02 11:48:56

LTSpice能不能進行任意降壓型DC-DC的環路特性分析,如何進行?

2024-01-04 07:09:17

,保證電路正常、穩定工作。 *從設備前端設計入手,關注EMC/EMI設計,降低設計成本。 2數字電路PCB的EMI控制技術 在處理各種形式的EMI時,必須具體問題具體分析。在數字電路的PCB設計中

2011-11-09 20:22:16

Sanjaya《模擬及數字控制環路優化設計》培訓內容之新能源電路拓撲&EMC設計與優化

2018-07-26 08:06:59

`介紹了控制環路分析里面必須用到的各種零,極點的幅頻和相頻特性;然后對最常用的反饋調整器 TL431 的零,極點特性進行分析;TOPSWITCH 是市場上廣泛應用的反激式電源的智能芯片,它的控制方式

2019-03-16 11:42:42

經常看到網上的一些pcb設計技巧中提到,有一個回路面積的概念,不太明白這個回路面積怎么去看,比如說“減少地的回路面積”“減少視頻信號回路面積”4 p6 D) v$ q, uz. `7 E在自己設計的pcb中,這個回路面積怎么去看哦?謝謝大家

2014-10-24 11:06:20

1、很榮幸拿到這本《運放電路環路穩定性設計 原理分析、仿真計算、樣機測試》,花了幾天的時間瀏覽了一遍,書的內容知識點很多,內容確是非常豐富的,需要細細品味消化,需要對運放有一點的了解,才能更加

2023-05-22 12:37:54

芯片的輸入/輸出電壓傳輸區限提高噪聲容限(3)選擇die到pin的焊線,減小大電流路徑環路面積(4)選擇多層IC布線加強隔離效果(5)金屬罩用于使芯片接地(6)選擇芯片的最長可用轉換時間,可得最窄噪聲

2016-02-23 15:39:37

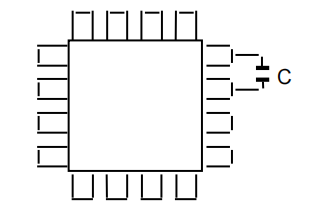

1000mil。6.存在較大電流變化的單元電路或器件(如電源模塊的輸入輸出端、風扇及繼電器)附近應放置儲能和高頻濾波電容,以減小大電流回路的回路面積。7.濾波器件需并排放置,以防止濾波后的電路被再次干擾。8.晶體

2016-05-17 15:04:46

增加EMC問題風險?布線換層,可能造成跡線的參考平面不連續,增加回線阻抗,可能造成環路面積增大,影響電磁輻射及電磁敏感性,因此會增加EMC問題的風險。

2021-07-15 22:38:43

1、公稱熔化熱能2、不會3、回路中斷,增大環路面積下期希望cs部分的抗干擾

2021-07-15 21:09:51

,因為有用信號都是差模信號。差模電流的磁場主要集中在差模電流構成的回路面積內,而回路面積之外,磁力線會相互抵消;共模電流的磁場在回路面積之外,共模電流產生的磁場方向相同。PCB的很多EMC設計都遵循以上

2018-11-23 16:21:49

、電源噪聲?2、電源復位?3、電源輸出?4、電源損壞?等等。瞬態干擾(EMS)對設備會產生威脅,出現產品功能及性能的問題。后面我們通過PCB的分析來講解開關電源系統EMS的問題;開關電源系統的產品EMC

2018-09-14 11:40:23

,無法實施改進措施,導致儀表不能上市。2、規律二:高頻電流環路面積S越大, EMI輻射越嚴重。高頻信號電流流經電感最小路徑。當頻率較高時,一般走線電抗大于電阻,連線對高頻信號就是電感,串聯電感引起輻射

2018-09-02 16:22:46

什么是SCF電路?怎樣去分析時域法的特性 ? 如何去分析頻域法的特性 ?

2021-04-20 06:01:25

需要從哪幾方面去分析電荷泵鎖相環系統的相位噪聲特性? 才能得出系統噪聲特性的分布特點以及與環路帶寬的關系。

2021-04-07 07:11:48

典型的BuckBoost的電源電路,沒有病必需要過CISPR25 Class 32.2 初測結果2.3 整改措施2.3.1 原理分析兩個開關環路中含有非連續的大電流環路是最主要的噪聲源增加Vin和Vss

2018-12-03 11:18:22

面的案子所示2.1)這是一個典型的BuckBoost的電源電路,沒有病必需要過CISPR25 Class 32.2 初測結果2.3 整改措施2.3.1 原理分析兩個開關環路中含有非連續的大電流環路

2018-10-17 16:43:07

其金屬機殼實現多點接地,接地點的間距應小于最高工作頻率波長的1/20,且金屬外殼單點接大地。總之,在電子電路設計中,最重要的一點是減小電路的回路面積,這對提高電子設計穩定性和提高電子系統EMC設計有著重要的作用。在實際的設計中,通過綜合評價以上的各種技術,通過靈活使用,以便達到提高系統穩定性的目的。

2019-06-12 04:20:24

正常、穩定工作。 *從設備前端設計入手,關注EMC/EMI設計,降低設計成本。2、數字電路PCB的EMI控制技術 在處理各種形式的EMI時,必須具體問題具體分析。在數字電路的PCB設計中,可以從下

2019-09-16 22:37:29

本文所介紹的各種方法與技巧有利于提高PCB的EMC特性,當然這些只是EMC設計中的一部分,通常還要考慮反射噪聲,輻射發射噪聲,以及其他工藝技術問題引起的干擾。

2021-04-27 06:20:32

摘要 : 要降低DC到DC電路的輻射發射,可以采取以下幾種方法: 地線和電源線的布局:確保地線和電源線的布局合理,并盡量減少它們之間的距離。使用短而粗的地線和電源線,以減小回路面積和環路面積,從而

2023-06-06 09:21:29

摘要 : 要降低DC到DC電路的輻射發射,可以采取以下幾種方法: 地線和電源線的布局:確保地線和電源線的布局合理,并盡量減少它們之間的距離。使用短而粗的地線和電源線,以減小回路面積和環路面積,從而

2023-06-12 14:26:21

能力。

· 地線和電源線的布局:與DC到DC電路類似,合理布局USB的地線和電源線,并盡量減少它們之間的距離。使用短而粗的地線和電源線,減小回路面積和環路面積,有助于降低輻射發射。

· USB濾波器

2023-06-14 09:30:14

的抗擾度。解決辦法:①模擬與數字電路應有各自的回路,最后單點接地; ②電源線與回線越寬越好; ③縮短印制線長度; ④電源分配系統去耦。4、減小環路面積及兩環路的交鏈面積。5、一個重要思想是:PCB上

2020-03-27 11:15:07

)A:電流的環路面積(cm2)I :電流的強度(mA)r :測試點到電流環路的距離(m) 6、共模輻射電場的計算 其中 :E:電場強度(V/m)f :電流的頻率(MHz)L:電纜的長度(m)I

2019-10-09 15:03:35

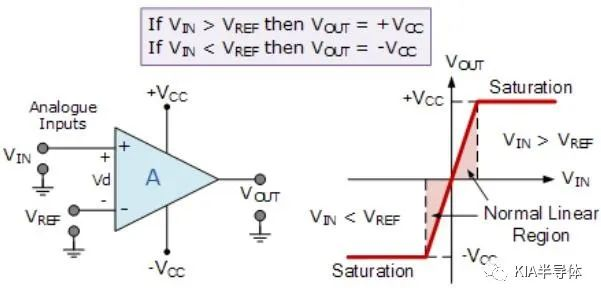

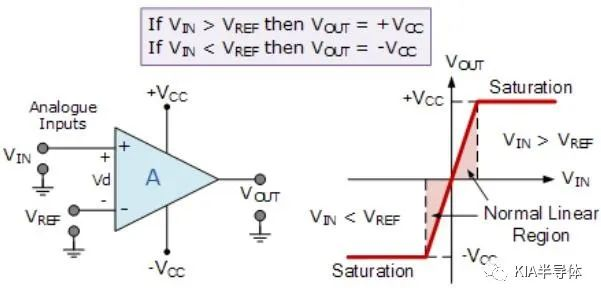

,開關電源也可以看成是黑盒,有輸入輸出。直接分析開關電源的環路穩定性,相當復雜,但是運放器件少,分析起來比較簡單。從運放開始,是突破口。2、開環系統對于運放來說,假設我們有下面這樣的電路。給運放一個

2022-11-22 08:00:00

高頻高壓直流電容 C_IP 是減少 PCB 環路面積和分離高頻和低頻兩個部分回路有效措施。? 合理增加磁珠抑制高頻電流? 為了額外降低 di/dt,可以在電路中增加已知的電感,以抑制高頻段的電流尖峰

2020-10-10 08:31:31

的頻響,保證電路正常、穩定工作。 ●從設備前端設計入手,關注EMC/EMI設計,降低設計成本。 2數字電路PCB的 EMI控制技術 在處理各種形式的EMI時,必須具體問題具體分析。在數字電路

2018-09-14 16:32:58

如何降低數字信號和仿真信號間的相互干擾呢?在設計之前必須了解電磁兼容 (EMC) 的兩個基本原則︰第一個原則是盡可能減小電流環路的面積;第二個原則是系統只采用一個參考面。相反,如果系統存在兩個參考面

2019-08-19 06:01:20

嗨,我對此很新......但是嘿......我盡我所能學習......我想知道測量組合電路面積的最佳方法是什么......,該區域是否會用LUT表示?..我認為順序電路的區域用Slice寄存器表示

2019-02-13 10:08:04

滿足什么特性的開關電源不需要環路補償?

2019-03-12 13:51:11

的表現是否穩定,就這么簡單!環路分析結果圖片二、環路分析的結果是什么?示波器根據輸出信號、輸入信號的幅度、相位隨頻率變化的關系,可得到環路系統的伯德圖(幅頻特性、相頻特性)。想要對產品的穩定性有所了解

2018-04-16 15:25:26

、電感環路面積以及環路方向非常敏感。 所以,電感的排列的原則有: (1)正確排列電感的方向,使其成直角,使電感間的串擾降到最小; (2)電感間距應盡可能遠。來源:http://www.cenkersz.com/Article/dgdzytxst_1.html

2017-05-13 10:35:22

環路對消原理提高抗干擾能力,增大傳輸距離):圖 1 ,環路對消( boost 電路的續流環)6、降低環路面積不僅降低了輻射,同時還降低了環路電感,使電路性能更佳。7、降低環路面積要求我們精確設計各走線

2021-07-08 09:17:03

環路分析儀的主要功能是量測待測物電源產品在頻域上的特性,了解其性能及穩定性,并可輔助控制線路的設計。其工作原理是給電路輸入一個頻率變化的干擾小訊號,分析增益余量和相位余量,判斷環路是否穩定。 傳統

2017-05-03 21:59:56

調節對EMC影響,布板走線環路面積也有著重要的影響!另二個環路是吸收環路和整流環路,先提前了解下,后面再講! 3、PCB設計與EMC的關聯 PCB環路對EMC的影響非常重要,比如反激主功率環路

2018-10-15 10:16:33

環路對消原理提高抗干擾能力,增大傳輸距離):圖 1 ,環路對消( boost 電路的續流環)6、降低環路面積不僅降低了輻射,同時還降低了環路電感,使電路性能更佳。7、降低環路面積要求我們精確設計各走線

2022-04-16 14:30:53

不合格才進行改進,非但技術上帶來很大難度、而且返工必然帶來費用和時間的大大浪費,甚至由于涉及到結構設計、PCB設計的缺陷,無法實施改進措施,導致產品不能上市。 規律二、高頻電流環路面積S越大, EMI輻射

2014-12-09 09:55:09

:采樣電路設計。電路的合理布局可以降低干擾,提高電磁兼容性能。按照電路的功能劃分若干個功能模塊,分析每個模塊的干擾源與敏感信號,以便進行特殊處理。印制板布線時,需要注意以下幾個方面:1、保持環路面積最小

2012-10-19 11:39:40

才進行改進,非但技術上帶來很大難度、而且返工必然帶來費用和時間的大大浪費,甚至由于涉及到結構設計、PCB設計的缺陷,無法實施改進措施,導致產品不能上市。規律二高頻電流環路面積S越大, EMI輻射越嚴重

2015-08-03 13:50:49

前后沿的陡度;③ 晶體振蕩電平必須滿足一定幅度, 數字電路才能按一定的時序工作,使晶振產生的騷擾呈現覆蓋帶寬、騷擾電平高的特點;④ 收發天線極化、方向特性相同時,EMI輻射和接受最嚴重;收發天線面積

2023-09-08 11:01:38

的環路面積,連接線要盡可能短,并使信號線緊鄰地回路;2) 使用小型化器件和多層線路板,多層印制板可緊縮布線空間,高頻特性好,容易實現EMC;3) 印制板層數選擇考慮關鍵信號的屏蔽和隔離要求,先確定所需信號

2018-05-19 11:18:48

回路上感應出電壓,圖中是一個簡單的電路。在差模信號的回路中,電磁波會在此回路中感應出差模電壓。這個差模電壓直接疊加在信號電壓上,因此會對負載產生直接影響。這個感應差模電壓的大小與環路面積有直接的關系

2023-04-18 14:47:15

間距、電感環路面積(即磁通量)以及環路方向非常敏感。因此,緊湊的電路布局和降低耦合之間的最佳平衡是正確排列所有電感的方向。磁力線由上圖的磁力線可以看出互感與電感排列方向有關。對電路B的方向進行調整

2019-09-10 07:00:00

電壓可通過下面措施進行改進:增加高頻電容減小環路面積我們可以采取措施減小高頻電位跳變點的PCB環路面積。增加高頻高壓直流電容C_IP是減少PCB環路面積和分離高頻和低頻兩個部分回路有效措施。合理增加磁珠

2020-10-21 07:13:24

胡衡毅:大家好!我是村田電子的EMC工程師,我將利用這次機會和大家一起討論,近場分析在EMC中有哪些應用?

2019-08-06 07:08:28

鎖相環路由哪些組成?它的基本特性是什么?應用于哪些領域?

2021-04-12 06:58:54

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

鎖相環的原理,特性與分析所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱環路,通常用PLL 表示。

2008-08-15 13:18:46

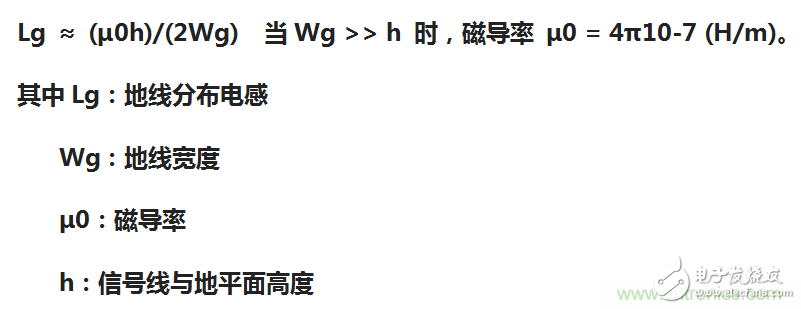

我們都知道信號線與回路的環路面積對電路 EMC 特性影響很大,理論上環路面積越大,信號的天線效應越明顯,EMC 特性也越差。其實除了環路面積,電路設計中另一指標對 EMC 特性的影響還更大。下面通過

2019-10-20 08:00:00

`高速電路PCB設計與EMC技術分析`

2017-09-21 21:31:03

基礎電路的EMC影響分析:表面上該電路并沒有什么問題,也沒有電路壽命的問題,但是在進行EMC 測試時此電路就存在致命問題,由于在加熱階段可控硅始終以50Hz 的頻率進行開通和

2009-10-08 21:17:53 45

45 鎖相環路的原理及特性

鎖相環路的應用

單片集成鑒相器

集成壓控振蕩器

單片集成鎖相環

.................

2010-08-28 15:56:34 99

99 穩定的反饋環路對開關電源來說是非常重要的,如果沒有足夠的相位裕度和幅值裕度,電源的動態性能就會很差或者出現輸出振蕩。 下面先介紹了控制環路分析里面必須用到的各種零,極點的幅頻和相頻特性;然后對最常用的反饋調整器TL431的零,極點特性進行分析;T

2011-02-28 14:41:30 0

0 傳統上,EMC一直被視為「黑色魔術(black magic)」。其實,EMC是可以藉由數學公式來理解的。不過,縱使有數學分析方法可以利用,但那些數學方程式對實際的EMC電路設計而言,仍然

2012-05-18 14:11:27 889

889 利用鎖相環的等效噪聲模型,重點分析電荷泵鎖相環系統的相位噪聲特性,得出系統噪聲特性的分布特點以及與環路帶寬的關系。

2012-11-22 10:44:47 16471

16471 PCB電路設計中布線的EMC分析,下來看看

2016-07-29 19:05:18 0

0 變面積臨界流文丘里噴嘴特性研究_陳元杰

2017-03-19 18:58:37 0

0 環路面積S越大,?EMI輻射越嚴重

高頻信號電流流經電感最小路徑。當頻率較高時,一般走線電抗大于電阻,連線對高頻信號就是電感, 串聯電感引起輻射。 電磁輻 射大多是被測設備 (EUT) 上的高頻電流

2019-07-26 11:46:53 2904

2904

多層印制電路板中,可設置接地層,接地層設計成網狀。地線網格的間距不能太大,因為地線的一個主要作用是提供信號回流路徑,若網格的間距過大,會形成較大的信號環路面積。大環路面積會引起輻射和敏感度問題。另外,信號回流實際走環路面積小的路徑,其他地線并不起作用。

2019-08-12 16:51:44 1860

1860 文中將分析EMC設計的3大規律:EMC費效比關系規律;高頻電流環路面積S越大, EMI輻射越嚴重;環路電流頻率f越高,引起的EMI輻射越嚴重,電磁輻射場強隨電流頻率f的平方成正比增大。

2021-09-03 16:29:02 5514

5514 濾波電容器、共模電感、磁珠在EMC設計電路中是常見的身影,也是消滅電磁干擾的三大利器。對于這三者在電路中的作用,相信還有很多工程師搞不清楚,文章從設計中詳細分析了消滅EMC三大利器的原理。

2020-09-09 14:33:39 1206

1206 環路分析儀的主要功能是量測待測物電源產品在頻域上的特性,了解其性能及穩定性,并可輔助控制線路的設計。

2020-09-18 15:35:05 6185

6185 電流通過感應進入到電路環路,這些環路是封閉的,并具有變化的磁通量。電流的幅度與環的面積成正比。較大的環路包含有較多的磁通量,因而在電路中感應出較強的電流。因此,必須減少環路面積。

2021-03-03 16:16:51 1265

1265 LTC3833演示電路面積緊湊型2.5V、5A、1.2 MHz降壓轉換器(6-28V至2.5V@5A)

2021-03-22 22:22:24 5

5 閑談醫療電子的可靠性、環路穩定性和EMC

2021-03-24 16:06:45 37

37 高速電路PCB設計與EMC技術分析.pdf

2021-11-21 10:09:40 0

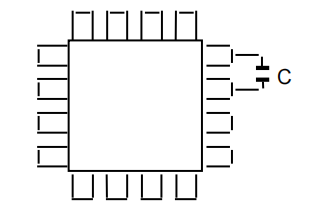

0 迄今為止,大多數 NEC 的微控制器封狀都有相鄰電源引腳。這引腳使 PCB 設計者能更輕易地減少微控制器與退耦電容之間的電流環路面積,當然,要最小化環路面積,每相鄰電源引腳對之間要有一個電容。不僅降低了環路面積,也減少了退耦電容的連接阻抗。

2022-08-16 09:10:52 1300

1300

如何優化PCB走線來減小回路電感和環路面積? 隨著電路設計的復雜性和頻率的不斷提高,電路中的電感和環路造成的影響也越來越明顯。因此,優化PCB走線以減小回路電感和環路面積已經成為了這個領域中的一項

2023-10-23 09:58:56 1063

1063 什么是電路設計中的自感和互感?PCB走線的回路電感和環路面積是什么? 電路設計中的自感和互感是電磁學中非常重要的兩個概念,它們在電路中起著重要的作用。電路中的自感和互感涉及到電流、磁感應強度和電壓

2023-10-23 09:58:59 851

851 在電子電路中是非常重要的,因為大多數電路都是閉環的,而且反饋回路的特性對電路的性能有很大的影響。 環路增益的特性會影響閉環系統的穩定性、帶寬和噪聲等方面。一個理想的環路增益特性應該是穩定、平滑的,在正常工作范圍內

2023-10-25 11:39:58 1401

1401 環路增益是什么?什么樣的環路增益特性是理想的呢? 環路增益(loop gain)是同相反饋系統中的一個重要概念,用于描述反饋回路的閉環增益。在電子電路和控制系統中,環路增益對系統的穩定性、幅頻特性

2023-11-08 17:46:24 1704

1704 什么是環路面積?怎么減小走線的環路電感? 環路面積是指電路中電流在閉合路徑上所圍成的面積。環路電感是在電路中由于閉合電流所引起的磁感應強度變化而產生的電動勢。 為了減小走線的環路電感,我們可以采取

2023-11-09 09:30:15 1422

1422 運放比較器電路特性分析

2023-12-04 11:14:10 470

470

常見EMC器件的特性及選型分析? EMC(電磁兼容性)是指電子設備在電磁環境中正常工作,同時不對周圍環境產生干擾。為了滿足EMC的需求,需要選擇合適的EMC器件。 一、EMC器件的特性 1. 輸入

2024-01-03 13:54:24 533

533 的移相特性非常重要,并且在電子電路中有許多實際應用。 首先,我們來觀察和分析RC電路的移相特性。為了用于觀測和分析移相特性,我們可以通過輸入一個正弦信號來激勵RC電路。正弦信號是一種周期性變化的信號,通常用于分析系統的頻率響應。在

2024-03-09 14:07:49 309

309

電子發燒友App

電子發燒友App

評論