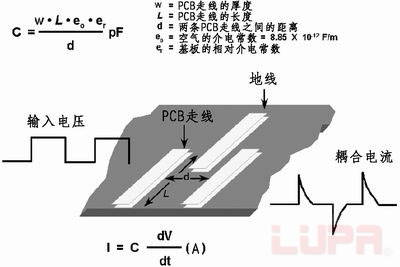

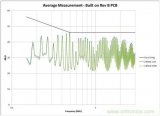

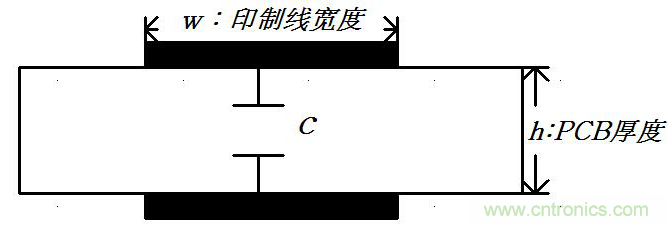

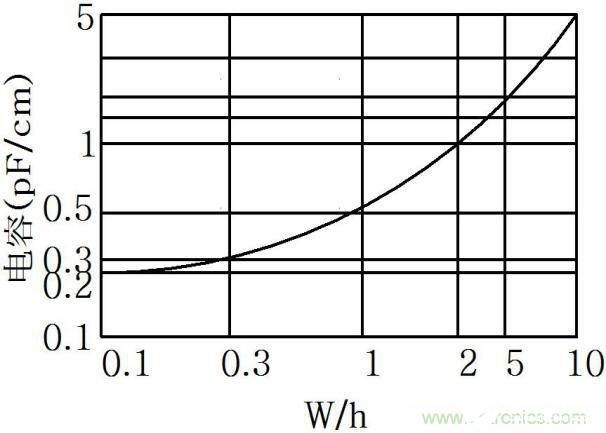

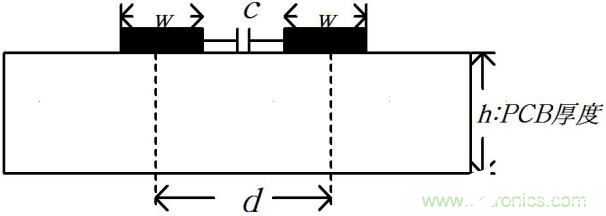

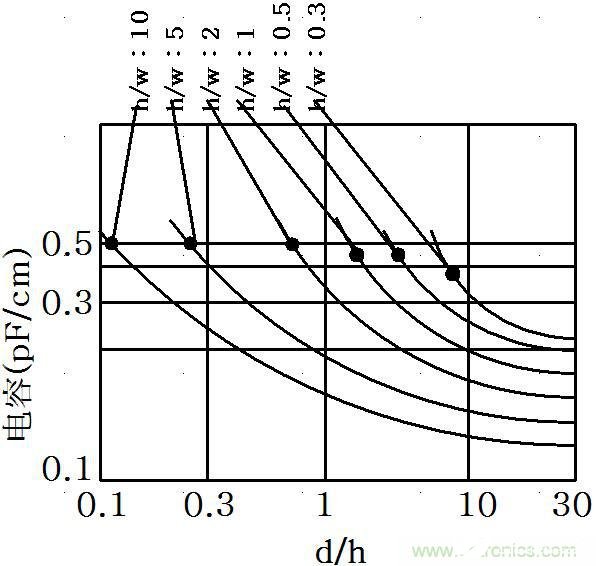

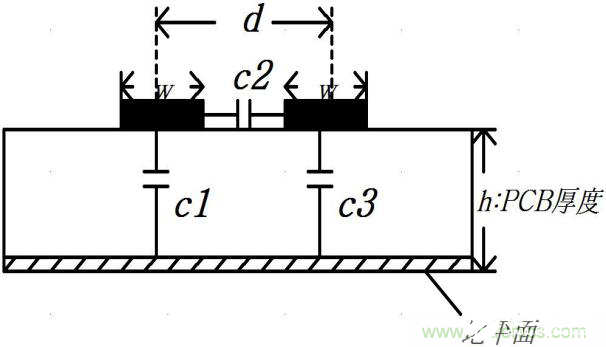

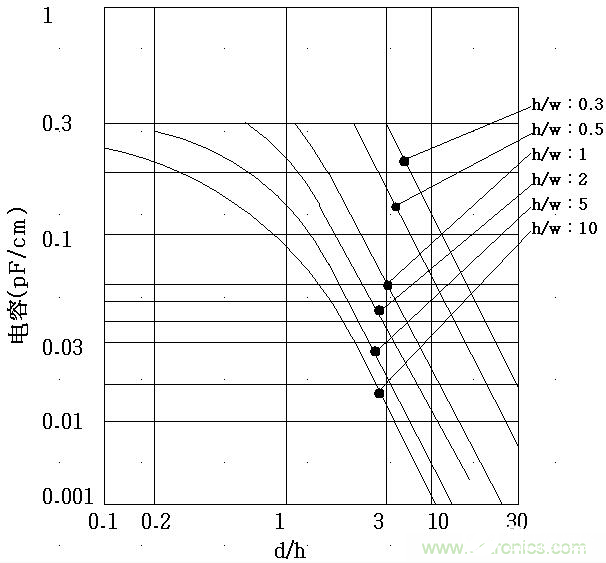

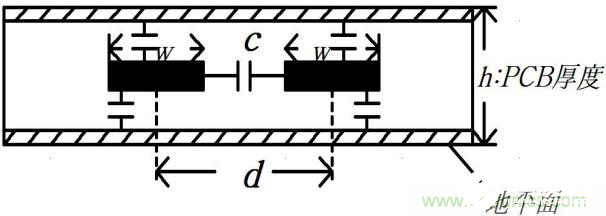

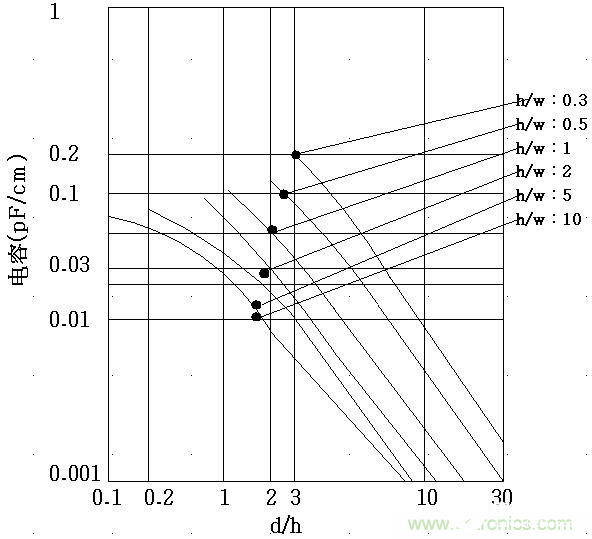

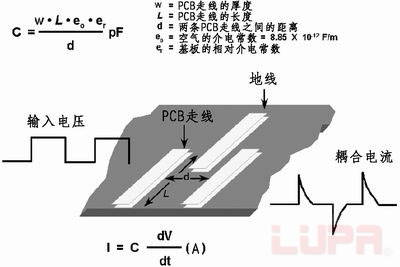

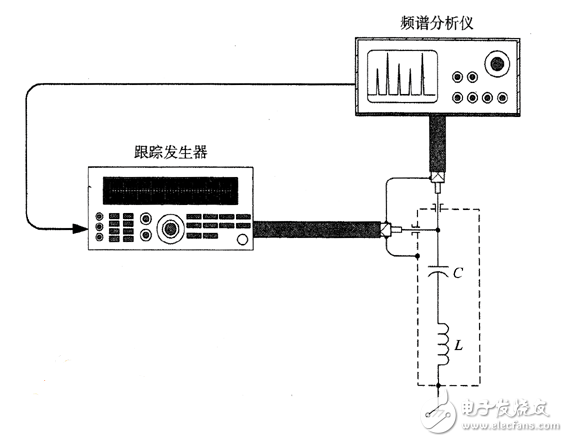

PCB布線設計時寄生電容的計算方法

在PCB上布兩條靠近的走線,很容易產生寄生電容。由于這種寄生電容的存在,

2009-09-30 15:13:33 26465

26465

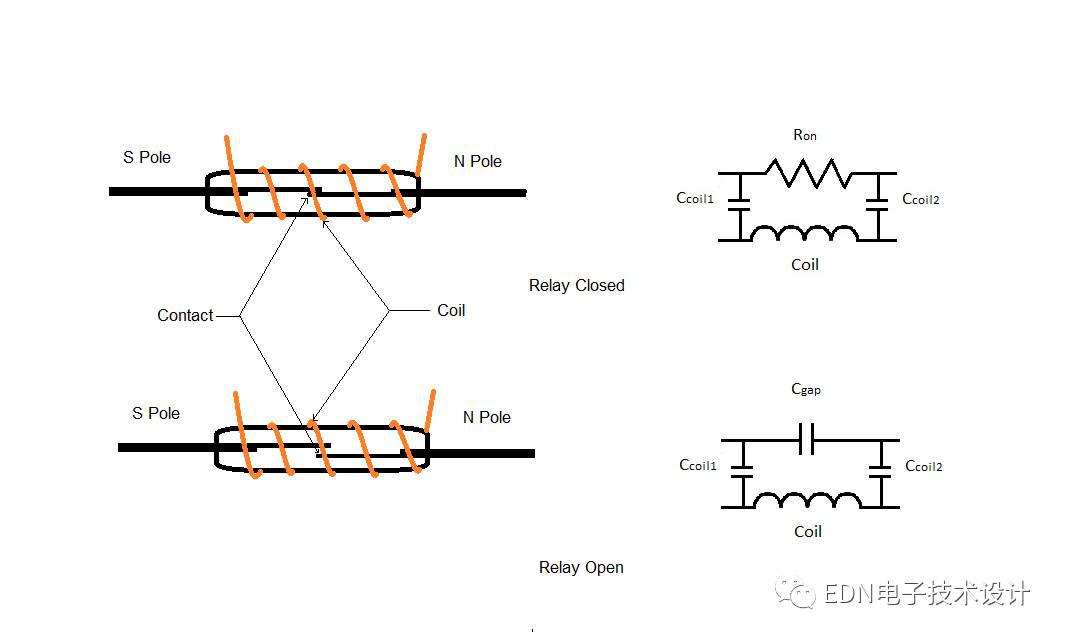

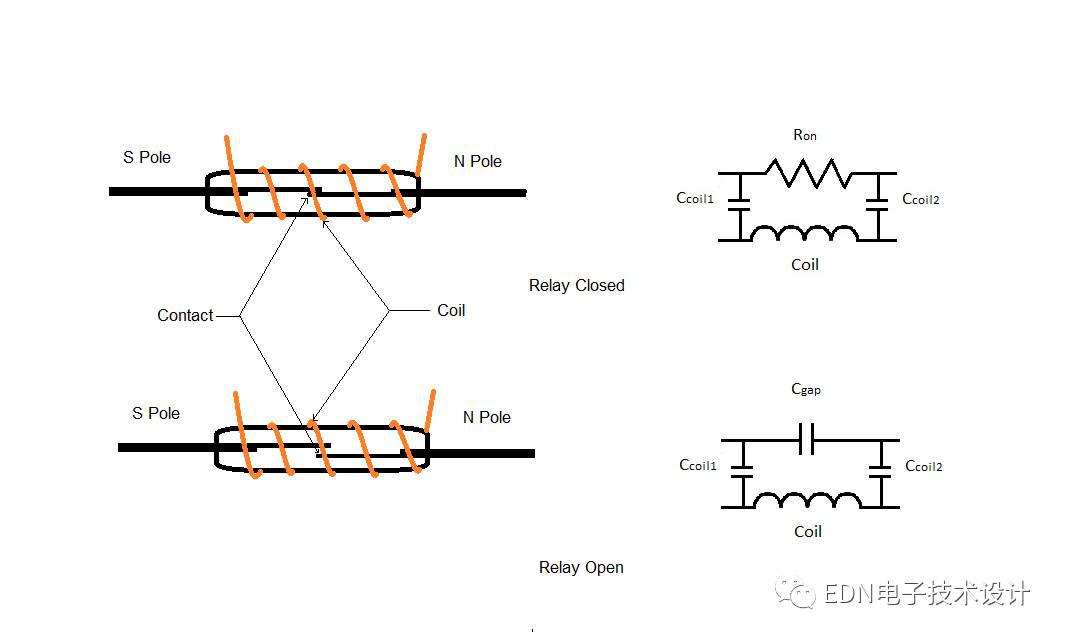

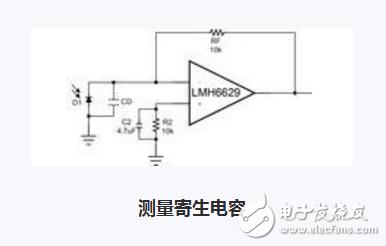

在被測點阻抗較高時,即使該點僅有較小的電容,其帶寬也會受限。在基于磁簧繼電器的多路選擇器中,由于各磁簧繼電器的寄生電容會在輸出端并聯,加大了輸出端的電容,使得電路的帶寬變窄。

2018-12-14 15:14:47 21354

21354

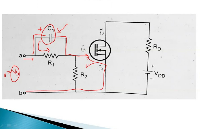

首先,我們介紹設計寄生電容對三極管產生的影響;然后,我們學習上拉電阻和下拉電阻的含義以及在電路中的使用方法。

2019-05-20 07:28:00 9439

9439

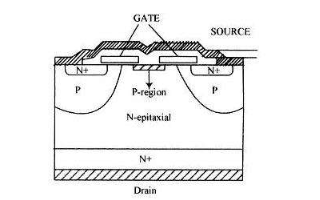

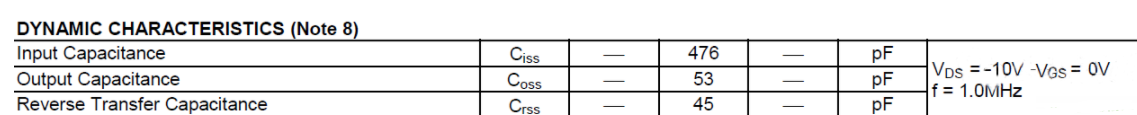

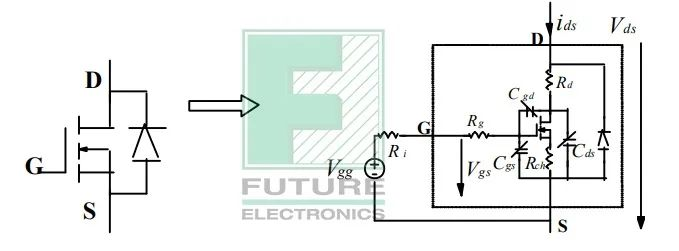

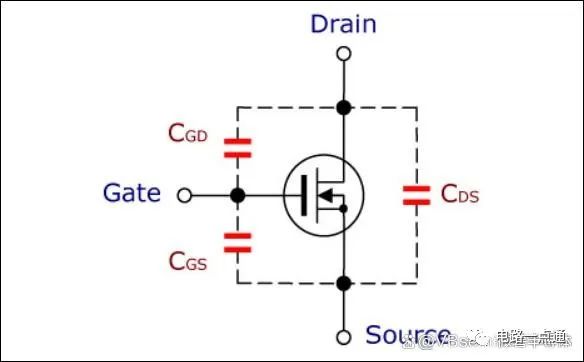

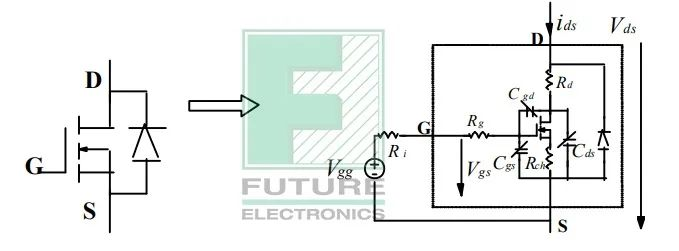

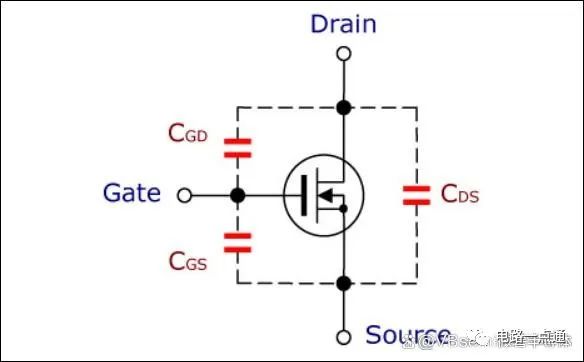

我們應該都清楚,MOSFET 的柵極和漏源之間都是介質層,因此柵源和柵漏之間必然存在一個寄生電容CGS和CGD,溝道未形成時,漏源之間也有一個寄生電容CDS,所以考慮寄生電容時,MOSFET

2021-01-08 14:19:59 15831

15831

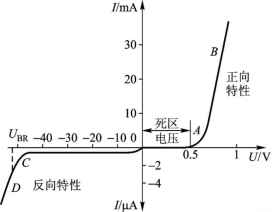

寄生電容有一個通用的定義:寄生電容是存在于由絕緣體隔開的兩個導電結構之間的虛擬電容(通常不需要的),是PCB布局中的一種效應,其中傳播的信號表現得好像就是電容,但其實并不是真正的電容。

2024-01-18 15:36:14 868

868

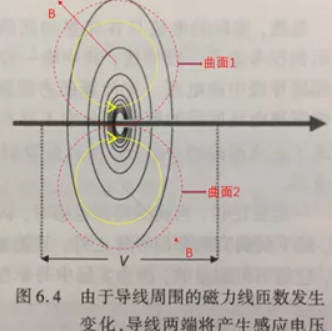

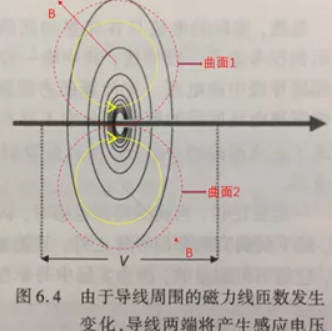

,由于干擾源的不確定性,串擾噪聲一般會同時影響信號的邊沿和幅度。因此,對于串擾來說兩個方面的影響都應該考慮。串擾形成的根源在于耦合。在多導體系統中,導體間通過電場和磁場發生耦合。這種耦合會把信號的一部分能量傳遞到鄰近的導體上,從而形成噪聲。耦合的方式主要有兩種:1、容性耦合。2、感性耦合。

2019-05-31 06:03:14

。兩根線(也包括PCB的薄膜布線)獨立的情況下,相互間應該不會有電氣信號和噪聲等的影響,但尤其是兩根線平行的情況下,會因存在于線間的雜散(寄生)電容和互感而引發干擾。所以,串擾也可以理解為感應噪聲

2018-11-29 14:29:12

電容會進一步減小,這種現象正是使用隔離底線抑制串擾的出發點之一。圖2.容性耦合(Capacitive coupling)感性耦合如果一條走線上有數字信號傳輸,在信號電平跳變過程中,即信號處于跳變邊沿

2018-12-24 11:56:24

所謂串擾,是指有害信號從一個傳輸線耦合到毗鄰傳輸線的現象,噪聲源(攻擊信號)所在的信號網絡稱為動態線,***擾的信號網絡稱為靜態線。串擾產生的過程,從電路的角度分析,是由相鄰傳輸線之間的電場(容性)耦合和磁場(感性)耦合引起,需要注意的是串擾不僅僅存在于信號路徑,還與返回路徑密切相關。

2019-08-02 08:28:35

低頻下,所有三種電容器均未表現出寄生分量,因為阻抗明顯只與電容相關。但是,鋁電解電容器阻抗停止減小,并在相對低頻時開始表現出電阻特性。這種電阻特性不斷增加,直到達到某個相對高頻為止(電容器出現電感)。鋁聚合物電容器為與理想狀況不符的另一種電容器。

2019-08-15 06:33:32

紋波電壓波形中都能看到其某些部分。圖2:電容器及其寄生要素在連續同步降壓調節器中形成不同的紋波電壓圖3顯示了一個深度連續反激或者降壓調節器的波形,其輸出電容器電流可以為正和負,而具體狀態會不斷快速變化

2018-09-29 09:22:17

寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,和一個電阻的串聯,在低頻情況下表現不是很明顯,而在高頻情況下,等效值會增大,不能忽略。

2019-09-29 10:20:26

寄生電容的影響是什么?焊接對無源器件性能的影響是什么?

2021-06-08 06:05:47

和噪聲等的影響,但尤其是兩根線平行的情況下,會因存在于線間的雜散(寄生)電容和互感而引發干擾。所以,串擾也可以理解為感應噪聲。

2019-08-08 06:21:47

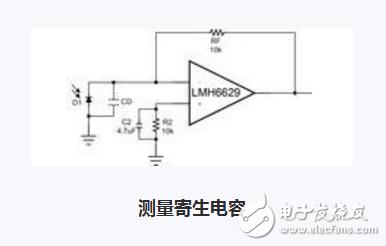

在LTC6268-10芯片手冊中,為了減小寄生反饋電容的影響,采用反饋電阻分流的方式減小寄生電容。

請問,在這種工作方式下,為了使寄生電容降到最低,對電路板的材料類型和厚度有什么要求嗎?

2023-11-16 06:28:44

MOSFET的工作波形。由于感性負載下,電流相位上會超前電壓,因此保證了MOSFET運行的ZVS。要保證MOSFET運行在感性區,諧振電感上的諧振電流必須足夠大,以確保MOSFET源漏間等效的寄生電容上存儲

2018-11-21 15:52:43

感性負載下,電流相位上會超前電壓,因此保證了MOSFET運行的ZVS。要保證MOSFET運行在感性區,諧振電感上的諧振電流必須足夠大,以確保MOSFET源漏間等效的寄生電容上存儲的電荷可以在死區時間內被

2018-07-13 09:48:50

)越快,產生的串擾也就越大。空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產生的串擾信號

2009-03-20 14:04:47

信號沿的變化(轉換率)越快,產生的串擾也就越大。空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由

2018-08-29 10:28:17

沿的變化(轉換率)越快,產生的串擾也就越大。 空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由

2020-06-13 11:59:57

)所示。 圖13W規則只是一個籠統的規則,在實際的PCB設計中,若死板地按照3W規則來設計會導致成本的增加。無法滿足3W規則時,可以通過對串擾的量化的理解,來改變一些其他的參數保持信號完整性。2.串

2014-10-21 09:53:31

飽和現象。 圖11 圖11為RT=0.3ns,L=2000mil,線間距從3mil變化至12mil時串擾的變化。4. 結論在實際的工程操作中,高速信號線一般很難調節其信號的上升時間,為了減少串擾,我們

2014-10-21 09:52:58

Y電容在電磁干擾中的作用是什么?

2023-04-20 15:04:10

寄生電容是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,一個電阻的串聯,低頻情況下表現不明顯,而高頻情況下,等效值會增大。在計算中我們要考慮

2021-01-11 15:23:51

串擾串擾的途徑:容性耦合和感性耦合。串擾發生在兩種不同情況:互連性為均勻傳輸線(電路板上大多數線)非均勻線(接插件和封裝)近端遠端串擾各不同。返回路徑是均勻平面時是實現最低串擾的結構。通常發生這種

2017-11-27 09:02:56

。兩根線(也包括PCB的薄膜布線)獨立的情況下,相互間應該不會有電氣信號和噪聲等的影響,但尤其是兩根線平行的情況下,會因存在于線間的雜散(寄生)電容和互感而引發干擾。所以,串擾也可以理解為感應噪聲

2019-03-21 06:20:15

什么是串擾?互感和互容電感和電容矩陣串擾引起的噪聲

2021-02-05 07:18:27

航空通信系統變得日益復雜,我們通常需要在同一架飛機上安裝多條天線,這樣可能會在天線間造成串擾,或稱同址干擾,影響飛機運行。在本教程模型中,我們利用COMSOL Multiphysics 5.1 版本模擬了飛機機身上兩個完全相同的天線之間的干擾,其中一個負責發射,另一個負責接收,以此來分析串擾的影響。

2019-08-26 06:36:54

橫截面的幾何結構(幾何結構決定電場分布,電場分布決定有效介電常數)。嚴格來說,不管是延遲還是時延都取決于導體周圍的有效介電常數。在微帶線中,有效介電常數受橫截面的幾何結構影響比較大;而串擾,其有效

2015-01-05 11:02:57

串擾信號產生的機理是什么串擾的幾個重要特性分析線間距P與兩線平行長度L對串擾大小的影響如何將串擾控制在可以容忍的范圍

2021-04-27 06:07:54

在高壓回路中,正負極對地會產生一個寄生電容,而寄生電容與回路中的電阻會組成一個RC充放電電路。在使用國標電流橋檢測電路方法時,正負極對地的寄生電容和電阻的大小會影響到AD采集。在RC充滿的時間一般為3RC以上,在此過程中如何探討RC電路充滿電壓的時間?

2020-07-27 23:14:10

,同樣對傳輸線2有 。 圖1 雙傳輸線系統中電容示意圖在實際的電路PCB中,往往N多條傳輸線共存,如果要考慮所有傳輸線間的串擾情況,那將是非常復雜的N階矩陣。信號間串擾信號的仿真分析一般通過電磁場仿真器

2016-10-10 18:00:41

。 由以上兩式,我們可以看出遠端串擾總噪聲由于容性和感性耦合的極性關系而相互消減,即遠端串擾是可以消除的。在PCB布線中,帶狀線(Stripline) 電路更能夠顯示感性和容性耦合之間很好的平衡,其

2018-09-11 15:07:52

從開關節點到輸入引線的少量寄生電容(100毫微微法拉)會讓您無法滿足電磁干擾(EMI)需求。那100fF電容器是什么樣子的呢?在Digi-Key中,這種電容器不多。即使有,它們也會因寄生問題而提

2019-05-14 08:00:00

在嵌入式系統硬件設計中,串擾是硬件工程師必須面對的問題。特別是在高速數字電路中,由于信號沿時間短、布線密度大、信號完整性差,串擾的問題也就更為突出。設計者必須了解串擾產生的原理,并且在設計時應用恰當的方法,使串擾產生的負面影響降到最小。

2019-11-05 08:07:57

大部分傳導 EMI 問題都是由共模噪聲引起的。而且,大部分共模噪聲問題都是由電源中的寄生電容導致的。對于該討論主題的第 1 部分,我們著重討論當寄生電容直接耦合到電源輸入電線時會發生的情況1. 只需

2022-11-22 07:29:30

貼片晶振的PCB layout需要注意哪些晶振相鄰層挖空是如何控制寄生電容Cp的呢?為什么溫度會影響晶振頻率呢?

2021-02-26 07:43:28

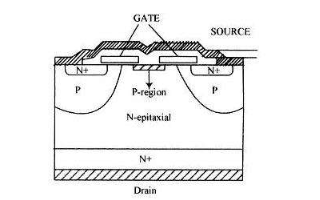

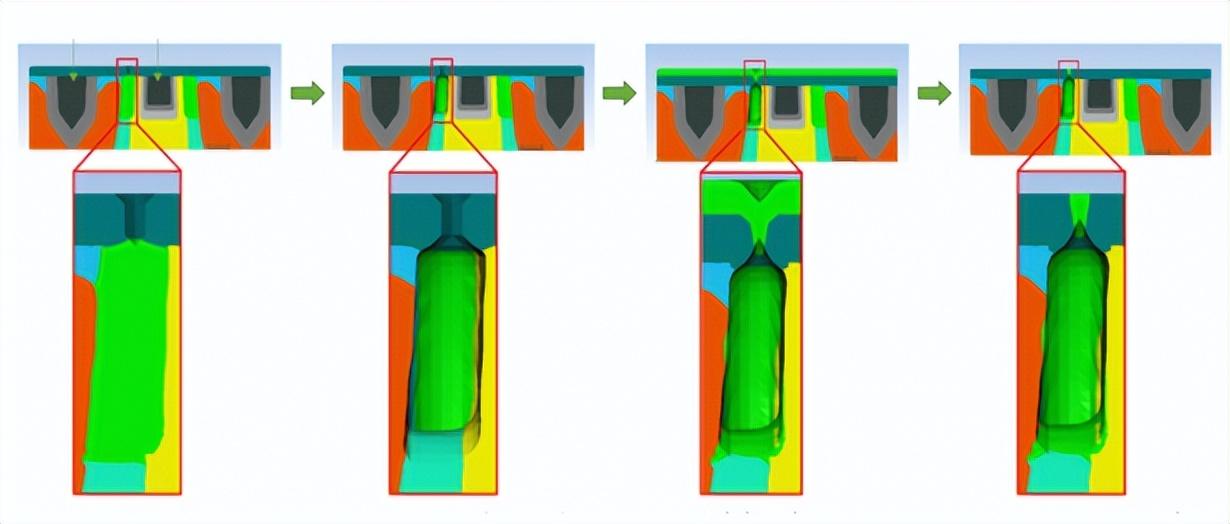

VDMOS的基本原理一種減小寄生電容的新型VDMOS結構介紹

2021-04-07 06:58:17

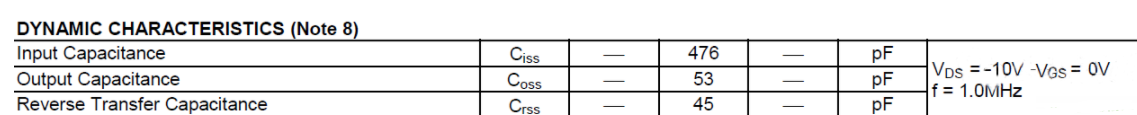

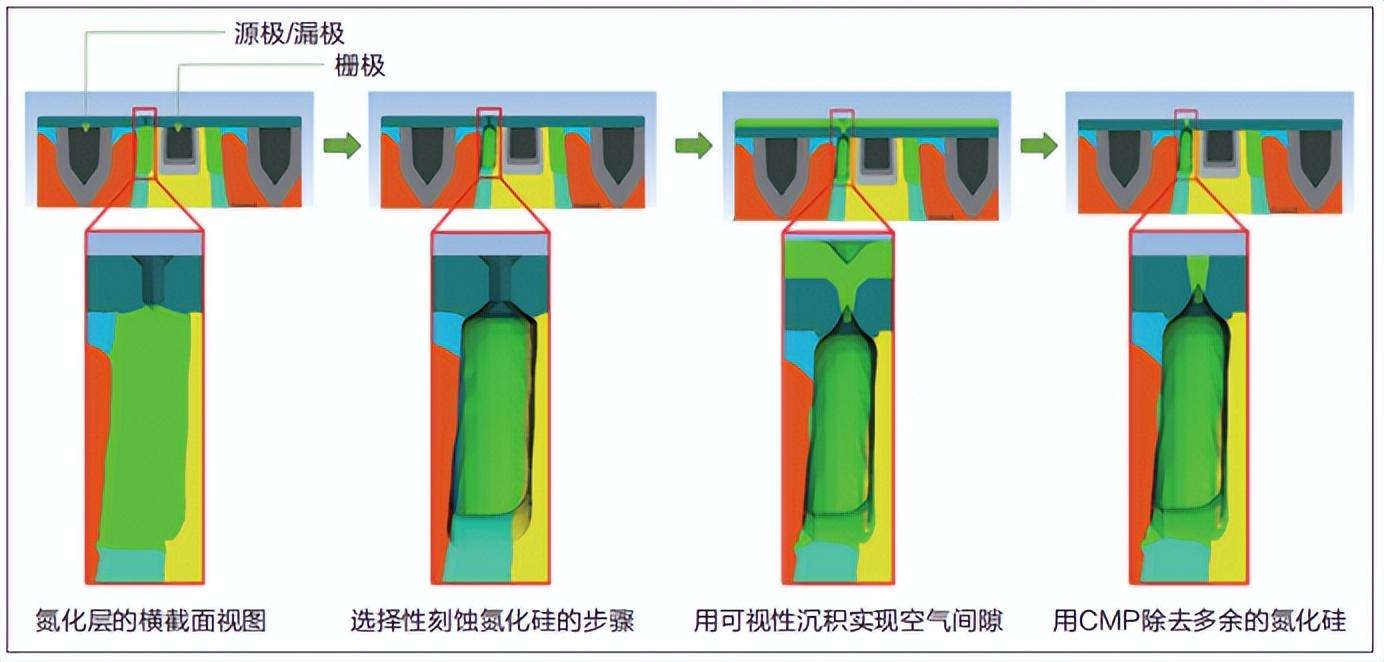

也是基于電容的特性,下面將從結構上介紹這些寄生電容,然后理解這些參數在功率MOSFET數據表中的定義,以及它們的定義條件。1、功率MOSFET數據表的寄生電容溝槽型功率MOSFET的寄生電容的結構如圖

2016-12-23 14:34:52

`磁芯對電感寄生電容的影響`

2012-08-13 15:11:07

`磁芯對電感寄生電容的影響`

2012-08-14 09:49:47

;Verdana">磁芯對電感寄生電容的影響分析</font></strong&

2009-12-23 16:07:01

途徑,異步信號線,控制線,和IO口走線上,它會使電路或者元件出現功能不正常的現象。 串擾中的信號耦合分為容性耦合和感性耦合,通常感性串擾占的比例大于容性串擾。

2020-11-02 09:19:31

可知,在多負載的Fly_By鏈路中,由于分支Stub,過孔寄生電容,芯片封裝電容和Die電容等因素,導致負載呈容性,使得信號在支路部分感受到的阻抗將會比實際走線阻抗偏低。而容性負載補償就是事先將支路部分

2023-05-16 17:57:26

噪聲的傳導回路面積較大,進一步推動輻射發射的產生。在第 3 部分中,我將全面介紹降壓穩壓器電路中影響 EMI 性能和開關損耗的感性和容性寄生元素。通過了解相關電路寄生效應的影響程度,可以采取適當的措施將

2020-11-03 07:54:52

檢驗具有高轉換率電流的關鍵回路寄生組分和輻射EMI功率級寄生電容EMI頻率范圍和耦合模式

2021-02-24 08:01:34

,寄生電容的影響已經不能忽視了。在系統中,這些不期望的電容來自方方面面,比如PCB的材質、厚度、板層結構、走線平行度,這些都是影響PCB板的寄生電容,還有元器件本身的寄生電容,最可惡的是這些東西還受

2020-12-15 15:48:52

變高,邊沿變陡,印刷電路板的尺寸變小,布線密度加大等都使得串擾在高速PCB設計中的影響顯著增加。串擾問題是客觀存在,但超過一定的界限可能引起電路的誤觸發,導致系統無法正常工作。設計者必須了解串擾產生

2009-03-20 13:56:06

產生的串擾隨受干擾線路負載阻抗的增大而增大,所以減小負載可以減小耦合干擾的影響;

??;??? [td]2)盡量增大可能發生容性耦合導線之間的距離,更有效的做法是在導線間用地線隔離

2018-08-28 11:58:32

和遠端串擾這種方法來研究多線間串擾問題。利用Hyperlynx,主要分析串擾對高速信號傳輸模型的侵害作用并根據仿真結果,獲得了最佳的解決辦法,優化設計目標。【關鍵詞】:信號完整性;;反射;;串擾;;近

2010-05-13 09:10:07

電容器的寄生作用與雜散電容.pdf

2006-04-04 23:33:03 0

0 鐵氧體電感器在較高頻率時可等效為“電阻、電感”的串聯支路與一寄生電容的并聯,該電容的存在對電感器的高頻性能有重要影響。本文建立了鐵氧體環形電感器2D平行平面場和3D

2009-04-08 15:45:17 66

66 寄生電容對電磁干擾濾濾器效能的影響

本文將針對交換式電源供應器在高頻切換所帶來的傳導性電磁干擾(Conducted Electromagnetic Interference)問題,藉由不同繞

2010-06-19 16:30:37 54

54 一種減少VDMOS寄生電容的新結構

0 引 言 VDMOS與雙極晶體管相比,它的開關速度快,開關損耗小,輸入電阻高,驅動電流小,頻率特性好,跨導高度線性

2009-11-25 17:49:50 1003

1003 電容器的寄生作用與雜散電容

電容器的寄生作用問:我想知道如何為具體的應用選擇合適的電容器,但我又不清楚許多不同種類 的電容器有哪些優點和缺點?

2009-11-26 10:44:19 2130

2130 一種減少VDMOS寄生電容的新結構

0 引 言 VDMOS與雙極晶體管相比,它的開關速度快,開關損耗小,輸入電阻高,驅動電流小,頻率特性好,跨

2009-11-27 09:24:23 613

613 一種減少VDMOS寄生電容的新結構

0 引 言 VDMOS與雙極晶體管相比,它的開關速度快,開關損耗小,輸入電阻高,驅動

2010-01-11 10:24:05 1321

1321 寄生電容,寄生電容是什么意思

寄生的含義 寄身的含義就是本來沒有在那個地方設計電容,但由于布線構之間總是有互容,互

2010-03-23 09:33:55 2558

2558 電容器的寄生作用與雜散電容

電容器的寄生作用問:我想知道如何為具體的應用選擇合適的電容器,但我又不清楚許多不同種類 的電容器有哪

2010-01-04 17:03:54 1297

1297

電容器的寄生作用與雜散電容,還不錯哦

2016-06-15 15:53:57 6

6 電磁干擾EMI中電子設備產生的干擾信號是通過導線或公共電源線進行傳輸,互相產生干擾稱為傳導干擾。傳導干擾給不少電子工程師帶來困惑,如何解決傳導干擾?這里,我們先著重討論當寄生電容直接耦合到電源輸入

2018-05-18 01:17:00 2785

2785

電容器的寄生作用與雜散電容

2017-01-28 21:32:49 5

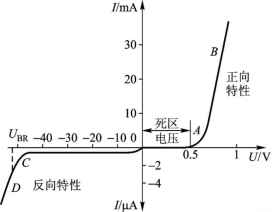

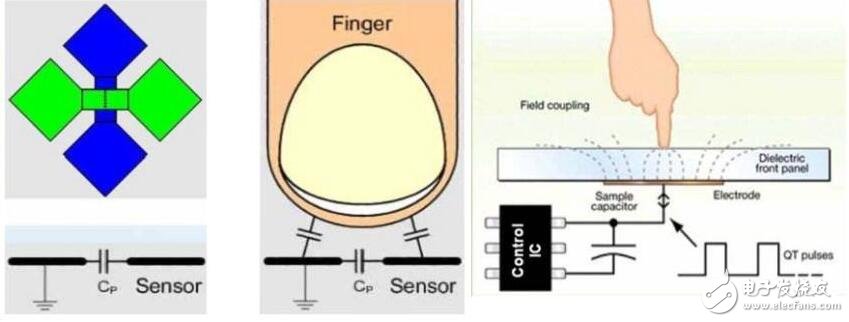

5 二極管以其單向導電特性,在整流開關方面發揮著重要的作用;其在反向擊穿狀態下,在一定電流范圍下起到穩壓效果。令人意外的是,利用二極管的反偏壓結電容,能夠有效地減少信號線上的接入寄生電容,這里將近一步討論這個運用。

2017-03-21 11:31:30 3813

3813

升壓設計中最關鍵的部件之一像圖1是變壓器。變壓器的寄生組件,可以使他們偏離它們的理想特性和寄生電容與二次關聯可引起大共鳴開關電流前沿的電流尖峰波形。這些尖峰可以導致調節器顯示表現為義務的不穩定的操作

2017-05-02 14:15:40 19

19 寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,和一個電阻的串連,在低頻情況下表現不是很明顯,而在高頻情況下,等效值會增大,不能忽略。

2018-01-31 10:09:29 21526

21526

寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,和一個電阻的串連,在低頻情況下表現不是很明顯,而在高頻情況下,等效值會增大,不能忽略。

2018-01-31 10:57:56 26012

26012 電容的寄生電感和寄生電阻主要是指它的引線和極板形成的電感和電阻,尤其是容量較大的電容更為明顯。如果你解剖過電容器,會看到它的極板是用長達1米的金屬薄膜卷曲而成的,其層狀就像一個幾十、甚至上百圈的線圈

2018-01-31 13:44:55 37301

37301

本文首先介紹了寄生電容的概念,其次介紹了寄生電容產生的原因,最后介紹了寄生電容產生的危害。

2019-04-30 15:39:37 28588

28588 分布電容強調的是均勻性。寄生跟強調的是意外性,指不是專門設計成電容,卻有著電容作用的效應,比如三極管極間電容。單點說,兩條平行走線之間會產生分布電容,元器件間在高頻下表現出來的容性叫寄生電容。

2019-04-30 15:56:30 19503

19503

減小電感寄生電容的方法

如果磁芯是導體,首先:

用介電常數低的材料增加繞組導體與磁芯之間的距離

2019-07-18 08:00:00 1

1 寄生電感一半是在PCB過孔設計所要考慮的。在高速數字電路的設計中,過孔的寄生電感帶來的危害往往大于寄生電容的影響。它的寄生串聯電感會削弱旁路電容的貢獻,減弱整個電源系統的濾波效用。我們可以用下面的公式來簡單地計算一個過孔近似的寄生電感。

2019-10-11 10:36:33 19064

19064 在產品的EMC設計中,對PCB和物理結構的EMC評估,是非常重要的一環,往往還具有決定性作用。一個比較優秀的設計,應該可以較大程度地避免干擾電流流過產品內部電路,并將其導向大地。

2020-03-31 16:10:30 3071

3071

寄生的含義就是本來沒有在那個地方設計電容,但由于布線之間總是有互容,互容就好像是寄生在布線之間的一樣,所以叫寄生電容,又稱雜散電容。

2020-09-17 11:56:11 27673

27673 寄生電容是指電感,電阻,芯片引腳等在高頻情況下表現出來的電容特性。實際上,一個電阻等效于一個電容,一個電感,一個電阻的串聯,低頻情況下表現不明顯,而高頻情況下,等效值會增大。在計算中我們要考慮進去。

2020-10-09 12:04:17 34949

34949 AN39-升壓變壓器設計中的寄生電容效應

2021-04-28 17:42:25 4

4 的,今天我們就來講解一下,對于理想的MOS器件來說,我們只考慮器件本身,而不考慮MOS的寄生電容的話,那么是無需考慮驅動電流的大小的。相信大家都聽過一個名詞,叫寄生電容,也叫雜散電容,是電路中電子元件

2022-04-07 09:27:12 4967

4967

Q=CU,在相同電壓下,電容越大,所能儲存的電荷就越多。 簡單來講,任何兩個面之間都有寄生電容。但同樣,這兩個面的大小,位置關系,兩個面中間的介質材料等因素都會影響寄生電容的大小。舉個例子,變壓器的每匝導線間,都會有寄生電容,

2022-07-27 14:23:55 15292

15292

繼前篇的Si晶體管的分類與特征、基本特性之后,本篇就作為功率開關被廣為應用的Si-MOSFET的特性作補充說明。MOSFET的寄生電容:MOSFET在結構上存在下圖所示的寄生電容。

2023-02-09 10:19:24 1996

1996

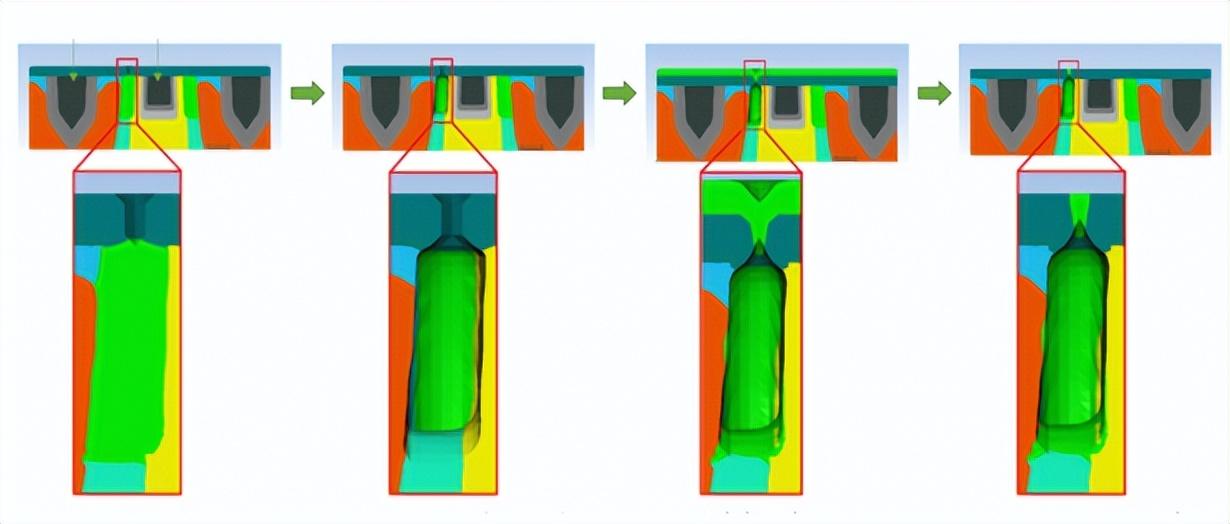

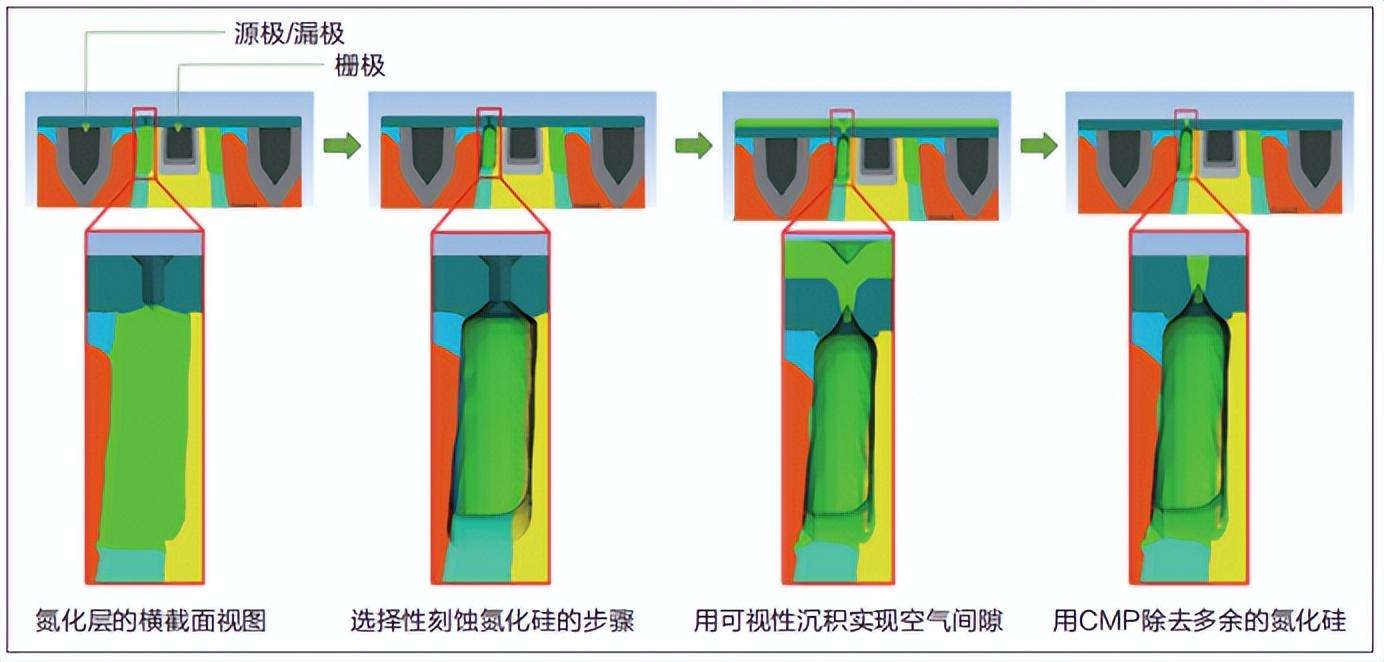

作者:泛林集團半導體工藝與整合工程師 Sumant Sarkar 使用Coventor SEMulator3D?創建可以預測寄生電容的機器學習模型 減少柵極金屬和晶體管的源極/漏極接觸之間的寄生電容

2023-03-28 17:19:08 559

559

來源:《半導體芯科技》雜志 作者:Sumant Sarkar, 泛林集團半導體工藝與整合工程師 使用Coventor SEMulator3D? 創建可以預測寄生電容的機器學習模型 減少柵極金屬

2023-06-02 17:31:46 305

305

本文要點寄生電容的定義寄生電容影響電路機理消除寄生電容的方法當你想到寄生蟲時,你可能會想到生物學上的定義——一種生活在宿主身上或在宿主體內的有機體,從宿主身上吸取食物。從這個意義上說,寄生蟲可能是

2022-05-31 11:09:01 1733

1733

使用Coventor SEMulator3D?創建可以預測寄生電容的機器學習模型

2023-07-06 17:27:02 187

187

寄生電容有一個通用的定義:寄生電容是存在于由絕緣體隔開的兩個導電結構之間的虛擬電容(通常不需要的),是 PCB 布局中的一種效應,其中傳播的信號表現得好像就是電容,但其實并不是真正的電容。

2023-07-24 16:01:36 5440

5440

pcb連線寄生電容一般多少 隨著電子產品制造技術的成熟和發展,隨之而來的是布線技術的迅速發展。不同的 PCB 布線技術對于電路性能的影響不同,而其中最常見的問題之一就是 PCB 連線寄生電容。這種

2023-08-27 16:19:44 1608

1608 許多優點,但由于它們的關斷速度受到所謂的寄生電容影響,使其對快速切換應用有限制。因此,理解寄生電容對MOS管快速關斷的影響至關重要。在本文中,我們將探討MOS管寄生電容的作用以及如何減輕其對快速關斷的影響。 MOS管的寄生電容: 在MOS管中,寄生電容產生的原因是因為當

2023-09-17 10:46:58 1244

1244 電容器的寄生作用與雜散電容

2022-12-30 09:21:51 3

3 電容器的寄生作用與雜散電容

2023-03-01 15:37:55 1

1 SiC MOSFET 和Si MOSFET寄生電容在高頻電源中的損耗對比

2023-12-05 14:31:21 258

258

寄生電容和寄生電感是指在電路中存在的非意圖的電容和電感元件。 它們通常是由于電路布局、線路長度、器件之間的物理距離等因素引起的。

2024-02-21 09:45:35 246

246

電子發燒友App

電子發燒友App

評論