簡介

電磁兼容性(EMC) 通常被定義為產品在其環境內發揮作用而不引入電磁干擾的能力。EMC合規性是將產品推向市場的必要條件。簡單地說,如果產品未通過目標市場的EMC合規性測試,則無法銷售該產品。

世界各地的監管機構均對設備被允許產生的輻射和傳導發射規定了限制。汽車和航空航天制造商甚至可能為其供應商設定了更為嚴格的標準。設計團隊非常清楚確保其產品符合EMC 規范的重要性,但許多團隊并未嘗試在設計期間執行EMC分析。

有一種看法認為,在PCBLayout 期間進行EMC分析可能是項非常耗時的任務,不僅難以設置和正確配置,而且會產生難以解釋的結果。從歷史上看,基于設計的分析一直將焦點放在信號完整性(SI) 和電源完整性(Pi) 上,而EMC“分析”則是放在完成制造并測試實際產品之后手動執行的。

人們經常忽視的一點是,在設計階段添加自動EMC 分析提供了避免在制造后出現EMC 合規性故障的機會。HyperLynx? DRC 提供了易于使用的EMC 分析功能,以及具有詳細記錄的規則檢查,其中包括對每項原則的解釋以及關于如何解決問題的建議。通過在制造前的PCBLayout 期間的適當時間點添加自動EMC分析,可以減少進行重新設計的需要,從而影響產品的開發成本和整體上市時間。

電磁兼容性可能是個令人生畏和讓人困惑的話題,特別對于新手工程師和設計人員以及那些不太精通該主題的人員更是如此。此外,有關電磁兼容性(EMC) 和電磁干擾(EMI) 之間的差異,也經常存在混淆。本文章的目的不在于提供有關EMC 和EMI 理論的深度教程,但快速回顧一下相關的定義還是非常適宜的。

如前所述,EMC 通常被定義為產品在其環境中發揮作用而不引入電磁干擾的能力。具體而言,產品必須:

■ 能夠耐受規定程度的干擾

■ 不會產生超過規定數量的干擾

■ 能夠保持自我兼容。

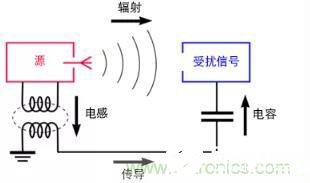

EMI 通常被定義為由于電磁感應或電磁輻射而對電路造成影響的干擾。

為進一步簡化這兩個定義:

EMC 是產品易受環境影響的程度,而EMI 則是給環境帶來的影響。

該主題非常復雜,致使人們認為,在PCB Layout 期間很難執行和解釋EMC 分析。但實際上,進行設計內分析要比等待實際產品完成制造后再進行測試更加輕松和經濟高效,因為在后一種情況下,修復問題需要投入的時間和成本要多得多。

有兩項統計數據足以證明進行設計內測試的重要性。

1. 雖然EMC 測試實驗室未被要求提供平均EMC 測試合格率,但一些研究表明,首次合格率僅約50%。

2. EMC 合規性故障被認為是導致汽車行業重新設計的第二大常見原因。

鑒于EMC 故障需要進行一次或多次重新設計,從而對產品開發成本和整體上市時間產生影響,在PCBLayout(EMC 合規性設計)期間執行EMC 分析是不可或缺的。

將EMC 分析“左移”至PCBLAYOUT 期間進行

在工程領域,術語“左移”通常用于描述將通常放在設計流程后期階段執行的任務移動(或轉移)到設計流程早期階段的行為。一般而言,轉移任務未必能夠消除流程后期對該任務的需求;其目的在于降低依賴性和改善結果。

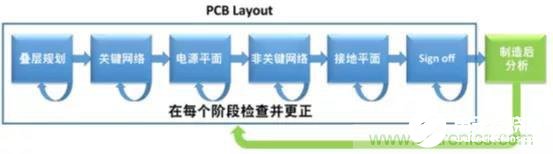

在本例中,基于制造后EMC 測試結果執行的EMC 分析將被轉移,并且還會使用HyperLynxDRC 在PCB Layout 階段的適當時間點執行。左移的目的是為工程師和設計人員提供機會,在整體設計流程的更早階段執行相關任務,最終消除迭代并確保整體流程更加高效。從根本上說,在PCBLayout 的各個階段進行的每次分析,都能令整個設計流程得到改進。應用的轉移程度越高,獲得的好處越大。

考慮典型使用案例。傳統上,工程師或設計人員會在PCB 設計期間執行一些非常簡單的手動EMC 分析,隨后依賴于制造后的EMC 測試結果來確定是否需要進行更詳細的分析。在這種設計后分析環境中檢測到的任何EMC 問題都必須回傳到設計人員采取糾正措施。完成第一組更改以解決在測試期間發現的EMC 問題后,必須制作新的設計并重新開始以上循環。

此外,人們還假設在測試期間發現的任何EMC 問題的詳細信息都是可以分析和傳達的,以便設計團隊能夠解決這些問題。這一假設的有效性將會因EMC 測試實驗室和設計團隊的專業知識水平而有所不同。

手動檢查EMC 問題不僅耗時,而且具有主觀性,可能不準確且容易出錯。通過使用HyperLynx DRC 將EMC 分析左移到自動化設計內流程后,確定和解決EMC 問題的周期時間便不再受制于外部影響。該分析越接近工程師或設計人員,運行頻率便越高,也就越容易在設計流程的更早期檢測和糾正問題。

EMC 分析_ 在早期經常運行

考慮到一項設計改進往往可以同時降低EMC 排放和敏感性,在早期PCB Layout 的適當階段經常運行分析,可以獲得顯著的優勢。許多設計團隊投入大量的精力來控制潛在的EMC/EMI 問題,而不是花時間使用分析方法來抑制它們。

如前所述,HyperLynxDRC 可通過對布局和布線執行各種EMC 和EMI 規則檢查,來支持實現最佳Layout 設計。為了最大限度減少不確定性并確保正確使用,HyperLynx DRC 的功能具有以下特點:

■ 詳細記錄每條規則

■ 解釋每條規則的原則

■ 提供包含圖表的示例,詳細說明需要的任何設置

■ 提供有關如何糾正問題的建議。

HyperLynx DRC 提供的許多EMC 檢查都會查找不容易仿真的項目,例如跨越平面分割的走線、參考平面更改、屏蔽和過孔等。在EMC/EMI 分析期間可以檢查的一些其他問題示例包括:

■ 殘留分支長度

■ 濾波器件布局

■ 分割平面上的IC

■ I/O 耦合

■ 銅皮孤島

■ 靠近平面邊緣的網絡

■ 基準電壓錯誤的走線。

對于以上每個示例,用戶無需深入了解EMC/EMI 規則便可運行自動分析。HyperLynx DRC 具有極強的自定義功能,用戶不僅可以使用其眾多的內置檢查,還可以編寫自定義設計規則檢查。

表1 是應該在PCB Layout 的不同階段使用EMC 分析來檢查的項目示例。

請注意,某些情況下,需要在PCB Layout 的多個階段檢查同一項目。但這并不意味著將同一參數檢查兩次,而是隨著設計的進展,可能需要重復進行分析。例如,考慮網絡的最大過孔數。完成關鍵網絡布線后的分析結果,在設計周期后期添加電源和接地平面以及非關鍵網絡之后可能會發生變化。

HyperLynxDRC 提供的EMC 分析結果非常準確,可以實現從結果到Layout 的交互顯示,并提供關于如何糾正問題的建議。基本規則很少需要任何設置,但更高級的規則確實需要一些設置。因此,更好的結果在一定程度上取決于設計團隊的EMC 專業知識。

總結

對于大多數工程師和設計人員來說,最大的成就莫過于在首次制造期間便生產出能夠以全速可靠工作,并且噪聲足夠低,無需使用昂貴的屏蔽和濾波便能通過EMC 合規性測試的產品。實現電磁兼容性是個重要的設計里程碑。HyperLynx DRC 將EMC 分析左移并嵌入到PCB 設計工具中,大幅降低了完成制造后出現EMC 合規性故障的可能性。

正如本文所討論的,添加自動EMC 分析不應該是個孤立事件,而應該是在PCB Layout 的適當階段發生的一系列事件,從而幫助指導工程師和設計人員獲得具有更好的EMC 性能的物理實現。在工程師與分析之間建立這種直接關系,意味著可以在PCBLayout 流程的每個階段應用支持EMC 合規性的關鍵設計決策。

在PCBLayout 流程中應用的每次EMC 分析左移,都能實現效率提升。任何左移計劃的最終目的都是讓設計系統能夠使用EMC 規則支持設計即正確的方法,以消除代價高昂的設計后迭代。

總之,通過使用HyperLynxDRC 將自動EMC 分析添加到PCBLayout,工程師和PCB 設計人員將能夠:

■ 設計具有正確EMC 性能的物理實現

■ 減少對制造后EMC 分析的依賴

■ 提高在首次制造期間通過EMC 合規性測試的可能性

■ 自動執行主觀、耗時而且可能容易出錯的手動過程

■ 減少或消除設計周期后期的返工。

當然,以上優勢還只是初期可以實現的優勢。與任何新技術一樣,轉型將會分階段進行。最初,設計團隊可能只關注一些精選的最關鍵、最容易出錯和導致誤解的基本規則。隨著設計團隊逐漸熟悉HyperLynxDRCEMC 規則檢查,他們肯定也會努力強化其流程,從而提高相關產品的時效性、準確性和質量。

目的是持續改進流程。最后,將自動EMC 分析添加到PCB Layout 對于產品開發團隊和制造團隊來說都是一個勝利,它能提高質量,降低成本并縮短產品上市時間。

責任編輯;zl

電子發燒友App

電子發燒友App

評論