前面我們分析了EMI的產(chǎn)生情況,這節(jié)里我們將針對高速PCB設(shè)計,來分析如何進(jìn)行EMI控制。

2012-03-31 11:07:14 1590

1590 隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決

2015-09-05 14:29:00 1691

1691

解決EMI問題的辦法很多,現(xiàn)代的EMI抑制方法包括:利用EMI抑制涂層、選用合適的EMI抑制零配件和EMI仿真設(shè)計等。本文從最基本的PCB布板出發(fā),討論PCB分層堆疊在控制EMI輻射中的作用和設(shè)計技巧。

2016-01-20 10:03:57 3541

3541 隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是高速PCB設(shè)計抗EMI干擾的九大規(guī)則: 規(guī)則一:高速

2018-04-13 08:20:00 1567

1567

隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。

2022-11-04 10:10:41 708

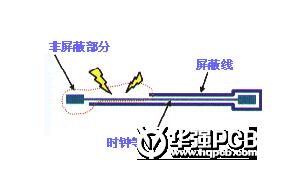

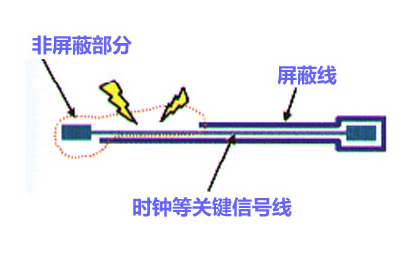

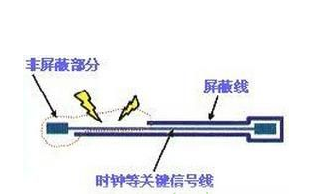

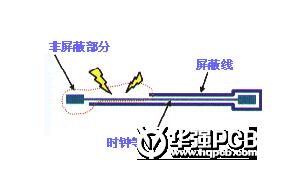

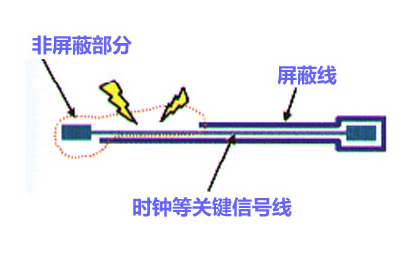

708 、高速信號走線屏蔽規(guī)則如上圖所示:在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,則需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。2...

2021-12-31 06:22:08

EMI問題是很多工程師在PCB設(shè)計遇到的最大挑戰(zhàn),由于電子產(chǎn)品信號處理頻率越來越高,EMI問題日益顯著,雖然有很多書籍對EMI問題進(jìn)行了探討,但是都不夠深入,《PCB設(shè)計中EMI控制原理與實(shí)戰(zhàn)

2011-05-19 15:58:44

,改進(jìn)了PCB設(shè)計的流程,簡化后期硬件調(diào)試中許多繁雜的工作。同時,IC內(nèi)部也要充分考慮到EMC/EMI的問題。目前,大部分芯片廠商都會處理好IC內(nèi)部的EMC/EMI的問題。但廣大的設(shè)計者也應(yīng)當(dāng)留意芯片

2014-12-22 11:52:49

PCB設(shè)計中跨分割的處理高速信號布線技巧

2021-02-19 06:27:15

(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2019-06-21 06:28:33

,不可避免地會引入EMC(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計相比,PCB設(shè)計過程中的EMC分析和模擬仿真是一個薄弱環(huán)節(jié)。

2019-07-22 06:45:44

設(shè)計,一些心得和大家交流、交流。規(guī)則一、高速信號走線屏蔽規(guī)則如上圖所示:在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線

2021-03-31 06:00:00

通過高速PCB來控制解決。做了4年的EMI設(shè)計,一些心得和大家交流、交流。規(guī)則一、高速信號走線屏蔽規(guī)則 如上圖所示:在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只

2022-04-18 15:22:08

高速PCB設(shè)計系列課:入門篇:林超文PCB設(shè)計PADS和OrCAD實(shí)操指南http://t.elecfans.com/topic/22.html?elecfans_trackid=bbspost

2015-05-05 09:30:27

隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。

2023-09-25 08:04:42

隨著信號上升沿時間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則:

2019-07-25 06:56:17

高速PCB設(shè)計中的電磁輻射檢測技術(shù),總結(jié)的太棒了

2021-04-25 07:38:23

高速PCB設(shè)計中的若干誤區(qū)與對策

2012-08-20 14:38:56

黑魔書,高速PCB設(shè)計經(jīng)典,推薦給需要的你!

2016-01-15 14:15:35

阻抗匹配阻抗匹配是指在能量傳輸時,要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計中,阻抗的匹配與否關(guān)系到信號的質(zhì)量優(yōu)劣。

2019-05-31 08:12:33

高速PCB設(shè)計之一 何為高速PCB設(shè)計電子產(chǎn)品的高速化、高密化,給PCB設(shè)計工程師帶來新的挑戰(zhàn)。PCB設(shè)計不再是產(chǎn)品硬件開發(fā)的附屬,而成為產(chǎn)品硬件開發(fā)中“前端IC,后端PCB,SE集成”3個環(huán)節(jié)中

2014-10-21 09:41:25

`請問高速PCB設(shè)計前期的準(zhǔn)備工作有哪些?`

2020-04-08 16:32:20

電路應(yīng)具備信號分析、傳輸線、模擬電路的知識。錯誤的概念:8kHz幀信號為低速信號。 問:在高速PCB設(shè)計中,經(jīng)常需要用到自動布線功能,請問如何能卓有成效地實(shí)現(xiàn)自動布線? 答:在高速電路板中,不能只是看

2019-01-11 10:55:05

高速PCB設(shè)計指南

2012-08-12 13:09:35

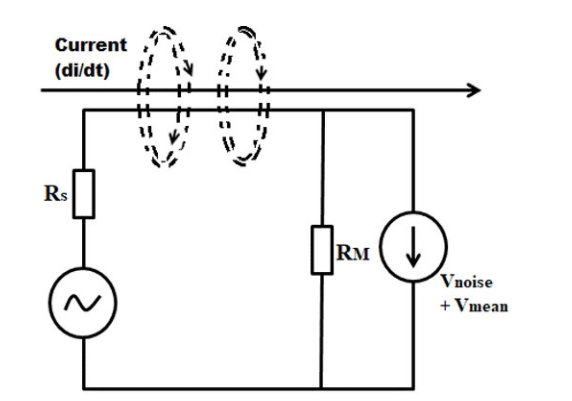

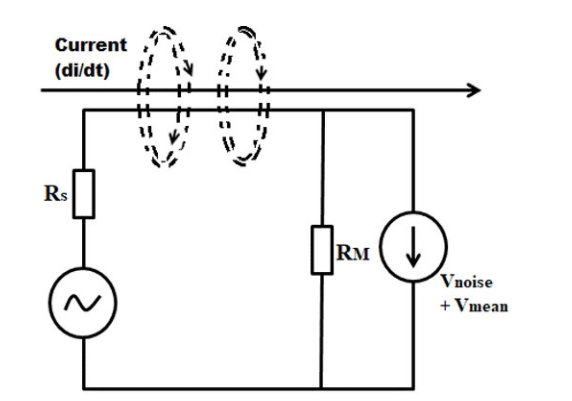

)。 如果在高速PCB設(shè)計中對EMC/EMI予以重視,將有助縮短産品研發(fā)周期加快産品上市時間。 EMC的三要素爲(wèi)輻射源,傳播途徑和受害體。傳播途徑分爲(wèi)空間輻射傳播和電纜傳導(dǎo)。所以要抑制諧波,首先看看它

2012-10-17 15:59:48

本帖最后由 eehome 于 2013-1-5 09:53 編輯

高速PCB設(shè)計已成為數(shù)字系統(tǒng)設(shè)計中的主流技術(shù),PCB的設(shè)計質(zhì)量直接關(guān)系到系統(tǒng)性能的好壞乃至系統(tǒng)功能的實(shí)現(xiàn)。針對高速PCB

2012-03-31 14:29:39

`請問高速PCB設(shè)計規(guī)則有哪些?`

2020-02-25 16:07:38

規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地

2016-01-19 22:50:31

在高速pcb設(shè)計中,經(jīng)常聽到要求阻抗匹配。而設(shè)計中導(dǎo)致阻抗不匹配的原因有哪些呢?一般又對應(yīng)著怎么的解決方案?歡迎大家來討論

2014-10-24 13:50:36

高速PCB設(shè)計指南之(一~八 )目錄2001/11/21CHENZHI/LEGENDSILICON一、1、PCB布線2、PCB布局3、高速PCB設(shè)計二、1、高密度(HD)電路設(shè)計2、抗干擾技術(shù)3

2012-07-13 16:18:40

《Cadence Allegro實(shí)戰(zhàn)攻略與高速PCB設(shè)計》基本信息作者: 杜正闊 高寶君 何宗明 叢書名: EDA精品智匯館出版社:電子工業(yè)出版社ISBN:9787121284724上架時間

2017-08-11 17:11:31

在pcb設(shè)計中FPGA與高速并行DAC的布線應(yīng)該注意什么?

2023-04-11 17:30:54

在高速PCB設(shè)計中,過孔有哪些注意事項?

2021-04-25 09:55:24

圖解在高速的PCB設(shè)計中的走線規(guī)則

2021-03-17 07:53:30

高速PCB設(shè)計的基本內(nèi)容是什么高速PCB的設(shè)計方法是什么

2021-04-27 06:33:07

在高速PCB設(shè)計時為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計時怎樣來考慮這個問題?另外關(guān)于IBIS模型,不知在那里能提供比較準(zhǔn)確的IBIS

2012-03-03 12:41:55

解決高速PCB設(shè)計信號問題的全新方法

2021-04-25 07:56:35

高速數(shù)字PCB設(shè)計信號完整性解決方法

2021-03-29 08:12:25

在PCB設(shè)計中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計中避免出現(xiàn)電磁問題。

2021-02-01 07:42:30

EMI的輻射干擾是PCB設(shè)計中的一大關(guān)鍵,更別說是高速PCB的設(shè)計了。而關(guān)于EMI的產(chǎn)生理論上工程師應(yīng)該都是很清楚的,并且也都知道一些普遍的關(guān)于抑制EMI的手段和方式。這里將為大家分享的是針對高速

2019-05-20 08:30:00

引言 隨著IC 器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC /EMI設(shè)計的觀點(diǎn)來看,在設(shè)備的PCB設(shè)計階段處理好EMC/EMI

2018-09-14 16:32:58

在一般的非高速PCB設(shè)計中,我們都是認(rèn)為電信號在導(dǎo)線上的傳播是不需要時間的,就是一根理想的導(dǎo)線,這種情況在低速的情況下是成立的,但是在高速的情況下,我們就不能簡單的認(rèn)為其是一根理想的導(dǎo)線了,電信號

2019-05-30 06:59:24

深入了解PCB設(shè)計,并且合理利用。熱門PCB設(shè)計技術(shù)方案:PCB設(shè)計的核心與解決方案高速PCB中電源完整性的設(shè)計闡述DFM技術(shù)在PCB設(shè)計中的應(yīng)用闡述高速DSP系統(tǒng)的電路板級電磁兼容性設(shè)計高速PCB

2014-12-16 13:55:37

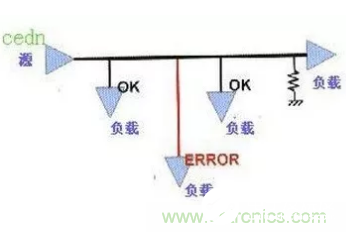

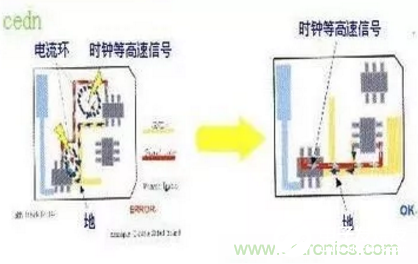

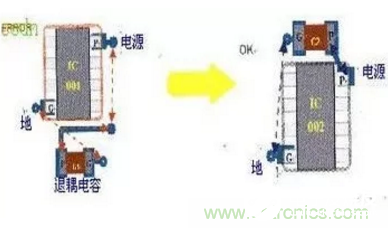

的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。規(guī)則二:高速信號的走線閉環(huán)規(guī)則由于PCB板的密度越來越高

2017-11-02 12:11:12

什么是高速pcb設(shè)計高速線總體規(guī)則是什么?

2019-06-13 02:32:06

高速PCB設(shè)計指南之(一~八 )目錄 2001/11/21 一、1、PCB布線2、PCB布局3、高速PCB設(shè)計

二、1、高密度(HD)電路設(shè)計2、抗干擾技術(shù)

2008-08-04 14:14:42 0

0 高速PCB設(shè)計的疊層問題

2009-05-16 20:06:45 0

0 電容在高速PCB設(shè)計中的應(yīng)用:探討高速PCB設(shè)計電容的應(yīng)用。電容是電路板上不可缺少的一個部分,并且起到了至關(guān)重要的作用,探討他具備至關(guān)重要的價值。您在設(shè)計中是否有這樣

2009-08-16 13:11:56 0

0 高速PCB設(shè)計時應(yīng)從哪些方面考慮EMC、EMI的規(guī)則

一般EMI/EMC 設(shè)計時需要同時考慮輻射(radiated)與傳導(dǎo)(conducted)兩個方面,前者歸屬于頻率較高的

2009-03-20 14:05:36 1360

1360 高速PCB設(shè)計指南之一

第一篇 PCB布線在PCB設(shè)計中,布線是完成產(chǎn)品設(shè)計的重要步驟,可以說前面的準(zhǔn)備工作都是為它而做

2009-11-11 14:57:48 600

600 高速PCB設(shè)計指南之七

第一篇 PCB基本概念

1、“層(Layer) ”的概念 與字處理或其它許多

2009-11-11 15:07:15 433

433 高速PCB設(shè)計指南之八

第一篇 掌握IC封裝的特性以達(dá)到最佳EMI抑制性能

將去耦電容直接放在IC封裝內(nèi)可以

2009-11-11 15:07:54 464

464 高速PCB抄板與PCB設(shè)計方案

目前高速PCB的設(shè)計在通信、計算機(jī)、圖形圖像處理等領(lǐng)域應(yīng)用廣泛。而在這些領(lǐng)域工程師們用的高速PCB

2009-11-18 14:11:47 824

824 基于Cadence的高速PCB設(shè)計

隨著人們對通信需求的不斷提高,要求信號的傳輸和處理的速度越來越快.相應(yīng)的高速PCB的應(yīng)用也越來越廣,設(shè)計也越來越

2009-12-12 17:50:27 954

954 高速PCB 設(shè)計已成為數(shù)字系統(tǒng)設(shè)計中的主流技術(shù),PCB的設(shè)計質(zhì)量直接關(guān)系到系統(tǒng)性能的好壞乃至系統(tǒng)功能的實(shí)現(xiàn)。針對高速PCB的設(shè)計要求,結(jié)合筆者設(shè)計經(jīng)驗,按照PCB設(shè)計流程,對PCB設(shè)計

2011-08-30 15:44:23 0

0 目前,EMI問題是很多工程師在PCB設(shè)計遇到的最大挑戰(zhàn),由于電子產(chǎn)品信號處理頻率越來越高,EMI問題日益顯著,雖然有很多書籍對EMI問題進(jìn)行了探討,但是都不夠深入,《PCB設(shè)計中EMI控

2011-09-05 14:29:17 0

0 簡要闡述了高速PCB設(shè)計的主要內(nèi)容, 并結(jié)合Cadence軟件介紹其解決方案比較了傳統(tǒng)高速設(shè)計方法與以Cadence為代表的現(xiàn)代高速PCB設(shè)計方法的主要差異指出在進(jìn)行高速設(shè)計過程中必須借助于

2011-11-21 16:53:58 0

0 理論研究和實(shí)踐都表明,對高速電子系統(tǒng)而言,成功的PCB設(shè)計是解決系統(tǒng)EMC問題的重要措施之一.為了滿足EMC標(biāo)準(zhǔn)的要求,高速PCB設(shè)計正面臨新的挑戰(zhàn),在高速PCB設(shè)計中,設(shè)計者需要糾正或放棄

2011-11-23 10:25:41 0

0 高速PCB設(shè)計技術(shù)(中文)

2011-12-02 14:16:44 161

161 高速PCB設(shè)計指南,大家自己有需要的趕緊下載吧,機(jī)不可失

2015-10-27 14:09:28 0

0 高速PCB設(shè)計指南.........................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計指南............................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計指南.......................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計指南,好資料,又需要的下來看看

2017-01-12 12:18:20 0

0 如何快速解決PCB設(shè)計EMI問題

2017-01-14 12:48:43 0

0 高速PCB設(shè)計電容的應(yīng)用

2017-01-28 21:32:49 0

0 高速訊號會導(dǎo)致PCB板上的長互連走線產(chǎn)生傳輸線效應(yīng),它使得PCB設(shè)計者必須考慮傳輸線的延遲和阻抗搭配問題,因為接收端和驅(qū)動端的阻抗不搭配都會在傳輸在線產(chǎn)生反射訊號,而嚴(yán)重影響到訊號的完整性。另一方面

2018-05-22 07:18:00 5034

5034 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-03-15 14:05:42 4494

4494

隨著,信號上升沿時間的減小,信號頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的光注。高速PCB設(shè)計的成功,對EMI的貢獻(xiàn)越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2019-06-05 14:56:36 587

587

在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 高速PCB設(shè)計EMI有什么規(guī)則

2019-08-21 14:38:03 807

807

低EMI DC/DC變換器PCB設(shè)計

2020-02-04 15:26:08 3835

3835 如上圖所示:在PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2

2020-06-05 10:54:04 2839

2839 高速PCB設(shè)計是指信號的完整性開始受到PCB物理特性(例如布局,封裝,互連以及層堆疊等)影響的任何設(shè)計。而且,當(dāng)您開始設(shè)計電路板并遇到諸如延遲,串?dāng)_,反射或發(fā)射之類的麻煩時,您將進(jìn)入高速PCB設(shè)計領(lǐng)域。

2020-06-19 09:17:09 1537

1537 PCB設(shè)計布局被認(rèn)為是促進(jìn)EMI在電路中傳播的主要問題之一。這就是為什么在開關(guān)電源中降低EMI的普遍而通用的技術(shù)之一是布局優(yōu)化。

2021-01-28 10:58:06 2089

2089

下文是硬件工程師在PCB設(shè)計早期容易忽略,卻很有用的幾個EMI設(shè)計指南,這些指南也在一些權(quán)威書刊中常常被提到。

2020-10-09 09:54:57 3137

3137 在高速PCB設(shè)計中,差分信號的應(yīng)用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強(qiáng)、能有效抑制EMI、時序定位精確的優(yōu)勢。

2021-03-23 14:40:47 2761

2761 PCB設(shè)計之在真實(shí)世界里的EMI控制說明。

2021-06-23 14:53:34 0

0 在進(jìn)行PCB設(shè)計時,我們經(jīng)常會遇到各種各樣的問題,如阻抗匹配、EMI規(guī)則等。本文為大家整理了一些和高速PCB相關(guān)的疑難問答,希望對大家有所幫助。

2022-08-11 08:55:42 2133

2133 隨著信號上升沿時間的減小,信號頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的重視。高速pcb設(shè)計的成功,對EMI的貢獻(xiàn)越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2022-11-11 11:44:51 528

528 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,則需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2022-12-14 10:04:00 292

292 高速PCB設(shè)計指南之七

2022-12-30 09:22:13 4

4 高速PCB設(shè)計指南之五

2022-12-30 09:22:14 3

3 高速PCB設(shè)計指南之八

2022-12-30 09:22:14 5

5 高速PCB設(shè)計指南之六

2022-12-30 09:22:15 3

3 高速PCB設(shè)計指南之四

2022-12-30 09:22:15 4

4 高速PCB設(shè)計指南二

2022-12-30 09:22:16 5

5 高速PCB設(shè)計電容的應(yīng)用

2022-12-30 09:22:16 29

29 高速PCB設(shè)計的疊層問題

2022-12-30 09:22:17 37

37 高速PCB設(shè)計電容的應(yīng)用

2023-03-01 15:37:57 2

2 PCB設(shè)計之高速電路

2023-12-05 14:26:22 290

290

電子發(fā)燒友App

電子發(fā)燒友App

評論