1,布局

2,布線(串?dāng)_, 阻抗匹配)

3,電源去藕

4,信號的濾波和防護(hù)

5,安規(guī)

移動無線電輻射

布局

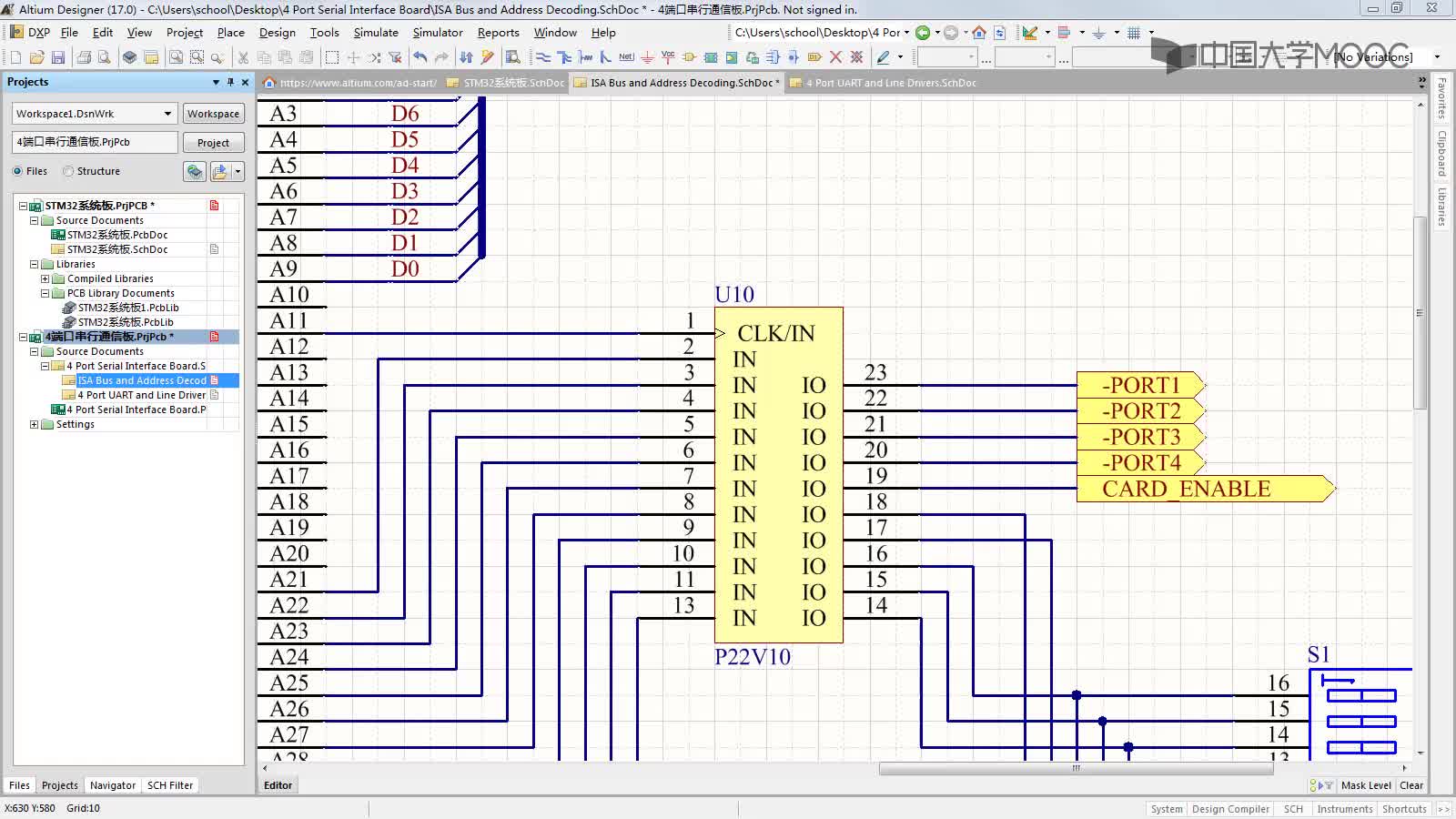

疊層結(jié)構(gòu):嚴(yán)格控制特性阻抗在規(guī)范范圍內(nèi),保證走線到參考層的距離小于到其他層的距離,這是板級EMC設(shè)計的前提。參考面盡量完整,高速信號最好參考GND。

高速電路和低速電路,數(shù)字電路和模擬電路,IO電路,盡量都有自己的區(qū)域,避免重疊。

按照功能模塊的方式劃分區(qū)域,盡量避免區(qū)域重疊、

宏照片的電子線路。多氯聯(lián)苯在照明

布局要求:

1,高頻信號與輸入輸出信號分開。

3,相關(guān)的功能模塊靠近連接器放置。

4,走線層到參考層的距離小于到其他層的距離。

5,壓板結(jié)構(gòu)必須保證走線的特性阻抗在規(guī)范范圍內(nèi)。

布線

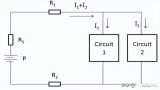

布線的一個指導(dǎo)原則,電流必須構(gòu)成一個完整回路的,所以我們必須要人為給其設(shè)置一個路徑,讓它按照我們想要的路徑來走,并且,讓這個回路的面積盡量小。

正向的電流路徑是我們實際Lay的線,那么其反向的回流路徑呢。

高頻信號的地線電流總是會選擇阻抗Z(不是電阻R)最小的路徑走,這條路徑并不是終端到源端的直線路徑(電阻R最小),而是走線在參考層上鏡像路徑(阻抗Z最小),也就是走線在其相鄰參考平面上投影的路徑。我們要做的就是保證這條路徑連續(xù),這樣其構(gòu)成的環(huán)路面積就是最小的,產(chǎn)生的電磁波輻射就是最小。

信號的回路要做到真正的全部連續(xù),不只是走線部分,還包括源端和終端,甚至要考慮到IC內(nèi)部。

信號的回流:

高速信號的回流電流并不是完全分別在信號線的正下方,而是按一定的電流密度分布在其正下方及兩側(cè),其正下方的電流密度最大,往兩側(cè)遞減,如果信號太靠近板邊,就會有部分回流電流通過空間輻射的形式返回源端,這樣就造成電磁輻射。

布線規(guī)則:

1,高速信號參考完整的參考面,不得有跨島;

2,與其島邊(電源島,地島)間距至少3W;

3,對于分割了GND_Chassis的IO口,每個IO口都要有GND到GND_Chassis的電容。

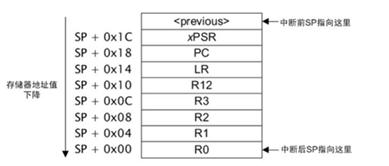

那些情況會導(dǎo)致回路不連續(xù):換層,跨島,參考層不完整。

換層分幾種情況:信號換層但參考面不變,參考面改變但其屬性不變,參考面改變且其屬性也改變。

跨島:走線在參考面的投影區(qū)銅皮沒有連續(xù)(示意圖如下)。

布線規(guī)則:

在兩個地層直接換層加地釘;

地釘或過孔電容與換層過孔間距最大不能超過3W;

換層過孔應(yīng)在參考平面內(nèi),而不能在參考平面之外或邊緣;

前提條件,面臨過孔或跨島的選擇時,應(yīng)選擇過孔;

時鐘信號不允許跨島。

時鐘信號、高速信號與其他信號線間距至少3W;

時鐘信號,高速信號走線不得穿過高速、大功率等器件,以及不能穿過IO連接器和插槽下方;

時鐘芯片,時鐘Buffer等高速器件下方不能有其他信號穿過;

時鐘信號力IO連接器側(cè)板邊300mil以上,在其他位置離板邊200mil以上;

自身有繞線時(比如蛇形繞線),線間距至少5W;

走線不得與IO線并行走線,且線間距至少5W;

時鐘線盡可能在內(nèi)層走線;

差分對于差分對之間間距保證20mil以上;

按照信號流向走線,濾波器和變壓器的初、次級信號走線不可重疊,蛇形繞線的走線也有此要求;

RGB型號與其他信號線和島邊(電源島,地島)間距至少5W;

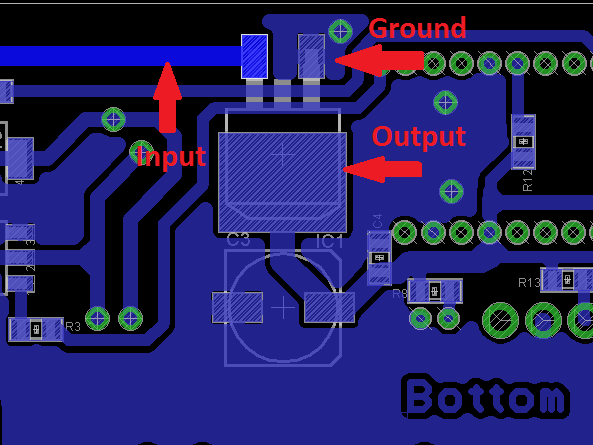

IO電路從連接器往里看,要先進(jìn)過防護(hù)器件,然后再是濾波電路,且都需要靠近連接器。

高速信號在經(jīng)過濾波器件和防護(hù)器件的時候,要按照信號流向依次通過,不能出現(xiàn)分支走線,如 ,RGB信號要從防護(hù)IC的PIN腳上穿過,不能單獨引分支線到防護(hù)IC上。

時鐘信號線可以在參考平面進(jìn)行切換,但切換次數(shù)需要盡量可能控制在3次以內(nèi);

時鐘信號的源端匹配電阻要靠近時鐘輸出腳放置;

RGB信號的阻抗匹配,要按照芯片的設(shè)計指導(dǎo)設(shè)計;

走線拐彎使用鈍角,不能使用直角和銳角;

高速信號和時鐘信號不能出現(xiàn)沒有端接的情況,特別是預(yù)留方案時,信號的兩端都有預(yù)留有0歐姆電阻。

串?dāng)_:

信號走線間距如果太小,由于走線之間的分布電容影響,信號線之間的高頻信號會相互串?dāng)_,影響信號質(zhì)量,造成EMC問題。

特別是IO信號,如果串?dāng)_到了高頻的噪聲,就很容易通過外設(shè)引線造成嚴(yán)重的輻射。

信號線之間的分布電容與走線的間距,并行走線的長度,正對面積等因素有關(guān),因此為了減少信號線之間的串?dāng)_,應(yīng)該增大走線間距,減少并行走線的長度。相鄰走線層要避免并行走線,因為其分布電容也很大,原則上要求垂直走線。

串?dāng)_的程度除了與分布電容有關(guān)外,還和信號的頻率、幅度有關(guān),這就是為什么高頻信號更容易發(fā)生串?dāng)_。

阻抗匹配

對于高速信號來說,其走線路徑都要求阻抗匹配,阻抗不匹配時會在阻抗不連續(xù)點產(chǎn)生反射,從而會影響信號質(zhì)量,產(chǎn)生EMC問題。

如果一組信號從源端-走線-終端這樣一個路徑上,源端阻抗=走線的特性阻抗=終端阻抗,這種理想情況下就不會發(fā)生反射。可以這樣理解,阻抗變化越大,信號反射就越大,產(chǎn)生的EMC問題也就越嚴(yán)重,分支走線,終端空載等情況都是很嚴(yán)重的阻抗不匹配。

電源去耦

功能模塊之間(芯片之間),電源和地時共用的,模塊工作時產(chǎn)生的噪聲很容易通過這兩個公共的路徑相互耦合,造成嚴(yán)重的EMC問題。

地往往會做到很大的面積,而且是單獨的一層,這樣相對來說比較干凈(噪聲非常小)。

電源則需要去藕,保證電路工作時不對其他電路產(chǎn)生影響。

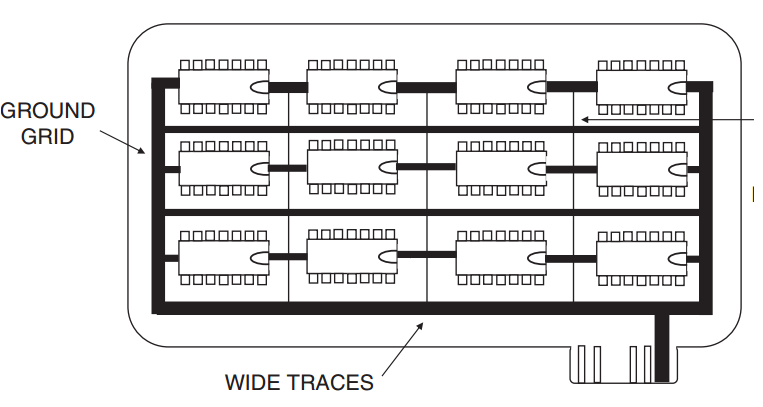

為了保證電容的濾波效果,電容到電源或地的阻抗Z必須盡量小。

對于走線的電源,保證每個電源PIN腳都有一個0.1uF的電容,走線要加粗。

對于BGA的芯片,則四個角上分布0.1uF,0.01uF的電容至少各一個。

電源的濾波電路參照原理圖放置,電容和磁珠盡量靠近芯片放置。

濾波電容盡可能直接打孔到地層,如果必須使用走線時,走線要保證短而粗。

一個到電源或地的過孔最多允許兩個電容使用。

信號的濾波與防護(hù)

IO信號一般都需要接上外設(shè)使用,而外設(shè)一般都有比較長的連線,如果IO信號(包括電源和地)上帶有高頻噪聲,就很容易通過 外設(shè)連線向空間產(chǎn)生較大的輻射,因此,IO信號都需要經(jīng)過濾波。

為了避免經(jīng)過濾波后的信號在板內(nèi)遭到二次污染,所以濾波電路要靠近端口放置。

外界設(shè)備也容易引入外來的干擾,甚至是破壞性的干擾,因此,都需要使用防護(hù)器件,且要放在濾波電路前,防止破壞性干擾使濾波電路失效。

安規(guī)

安規(guī):有電氣隔離要求的線路之間,必須能耐受規(guī)定的電壓而不發(fā)生絕緣損壞。

設(shè)定規(guī)則:屬于不同線路的銅(via trace shape pad)要保證一定的airgap距離,以耐受規(guī)定電壓。

同層:外層絕緣介質(zhì)為空氣,擊穿電壓強(qiáng)度為3KV/mm。內(nèi)層絕緣介質(zhì)為FR4。

不同層:絕緣介質(zhì)為FR4,擊穿電場強(qiáng)度為15KV/mm。!!!注意考慮電場分布的非均勻性。

電子發(fā)燒友App

電子發(fā)燒友App

評論