在數(shù)字電路中,凡是任一時(shí)刻的穩(wěn)定輸出不僅決定于該時(shí)刻的輸入,而且還和電路原來狀態(tài)有關(guān)者都叫時(shí)序邏輯電路。時(shí)序邏輯電路結(jié)構(gòu)示意圖如圖2-41所示。時(shí)序邏輯電路的狀態(tài)是靠具有存儲功能的觸發(fā)器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 53526

53526

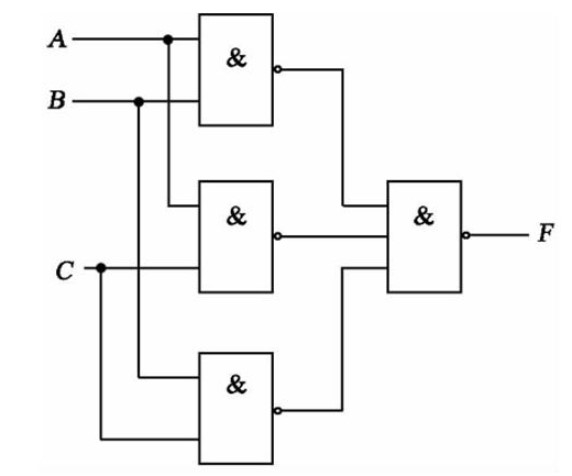

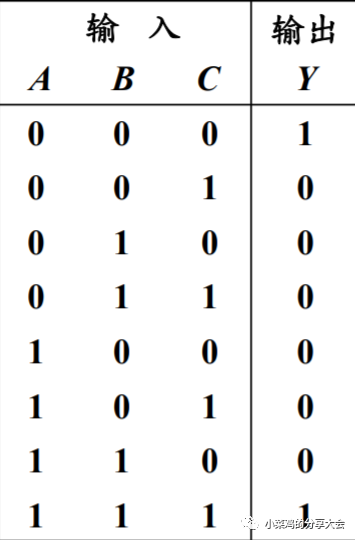

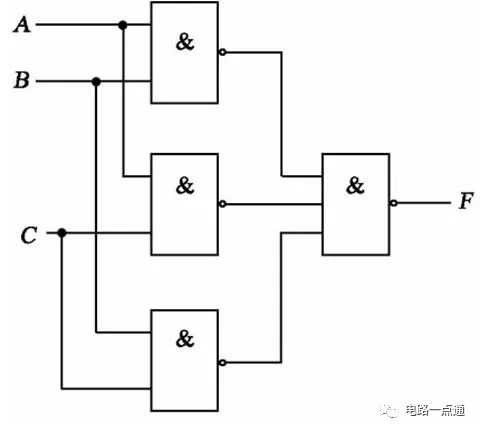

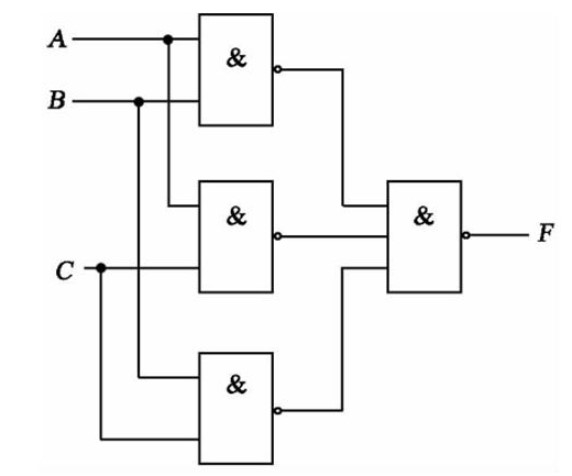

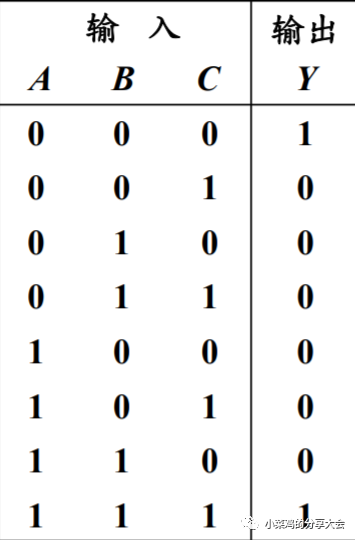

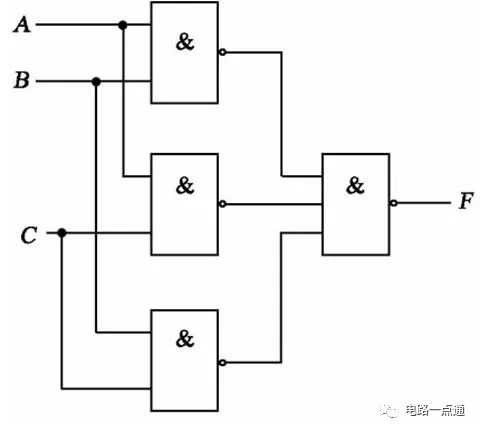

分析組合邏輯電路的目的是,對于一個(gè)給定的邏輯電路,確定其邏輯功能。

2020-08-04 15:50:00 32562

32562 主要介紹幾種邏輯電路的高速特性包括 ITL 邏輯電路、 CMOS 邏輯電路、 ECL 邏輯電0路,和 LVDS 器件的基本結(jié)構(gòu)、 工作原理和特點(diǎn),以及邏輯門電路的使用規(guī)則 。

2023-09-25 14:46:09 629

629

邏輯門及組合邏輯電路實(shí)驗(yàn)實(shí)驗(yàn)?zāi)康?. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態(tài)門的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計(jì)和實(shí)現(xiàn)方法。4.

2008-09-25 17:28:34

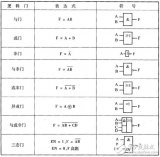

邏輯電路主要邏輯門電路之間的關(guān)系是怎樣的

2020-04-15 17:53:30

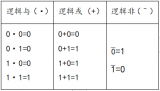

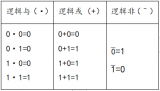

介紹一些邏輯電路的基礎(chǔ)知識。 1.邏輯代數(shù) 邏輯代數(shù)中的變量稱為邏輯變量,用大寫字母表示。邏輯變量的取值只有兩種,即邏輯0和邏輯1,0 和 1 稱為邏輯常量,并不表示數(shù)量的大小,而是表示兩種對立

2020-12-23 17:25:49

邏輯電路的糾錯(cuò)技術(shù)是如何實(shí)現(xiàn)的?糾錯(cuò)技術(shù)在邏輯電路中有什么作用?

2021-06-18 09:50:31

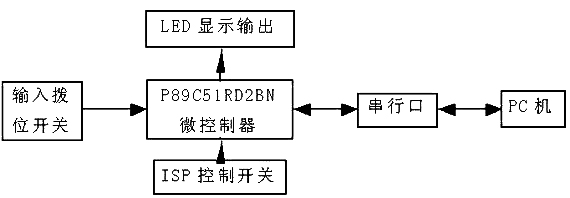

CPLD邏輯電路

2019-10-29 09:10:54

FPGA則應(yīng)該理解為可用電腦編輯的數(shù)字邏輯電路集成芯片,其實(shí)是在描繪一個(gè)數(shù)字邏輯電路。關(guān)于兩者的區(qū)別在于以下:1、速度上(兩者最大的差別)因?yàn)镕PGA是硬件電路,運(yùn)行速度則取決于晶振速度,系統(tǒng)

2021-07-13 08:43:08

組合邏輯電路。下圖即是組合邏輯電路的一般框圖,它可用如下的邏輯函數(shù)來描述,即 Li=f(A1,A2,…,An) (i=1,2,…,m) 式中 A1,A2,…,An為輸入變量。組合邏輯電路具有如下特點(diǎn)

2009-04-07 10:54:26

fpga時(shí)序邏輯電路的分析和設(shè)計(jì) 時(shí)序邏輯電路的結(jié)構(gòu)及特點(diǎn)時(shí)序邏輯電路——任何一個(gè)時(shí)刻的輸出狀態(tài)不僅取決于當(dāng)時(shí)的輸入信號,還與電路的原狀態(tài)有關(guān)。[hide][/hide]

2012-06-20 11:18:44

`內(nèi)容簡介本書是“實(shí)用電子電路設(shè)計(jì)叢書”之一。本書以實(shí)現(xiàn)高速高可靠性的數(shù)字系統(tǒng)設(shè)計(jì)為目標(biāo),以完全同步式電路為基礎(chǔ),從技術(shù)實(shí)現(xiàn)的角度介紹ASIC邏輯電路設(shè)計(jì)技術(shù)。內(nèi)容包括:邏輯門電路、邏輯壓縮、組合

2018-04-03 17:14:16

FPGA的邏輯電路基礎(chǔ)知識四、邏輯值 邏輯0:表示低電平,對應(yīng)GND。 邏輯1:表示高電平,對應(yīng)VCC。 邏輯X:表示未知,可能高電平,可能低電平。 邏輯Z:表示高阻態(tài),外部沒有激勵(lì)信號,懸空狀態(tài)

2019-12-10 20:32:03

為什么FPGA可以用來實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

2023-04-23 11:53:26

Verilog程序模塊的結(jié)構(gòu)是由哪些部分組成的?如何去實(shí)現(xiàn)時(shí)序邏輯電路和組合邏輯電路的設(shè)計(jì)呢?

2021-11-03 06:35:57

“ 1”。結(jié)果是組合邏輯電路沒有反饋,并且施加到其輸入的信號的任何變化都會立即對輸出產(chǎn)生影響。換句話說,在組合邏輯電路中,輸出始終取決于其輸入的組合。因此,組合電路是無記憶的。因此,如果其輸入條件之一從

2021-01-19 09:29:30

;nbsp; 組合邏輯電路設(shè)計(jì)中應(yīng)注意的問題 3.2 算術(shù)運(yùn)算電路 3.2.1 半加器電路

2008-05-15 21:57:28

時(shí)序邏輯電路的特點(diǎn)

2019-10-08 05:34:53

時(shí)序邏輯電路的設(shè)計(jì)實(shí)驗(yàn)1 進(jìn)一步強(qiáng)化EDA仿真軟件的使用;2 掌握利用MSI

2009-03-19 15:10:18

電路給我們的感覺總是枯燥無味的,讓人感覺高深莫測的一門學(xué)科。然而,正是這們學(xué)科在不斷的改造我們的生活,我們也無時(shí)無刻不再感嘆他的奇妙,有時(shí)我們在不知不覺中也感受到他的樂趣。這便是簡單邏輯電路在生活中

2018-07-12 13:03:30

邏輯關(guān)系表示出來;了解了這兩種邏輯電路的分析方法之后,為了加深理解,往往可以通過一個(gè)實(shí)際的設(shè)計(jì)任務(wù)來實(shí)現(xiàn)。在實(shí)踐中檢驗(yàn)理論知識,通過實(shí)踐理解各個(gè)基本芯片的工作原理與結(jié)論,同時(shí)還可以加強(qiáng)自己的實(shí)踐動(dòng)手能與

2021-11-18 06:30:00

組合邏輯電路PPT電子教案學(xué)習(xí)要點(diǎn): 組合電路的分析方法和設(shè)計(jì)方法 利用數(shù)據(jù)選擇器和譯碼器進(jìn)行邏輯設(shè)計(jì)的方法 加法器、編碼器、譯碼器等中

2009-09-16 16:05:29

組合邏輯電路 一、實(shí)驗(yàn)?zāi)康? 1. 加深理解組合邏輯電路

2009-09-16 15:09:13

組合邏輯電路實(shí)驗(yàn)實(shí)驗(yàn)三 組合邏輯電路一、 實(shí)驗(yàn)?zāi)康?、 掌握組合邏輯電路的功能測試2、 驗(yàn)證半加器和全加器的邏輯功能3、 學(xué)會

2009-03-20 18:11:09

邏輯電路中,輸出始終取決于其輸入的組合。因此,組合電路是無記憶的。 因此,如果其輸入條件之一從0-1或1-0改變狀態(tài),則默認(rèn)情況下,組合邏輯電路的結(jié)果輸出也將在其設(shè)計(jì)中具有“無內(nèi)存”,“時(shí)序”或“反饋回路

2020-12-31 17:01:17

組合邏輯電路的設(shè)計(jì)及實(shí)驗(yàn)

2009-10-10 11:44:49

后續(xù)知識點(diǎn)的學(xué)習(xí)帶來困難。根據(jù)多年的教學(xué),發(fā)現(xiàn)教師在教學(xué)中強(qiáng)調(diào)數(shù)字邏輯電路的特點(diǎn)對于學(xué)生在數(shù)字邏輯電路這門課程的學(xué)習(xí)起到至關(guān)重要的作用。本文將這一思想具體落實(shí)到數(shù)字邏輯電路課程的各個(gè)知識點(diǎn)上,希望能幫助

2010-05-13 09:11:16

組合邏輯電路的基本模塊是什么?時(shí)序邏輯電路怎樣進(jìn)行工作的?

2021-09-18 09:19:42

集成邏輯電路、組合邏輯電路實(shí)驗(yàn)?zāi)康?. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態(tài)門的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計(jì)和實(shí)現(xiàn)方法

2008-12-11 23:36:32

組合邏輯電路 :

2007-12-20 23:02:07 28

28

數(shù)字邏輯電路的內(nèi)容:數(shù)制與編碼,,邏輯代數(shù)和邏輯函數(shù),集成邏輯門,組合邏輯電路,中規(guī)模集成組

2008-09-06 01:54:26 33

33 基本邏輯電路: 組合邏輯電路、&

2008-09-12 16:35:29 40

40 組合邏輯電路設(shè)計(jì)一、實(shí)驗(yàn)?zāi)康?. 熟悉組合邏輯電路的基本設(shè)計(jì)方法;2. 練習(xí)用門電路、譯碼器、數(shù)據(jù)選擇器設(shè)計(jì)組合邏輯電路。二、實(shí)驗(yàn)設(shè)備1.

2008-09-12 16:41:23 0

0 時(shí)序邏輯電路的輸出不但和當(dāng)前輸入有關(guān),還與系統(tǒng)的原先狀態(tài)有關(guān),即時(shí)序電路的當(dāng)前輸出由輸入變量與電路原先的狀態(tài)共同決定。為達(dá)到這一目的,時(shí)序邏輯電路從某一狀態(tài)

2009-03-18 22:13:04 71

71 組合邏輯電路(簡稱組合電路)任意時(shí)刻的輸出信號僅取決于該時(shí)刻的輸入信號,與信號作用前電路原來的狀態(tài)無關(guān)時(shí)序邏輯電路(簡稱時(shí)序電路)任意時(shí)刻的輸出信號不僅取決

2009-07-15 18:45:58 0

0 組合邏輯電路電子教案:數(shù)字邏輯電路可分為兩大類: 一類叫組合邏輯電路;另一類叫時(shí)序邏輯電路。本章首先介紹組合邏輯電路的共同特點(diǎn)和描述方法,然后重點(diǎn)介紹組合邏輯電

2009-09-01 08:58:29 0

0 同步時(shí)序邏輯電路:本章系統(tǒng)的講授同步時(shí)序邏輯電路的工作原理、分析方法和設(shè)計(jì)方法。從同步時(shí)序邏輯電路模型與描述方法開始,介紹同步時(shí)序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 異步時(shí)序邏輯電路:本章主要從同步時(shí)序邏輯電路與異步時(shí)序邏輯電路狀態(tài)改變方式不同的特殊性出發(fā), 系統(tǒng)的介紹異步時(shí)序邏輯電路的電路結(jié)構(gòu)、工作原理、分析方法和設(shè)計(jì)方法。

2009-09-01 09:12:34 0

0 鐘控傳輸門絕熱邏輯電路和SRAM 的設(shè)計(jì)

本文利用NMOS管的自舉效應(yīng)設(shè)計(jì)了一種新的采用二相無交疊功率時(shí)鐘的絕熱邏輯電路---鐘控傳輸門絕熱邏輯電路,實(shí)現(xiàn)對輸

2010-02-23 10:14:13 15

15 講述組合邏輯電路設(shè)計(jì)基礎(chǔ)

2010-05-06 10:29:15 0

0 數(shù)字邏輯電路設(shè)計(jì)課程

數(shù)字邏輯電路的設(shè)計(jì)包括兩個(gè)方面:基本邏輯功能電路設(shè)計(jì)和邏輯電路系統(tǒng)設(shè)計(jì)。關(guān)于基本邏輯功能電路設(shè)計(jì)一般在《數(shù)字電路技術(shù)基礎(chǔ)

2010-05-24 16:05:50 0

0 摘要:基于邏輯電路的設(shè)計(jì)中經(jīng)常涉及到用卡諾圖化簡邏輯函數(shù)的過程,給出了利用次態(tài)卡諾圖設(shè)計(jì)邏輯電路的方法及不同觸發(fā)器的狀態(tài)方程在次態(tài)卡諾圖上的表示,并舉例加以說

2010-05-25 09:41:28 13

13 數(shù)字邏輯電路按邏輯功能和電路組成的特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 數(shù)字邏輯電路可分為組合邏輯電路和時(shí)序邏輯電路兩大類。組合邏輯電路在任一時(shí)刻的穩(wěn)定輸出只取決于當(dāng)前的輸入,而與過去的輸入無關(guān)。在結(jié)構(gòu)上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數(shù)字集成電路,根據(jù)原理可分為兩大類,既組合邏輯電路和時(shí)序邏輯電路。

組合邏輯電路的組成是邏輯門電路。電路的輸出狀態(tài)僅由同一時(shí)刻的輸入狀態(tài)決定,與電路的原

2010-08-18 15:05:23 55

55 一、實(shí)驗(yàn)?zāi)康恼莆战M合邏輯電路的設(shè)計(jì)與測試方法

2010-09-21 16:52:20 0

0 基本組合邏輯電路

一、 實(shí)驗(yàn)?zāi)康?⒈ 掌握一般組合邏輯電路的分析和設(shè)計(jì)方法。?⒉ 熟悉集成優(yōu)先編碼器的邏輯功能及簡單應(yīng)用。

2008-09-24 22:14:03 2504

2504

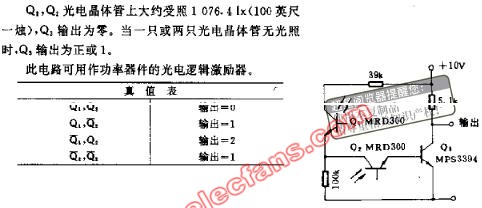

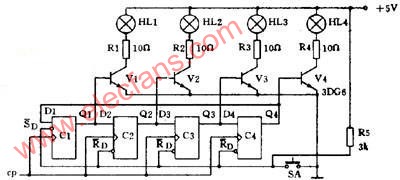

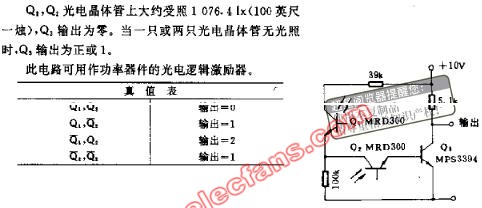

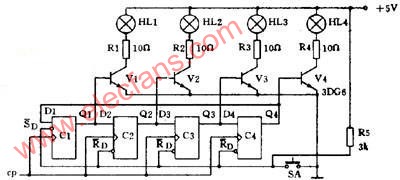

光電邏輯電路圖

2008-12-22 02:33:35 803

803

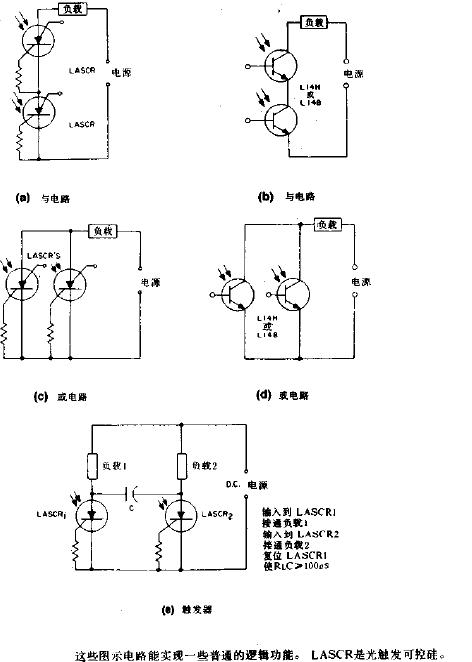

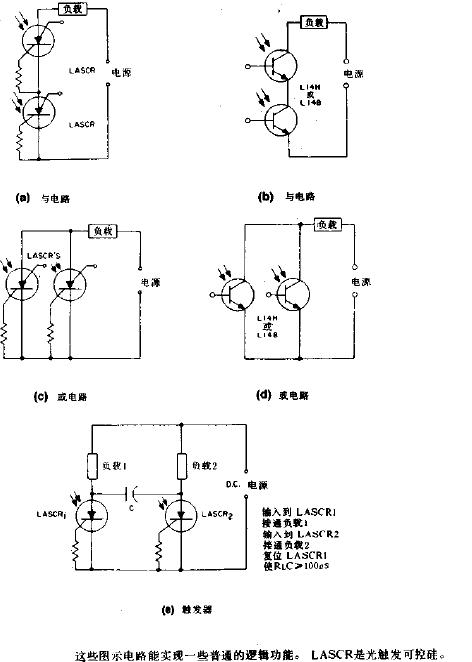

光觸發(fā)邏輯電路圖

2009-04-02 09:20:41 770

770

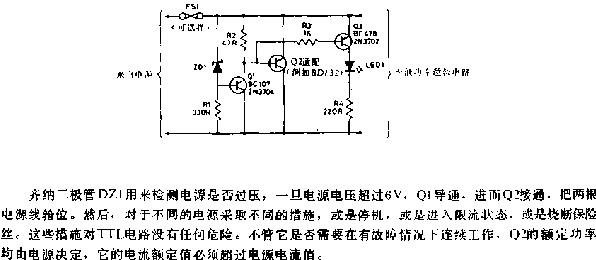

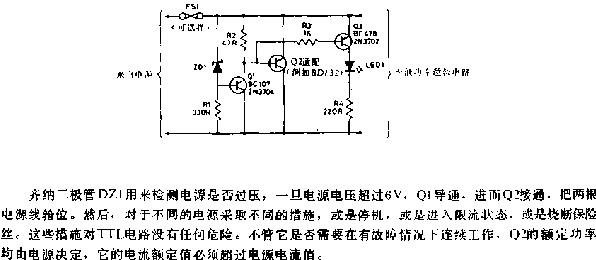

邏輯電路電源的過壓保護(hù)電路圖

2009-04-07 09:08:44 928

928

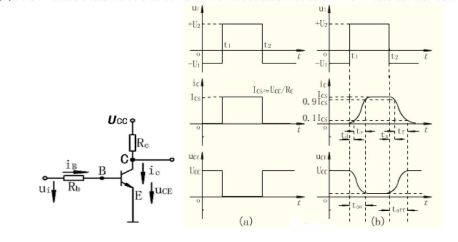

時(shí)序邏輯電路的分析方法

1. 時(shí)序邏輯電路的特點(diǎn) 在時(shí)序邏輯電路中,任意時(shí)刻的輸出信號不僅取決于當(dāng)時(shí)的輸入信

2009-04-07 23:18:11 8146

8146

時(shí)序邏輯電路的特點(diǎn)

在第三章所討論的組合邏輯電路中,任一時(shí)刻的輸出信號僅僅取決于該時(shí)刻的輸入信號,而與電路原來

2009-09-30 18:19:22 9900

9900

數(shù)字邏輯電路

數(shù)字邏輯電路的用途和特點(diǎn)

數(shù)字電子電路中的后起之秀是數(shù)字邏輯電路。把它叫做數(shù)字電路是因?yàn)?b class="flag-6" style="color: red">電路中傳遞的雖然也是脈沖,但這些脈沖是

2009-11-10 10:13:26 17159

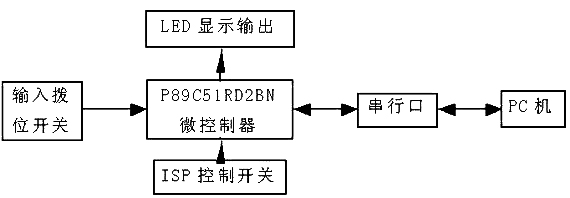

17159 CPLD邏輯電路 圖6是CPLD內(nèi)部邏輯電路,CPLD選用的是LATTICE公司的ispLSI1016E,邏輯設(shè)計(jì)采用原理圖輸入法,主要功能是對MUX的通道進(jìn)行選擇、對A/D轉(zhuǎn)換器進(jìn)

2009-11-13 12:04:13 2502

2502

各種邏輯電路簡介

邏輯電路:

以二進(jìn)制為原理、實(shí)現(xiàn)數(shù)字信號邏輯運(yùn)算和操作的電路。分組合邏輯電路和

2009-11-24 13:27:04 2959

2959 CMOS邏輯電路,CMOS邏輯電路是什么意思

CMOS是單詞的首字母縮寫,代表互補(bǔ)的金屬氧化物半導(dǎo)體(Complementary Metal-Oxide-Semiconductor),它指的是一種特殊類

2010-03-08 11:31:47 3574

3574 什么是陣列邏輯電路

陣列邏輯電路的特點(diǎn): 邏輯元件在硅片上以陣列形式排列,芯片面積小、用戶自編程、設(shè)計(jì)方便。 典型的陣列

2010-04-15 13:43:17 3714

3714 如何看懂?dāng)?shù)字邏輯電路

數(shù)字電子電路中的后起之秀是數(shù)字邏輯電路。把它叫做數(shù)字電路是因?yàn)?b class="flag-6" style="color: red">電路中傳遞的雖然也是脈沖,但這些脈沖是用來表示二進(jìn)制數(shù)碼的,例如

2010-05-24 11:35:01 2727

2727

數(shù)字邏輯電路教學(xué)中的C語言描述和應(yīng)用

摘要:為了改進(jìn)數(shù)字邏輯電路教學(xué)方法以適應(yīng)電子技術(shù)迅猛發(fā)展的需要,我們探索和實(shí)踐了數(shù)字邏輯電路教

2010-05-24 15:40:52 1839

1839

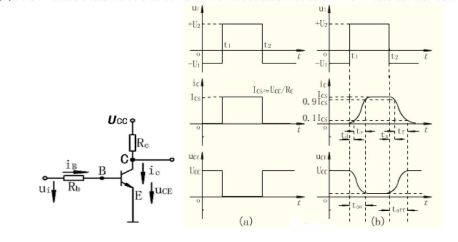

本章分析幾種邏輯電路的高速特性,包括TTL邏輯電路、CMOS邏輯電路、ECL邏輯電路,和LVDS器件的基本結(jié)構(gòu)、工作原理和特點(diǎn),以及邏輯門電路的使用規(guī)則。 3.1 高速TTL電路 TTL電路,是出現(xiàn)

2012-05-25 16:31:29 1274

1274 組合邏輯電路,感興趣的可以下載看看,免費(fèi)的哦!

2015-10-29 15:08:16 31

31 定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)定時(shí)控制器邏輯電路設(shè)計(jì)

2015-12-17 18:18:50 0

0 主要講了時(shí)序邏輯電路的相關(guān)知識,能夠方便大家學(xué)習(xí)使用

2016-02-29 14:25:53 0

0 數(shù)字邏輯電路第3章的PPT,一些難度大,質(zhì)量很高。

2016-06-03 16:57:53 0

0 電子專業(yè)單片機(jī)相關(guān)知識學(xué)習(xí)教材資料之組合邏輯電路的分析與設(shè)計(jì)

2016-09-02 14:30:26 0

0 電子專業(yè)單片機(jī)相關(guān)知識學(xué)習(xí)教材資料之時(shí)序邏輯電路的分析與設(shè)計(jì)

2016-09-02 14:30:26 0

0 詳細(xì)介紹了組合邏輯電路的分析方法,包括加法器、譯碼器、編碼器、分配器、選擇器等組合邏輯電路的分析方法

2017-01-22 13:13:01 3

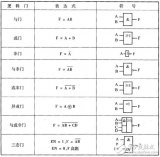

3 邏輯電路是包含邏輯關(guān)系的數(shù)字電路, 以二進(jìn)制為原理、實(shí)現(xiàn)數(shù)字離散信號的傳遞,邏輯運(yùn)算和操作的電路。最基本的邏輯電路是常見的門電路,而最簡單的門電路為與電路、或電路和非電路。

2017-05-22 09:58:43 20474

20474

邏輯電路按其邏輯功能和結(jié)構(gòu)特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路。

2017-05-22 15:15:59 70760

70760

若一個(gè)邏輯電路在任何時(shí)刻產(chǎn)生的穩(wěn)定輸出信號僅僅取決于該時(shí)刻的輸入信號,而與過去的輸入信號無關(guān),即與輸入信號作用前的電路狀態(tài)無關(guān),則稱該電路為組合邏輯電路。

2018-01-30 16:03:16 49501

49501

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來的狀態(tài)無關(guān)。

2018-01-30 16:24:25 38002

38002

組合邏輯電路的設(shè)計(jì)與分析過程相反,本文小編主要跟大家介紹一下關(guān)于組合邏輯電路的設(shè)計(jì)步驟,順便回顧一下組合邏輯電路的分析方法。

2018-01-30 16:46:31 119435

119435

邏輯電路按其邏輯功能和結(jié)構(gòu)特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路。單一的與門、或門、與非門、或非門、非門等邏輯門不足以完成復(fù)雜的數(shù)字系統(tǒng)設(shè)計(jì)要求。組合邏輯電路是采用兩個(gè)或兩個(gè)以上基本邏輯門來實(shí)現(xiàn)更實(shí)用、復(fù)雜的邏輯功能。

2018-01-30 17:05:44 62959

62959

組合邏輯電路和時(shí)序邏輯電路都是數(shù)字電路,組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來的狀態(tài)無關(guān)。而時(shí)序邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出不僅取決于當(dāng)時(shí)的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關(guān)。

2018-01-30 17:26:04 91327

91327

分析時(shí)序邏輯電路也就是找出該時(shí)序邏輯電路的邏輯功能,即找出時(shí)序邏輯電路的狀態(tài)和輸出變量在輸入變量和時(shí)鐘信號作用下的變化規(guī)律。上面講過的時(shí)序邏輯電路的驅(qū)動(dòng)方程、狀態(tài)方程和輸出方程就全面地描述了時(shí)序邏輯電路的邏輯功能。

2018-01-30 18:55:32 123040

123040

本文開始介紹了時(shí)序邏輯電路的特點(diǎn)和時(shí)序邏輯電路的三種邏輯器件,其次介紹了時(shí)序邏輯電路的組成與時(shí)序邏輯電路檢修方法,最后介紹了時(shí)序邏輯電路的應(yīng)用舉例。

2018-03-01 10:53:38 106881

106881

根據(jù)邏輯功能的不同,可把數(shù)字電路分為組合邏輯電路(Combinational Logic Circuit)和 時(shí)序邏輯電路(Sequential Logic Circuit)兩大類。

2018-07-20 08:00:00 0

0 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2019-02-26 15:22:20 30485

30485 時(shí)序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時(shí)序邏輯電路有觸發(fā)器、 寄存器和計(jì)數(shù)器等。

2019-02-26 15:25:01 49630

49630 組合邏輯電路是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來的狀態(tài)無關(guān)。而時(shí)序邏輯電路不僅僅取決于當(dāng)前的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關(guān)。

2019-02-26 15:32:30 62616

62616 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2019-05-16 18:32:37 7636

7636

組合邏輯電路是無記憶數(shù)字邏輯電路,其任何時(shí)刻的輸出僅取決于其輸入的組合.

2019-06-22 10:53:20 46654

46654

邏輯電路在任何時(shí)刻產(chǎn)生的穩(wěn)定的輸出信號僅僅取決于該時(shí)刻的輸入信號,而與過去的輸入信號無關(guān),即與輸入信號作用前的狀態(tài)無關(guān),這樣的電路稱為組合邏輯電路。

2020-08-08 10:40:00 5155

5155

FPGA (Field Programmable Gate Aray,現(xiàn)場可編程門陣列)是一種可通過重新編程來實(shí)現(xiàn)用戶所需邏輯電路的半導(dǎo)體器件。為了便于大家理解FPGA的設(shè)計(jì)和結(jié)構(gòu),我們先來簡要介紹一些邏輯電路的基礎(chǔ)知識。

2020-10-13 11:21:40 25439

25439

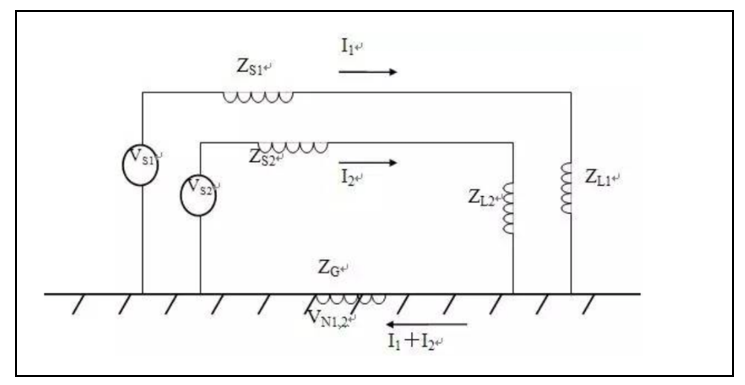

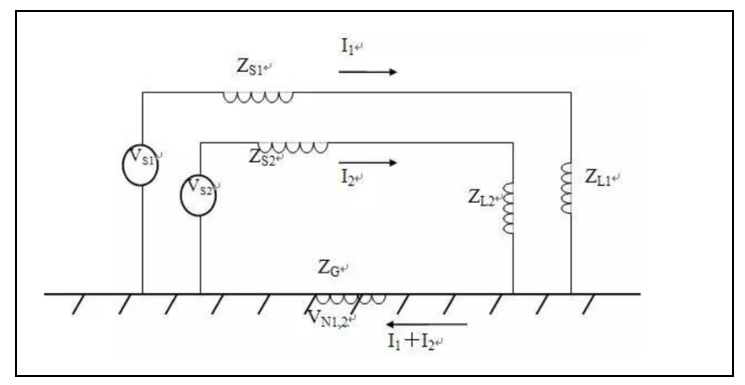

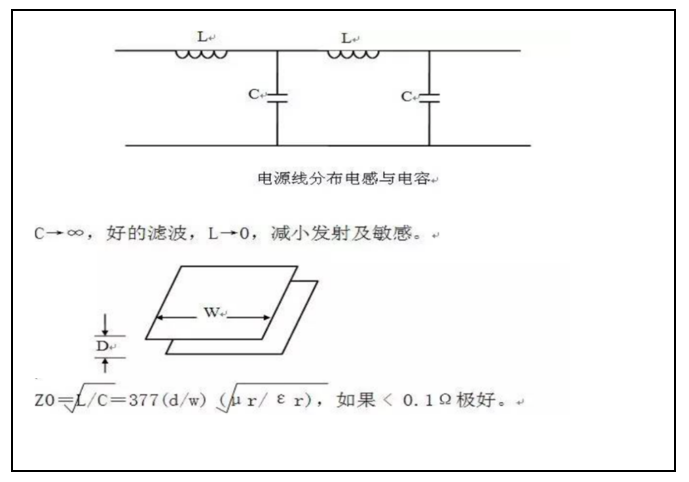

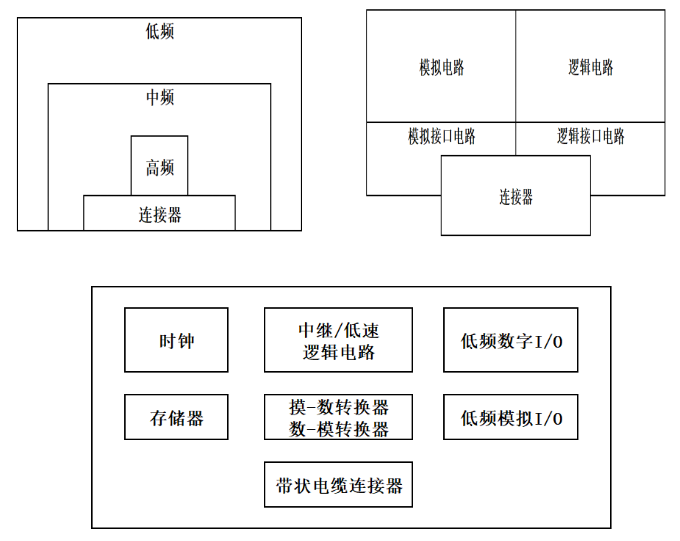

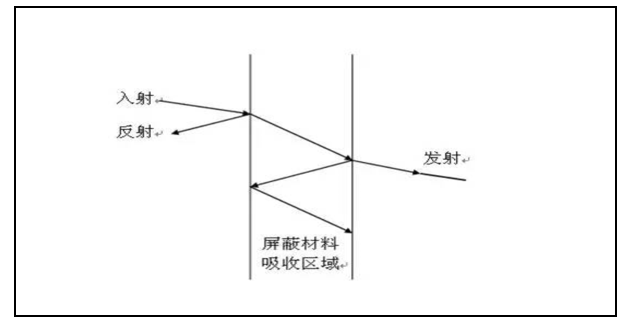

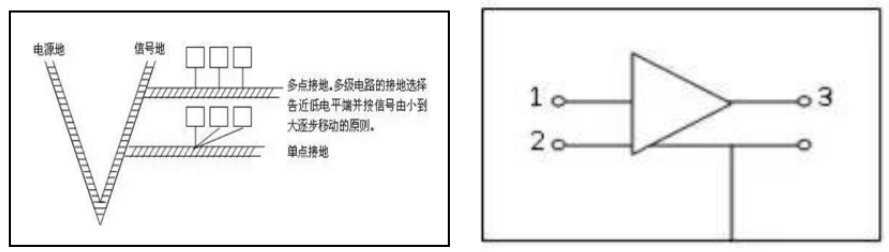

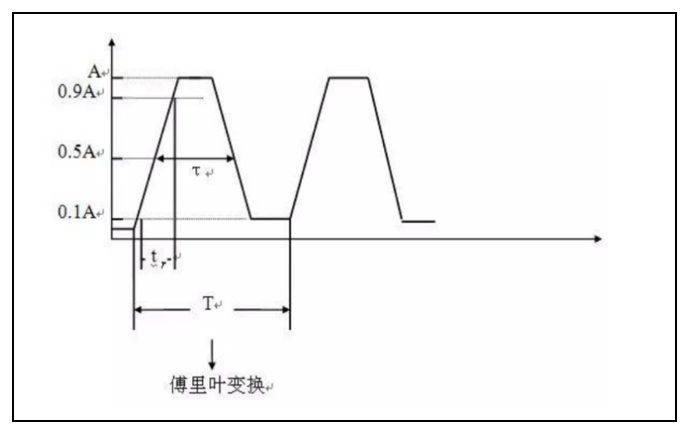

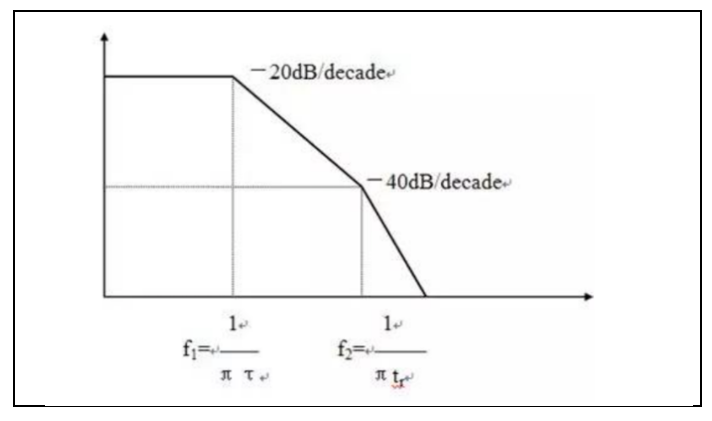

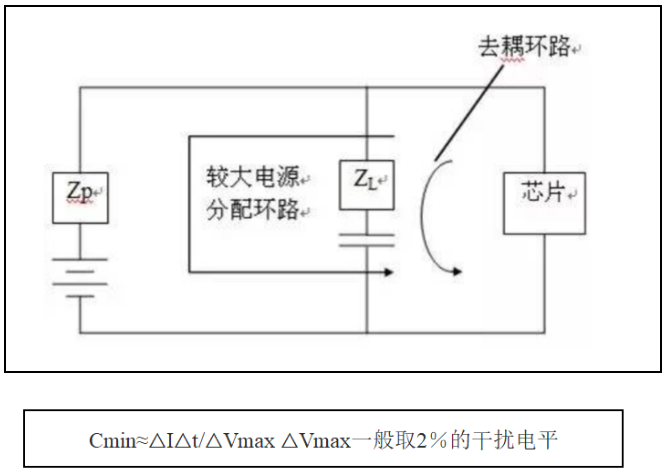

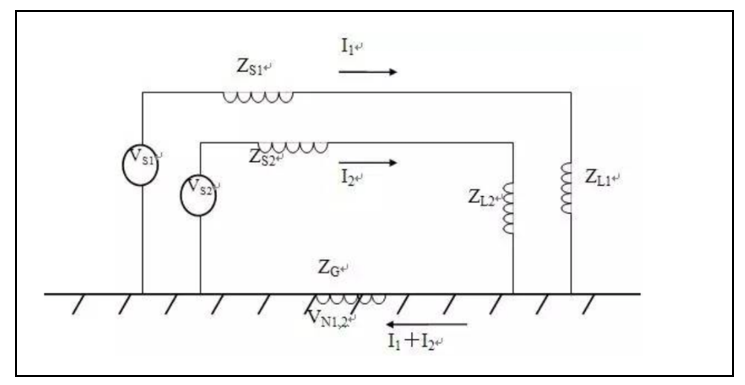

方法是屏蔽、濾波和接地,用它們來切斷干擾的傳輸途徑。

本文將著重在單板的EMC設(shè)計(jì)上,介紹一些重要的EMC知識及法則。在最初電路板的設(shè)計(jì)階段就著手考慮對電磁兼容的設(shè)計(jì),種類包括公共阻抗耦合、串?dāng)_、...

2022-02-10 10:31:49 1404

1404

所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2022-08-12 17:19:26 11081

11081

組合邏輯電路的特點(diǎn)是輸入的變化直接反映了輸出的變化,其輸出的狀態(tài)僅取決于輸入的當(dāng)前狀態(tài),與輸入、輸出的原始狀態(tài)無關(guān)。如果從電路結(jié)構(gòu)上來講,組合邏輯電路是沒有觸發(fā)器組件的電路。

2022-10-24 16:02:32 965

965 數(shù)字電路的分類

(1)按電路結(jié)構(gòu)分類

組合邏輯電路

時(shí)序邏輯電路:。

(2)按集成電路規(guī)模分:小規(guī)模、中規(guī)模和大規(guī)模。

2022-12-05 14:54:47 12

12 組合邏輯電路:用各種門電路組成的,用于實(shí)現(xiàn)某種功能的復(fù)雜邏輯電路。特點(diǎn):某一時(shí)刻的輸出狀態(tài)僅由該時(shí)刻電路的輸入信號決定, 而與該電路在此輸入信號之前所具有的狀態(tài)無關(guān)。

2022-12-05 14:52:54 9

9 所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2023-03-06 14:37:26 1843

1843 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2023-03-14 17:06:50 4816

4816

本篇內(nèi)容主要回顧第三章組合邏輯電路的知識,雖然前面提到過組合邏輯電路是數(shù)字電路中很重要的一部分,但是學(xué)習(xí)起來相對簡單,主要是要學(xué)會掌握方法。

2023-05-24 14:38:59 1166

1166

所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2023-08-16 09:15:23 3562

3562

當(dāng)邏輯電路由多個(gè)邏輯門組成且不含存儲電路,對于給定的輸入變量組合將產(chǎn)生確定的輸出,則這種邏輯電路稱為組合邏輯電路。

2024-02-04 11:46:36 320

320

組合邏輯電路和時(shí)序邏輯電路是數(shù)字電路中兩種重要的邏輯電路類型,它們主要區(qū)別在于其輸出信號的依賴關(guān)系和對時(shí)間的敏感性。

2024-02-04 16:00:27 449

449 時(shí)序邏輯電路是一種能夠存儲信息并根據(jù)時(shí)鐘信號按照特定順序執(zhí)行操作的電路。它是計(jì)算機(jī)硬件中非常重要的一部分,用于實(shí)現(xiàn)存儲器、時(shí)序控制器等功能。與之相對的是組合邏輯電路,它根據(jù)輸入信號的組合情況,立即

2024-02-06 11:18:34 499

499

電子發(fā)燒友App

電子發(fā)燒友App

評論