本文介紹了如何準(zhǔn)確地估算采樣時鐘抖動,以及如何計算正確的上下整合邊界。

2012-04-01 10:19:38 1666

1666

本系列文章共有三部分,第 1 部分重點介紹如何準(zhǔn)確地估算某個時鐘源的抖動,以及如何將其與 ADC 的孔徑抖動組合。在第 2 部分中,該組合 抖動 將用于計算 ADC 的 SRN,然后將其與實際

2012-05-07 11:37:30 2668

2668

為了正確理解時鐘相關(guān)器件的抖動指標(biāo)規(guī)格,同時選擇抖動性能適合系統(tǒng)應(yīng)用的時鐘解決方案,本文詳細(xì)介紹了如何理解兩種類型時鐘驅(qū)動器的抖動參數(shù),以及從鎖相環(huán)輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 14342

14342

隨著技術(shù)的發(fā)展,數(shù)字信號的時鐘頻率越來越高,電路系統(tǒng)對于信號的建立、保持時間、時鐘抖動等要素提出越來越高的要求。

2018-08-07 09:45:46 8261

8261 時鐘抖動是相對于理想時鐘沿實際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 892

892

在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術(shù)的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t)”和幅度噪聲項“λ(t)。對評估的三個

2022-11-23 07:59:49

開關(guān)架構(gòu),具有一個內(nèi)部旁路電容器以降低輻射EMI。電容器將吸收多余的EMI電流(在充電模式下)。此外,開發(fā)人員可以通過建議的PCB布局,通過在調(diào)節(jié)器附近添加兩個小的1微法(uF)電容器來進(jìn)一步降低EMI

2021-12-27 09:31:00

CC2530芯片 ZED 和ZC,在組網(wǎng)正常的情況下,ZED可以進(jìn)入低功耗模式,電流在uA級別。當(dāng)關(guān)閉ZC后,ZED會持續(xù)的進(jìn)行網(wǎng)絡(luò)發(fā)現(xiàn),無法進(jìn)入低功耗模式。電流達(dá)28mA;求教,如何降低ZC發(fā)現(xiàn)網(wǎng)絡(luò)的頻次以降低功耗?或者有其他什么方法來降低功耗?

2016-04-07 14:19:54

STM8在低功耗模式下可以降低主頻運(yùn)行嗎

2023-10-11 06:57:20

cc2640修改哪些參數(shù)可以降低連接后的功耗?cc2640我使用simpleBLEMulti修改的多角色從機(jī)連接,未連接的時候,待機(jī)功耗1.7uA,但是連接后,功耗0.2mA。我看文檔,連接后不會

2016-04-01 11:43:28

,頻率固定在396MHz;設(shè)備樹里關(guān)掉了不用的外設(shè);imx6q的GPU頻率是否可以降低?還有沒有什么其他方法可以降低功耗的?謝謝。

2022-01-10 07:30:09

如圖,這個ADP150給PLL供電為什么可以降低相位噪聲

2019-01-10 09:49:23

你知道有哪些措施可以降低單片機(jī)系統(tǒng)的功耗嗎?

2021-12-20 08:00:04

各種抖動技術(shù)規(guī)范是什么抖動的影響有哪些

2021-04-06 09:22:00

本文針對全方位的信號路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術(shù)。研究選用雙級聯(lián)PLLatinum架構(gòu),配置高性能壓控振蕩器(VCXO),很好地實現(xiàn)了降噪和時鐘抖動濾除的作用。

2019-07-05 07:47:46

ZED 和ZC,在組網(wǎng)正常的情況下,ZED可以進(jìn)入低功耗模式,電流在uA級別。CC2530芯片當(dāng)關(guān)閉ZC后,ZED會持續(xù)的進(jìn)行網(wǎng)絡(luò)發(fā)現(xiàn),無法進(jìn)入低功耗模式。電流達(dá)28mA;求教TI工程師,如何降低ZC發(fā)現(xiàn)網(wǎng)絡(luò)的頻次以降低功耗?或者有其他什么方法來降低功耗?

2020-08-07 07:03:22

問題:如何使用擺率控制來降低EMI?

2019-03-05 20:59:44

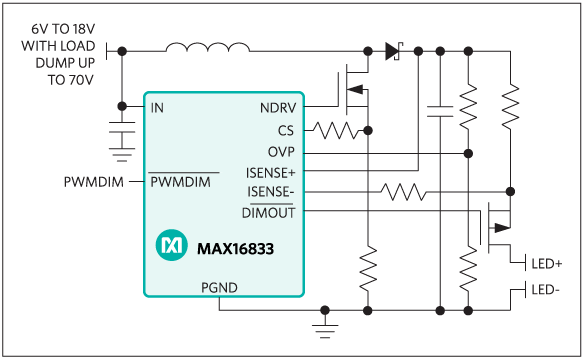

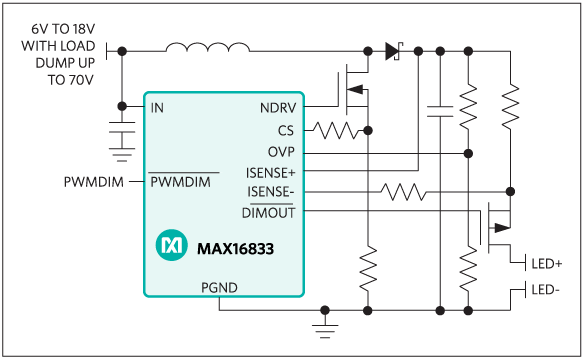

問題:如何通過驅(qū)動高功率LED降低EMI?

2019-03-05 14:33:29

(4)采用軟恢復(fù)特 性的二極管,以降低高頻段EMI (5)有源功率因數(shù)校正,以及其他諧波校正技術(shù) (6)采用合理設(shè)計的電源線濾波器 (7)合理的接地處理 (8)有效的屏蔽措施 (9)合理

2011-10-25 15:50:34

應(yīng)用基準(zhǔn)的CISPR 25,以及針對信息技術(shù)設(shè)備的CISPR 22。如何降低電源設(shè)計的EMI輻射呢?一種方法是用金屬完全屏蔽開關(guān)電源。但在大多數(shù)應(yīng)用中,由于成本和空間的原因,這種方法無法實現(xiàn)。一種更好的方法

2019-06-03 00:53:17

了100MHZ時鐘的標(biāo)準(zhǔn)偏差,大約是308ps。然后我讀到可以通過適當(dāng)?shù)腜LL配置最小化抖動。我還在Vivado找到了“時鐘向?qū)P”-Block。現(xiàn)在我有一些問題:可以測量IO-Pin上時鐘信號

2020-08-19 06:09:57

高信噪比=低ADC孔徑抖動嗎?在設(shè)計中,為了避免降低ADC的性能,工程師一般會采用抖動極低的采樣時鐘。然而,用于產(chǎn)生采樣時鐘的振蕩器常常用相位噪聲而非時間抖動來描述特性。那么,有木有方法將振蕩器相位噪聲轉(zhuǎn)換為時間抖動呢?

2019-08-13 06:27:54

的抖動。就消費(fèi)類電子產(chǎn)品而言,通常較少關(guān)注這些。但是,對于一些高精度應(yīng)用而言,這些方法通常不是首選的方法。 結(jié)論總之,降低 EMI 方法的選擇涉及您的應(yīng)用、時鐘頻率和成本/性能考慮等諸多方面。一般而言,它是所有上述方法的綜合。

2018-09-19 14:42:35

剛學(xué)沒多久,關(guān)于數(shù)字地模擬地怎么連接不是很會啊,為了區(qū)分我把模擬地改為GND1了,這樣連接可以嗎?攝像頭這樣連接,可以降低高頻干擾嗎?發(fā)了一下自己畫的PCB,希望各位大神給點建議啊!PCB.zip (84.32 KB )

2019-04-08 09:35:47

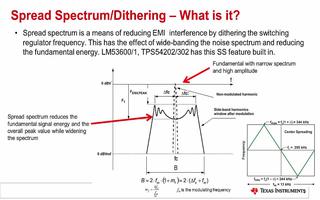

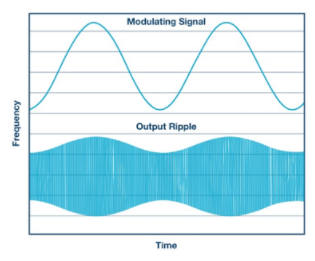

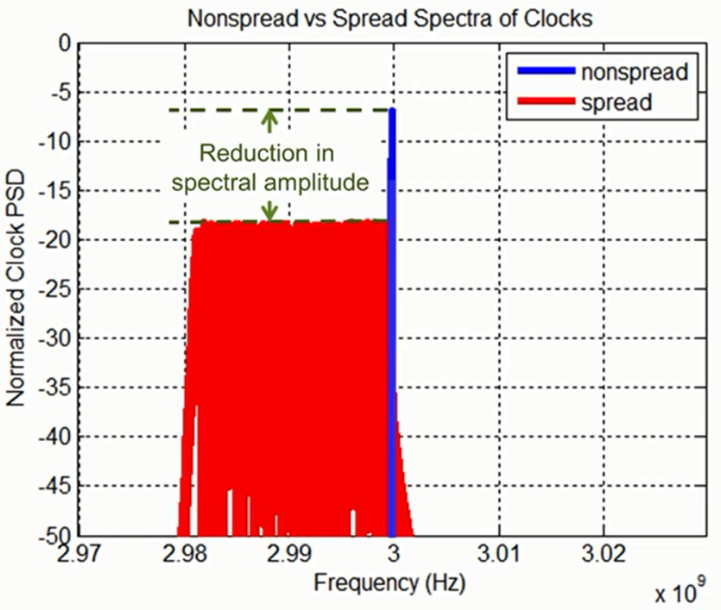

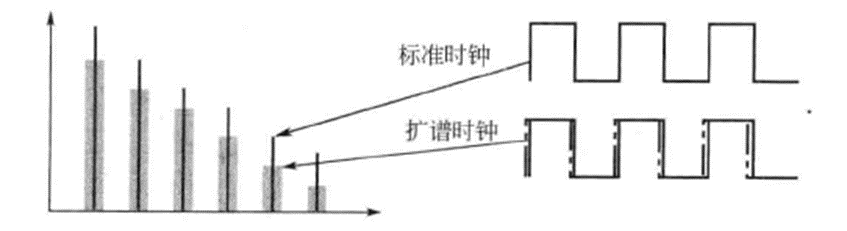

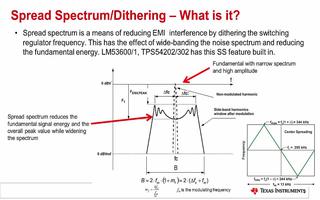

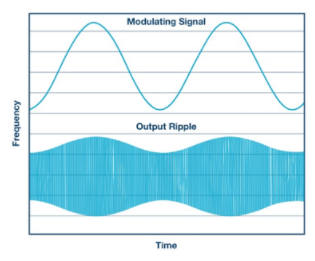

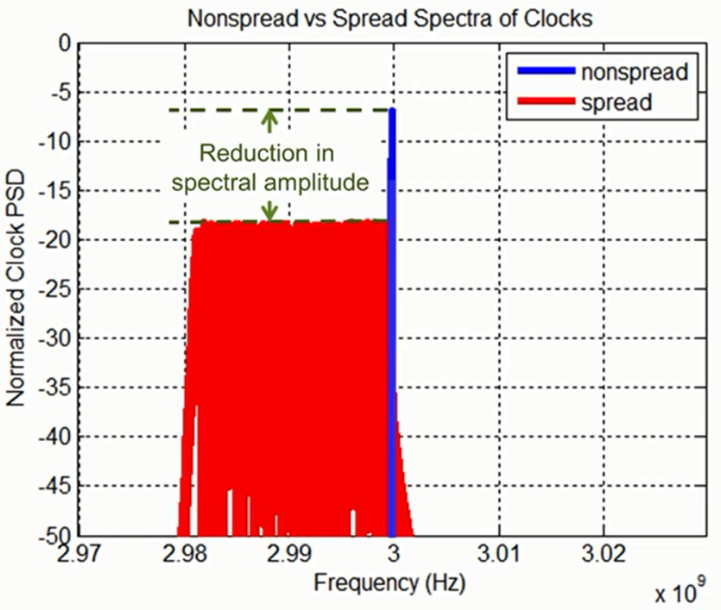

信號進(jìn)行調(diào)制,把信號能量擴(kuò)展到一個比較寬的頻率范圍上。實際上,該方法是對時鐘信號的一種受控的調(diào)制,這種方法不會明顯增加時鐘信號的抖動。實際應(yīng)用證明擴(kuò)展頻譜技術(shù)是有效的,可以將輻射降低7到20dB。3.6

2017-08-09 15:09:57

有什么方法可以降低D類放大器音頻中的電磁干擾嗎?

2021-06-04 06:12:13

有什么方法可以降低IC封裝的熱阻嗎?求解

2021-06-23 07:24:48

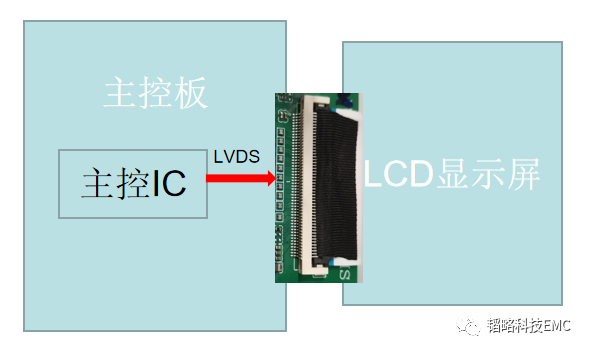

液晶顯示(LCD)技術(shù)的基本原理是什么?液晶顯示(LCD)噪聲產(chǎn)生的原因是什么?有什么方法可以降低LCD的噪聲?

2021-05-31 06:08:04

請問有什么方法可以降低Linux的成本嗎?

2021-04-25 06:15:12

有什么方法可以降低微波/射頻器件的成本嗎?

2021-05-25 06:49:40

有什么方法可以降低電纜的電感量嗎?

2021-05-11 07:02:45

),原邊RCD吸收電路(R7,C5,D6和R8),二次側(cè)RC吸收(R14,C6)以及結(jié)構(gòu)優(yōu)化的變壓器以降低共模EMI干擾。2.2變壓器設(shè)計中的共模噪聲抑制技術(shù)圖4顯示了變壓器內(nèi)部的電荷分布結(jié)構(gòu),其中Qps

2018-06-11 09:36:41

看到有文章說濾波的時候提高電容容量可以降低負(fù)荷,增加使用壽命,這種說法正確嗎?這樣做有什么弊端嗎?

2023-09-27 07:54:19

電源門控可以降低泄漏功耗嗎?有哪幾種情況采用PG能顯著減小泄漏功耗呢?

2022-02-11 06:34:36

一塊音視頻處理芯片輸出1080i的數(shù)據(jù)Data及其同步時鐘Clk,但是時鐘clk的抖動很大,我該如何處理呢?另外,抖動很大的時鐘源能否在后面接入一個模擬鎖相環(huán)降低時鐘的抖動呢?

2018-11-12 09:12:43

時鐘抖動或結(jié)束時鐘抖動的最佳方法是什么?

2021-03-17 07:04:07

我們在用125兆輸入FPGA內(nèi)部PLL倍頻為300兆,然后這個時鐘輸出到IO管腳引出測量,用了很高級的示波器和探頭,發(fā)現(xiàn)時鐘上下抖動有正負(fù)電平: 最高的正電平變成了零電平,零電平向下抖動,變成了最低

2018-05-10 08:14:33

Jitter)是一種從分散諧波干擾能量著手解決EMI問題的新方法。頻率抖動技術(shù)是指開關(guān)電源的工作頻率并非固定不變,而是周期性地由窄帶變?yōu)閷拵У姆绞絹?b class="flag-6" style="color: red">降低EMI,來減小電磁干擾的方法。 頻率抖動技術(shù)

2013-02-01 15:30:40

AD811和AD744應(yīng)用電路的設(shè)計可以降低結(jié)型FET運(yùn)算放大器的諧波失真:

2009-06-02 10:50:26 46

46 本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設(shè)計。

2009-11-27 11:24:07 15

15 高速互聯(lián)鏈路中參考時鐘的抖動分析與測量

在高速互聯(lián)鏈路中,發(fā)送器的參考工作時鐘的抖動是影響整個

2010-04-15 14:01:39 19

19 該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)期。關(guān)

2009-04-21 23:14:05 723

723

摘要:該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-22 09:35:13 296

296

摘要:該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-25 09:54:26 482

482

摘要:該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-05-08 10:19:03 431

431

理解不同類型的時鐘抖動

抖動定義為信號距離其理想位置的偏離。本文將重點研究時鐘抖動,并探討下面幾種類型的時鐘抖動:相鄰周期抖動、周期抖動、時間間隔誤

2010-01-06 11:48:11 1608

1608

時鐘抖動時域分析(下):

2012-05-08 15:26:25 29

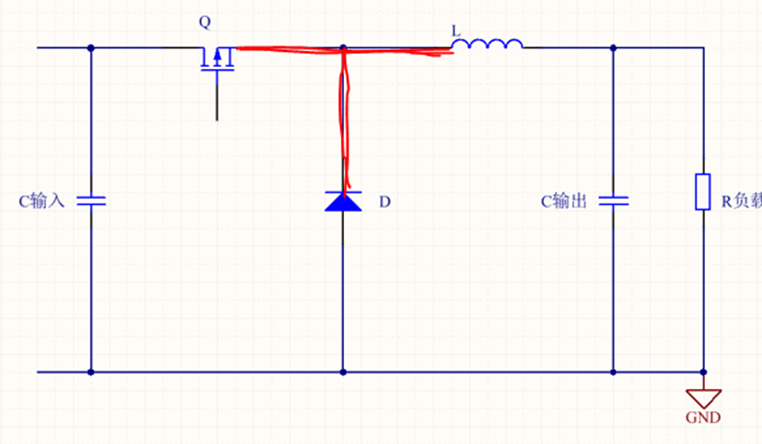

29 設(shè)計人員可以通過控制器的開關(guān)頻率抖動,減少一個脈沖寬度調(diào)制(PWM)控制器的電磁干擾(EMI)分布中頻譜分量的峰值幅度。時鐘抖動擴(kuò)頻技術(shù)并非意在取代傳統(tǒng)的EMI降低技術(shù),但它們與傳統(tǒng)技術(shù)的結(jié)合使用,可以減少系統(tǒng)中的EMI分布。它們還可以利用減少通過某些排放標(biāo)準(zhǔn)所需的屏蔽和濾波量來降低成本。

2013-02-19 14:07:10 2471

2471

的系統(tǒng)設(shè)計,如在某些情況下系統(tǒng)性能極限由系統(tǒng)決定時序裕量。所以對時序抖動有很好的了解在系統(tǒng)設(shè)計中變得非常重要。總抖動可以隨機(jī)抖動和確定性抖動分離組件。我們將不討論抖動的組件本申請說明。我們將專注于不同類型的時鐘

2017-04-01 16:13:18 6

6 很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現(xiàn)象,其不僅可導(dǎo)致噪聲增加,而且還會降低數(shù)據(jù)轉(zhuǎn)換器的有效位數(shù) (ENOB)。例如,如果系統(tǒng)需要 100MHz 14(最小值)位的 ENOB,我們

2017-04-08 04:51:23 1266

1266

級,從而降低成本和功耗。在欠采樣接收機(jī)設(shè)計中必須要特別注意采樣時鐘,因為在一些高輸入頻率下時鐘抖動會成為限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重點介紹如何準(zhǔn)確地估算某個時鐘源的抖動,以及如何將其與AD

2017-05-18 09:47:38 1

1 采用頻率抖動技術(shù)減小EMI 為抑制開關(guān)電源電磁干擾新思路

2017-09-14 14:08:01 14

14 時鐘抖動時域分析,第 2 部分

2017-10-26 16:10:42 6

6 時鐘抖動時域分析 第 3 部分

2017-10-26 16:13:28 4

4 時間域中分析的時鐘抖動,第 1 部分

2017-10-26 16:16:23 4

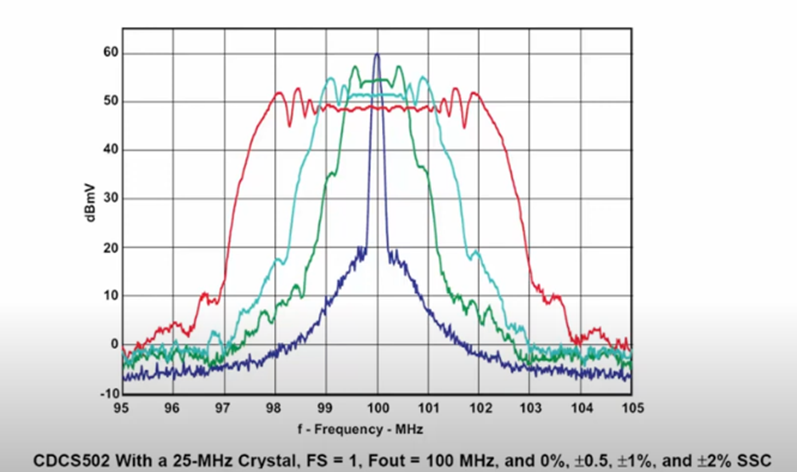

4 SSCG是一種Active且低成本的解決EMI問題的方案,可以在保證時鐘信號完整性的基礎(chǔ)上應(yīng)對更廣頻率范圍內(nèi)EMI問題。相比傳統(tǒng)上使用Ferrite Beads和RF Chokes抑制EMI

2018-08-22 14:45:27 8872

8872 工業(yè)及汽車系統(tǒng)的低EMI電源變換器設(shè)計(六)通過頻率抖動有效降低EMI

2019-04-08 06:07:00 1621

1621

優(yōu)秀PCB設(shè)計練習(xí)降低PCB的EMI有許多方法可以降低PCB設(shè)計的EMI基本原理:電源和地平面提供屏蔽頂層和

2019-08-20 09:11:38 3846

3846 時鐘抖動性能主題似乎是時鐘,ADC和電源的當(dāng)前焦點供應(yīng)廠家。理由很清楚;時鐘抖動會干擾包括高速ADC在內(nèi)的數(shù)字電路的性能。高速時鐘可以對它們所接收的功率的“清潔度”非常敏感,盡管量化關(guān)系需要一些努力。

2019-09-14 11:24:00 7712

7712

本文針對全方位的信號路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術(shù)。研究選用雙級聯(lián)PLLatinum架構(gòu),配置高性能壓控振蕩器(VCXO),很好地實現(xiàn)了降噪和時鐘抖動濾除的作用。

2020-09-23 10:45:00 2

2 使用合適的去耦電容可以降低電源/地平面的噪聲, 并由此來消弱來自這些平面的EMI。

2020-10-10 11:36:18 2699

2699

隨著元件集成度越來越高,設(shè)備小型化,電子產(chǎn)品的EMI問題日漸嚴(yán)重。降低模塊電源EMI,可以降低EMI的危害,避免傳輸信號質(zhì)量問題,對電路或設(shè)備造成干擾甚至破壞,設(shè)備不能滿足電磁兼容標(biāo)準(zhǔn)所規(guī)定的技術(shù)指標(biāo)要求等問題。

2020-10-16 10:12:43 1128

1128 MT-200:降低ADC時鐘接口抖動

2021-03-21 01:18:30 7

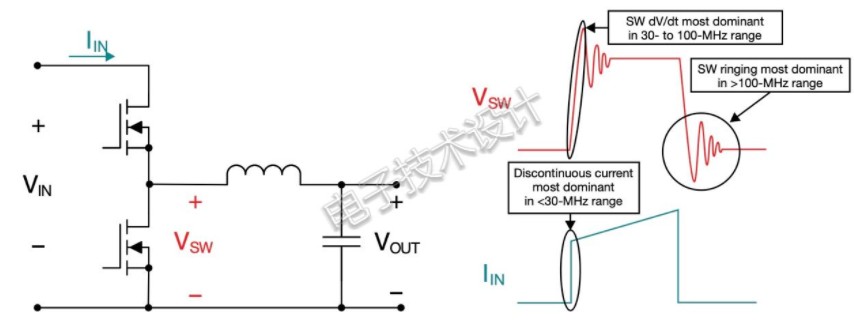

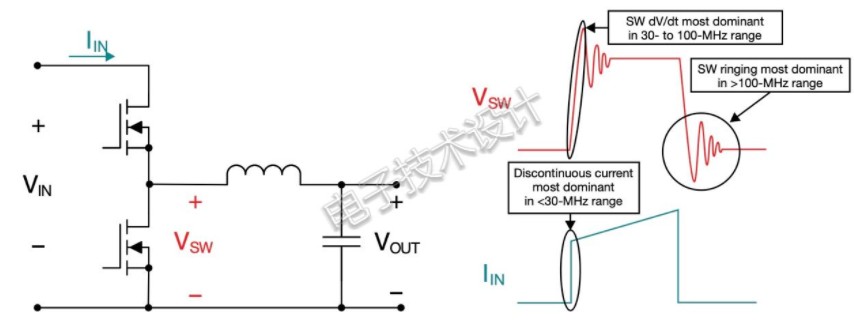

7 圖1以降壓轉(zhuǎn)換器拓?fù)錇槔f明了不同頻帶下各個因素的影響。隨著設(shè)計壓力不斷提升,通過提高開關(guān)頻率來降低尺寸和成本,以及通過增大壓擺率來提高效率,使EMI問題變得更加嚴(yán)重。因此,有必要采用不影響電源設(shè)計、同時具有成本效益且易于集成的EMI緩解技術(shù)。

2021-05-01 09:17:00 4041

4041

超低抖動時鐘的產(chǎn)生與分配

2021-04-18 14:13:51 8

8 DN305雙單片降壓穩(wěn)壓器提供兩個1.4A輸出,帶兩相開關(guān)以降低EMI

2021-05-07 11:26:01 1

1 用時鐘展頻技術(shù)降低EMI技術(shù)探索用時鐘展頻技術(shù)降低EMI技術(shù)探索 汽車電子系統(tǒng)和工業(yè)系統(tǒng)變復(fù)雜且密集,因此如何降低電磁干擾(EMI)的影響成為了工程師在設(shè)計之初,就必須要考慮的因素。干擾源通過一定

2021-06-21 14:33:37 748

748 KOYUELEC光與電子提供技術(shù)支持,有容微電子GM50101:超低附加抖動時鐘緩沖器。

2022-05-07 11:40:15 1071

1071 內(nèi)部頻率抖動(或調(diào)制)也有助于控制 EMI。調(diào)制開關(guān)頻率時,可以降低峰值能量并將其重新分配到其他頻率及其諧波。

2022-05-24 10:18:00 1132

1132

ADI 公司還有許多其他產(chǎn)品可以有效地使用設(shè)計技術(shù)來降低 EMI。如前所述,使用 SSFM 是一種技術(shù)。其他方法包括減慢快速內(nèi)部時鐘邊沿和內(nèi)部過濾。

2022-06-20 15:36:59 1428

1428

減少D類音頻放大器中的電磁干擾(EMI)以降低材料清單(BOM)成本卻不影響音頻性能

2022-11-03 08:04:46 0

0 時鐘抖動使隨機(jī)抖動和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 時鐘抖動解秘—高速鏈路時鐘抖動規(guī)范基礎(chǔ)知識

2022-11-07 08:07:30 1

1 模擬輸出信號處的電磁干擾(EMI)雜散。利用相位控制架構(gòu)而非傳統(tǒng)PLL,SCG系統(tǒng)被證明可以將分頻時鐘脈沖的頻譜高度降低到9.6dB。

2023-02-14 16:43:56 0

0 ,從而降低發(fā)射峰值的幅度。本應(yīng)用筆記將展示DS1086如何與兩個常見的微控制器(8051和PIC)連接。將討論設(shè)計注意事項,因為隨著抖動引入系統(tǒng),系統(tǒng)設(shè)計人員應(yīng)了解抖動可能對整個系統(tǒng)產(chǎn)生的影響。除了降低EMI之外,本文還討論了使用DS1086代替晶體振蕩器的其他優(yōu)點。

2023-03-01 15:33:18 534

534

1.1.1.??抖動定義和分類 ITU-T G.701對抖動的定義為:“抖動是指數(shù)字信號在短期內(nèi)相對于理想位置發(fā)生的偏移重大影響的短時變化”。 對于真實物理世界中的時鐘源,比如晶振、DLL、PLL,它們的時鐘輸出周期都不可能是一個單點的固定值,而是隨時間而變化的

2023-03-10 14:54:32 657

657

系統(tǒng)時序設(shè)計中對時鐘信號的要求是非常嚴(yán)格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準(zhǔn)。但實際中時鐘信號往往不可能總是那么完美,會出現(xiàn)抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 1637

1637 擴(kuò)頻時鐘是以受控方式對系統(tǒng)時鐘進(jìn)行抖動以降低峰值能量含量的過程。SSC技術(shù)用于最小化電磁干擾(EMI)和/或通過聯(lián)邦通信委員會(FCC)的要求。

2023-05-26 16:51:37 4629

4629

先來聊一聊什么是時鐘抖動。時鐘抖動實際上是相比于理想時鐘的時鐘邊沿位置,實際時鐘的時鐘邊沿的偏差,偏差越大,抖動越大。實際上,時鐘源例如PLL是無法產(chǎn)生一個絕對干凈的時鐘。這就意味著時鐘邊沿出現(xiàn)在

2023-06-09 09:40:50 1128

1128

本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 960

960

請問運(yùn)放產(chǎn)生噪聲的原理是什么?怎么可以降低? 運(yùn)放(Operational Amplifier,簡稱OP-AMP)是一種重要的電子元件,廣泛應(yīng)用于模擬和線性電路中。然而,在實際應(yīng)用中,運(yùn)放會生成一定

2023-11-09 15:38:32 947

947 增加共模濾波器的節(jié)數(shù)可以降低共模干擾嗎? 增加共模濾波器的節(jié)數(shù)可以降低共模干擾。共模干擾是電路中常見的問題,特別是在高頻信號傳輸和信號處理中常常會遇到。共模濾波器的目的是抑制共模干擾,提高信號的質(zhì)量

2023-11-20 16:46:27 229

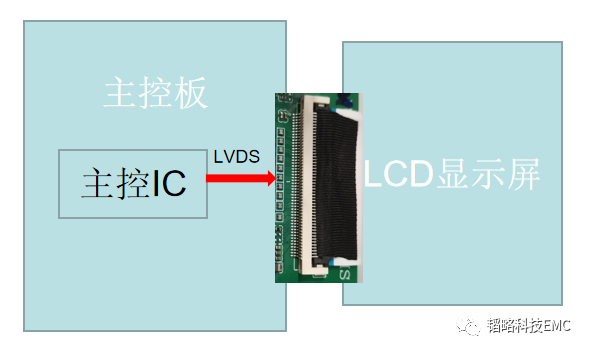

229 如何有效解決LVDS時鐘EMI問題

2023-11-23 09:04:46 485

485

電子發(fā)燒友App

電子發(fā)燒友App

評論