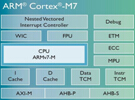

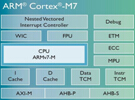

ARM 為新一代 Cortex-M7 芯片提供了 28 納米制程工藝,工作頻率比現有的 Cortex-M 系列處理器高出 400 MHz,提升了近一倍性能。在此之外,它還支持 64 位數據傳輸,和雙指令并發處理。

2014-09-24 14:30:37 2414

2414 ARM在上星期公布了最新的M系列處理器核心Cortex-M7后,緊接著合作伙伴ST(意法半導體)也于臺灣時間9/30公布了搭載該核心的STM32F7 MCU(微控制器)產品線,其產品線的負責主管向臺灣媒體們說明了產品細節與市場策略。

2014-10-02 11:59:31 3671

3671

Cortex-M7的設計做了徹底的改變,而之前的M3、M4只是在先前的架構上做了相應的延伸,該芯片將在物聯網和其他相關領域中應用。

2014-10-08 16:26:38 7360

7360

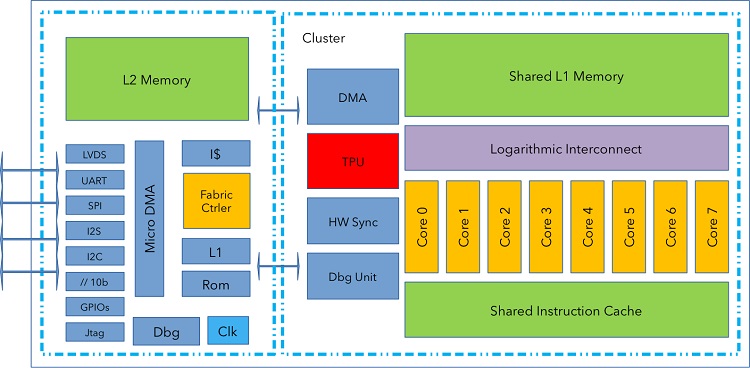

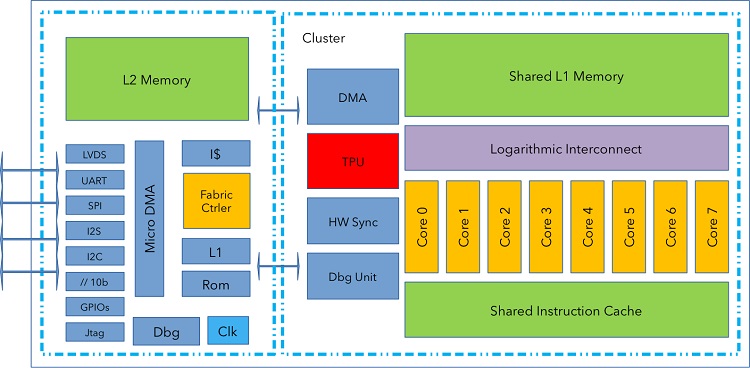

副總裁Joel Cambonie表示,GAP8可實現較ARM Cortex-M0到Cortex-M7等核心更高兩倍的能源效率。

2016-12-09 10:38:41 2417

2417

ARM7、ARM9、ARM11、ARM-Cortex有什么關系?ARM7,ARM9,cortex-m3,cortex-m4,cortex-a8的區別在哪里?

2021-07-01 07:50:20

ARM7、ARM9、ARM11與ARM-Cortex有何關系?ARM7、ARM9、cortex-m3、cortex-m4與cortex-a8的區別在哪?

2021-10-21 06:27:27

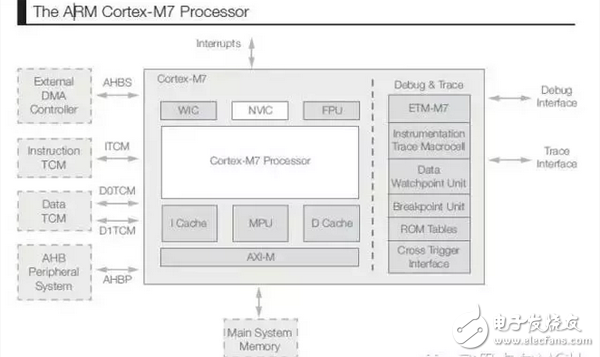

Cortex-M7處理器是一款高效、高性能的嵌入式處理器,具有低中斷延遲、低成本調試的特點,并具有與現有Cortex-M Profile處理器的向后兼容性。

該處理器具有有序的超標量流水線,這意味著

2023-08-17 07:55:23

本節介紹Cortex-M7處理器程序員模型。

除了各個核心寄存器描述外,它還包含有關軟件執行和堆棧的處理器模式和特權級別的信息

2023-08-23 06:22:01

的Cortex-M3核心,核心頻率為96Mhz,并擁有32KB的RAM和512KB的Flash,對于大部份的嵌入式系統來說是非常的夠用,此外,借著LPC1768多功能的特點,細小的mbed還提供了極豐富的連接性,包括

2013-01-29 15:05:30

ARM Cortex-M33處理器是第一款ARMv8-M處理器,旨在滿足嵌入式和物聯網市場,特別是那些需要高效安全或數字信號控制的市場。

ARMv8-M引入了TrustZone,這構成了嵌入式和物

2023-08-28 06:12:15

Cortex-M處理器系列針對低成本、高能效的微控制器進行了優化。

這些處理器可以在各種應用中找到,包括物聯網、工業和日常消費設備。

該處理器系列基于M-Profile架構,可為深度嵌入式系統提供低

2023-08-29 07:00:04

目錄Cortex-M系列Cortex-M0:Cortex-M0+:Cortex-M1:Cortex-M3:Cortex-M4:Cortex-M7:規格對比Cortex-A系列

2022-02-07 08:28:20

基于ARMv8-M架構的ARM? Cortex?-M處理器包含ARM ***?技術,采用ARM CoreLink? 系統IP的物聯網子系統可實現更快、最低風險的芯片上市周期

2019-10-23 08:21:13

子系統SSE-050為物聯網(IoT)和嵌入式細分市場的產品提供了起點。

SSE-050為ARM?Cortex?-M3處理器提供流程和技術不可知的參考、預集成、經過驗證的硬件和軟件子系統,可進行擴展以

2023-08-24 06:16:44

隨著科技的不斷發展,“智能化”為醫療設備不斷賦能。嵌入式ARM核心板因其性能強、低成本、穩定性高的特點,在醫療領域得到廣泛應用。飛凌嵌入式始終秉持專業態度,積極探索嵌入式ARM技術在醫療行業

2022-06-30 14:53:00

【STM32F750x8】本文檔是關于ARM? Cortex?-M7 內核的單片機 STM32F750x8的數據手冊, 介紹了它的主要外設資源和電特性參數。 核心:ARM@32位Cortex-M7

2022-11-28 07:09:42

弱弱詢問下,ARM7,ARM9,cortex-m3,cortex-m4,cortex-a8的區別在什么地方

2012-07-01 23:02:01

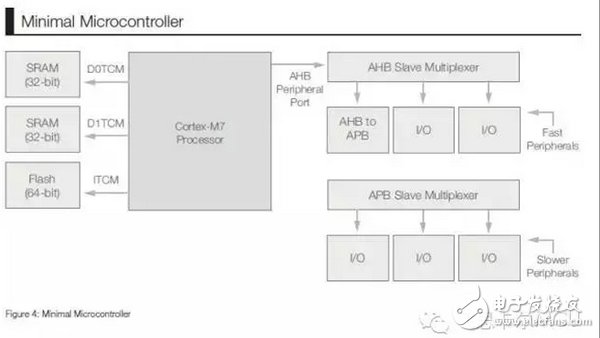

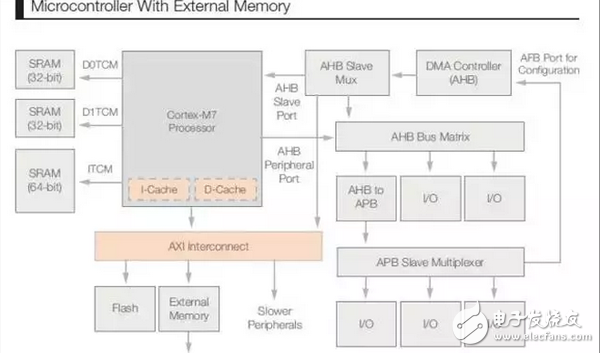

ARM Cortex-M7處理器是Cortex-M系列中性能最高的處理器,可用于設計復雜的MCU和SoC。

Cortex-M7提供業界領先的5.01核心標記/MHz標量性能,同時保持了ARMv7-M

2023-08-25 06:25:54

ARM Cortex-M23處理器是一款非常緊湊的兩級流水線處理器,支持ARMv8-M基準架構。

配備TrustZone的Corest-M23是最受限制的物聯網和嵌入式應用程序的理想處理器,這些

2023-08-25 06:19:14

Corstone?-102參考包IP是創建基于高效Arm?Cortex?-M內核的物聯網(IoT)片上系統(SoC)設計的理想起點。

Corstone-102為安全受限的設備提供了堅實

2023-08-10 07:59:20

Arm?Corstone?-300參考包(Corstone?-300)是創建基于Cortex?-M55處理器核心的物聯網(IoT)片上系統(SoC)設計的理想起點。

Corstone?-300個示例

2023-08-10 07:56:42

恩智浦推出了Cortex-M7 + M4內核的MCU(i.MX RT1170),主頻高達1GHz,打破MCU低頻的傳統。今天,我們來了解一下世界上幾個知名MCU廠商各家的MCU產品。概念:MCU:Micr...

2021-11-03 09:10:48

在前不久,恩智浦推出了Cortex-M7 + M4內核的MCU(i.MX RT1170),主頻高達1GHz,打破MCU低頻的傳統。今天,我們來了解一下世界上幾個知名MCU廠商各家的MCU產品。概念

2021-11-03 08:05:35

Cortex-M7硬件的以下功能在Cortex-M7循環模型中完全實現:

·Cortex-M7整型內核·NVIC嵌套矢量化中斷控制器·WIC-喚醒中斷控制器接口支持(僅支持接口)。

·AXI4

2023-08-12 07:01:53

法半導體(ST)近日就宣布推出業界首款基于ARM最新Cortex-M7內核的STM32 F7系列微控制器,其性能遠超ST之前的32位STM32F4微控制器,用戶通過無縫升級路徑可將處理性能和DSP性能提高一倍。

2019-07-10 06:01:57

是基于Cortex-M7內核,而Cortex-M7和Cortex-M3/M4的復位序列有些不一樣。本文中,將針對這個問題做詳細講解。

2021-03-10 07:27:15

描述Cortex-M7處理器的核心本質為微控制器,卻擁有高達600MHz的主頻,高密度的512KB TCM SRAM和16MB的高速SDRAM,超快的實時響應,超強處理性能賦予了RT1052視頻

2022-01-25 08:19:12

Cortex-M7能達到600Mhz的頻率,性能完全可以媲美Cortex-A系列,那對于Linux系統是否能夠很好的應付。

2023-11-03 06:35:09

Cortex-M3與ARM7的性能比較

名稱?????????????????????????????????????ARM7

2018-06-21 14:04:01

SOM-TL335x核心板創龍SOM-TL335x是一款基于TI Sitara系列AM3352/AM3354/AM3359 ARM Cortex-A8高性能低功耗處理器設計的低成本工業級核心板,通過

2020-09-27 15:36:57

各位大佬,打擾了, 求助一個問題。最近發現atmsame70 (cortex-m7 的內核) 運行 rt-thread (大概v2.x 的版本吧,好幾年之前移植的工程了) 偶爾會出現剛啟動不久就直接

2023-05-05 11:35:41

WIFI連接已經越來越重要和流行,尤其在以物聯網為背景的應用中。飛思卡爾提供多款基于ARM Cortex-M0+或者ARM Cortex-M4的單片機,豐富功能的實時操作系統MQX和全功能TCP/IP協議棧支持。RealTek 8189EM是一個可以支持802.11b/g/n低功耗WIFI模塊。

2016-06-13 11:39:33

提及物聯網,各位能真正理解物聯網內部核心架構嗎?還是只是對關于物聯網技術層面或多或少的有所了解而已。其實,物聯網平臺是基于互聯網的基礎,通過通訊技術類構建的,而不是依賴其他特定的硬件模塊的,用戶可以基于自身的設備技術架構,簡單輕松接入物聯網。

2020-10-29 09:45:45

Operating Frequency CPU AT91M40800 0 100 40 ARM7TDMI AT91M42800A 0 144 33 ARM7TDMI AT91M55800A 0 176 33

2014-10-13 17:51:37

CORTEX-M7設置項總是卡死,沒有反應。

2023-08-08 07:32:42

Cambonie表示,GAP8可實現較ARM Cortex-M0到Cortex-M7等核心更高兩倍的能源效率。GAP8處理器來自意大利波隆納大學(UniversiTIes of Bologna)與瑞士蘇黎世聯邦

2020-10-13 16:37:50

IMX8MP EVK bone stock 在加載 Cortex-M7 RPMSG 固件時凍結

2023-04-21 07:48:51

1 核心板簡介創龍科技SOM-TLIMX8MP是一款基于NXP i.MX 8M Plus的四核ARM Cortex-A53 + 單核ARM Cortex-M7異構多核處理器設計的高端工業核心

2023-06-13 17:01:33

核心板和評估底板組成。ARM Cortex-A53(64-bit)主處理單元主頻高達1.6GHz,ARM Cortex-M7實時處理單元主頻高達800MHz。處理器采用14nm最新工藝,內置

2023-06-13 16:58:29

外圍的傳感器和處理中間的無線通信技術,到核心的云平臺,再到智能手機的一個互動過程。本文主要介紹NXP低功耗無線產品ZigBee、BLE和Cortex M系列MCU在物聯網中的應用,以及品佳集團基于NXP產品智能家居解決方案介紹。

2019-07-16 07:28:22

描述PSOC6核心板核心板模塊cy8c6234,板載DAP下載器,超低功耗 PSoC 6 MCU 架構提供物聯網設備所需的處理性能,消除了功耗和性能之間的權衡。 PSoC 6 MCU 包含雙 CPU

2022-08-15 07:50:02

與當初ARM公司發表聲明Cortex-M7內核時所聲明的無論是在功耗、頻率等還是有一定差異的!但是這或許只能理解為ST...

2021-08-20 08:14:44

意法半導體STM32F7系列MCU采用高性能的ARM Cortex-M7核心,借助ST的ART Accelerator?和L1緩存,STM32F7微控制器可提供Cortex-M7內核的最高理論性

2021-11-26 08:13:08

CORTEX-M7設置項總是卡死,沒有反應。

2024-03-13 06:47:10

工作時)。低功耗模式(STOP模式)下的消耗電流為120μA,待機時的消耗電流為1.7μA。主要特性描述:1. 內核:ARM 32bit Cortex-M7 CPU和FPU自帶實時加速器,內置L1緩存

2014-09-28 11:15:12

iMX6UL開發板廣泛應用于物聯網、人機界面、電子支付、智能家居、工控、醫療、安防、金融、電力、手持設備、顯示控制等領域。核心板配置:ARM Cortex-A7架構 主頻高達528MHz,核心

2018-04-26 01:41:48

物聯網技術核心詳解:RFID5.3 物聯網中的電子身份識別簡介5.4 TIA標準成物聯網及M2M技術未來的基礎6 物聯網的應用6.1基于物聯網技術的高校資產管理系統6.2物聯網技術在我國金融領域

2012-07-26 22:09:30

平臺5.2 物聯網技術核心詳解:RFID5.3 物聯網中的電子身份識別簡介5.4 TIA標準成物聯網及M2M技術未來的基礎6 物聯網的應用6.1基于物聯網技術的高校資產管理系統6.2物聯網技術在我國

2014-11-06 09:52:46

申請理由:目前在進行ATMEL CORTEX-M7的一個MCU開發, 型號為ATSAMS70Q19, 想試用下CMSIS-DAP Mini仿真器能否支持, 手上除有這個M7的硬件, ST的M4/M

2016-06-12 15:47:26

《ARM Cortex-M3應用開發實例詳解》作 者:劉波文 編著 內容簡介 劉波文編著的《ARM Cortex-M3應用開發實例詳解》針對市場上新型熱門的ARM芯片SAM3U Cortex-M

2014-03-13 11:06:45

`一、硬件平臺 二、實驗簡介 STMH32H7采用Cortex-M7內核,相比Cortex-M3系列除了內置硬件FPU單元,在數字信號處理方面還增加了DSP指令集,支持諸如單周期乘加指令(MAC

2020-04-14 22:47:36

當今在談論物聯網,其中傳感作為物聯網核心,數以“億”計的傳感器被嵌入到各種設備中,作為物聯網感知層核心部件,由于傳感器的部署規模并未普及,使得沒有足夠的“物理層”接入點,導致數據不足,從源頭上阻礙物聯網發展。

2020-05-15 06:45:22

Cortex-M4,Cortex-M7,Cortex -M33或Cortex-M35P處理器,以取代MCU+DSP兩個處理器的設計。在一個處理器中結合使用基于Arm的擁有DSP指令擴展功能的MCU對于

2022-07-29 14:48:46

作單核或最多四個處理器的集群嵌入式和物聯網市場的合理選擇7.Cortex-A35ARM設計的最小且最節能的應用處理器電源管理功能可降低功耗預算支持適用于嵌入式應用的64位處理用于物聯網節點和網關的理想

2018-08-23 10:04:38

低功耗藍牙芯片是發展物聯網的核心任務

2020-12-30 07:05:37

全新 ARM Cortex-M 處理器為物聯網安全樹立新一代行業標準 ·這些全新的處理器讓開發者能夠更輕松地打造極其節能、安全且可以聯網的物聯網設備。 ·Cortex-M

2016-11-12 15:50:06

在協處理器 (Cortex-M7) 的 SDK 中,我沒有找到任何使用“自定義腳本”的 SDMA 示例。

目的是測量未知頻率信號的高/低電平持續時間。

當 GPIO 中出現下降沿或上升沿時,我

2023-05-24 08:01:41

STM32746G-EVAL2,評估板是基于ARM Cortex-M7內核的STM32F746NGH6微控制器的完整演示和開發平臺。它具有四個I2C接口,六個SPI,三個多路復用單工I2S接口

2019-04-22 10:23:53

STM32756G-EVAL2,評估板是基于ARM Cortex-M7內核的STM32F756NGH6微控制器的完整演示和開發平臺。它具有四個I2C接口,六個SPI,三個多路復用單工I2S接口

2019-04-18 07:57:52

STM32F769I-DISCO,Discovery套件允許用戶使用基于ARM Cortex-M7內核的STM32F7系列微控制器開發和共享應用程序。該發現套件支持多種應用,可從音頻,多傳感器支持,圖形,安全性,視頻和高速連接功能中受益。 Arduino連接支持提供無限擴展功能,可選擇多種專用附加板

2019-03-13 08:57:16

STM32F769I-EVAL,評估板是基于ARM Cortex-M7內核的STM32F769NI微控制器的完整演示和開發平臺。它具有以下四個I2C接口,六個SPI,三個多路復用全雙工I2S

2019-03-12 10:26:07

Arm平臺安全架構(PSA)采用高性價比、領先技術全面提升物聯網市場的安全技術支持基于STM32H7系列開發的Arm? Cortex?-M7微控制器整合PSA概念和先進的安全功能服務中國,2017年

2017-10-30 14:29:34

如何利用Cortex-M7的低功耗定時器LPTIM去產生PWM波呢?有哪些操作步驟?

2022-01-26 06:10:27

本文檔介紹了如何將基于ARM快速模型的Cortex-M33物聯網套件FvP與MDK工具鏈一起使用的分步過程。

雖然我們已經測試了這些實現,但還會對工具和FPGA映像進行更新。

預計這些實現和后續實現之間會有差異。

2023-09-05 07:22:52

的圖像(QBHOUSE)為例,在 AVH Corstone-300 平臺上使用 Arm Cortex-M55驗證推理結果。結果如圖7所示,與服務器主機直接推理的推理結果高度一致。這表明我們已經成功地

2022-09-02 14:48:31

如何采用Cortex-M3單片機設計的WiFi物聯網小車?

2021-05-24 06:43:41

Cortex-M7處理器設計基于ARMv7-M架構。它支持Cortex-M4處理器上的所有可用指令,并使用相同的異常模型進行中斷處理。在大多數情況下,為Cortex-M4處理器編寫的程序代碼可以在

2018-05-11 13:31:34

都在積極為即將到來的信息與通信基礎設施的重大變革做準備。事實上,根據IDC分析師的預測,到2020年年末,全球聯網的設備裝機總量將達2,120億臺,其中將有301億臺為物聯網設備。

2019-08-16 07:48:47

instructions, see the ARM?v7-M Architecture Reference Manual.” -----《ARM Cortex-M7 Processor

2022-09-21 11:31:15

近來準備做ARM9核心板 大家有啥建議不?

2012-08-04 22:23:17

深入淺出Cortex-M7——i.MX RT1050

2018-03-06 08:39:38

嗨!致命錯誤:選定的核心(Cortex-M3)與目標核心(Cortex-M0)不同會議中止!使用STEVAL-SPIN3202,即使編譯順利,鏈路上也會出現上述錯誤。 我不知道為什么。 感謝您的建議

2019-01-14 06:30:51

請問Arm Cortex-M85內核相對于M7內核有哪些提升?有沒有哪位大神科普一下

2022-09-22 10:37:06

請問Cortex-M7內核的Cache是如何提升訪問效率的?

2022-01-26 08:23:55

mbed 物聯網操作系統會成為cortex-m中的android嗎?

2024-01-17 07:14:10

上禮拜五和這禮拜一,分別去參加了研華物聯網論壇和ARM技術交流會,感覺收獲蠻大的,從某種意義上來講物聯網無論從外(研華的物聯網方案)到內(ARM新的Cortex系列的芯片)都有了實質性的變化。

2021-07-05 07:53:07

STM32H743ZIT6,32位Arm?Cortex?-M7 480MHz MCU,最高2MB閃存, 高達1MB RAM、46個通信和模擬接口

2023-02-07 16:16:26

STM32H743VIT6,32位Arm?Cortex?-M7 480MHz MCU,最高2MB閃存, 高達1MB RAM、46個通信和模擬接口 特征

2023-02-07 16:21:55

ARM新銳Cortex_A7核心架構解析

2017-09-28 10:10:02 11

11 STM32H723VEHigh-performance and DSP with DP-FPU, Arm Cortex-M7 MCU with 512 Kbytes Flash, 564

2021-12-07 12:51:13 4

4 熱點新聞 1、為 IPO 做準備!Arm 董事會引入高通和英特爾前高管 軟銀集團旗下芯片設計公司 Arm 已將高通前首席執行官保羅?雅各布斯(Paul Jacobs)和英特爾前高管羅斯?斯庫

2022-12-01 19:10:02 637

637 電子發燒友網站提供《通過MPLAB Harmony v3將XDMAC與Arm Cortex-M7 MCU上的QSPI搭配使用.pdf》資料免費下載

2023-09-20 14:51:03 0

0 電子發燒友網站提供《GD32H737xx系列Arm Cortex-M7 MCU數據手冊.pdf》資料免費下載

2024-01-03 10:42:12 4

4 電子發燒友網站提供《GD32H757xx系列Arm Cortex-M7 MCU數據手冊.pdf》資料免費下載

2024-01-03 10:47:07 1

1 電子發燒友網站提供《GD32H759xx系列Arm Cortex-M7 MCU數據手冊.pdf》資料免費下載

2024-01-03 10:45:26 3

3

正在加载...

電子發燒友App

電子發燒友App

評論