現(xiàn)代內(nèi)存芯片的編號識別

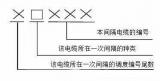

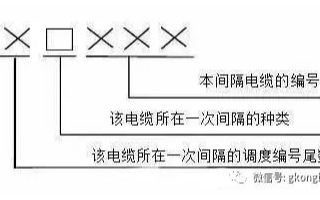

一、現(xiàn)代(HYUNDAI)公司的SDRAM內(nèi)存芯片上的標(biāo)識格式如下(這里說的是2000年9月30日后的新版本HY內(nèi)存芯片):HY XX X XX X X&n

2008-09-04 13:00:04 2535

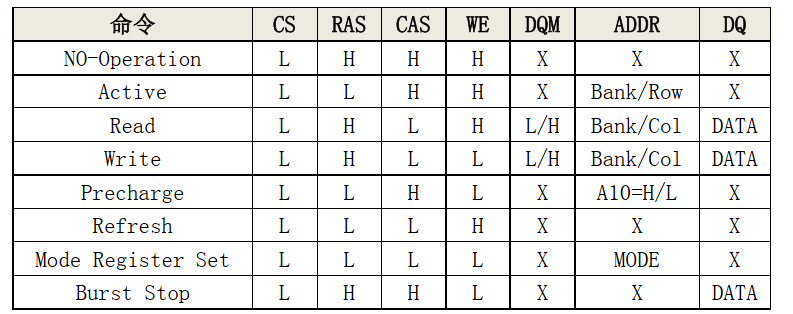

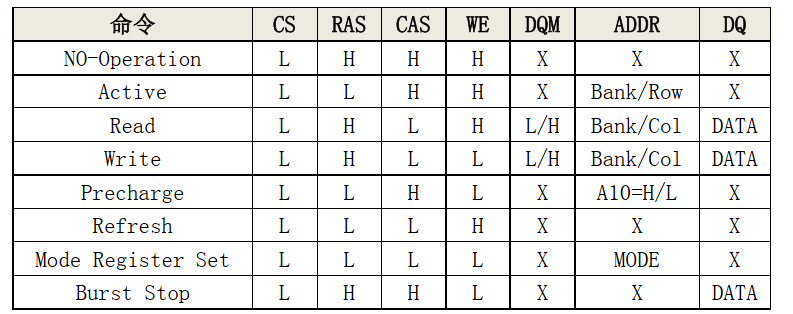

2535 SDRAM的驅(qū)動需要用到一些命令,介紹幾個常見的命令。

2023-04-04 17:13:19 1306

1306

基于DSP平臺的人民幣編號識別系統(tǒng)的設(shè)計與實現(xiàn)。

2016-05-10 16:31:07 18

18 stm32固件庫手冊使用方法(以FMC_SDRAM擴展外部儲存為例)一、SDRAM簡介二、利用固件庫FMC外設(shè)初始化1.初始化SDRAM時序結(jié)構(gòu)體2.初始化SDRAM結(jié)構(gòu)體3.初始化SDRAM命令

2022-01-20 08:22:13

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA讀寫SDRAM的實例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計論文主要包括了:FPGA讀寫SDRAM的實例,SDRAM控制器核心介紹,系列SDRAM數(shù)據(jù)手冊

2018-12-25 08:00:00 56

56 華睿科技車廂成像及編號識別系統(tǒng)是一款滿足鐵路安全檢測領(lǐng)域高清線掃成像系統(tǒng),該系統(tǒng)廣泛應(yīng)用于TVDS客車車輛運行故障動態(tài)圖像檢測、TEDS動車組運行故障動態(tài)檢測及貨車運行狀態(tài)動態(tài)檢測等領(lǐng)域。

2018-05-17 15:05:00 886

886

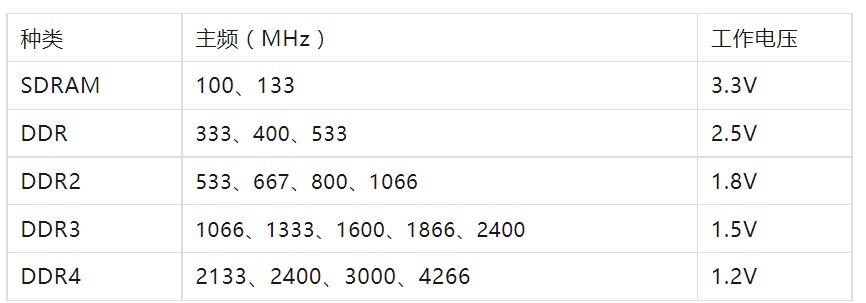

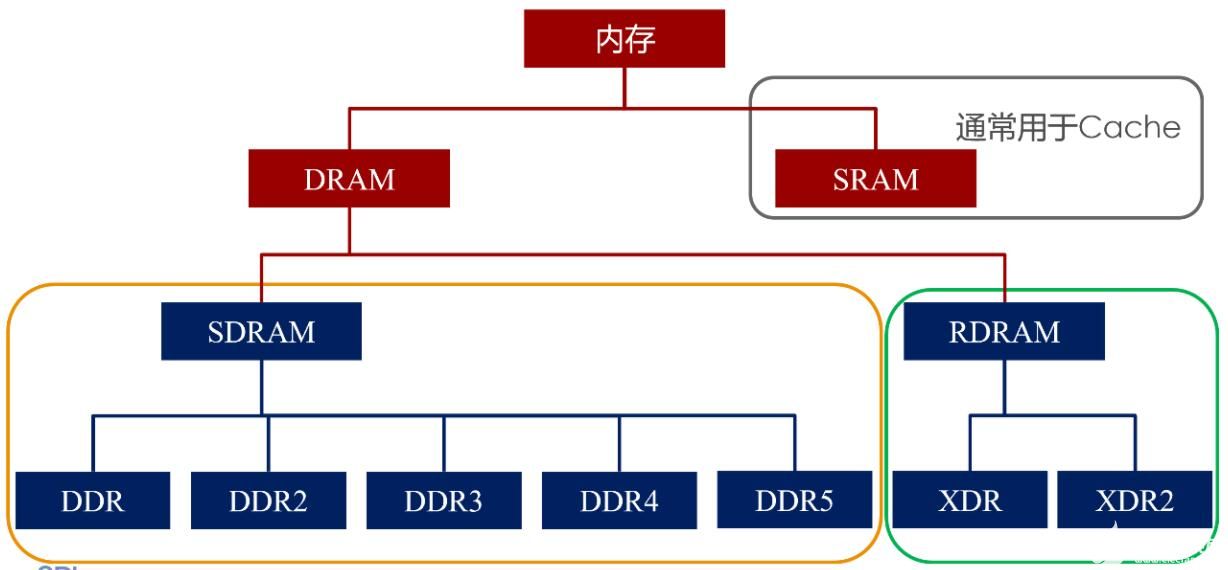

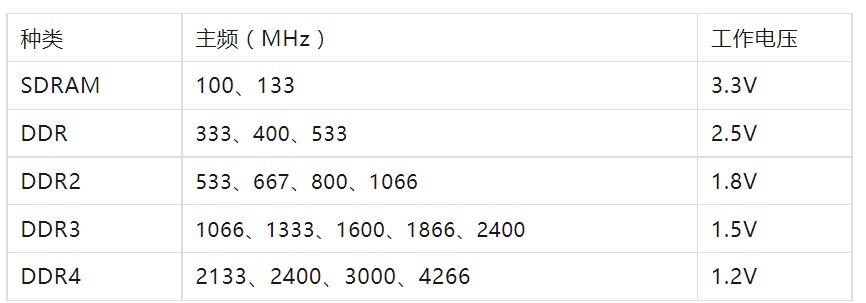

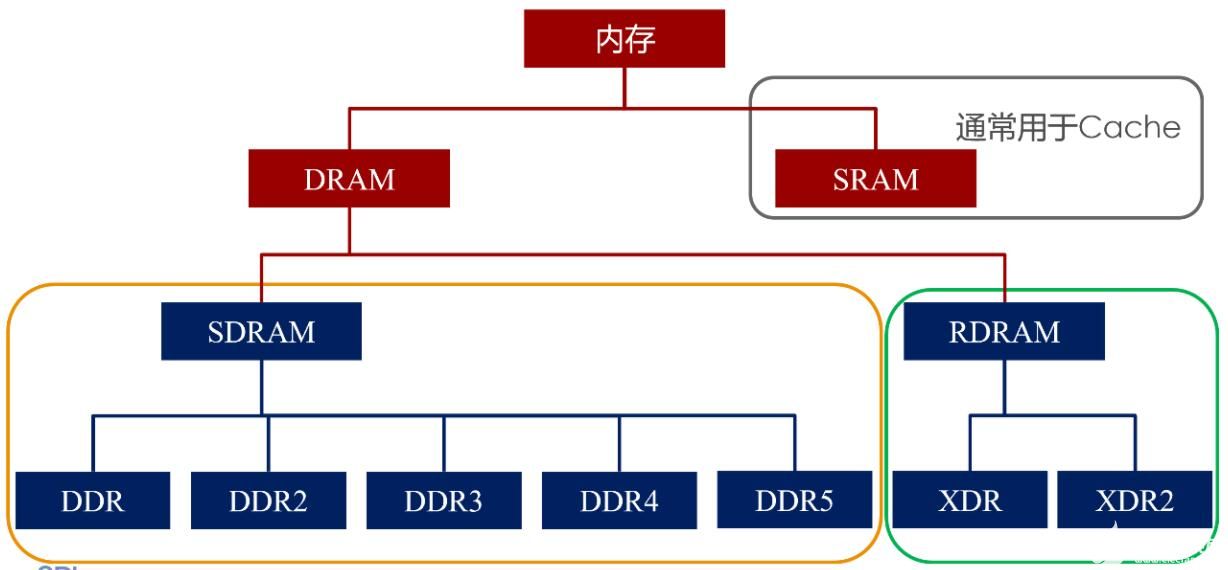

DRAM (動態(tài)隨機訪問存儲器)對設(shè)計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統(tǒng)的存儲系統(tǒng)設(shè)計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 90959

90959 動物實驗的編碼標(biāo)記雖然是動物實驗開始的**步,但是,是非常重要關(guān)鍵的一步。如果不能準(zhǔn)確地編號和今后方便地識別,有可能從實驗的**步就已經(jīng)給這個實驗的結(jié)果埋下了不可挽回的隱患。所以說有一個好的動物標(biāo)記

2022-07-26 15:47:33 0

0

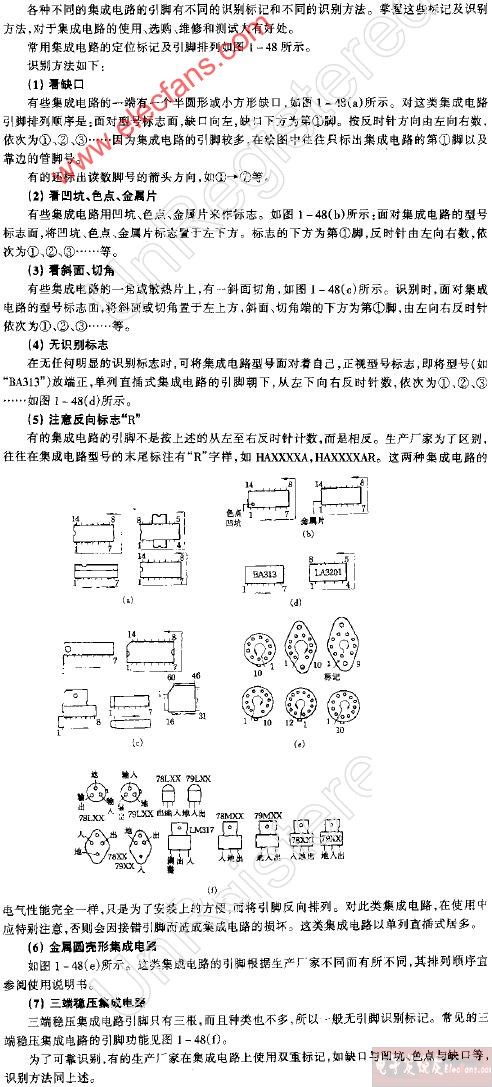

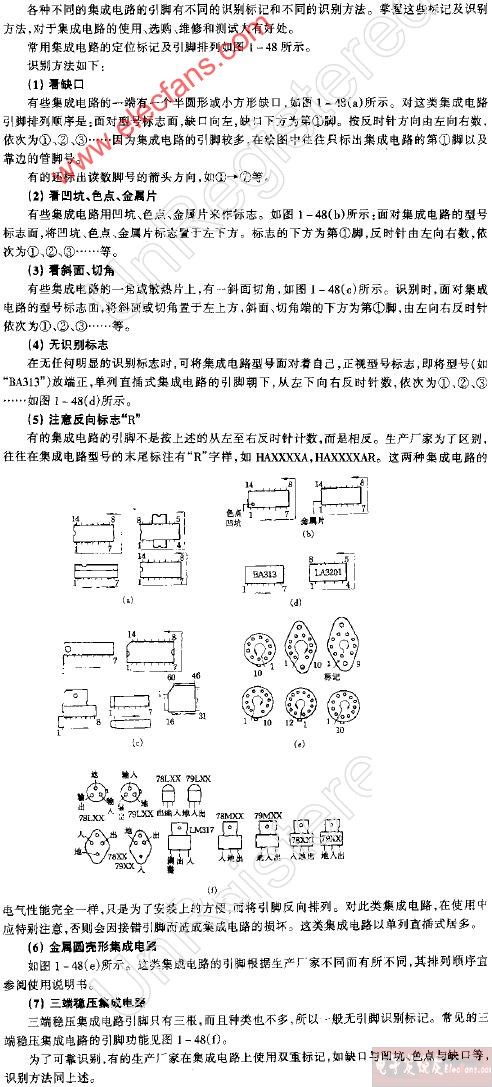

常見集成電路引腳的識別

2009-08-01 17:47:37 1113

1113

高等電力系統(tǒng)節(jié)點編號,靜態(tài)編號MATLAB程序。解決節(jié)點導(dǎo)納稀疏問題。

2016-05-09 11:57:11 0

0 SDRAM設(shè)計詳細(xì)說明

完成SDRAM的上層驅(qū)動設(shè)計,對SDRAM讀寫、管理無誤,與其他模塊的接口正確。

口令:MMCTEAM

SDRAM的工作原理

2010-04-22 14:02:57 131

131 SDRAM內(nèi)存 SDRAM是Synchronous Dynamic Random Access Memor

2009-12-17 16:15:28 617

617 SDRAM的原理和時序

2022-12-30 09:20:50 0

0 SDRAM的原理和時序

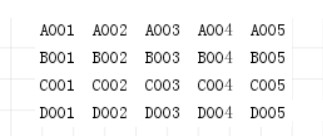

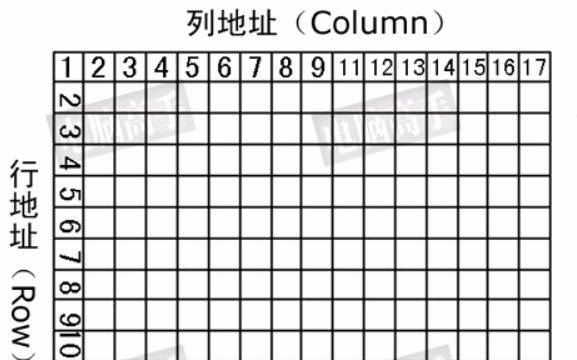

SDRAM內(nèi)存模組與基本結(jié)構(gòu) 我們平時看到的SDRAM都是以模組形式出現(xiàn),為什么要做成這種形式呢?這首先要接觸到兩個概念:物理Bank與芯片位寬

2010-03-11 14:43:26 167

167 嵌入式測試和測量挑戰(zhàn)目錄引言3-4DRAM發(fā)展趨勢 3DRAM4-6SDRAM 6-9DDR SDRAM6DDR2 SDRAM 7DDR3 SDRAM 8DDR4 SDRAM 9GDDR 和LPDDR 9DIMMs 9-13DIMM 物理尺寸 9DIMM

2010-06-30 09:28:08 93

93 電子發(fā)燒友網(wǎng)站提供《如何使用數(shù)組保存管腳編號.zip》資料免費下載

2023-01-30 15:58:09 0

0 什么是SDRAM內(nèi)存

SDRAM是“Synchronous Dynamic random access memory”的縮寫,意思是“同步動態(tài)隨機存儲器”,就是我們平時所說的“同步內(nèi)存”,這種

2009-12-17 11:14:39 683

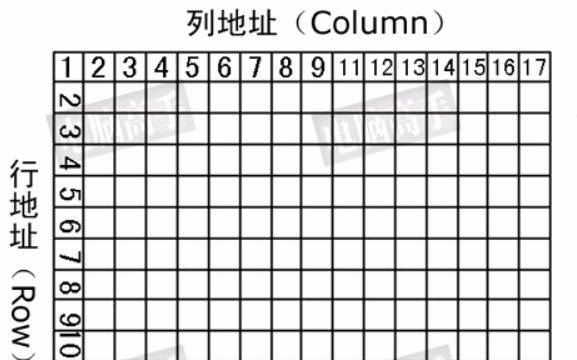

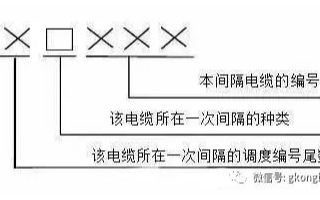

683 本間隔電纜的編號:通常從101開始編號,以先間隔各個電氣設(shè)備至端子箱電纜,再端子箱至主控室電纜,先電流回路,后控制回路,再信號回路,最后其他回路(如電氣聯(lián)鎖回路,電源回路)的順序,逐條編號,同一間隔電纜編號不允許重復(fù)。

2022-12-12 14:57:18 1561

1561 APM32E103VET6S_SDRAM模塊_SDRAM與IO口沖突問題

2022-11-09 21:03:42 0

0 ref-sdr-sdram-verilog代碼

SDR SDRAM Controller v1.1 readme.txt

This readme file for the SDR SDRAM

2009-06-14 08:50:44 32

32 為了便于二次回路的施工與日常維護(hù),根據(jù)“四統(tǒng)一”的原則,必須對電纜和電纜所用芯進(jìn)行編號,編號應(yīng)該做到使用者能根據(jù)編號了解回路用途,能正確接線。

2023-09-19 12:12:01 235

235

北橋芯片編號的意思

問:最近購買了一塊嘉玉PT890主板,采用VIA PT890芯片組,發(fā)現(xiàn)主板的南北橋芯片上又許多編號,但是不知

2010-02-05 09:36:57 1071

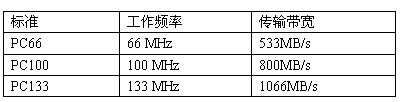

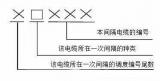

1071 SDRAM傳輸標(biāo)準(zhǔn) 標(biāo)準(zhǔn)的SDRAM分為66MHz SDRAM(即俗稱的PC 66,但PC 66并非正規(guī)術(shù)語),PC 100以及PC 133,其標(biāo)準(zhǔn)工作頻率

2009-04-26 18:03:38 895

895

DDR SDRAM內(nèi)存

DDR SDRAM是Double Dat

2009-12-17 16:20:33 666

666 DDR SDRAM 全稱為Double Data Rate SDRAM,中文名為雙倍數(shù)據(jù)流SDRAM。DDRSDRAM 在原有的SDRAM 的基礎(chǔ)上改進(jìn)而來。也正因為如此,DDR 能夠憑借著轉(zhuǎn)產(chǎn)成本優(yōu)勢來打敗昔日的對手RDRAM,成為當(dāng)今的主流

2013-09-13 15:17:30 210

210 針對SDRAM 操作繁瑣的問題,在對SDRAM 存儲器和全頁突發(fā)式操作進(jìn)行研究的基礎(chǔ)上,提出一種簡易SDRAM 控制器的設(shè)計方法。該設(shè)計方法充分利用全頁式高效率存取的優(yōu)點,對SDRAM 進(jìn)行配置、全頁突發(fā)式讀寫時,操作方便。在實現(xiàn)sDRAM 的快速批量存儲方面,具有良好的應(yīng)用價值。

2020-12-18 16:13:18 6

6 要生成的編號通常比較復(fù)雜,如根據(jù)當(dāng)天的日期建立編號,或者批量生成編號,或者將給定的批量數(shù)據(jù)中的數(shù)字轉(zhuǎn)換成位數(shù)固定的編號

2022-10-12 11:03:16 1592

1592

ref-sdr-sdram-vhdl代碼

SDR SDRAM Controller v1.1 readme.txt

This readme file for the SDR SDRAM

2009-06-14 08:52:53 46

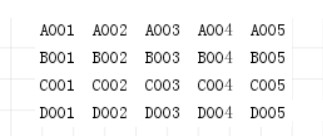

46 介紹SDRAM電路設(shè)計之前先了解下SDRAM的尋址原理。SDRAM內(nèi)部是一個存儲陣列,可以把它想象成一個表格,和表格的檢索原理一樣,先指定行,再指定列,就可以準(zhǔn)確找到所需要的存儲單元,這是內(nèi)存芯片

2018-06-11 17:11:00 3543

3543

SDRAM與DDR布線指南

2022-12-30 09:20:50 0

0 SDRAM的工作原理(中國科學(xué)院西安光學(xué)精密機械研究)

本文以三星公司的SDRAM器件K4S561632C[4]為例來是說明SDRAM的工作原理。

2010-03-26 17:54:29 155

155 SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM。第一代SDRAM

2020-04-03 16:04:01 1367

1367 DDR內(nèi)存1代已經(jīng)淡出市場,直接學(xué)習(xí)DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 1667

1667

編號的端口

任何服務(wù)器計算機都使用編號的端口向互聯(lián)網(wǎng)提供其服務(wù),服務(wù)器上可用的每項服務(wù)對應(yīng)于一個端口。例如,如果一臺服務(wù)器計算機同時運行Web服務(wù)器和FTP

2009-08-05 09:08:28 618

618 動物實驗的編碼標(biāo)記雖然是動物實驗開始的第一步,但是,是非常重要關(guān)鍵的一步。如果不能準(zhǔn)確地 編號和今后方便地識別,有可能從實驗的第一步就已經(jīng)給這個實驗的結(jié)果埋下了不可挽回的隱患。所以說 有一個好的動物

2022-07-23 09:41:33 0

0 Allwinner Axx SDRAM Support List——全志分SDRAM支持列表。

2016-09-26 16:31:14 8

8 本文檔使用 TAB = 4 對齊,使用keil5默認(rèn)配置打開閱讀比較方便。 【*】程序簡介 -工程名稱:FMC-SDRAM -實驗平臺: 秉火STM32 F429 開發(fā)板 -MDK版本:5.16

2017-12-13 15:13:37 18

18 SDRAM有一個同步接口,在響應(yīng)控制輸入前會等待一個時鐘信號,這樣就能和計算機的系統(tǒng)總線同步。時鐘被用來驅(qū)動一個有限狀態(tài)機,對進(jìn)入的...

2022-01-26 19:40:35 1

1 在很多通信芯片及系統(tǒng)的開發(fā)中,常常需要用到存儲容量大、讀寫速度快的存儲器。在各種隨機存儲器件中,SDRAM的價格低、體積小、速度快、容量大,是比較理想的器件。但是,與SRAM相比較,SDRAM的控制

2017-11-28 19:51:26 5

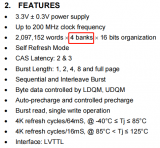

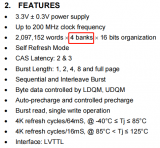

5 H57V1262GTR SDRAM模塊B型

SDRAM外擴存儲 8Mx16bit

型號 SDRAM Board (B)

2019-12-30 09:01:47 1044

1044

上圖中,把SDRAM用到的所有指令都羅列出來了,其實我們在運用SDRAM的時候,只用到其中部分指令。例如其中write/write with autoprecharge,這兩個指令我們都可以對SDRAM進(jìn)行寫操作,只是說在” writewith autoprecharge”指令

2022-05-09 10:09:29 1844

1844 SDRAM內(nèi)存詳解資料

2017-10-30 15:45:17 8

8 雖然目前SDRAM內(nèi)存條價格已經(jīng)接底線,內(nèi)存開始向DDR和Rambus內(nèi)存過渡。但是由于DDR內(nèi)存是在SDRAM基礎(chǔ)上發(fā)展起來的,所以詳細(xì)了解SDRAM內(nèi)存的接口和主板設(shè)計方法對于設(shè)計基于DDR內(nèi)存的主

2012-01-05 16:21:11 246

246 什么是SDRAM傳輸標(biāo)準(zhǔn)

標(biāo)準(zhǔn)的SDRAM分為66MHz SDRAM(即俗稱的PC 66,但PC 66并非正規(guī)術(shù)語),PC 100以及PC 133,其標(biāo)準(zhǔn)工作頻率分別為66MHz,100MHz和133MHz,對

2009-12-24 14:49:19 384

384 ? 為了便于二次回路的施工與日常維護(hù),根據(jù)“四統(tǒng)一”的原則,必須對電纜和電纜所用芯進(jìn)行編號,編號應(yīng)該做到使用者能根據(jù)編號了解回路用途,能正確接線。 二次編號應(yīng)根據(jù)等電位的原則進(jìn)行,就是電氣回路中遇于

2021-01-18 13:55:52 8768

8768

本公司目前MCU系列,到目前為止, SWM34x 支持外接8M16M SDRAM,SWD34S系列已經(jīng)把SDRAM合封入芯片,合封的SDRAM大小根據(jù)芯片型號不同,具體見官方手冊。

2023-04-28 09:30:22 961

961

SDRAM全稱Synchronous Dynamic RAM,同步動態(tài)隨機存儲器。首先,它是RAM,即隨機存儲器的一種。

2023-08-08 15:10:46 358

358

SDR SDRAM Controller August 2002, ver. 1.1 1M-WP-SDR-1.1 IntroductionThe single data rate (SDR

2009-06-14 08:51:43 95

95 本文將介紹DDR SDRAM的一些概念和難點,主要結(jié)合上一篇SDRAM的介紹加以對比。同時著重講解主流DDRII的技術(shù)。最后結(jié)合硬件設(shè)計提出一些參考。

DDR SDRAM全稱為Double Dat

2010-08-30 16:26:16 119

119 存儲在其內(nèi)部的信息不需要更新電路。SRAM具有很高的特點。 ? 同步動態(tài)隨機存取內(nèi)存(SDRAM)有一個同步接口,在響應(yīng)控制輸入之前等待一個時鐘信號,以便與計算機系統(tǒng)總線同步。時鐘用于驅(qū)動有限狀態(tài)機,并執(zhí)行進(jìn)入命令的管道操作。 英尚存儲芯片供

2022-12-08 16:03:24 310

310 貼片電容是一種常用的電子元件,應(yīng)用廣泛,具有多種不同的型號和規(guī)格。本文將介紹如何識別貼片電容及其常見型號。

2023-07-18 09:50:39 1155

1155 基于FPGA的SDRAM串口實驗(嵌入式開發(fā)板實驗報告)-基于FPGA的SDRAM串口實驗,verilog語言編寫

2021-08-04 09:43:17 37

37 SDRAM的結(jié)構(gòu)、時序與性能的關(guān)系

2022-12-30 09:20:51 0

0 什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會)進(jìn)行開發(fā)的新生代內(nèi)存技

2009-12-17 11:17:59 576

576 什么是DDR SDRAM內(nèi)存

DDR是一種繼SDRAM后產(chǎn)生的內(nèi)存技術(shù),DDR,英文原意為“DoubleDataRate”,顧名思義,就是雙數(shù)據(jù)傳輸模式。之所以稱其為“雙”,也

2009-12-17 11:15:53 1539

1539 SDR SDRAM Controller

Synchronous DRAM (SDRAM) has become a mainstream memory of choice in embedded

2009-05-14 11:04:58 46

46 摘 要:介紹了SDRAM的特點和工作原理,提出了一種基于FPGA的SDRAM控制器的設(shè)計方法,使用該方法實現(xiàn)的控制器可非常方便地對SDRAM進(jìn)行控制。

關(guān)鍵

2009-06-20 13:04:51 2016

2016 在pcb設(shè)計的后期,需要對電路板上的器件編號進(jìn)行正確擺放,快捷擺放器件的編號方法現(xiàn)在就來介紹。

2019-04-29 16:29:13 9900

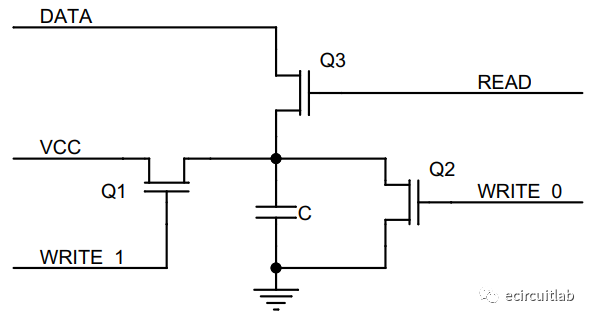

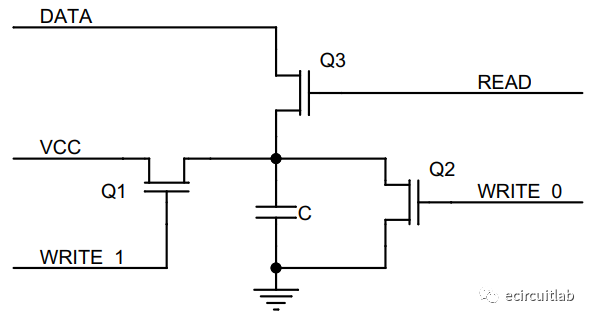

9900 所以SDRAM需要在電容的電量放完之前進(jìn)行刷新;隨機是指數(shù)據(jù)不是線性依次存儲,而是自由指定地址進(jìn)行數(shù)據(jù)的讀寫。” 這只是對SDRAM的概念介紹,下面再簡單的看一下SDRAM的內(nèi)部結(jié)構(gòu)。

2018-03-29 09:30:54 7296

7296

目前,在很多通信芯片及系統(tǒng)的開發(fā)中,常常需要用到存儲容量大、讀寫速度高的存儲器。在各種隨機存儲器件中,SDRAM 的價格低、體積小、速度快、容量大,是比較理想的器件。但是,與SRAM相比較

2021-06-30 09:16:47 2132

2132

DDR SDRAM是具有雙倍數(shù)據(jù)傳輸率的SDRAM,其數(shù)據(jù)傳輸速度為系統(tǒng)時鐘頻率的兩倍,由于速度增加,其傳輸性能優(yōu)于傳統(tǒng)的SDRAM。DDR SDRAM 在系統(tǒng)時鐘的上升沿和下降沿都可以進(jìn)行

2020-07-16 15:44:10 1779

1779 組成。 DRAM中又以SDRAM同步動態(tài)隨機存取內(nèi)存在近幾年來最廣為使用,SDRAM最重要的就是能夠“同步”內(nèi)存與處理器(CPU)的頻率,讓SDRAM頻率可超過100MHz使傳輸數(shù)據(jù)更能實時到位

2021-02-22 15:35:48 2882

2882

在現(xiàn)代的通信及基于FPGA的圖像數(shù)據(jù)處理系統(tǒng)中,經(jīng)常要用到大容量和高速度的存儲器。SDRAM有一個同步接口,在響應(yīng)控制輸入前會等待一個時鐘信號,這樣就能和計算機的系統(tǒng)總線同步。在各種的隨機存儲器件中

2020-12-06 07:41:00 1241

1241 SDRAM 以其高速和大容量的優(yōu)點獲得了極大的應(yīng)用,但是其接口與目前廣泛應(yīng)用的微處理器系統(tǒng)不兼容,介紹了用 VHDL 語言實現(xiàn)的SDRAM與RAM之間的接口控制電路,從而將SDRAM應(yīng)用到微處理器

2011-06-01 15:29:15 57

57 SDRAM存儲芯片擁有快速讀寫的性能,可以應(yīng)用以回波模擬系統(tǒng)作為數(shù)據(jù)高速緩存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有嚴(yán)格的控制時序和工作狀態(tài),可以使用有限狀態(tài)機理論

2011-10-24 15:08:05 81

81 原理圖繪制常利用復(fù)制的功能,復(fù)制完之后會存在位號重復(fù)或者同類型元件編號雜亂的現(xiàn)象,使后期BOM表的整理十分不便。重新編號可以對原理圖中的位號進(jìn)行復(fù)位和統(tǒng)一、方便設(shè)計和維護(hù)

2022-10-26 09:46:42 5286

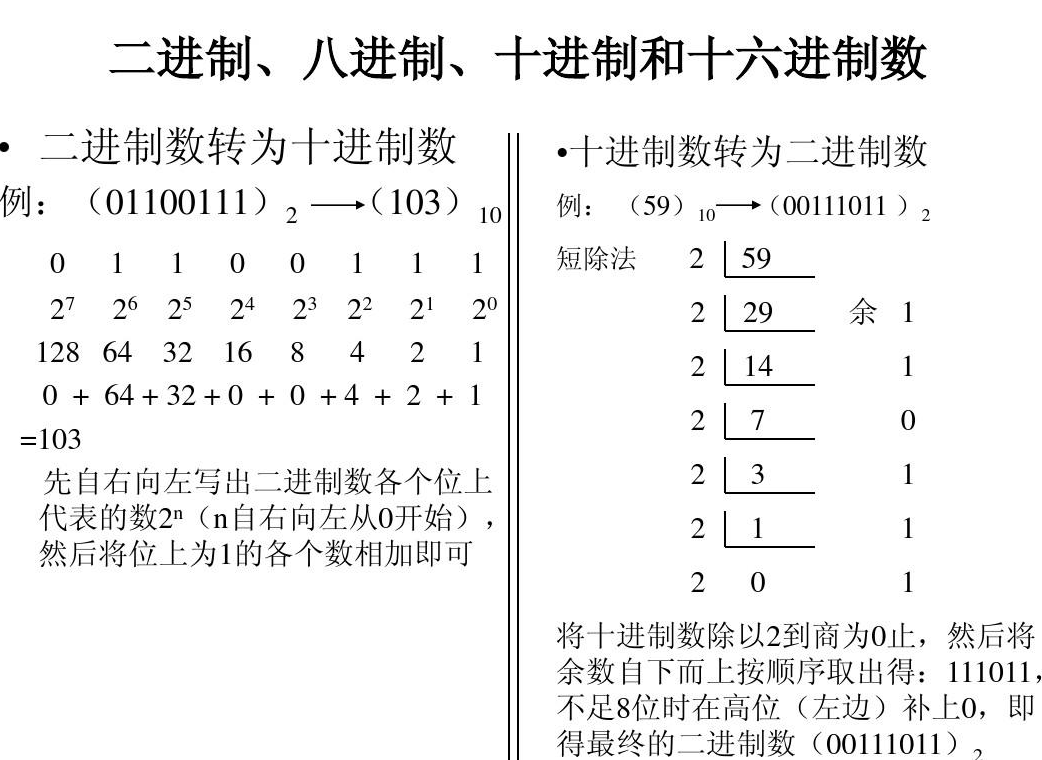

5286 八進(jìn)制編號系統(tǒng)的主要特征是 0 到 7 ,每個數(shù)字的權(quán)重或值從最低有效位(LSB)開始僅為8。在計算的早期階段,八進(jìn)制數(shù)和八進(jìn)制編號系統(tǒng)非常適用于計數(shù)輸入和輸出,因為它的計數(shù)為8,輸入和輸出的計數(shù)為8,一次一個字節(jié)。

2019-06-24 10:03:33 3764

3764

Xilinx FPGA工程例子源碼:The SDRAM controller is designed for the Virtex V300bg432-6

2016-06-07 14:41:57 8

8 本間隔電纜的編號:通常從101開始編號,以先間隔各個電氣設(shè)備至端子箱電纜,再端子箱至主控室電纜,先電流回路,后控制回路,再信號回路,最后其他回路(如電氣聯(lián)鎖回路,電源回路)的順序,逐條編號,同一間隔電纜編號不允許重復(fù)。

2018-12-07 15:53:08 4535

4535 =============================================doc DDR SDRAM reference design documentationmodel Contains the vhdl SDRAM model

2009-06-14 08:49:23 51

51 本文主要介紹的是ARM里的RAM和SDRAM有什么區(qū)別,首先介紹了RAM的類別及特點,其次對SDRAM做了詳細(xì)闡述,最后介紹了RAM和SDRAM的區(qū)別是什么。

2018-04-27 16:20:52 33997

33997 DDR5 是第五代 DDR SDRAM 的簡稱,DDR SDRAM 是英文 Double Data Rate SDRAM 的縮寫,中文譯為雙倍速率 SDRAM,而 SDRAM 又是

2020-02-03 18:30:59 4954

4954 SDRAM(synchronous dynamic random-access memory)即同步動態(tài)隨機存取內(nèi)存。在介紹SDRAM前,我們先了解下DRAM(Dynamic random-access memory),DRAR中文譯為動態(tài)隨機存取內(nèi)存

2023-09-27 15:02:32 606

606

SDRAM介紹同步動態(tài)隨機存儲器(SDRAM)特點:同步:memory工作時需要同步時鐘動態(tài):存儲陣列需要不斷刷新隨機:自由指定地址讀寫數(shù)據(jù)容量大價格便宜SDRAM存儲結(jié)構(gòu)SDRAM支持多BANK

2022-12-19 11:46:20 333

333

筆記本指紋識別器常見問題和保養(yǎng)方法

筆記本電腦的指紋識別器,實際上就是一個黃色的金屬塊,這就是指紋識別的窗口。

筆記本指紋識別器常見問題和

2009-12-18 10:17:53 9260

9260 介紹在 Nios II 中利用 SDRAM 控制模塊實現(xiàn)對 SDRAM 存儲芯片——

K4M561633G 的讀寫,通過本章,你能學(xué)到

(1)SDRAM 控制模塊的使用。

(2)在 Nios II 中讀寫 SDRAM 芯片。

2015-12-14 15:40:33 0

0 利用ISE的SDRAM設(shè)計的FIFO實驗(嵌入式開發(fā)轉(zhuǎn)后端開發(fā))-利用ISE的SDRAM設(shè)計的FIFO實驗,適合感興趣的學(xué)習(xí)者學(xué)習(xí),可以提高自己的能力,大家可以多交流哈

2021-08-04 12:14:36 18

18 SDRAM是同步動態(tài)隨機存取存儲器的縮寫。在微控制器應(yīng)用中,微控制器通過使用外部存儲控制器(EMC)操作訪問SDRAM ,SDRAM時鐘頻率通常為100MHz或133MHz。

2019-11-23 11:38:01 5660

5660

DDR_SDRAM介紹和時序圖,DDR_SDRAM介紹和時序圖

2016-02-23 11:58:38 6

6 眾所周知,SDRAM從開始工作伊始,一直伴隨著64ms刷新一遍的最基本規(guī)定(假設(shè)該SDRAM有4096行,那么必須大約15us的時間就要發(fā)出一次自刷新命令),這是為了保持SDRAM內(nèi)數(shù)據(jù)能夠在上電以后一直保持的原因,具體原因就不多解釋了,我們還是以實際操作為主。

2018-12-12 14:04:59 4891

4891 SDRAM與DDR布線指南:ecos應(yīng)用是與硬件平臺無關(guān)的,雖然開發(fā)板沒有涉及到SDRAM和DDR,不過,在某些高端平臺上使用ecos可能會遇到內(nèi)存布線問題,為了完整敘述,這里一并給出說明。 很

2010-03-18 15:29:08 170

170 SDRAM存儲器相關(guān)資料下載

2018-05-02 11:46:57 49

49 EPM1240的SDRAM控制器的設(shè)計

2017-10-31 08:24:31 21

21

電子發(fā)燒友App

電子發(fā)燒友App

評論