本文在簡(jiǎn)單介紹了全自主足球機(jī)器人比賽系統(tǒng)的基礎(chǔ)上,分析了傳統(tǒng)視覺(jué)系統(tǒng)的缺點(diǎn),給出了用cmos圖像傳感器 0v7620、SRAM幀存儲(chǔ)器 IS61LV25616、CPLD/FPGA控制器 EPF10K10LC84—3以及 DSP器件 tms320vc5416設(shè)計(jì)的新型嵌入式圖像采樣處理系統(tǒng)的設(shè)計(jì)方案。提出了RGB空間到HIS空間的變換方法,從而明顯提高了足球機(jī)器人視覺(jué)系統(tǒng)的速度和可靠性。

1 全自主式足球機(jī)器人概述

Fira的 RoboSot組是全自主足球機(jī)器人。全自主足球機(jī)器人比賽系統(tǒng)實(shí)際上是一個(gè)自主工作的小車(chē)。由于自主機(jī)器人內(nèi)部裝載有完整的控制系統(tǒng),因而不需要外界提供計(jì)算能力即可完全自主地收集和處理周?chē)h(huán)境信息,并進(jìn)行行為決策。機(jī)器人的頂端或其它部位一般安裝有彩色攝像頭,其鏡頭可以左右搖擺和上下俯仰,從而為機(jī)器人在一定的視角范圍內(nèi)提供彩色的視頻信息。此外,機(jī)器人還配備有超聲波或其它傳感器,以用來(lái)對(duì)環(huán)境進(jìn)行距離探測(cè)和障礙探測(cè)。而在多機(jī)器人參與比賽的時(shí)候,為實(shí)現(xiàn)機(jī)器人間的通信,還應(yīng)安裝無(wú)線(xiàn)通信系統(tǒng),以便其能夠共享已經(jīng)探測(cè)到的環(huán)境信息,從而構(gòu)成多機(jī)器人的協(xié)作系統(tǒng)。機(jī)器人還應(yīng)配備可充電電池組以為嵌入式計(jì)算機(jī)、傳感器、驅(qū)動(dòng)電機(jī)等提供電能。

全自主足球機(jī)器人比賽的特點(diǎn)是:不允許在比賽場(chǎng)地的正上方或其它非機(jī)器人本體上設(shè)置全局視覺(jué)系統(tǒng),而是將攝像機(jī)安裝在機(jī)器人的本體上,這樣攝像機(jī)只能提供比賽場(chǎng)地的部分信息,機(jī)器人需要不斷地將攝像機(jī)鏡頭進(jìn)行搖動(dòng)及俯仰,必要時(shí)還應(yīng)扭轉(zhuǎn)車(chē)體來(lái)搜尋需要的信息。

目前的足球機(jī)器人多采用現(xiàn)成的單板機(jī) (如PC104)再配以圖像采集卡、無(wú)線(xiàn)通信網(wǎng)卡、電機(jī)驅(qū)動(dòng)卡等板卡乜味實(shí)現(xiàn)。該方法無(wú)法獲得主板和配套板卡的硬件原理圖和主板 BIOS、板卡驅(qū)動(dòng)程序等詳細(xì)資料,因此不但體積大,而且由于硬件和驅(qū)動(dòng)軟件的限制很難達(dá)到足球機(jī)器人的最佳速度要求,同時(shí)可靠性也不高。而自行開(kāi)發(fā)足球機(jī)器人全套控制系統(tǒng)的底層硬件和底層控制軟件,雖然其自由度和靈活性高,但工作量很大。本文介紹了基于 0v7620圖像傳感器的足球機(jī)器人視覺(jué)系統(tǒng)。

2 Robosot視覺(jué)子系統(tǒng)原理

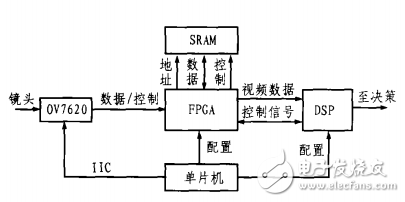

圖 1所示是一個(gè)嵌入式視覺(jué)子系統(tǒng)的硬件框圖。圖中,安裝在機(jī)器人上的cmos圖像傳感器把“球場(chǎng)”信息轉(zhuǎn)換成電信號(hào),并經(jīng)視頻采集芯片轉(zhuǎn)化為數(shù)字信號(hào)后在 FleA中進(jìn)行底層數(shù)據(jù)處理,然后在其管理下送入 SRAM幀存儲(chǔ)器。DSP在讀取 SRAM 存儲(chǔ)器中的數(shù)據(jù)并進(jìn)行高層處理后把處理結(jié)果通過(guò)DSP的MeBSP口傳送給決策子系統(tǒng)。當(dāng)與決策系統(tǒng)連線(xiàn)小于 15米時(shí),可利用 McBSP口模擬出 RS232信號(hào)以實(shí)現(xiàn)通信;而當(dāng)距離較大時(shí),則可采用 RS422或采用無(wú)線(xiàn)通信方式。

自主式足球機(jī)器人視覺(jué)系統(tǒng)硬件框圖

2.1圖像傳感器選擇

CCD攝像器件以其光照靈敏度高、噪聲低、像元尺寸小等優(yōu)點(diǎn),一直主宰著圖像傳感器市場(chǎng)。與此相反,cmos圖像傳感器過(guò)去由于存在靈敏度低、信噪比小、像元尺寸大等缺點(diǎn)而一直無(wú)法和CCD技術(shù)抗衡。但是,隨著 cmos大規(guī)模集成電路技術(shù)的不斷發(fā)展,這些缺點(diǎn)已逐漸被克服。而 cmos器件所具有的集成度高、制造成本低、單一電源供電(3.3V或5v)、功耗低和像素缺陷低等優(yōu)點(diǎn)也使其非常適合于自主式移動(dòng)足球機(jī)器人的視覺(jué)系統(tǒng)。本系統(tǒng)采用的是Omnivision公司推出的 cmos彩色圖像傳感器0v7620,該傳感器的最大分辨率為 664×492。它不但能工作在逐行掃描方式下,也能工作在隔行掃描方式下。0v7620可通過(guò) I℃總線(xiàn)配置片內(nèi)寄存器,以使其輸出RGB原始數(shù)據(jù)。系統(tǒng)加電復(fù)位后,先由單片機(jī)的I/0口產(chǎn)生 I℃總線(xiàn)信號(hào)來(lái)對(duì) 0v7620工作寄存器進(jìn)行初始化,然后 OV7620即可開(kāi)始按要求輸出圖像信號(hào),包括行同步信號(hào)HREF、場(chǎng)同步信號(hào)VSYNC、像素時(shí)鐘信號(hào)PCLK和數(shù)字圖像信號(hào)。

2.2 時(shí)序控制及圖像預(yù)處理

OV7620輸出的同步及圖像數(shù)據(jù)信號(hào)接至CPLD/Flea芯片后,即可在此進(jìn)行底層預(yù)處理,同時(shí)也在其控制下將該信號(hào)存人幀存儲(chǔ)器 SARM中。

Flea芯片選用 Ahem公司的 EPFIOKIO來(lái)接收行同步信號(hào) HREF、場(chǎng)同步信號(hào)VSYNC、像素時(shí)鐘信號(hào) PCLK及圖像數(shù)據(jù)信號(hào),同時(shí)產(chǎn)生 SRAM地址信號(hào)及寫(xiě)信號(hào)。此外,還可在 FPGA的控制下,對(duì)視頻數(shù)據(jù)進(jìn)行預(yù)處理或直接存人SRAM幀存儲(chǔ)器。FPGA處理完一場(chǎng)或一幀數(shù)據(jù)即通知 DSP讀取數(shù)據(jù)。tms320vc5416利用讀語(yǔ)句從 SRAM 中獲得視頻數(shù)據(jù),并將處理出的機(jī)器人(小車(chē))和球的位置、速度和方向信息經(jīng) DSP的McBSP口傳給決策系統(tǒng)。

2.3 幀存儲(chǔ)器選擇

視頻高速緩存方案通常有三種。

第一種是雙口RAM方式。雙口RAM具有兩套獨(dú)立的數(shù)據(jù)、地址和控制總線(xiàn),因而可從兩個(gè)端口同時(shí)讀寫(xiě)而互不干擾,并可將視頻數(shù)據(jù)從一個(gè)端口寫(xiě)入而由DSP(或其他處理器)從另一端口讀出。雙口RAM能達(dá)到很高的傳輸速度,并且具有隨機(jī)存取的優(yōu)點(diǎn),缺點(diǎn)是大容量的高速雙口RAM很難買(mǎi)到且價(jià)格昂貴,并且要占用大量的 FPGA引腳。

第二種是 FIFO先進(jìn)先出方式。FIFO存儲(chǔ)器就象數(shù)據(jù)管道一樣,數(shù)據(jù)從管道的一側(cè)流人,從另一側(cè)流出,先進(jìn)入的數(shù)據(jù)先流出。FIFO具有兩套數(shù)據(jù)線(xiàn)而無(wú)地址線(xiàn),可在其一端寫(xiě)操作而在另一端進(jìn)行讀操作。數(shù)據(jù)在其中順序移動(dòng),因而能夠達(dá)到很高的傳輸效率,且由于省去了地址線(xiàn)而有利于 PCB板布線(xiàn)。缺點(diǎn)是只能順序讀寫(xiě)數(shù)據(jù),因而顯得比較呆板,而且大容量的高速 FIFO多采用動(dòng)態(tài) RAM技術(shù)來(lái)刷新控制電路。

第三種是高速 SRAM切換方式。高速 SRAM只有一套數(shù)據(jù)、地址和控制總線(xiàn),可以通過(guò)三態(tài)緩沖門(mén)分別接到視頻采樣和 DSP上。進(jìn)行視頻采樣時(shí) ,可將SRAM的數(shù)據(jù)、地址和控制總線(xiàn)切換到采樣電路并由采樣電路控制,而 DSP的數(shù)據(jù)、地址和控制總線(xiàn)相對(duì) SRAM處于高阻態(tài)而不起作用;當(dāng)視頻采樣結(jié)束后,SRAM的數(shù)據(jù)、地址和控制總線(xiàn)又切換到 DSP 一 側(cè),以便 DSP進(jìn)行讀寫(xiě)。而此時(shí)采樣電路所控制的數(shù)據(jù)、地址和控制總線(xiàn)又相對(duì) SRAM處于高阻態(tài)而不起作用。這種方式的優(yōu)點(diǎn)是 SRAM可隨機(jī)存取,同時(shí)較大容量的高速 SRAM容易得到,且價(jià)格適中,缺點(diǎn)是切換控制電路比較復(fù)雜,且只能由視頻采樣和 DSP分時(shí)讀寫(xiě)。為此,可引入雙體存儲(chǔ)交替訪問(wèn)的方案,即再增加一片SRAM幀存儲(chǔ)器以構(gòu)成雙體存儲(chǔ)區(qū)。這樣,兩芯片便可交替采樣并與 DSP交換數(shù)據(jù),從而實(shí)現(xiàn)采樣與 DSP讀取數(shù)據(jù)的同時(shí)進(jìn)行。

綜合考慮以上三種高速緩存方案的性能、價(jià)格和方便性,本設(shè)計(jì)選用第三種方案并選用一片IS61LV25616芯片來(lái)實(shí)現(xiàn)。

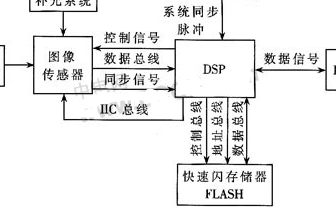

2.4視頻處理 DSP

視頻處理選用TI公司的 tms320vc5416來(lái)讀取SRAM中的視頻數(shù)據(jù),并通過(guò)軟件計(jì)算出機(jī)器人及球的位置、方向和速度,再把這些數(shù)據(jù)傳送到?jīng)Q策系統(tǒng)。tms320vc5416的時(shí)鐘速率可達(dá) 160MIPS,并且有先進(jìn)的指令系統(tǒng),在 FPGA的“協(xié)作”下 ,每秒可保證處理 l0幀 (20場(chǎng))以上的視頻數(shù)據(jù),因而可確保比賽的實(shí)時(shí)性。DSP在系統(tǒng)上電之后,其內(nèi)部的Bootloader程序首先運(yùn)行,同時(shí)將存儲(chǔ)于片外 FLASH 的程序和表格送到片內(nèi) RAM中運(yùn)行。這樣每秒可處理20幀以上的視頻數(shù)據(jù)。

2.5 單片機(jī)

單片機(jī)選用可在外部擴(kuò)展 FLASH ROM 的AT89C51/AT89C52。該單片機(jī)有三個(gè)作用:OV7620的控制、FPGA的配置及 DSP的啟動(dòng)。由于 EPF10K10在工作期間將配置數(shù)據(jù)保存在SRAM中,而SRAM是易丟失的。因此,SRAM單元必須在器件加電后裝人配置數(shù)據(jù),且在配置完成后將其存儲(chǔ)器和 I/O引腳初始化。初始化后,器件即可進(jìn)人用戶(hù)模式并開(kāi)始系統(tǒng)運(yùn)行。在開(kāi)發(fā)調(diào)試階段,可通過(guò)下載電纜對(duì)器件進(jìn)行配置,而當(dāng)整個(gè)系統(tǒng)設(shè)計(jì)完成后,便可利用單片機(jī)系統(tǒng)對(duì)其進(jìn)行配置。這樣,固化在單片機(jī)系統(tǒng)中的數(shù)據(jù)就可在系統(tǒng)上電時(shí)對(duì) FPGA芯片進(jìn)行配置。

3 軟件原理及調(diào)試

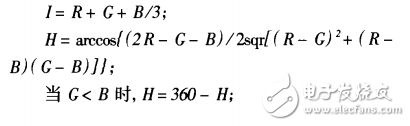

由于 OV7620輸出的是 RGB信號(hào) ,因此可直接利用此信號(hào)進(jìn)行圖像分割。但 RGB空間各分量具有很高的相關(guān)性,而顏色相近點(diǎn)的分散分布也不適于機(jī)器人足球系統(tǒng)。為此,可采用具有明確物理意義的HSI空間。該空間模型中的 H為色調(diào),對(duì)應(yīng)于光的主波長(zhǎng);S為飽和度,對(duì)應(yīng)于顏色中摻和白光的程度;I為光強(qiáng)度,對(duì)應(yīng)于光的明亮程度。HSI空間模型以 H 為主要分割參數(shù),但當(dāng) I較小時(shí),H的值趨向于不確定,因而此時(shí) H不能作為唯一的識(shí)別依據(jù) ,而應(yīng)把 I 也作為識(shí)別依據(jù)。實(shí)現(xiàn)時(shí),可用下面公式將 RGB空間變換到 HSI空間。

由于上述運(yùn)算中有反三角函數(shù),因而很難用FPGA實(shí)現(xiàn)。為此,在不影響識(shí)別結(jié)論的前提下,可利用下列簡(jiǎn)化公式來(lái)計(jì)算 H和 I:

FPGA使用的開(kāi)發(fā)軟件為 MAX+PLUSI。該軟件是一個(gè)集設(shè)計(jì)輸人、編譯、仿真和編程為一體的超級(jí)集成環(huán)境。FPGA的設(shè)計(jì)有 4個(gè)基本階段:設(shè)計(jì)輸人 、設(shè)計(jì)編譯、設(shè)計(jì)驗(yàn)證和器件編程。設(shè)計(jì)時(shí)應(yīng)首先根據(jù)系統(tǒng)的邏輯功能生成頂層結(jié)構(gòu)圖,然后分成幾個(gè)小模塊進(jìn)行下一級(jí)設(shè)計(jì)。接下來(lái)可由上而下分析其邏輯功能,并從底層進(jìn)行設(shè)計(jì)編譯,再對(duì)每一級(jí)進(jìn)行波形驗(yàn)證。當(dāng)最后的頂層模塊的邏輯功能在波形仿真中滿(mǎn)足系統(tǒng)時(shí)序要求時(shí),即可進(jìn)行器件編程。

用FPGA實(shí)現(xiàn) RGB空間到 HIS空間的轉(zhuǎn)換,并進(jìn)行色標(biāo)圖像分割以及色標(biāo)及機(jī)器人中心的計(jì)算時(shí),其數(shù)據(jù)處理量雖然遠(yuǎn)小于FPGA處理的數(shù)據(jù)量,但算法本身比較復(fù)雜,因而可用 DSP完成。初始調(diào)試時(shí),應(yīng)先盡量減少 FPGA的運(yùn)算量 ,然后把運(yùn)算任務(wù)交給DSP。當(dāng)DSP中的算法經(jīng)實(shí)踐檢驗(yàn)成熟后,便可將其移植到 FPGA中,以進(jìn)一步提高整個(gè)系統(tǒng)的速度。

4 結(jié)論

本文討論的嵌人式視覺(jué)系統(tǒng)方案綜合運(yùn)用了cmos圖像傳感器、FPGA、高速SRAM、數(shù)字信號(hào)處理器及單片機(jī)等先進(jìn)電子技術(shù),充分發(fā)揮了 FPGA的快速并行處理能力,同時(shí)利用了DSP強(qiáng)大靈活的數(shù)值運(yùn)算能力。目前,本系統(tǒng)已應(yīng)用到某足球機(jī)器人系統(tǒng)中,具有很強(qiáng)的實(shí)用性。但該系統(tǒng)僅實(shí)現(xiàn)了軟硬件的初步研制與開(kāi)發(fā)。進(jìn)一步的FPGA圖像預(yù)處理算法及視覺(jué)系統(tǒng)的變焦距問(wèn)題還沒(méi)有考慮,因而還有許多工作要做。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論