IP核是指在電子設計中預先設計的用于搭建系統芯片的可重用構件,可以分為軟核、固核和硬核三種形式。軟核通常以可綜合的RTL代碼的形式給出,不依賴于特定的工藝,具有最好的靈活性。硬IP核是針對某種特定

2021-07-22 08:24:29

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級

2018-12-11 11:07:21

目前,我在設計中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉換器AD9683轉換完成后的數據。但是JESD204 IP核的端口很多,我不知道應該如何將AD9683

2023-12-15 07:14:52

優勢,這些都是目前的IP技術所不及的。和傳統的STM電路相比,ATM技術對數據交換中猝發分組的適應能力和傳輸線路的利用率都是很高的。雖然,由于靈活性和價格的原因,ATM技術沒有獲得預期的成功,但其流量

2011-09-27 11:54:25

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

BRAM IP核包括哪幾種類型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

初始化時存入數據。那在IP核rom中存放大量數據對FPGA有什么影響,比如我想存65536個16位的數,然后在64M或者128M的時鐘下讀出來。會不會導致FPGA速度過慢?

2013-01-10 17:19:11

是具有知識產權核的集成電路芯核總稱,是經過反復驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關,可以移植到不同的半導體工藝中。到了SOC 階段,IP 核設計已成為ASIC 電路設計公司和FPGA

2018-09-03 11:03:27

FSL總線IP核及其在MicroBlaze系統中的應用

2015-01-18 21:01:20

,國際上只有I-Shou大學的Yu-Jung Huang等人設計了可驅動不同規模LCD的驅動電路IP核,通過在系統中植入嵌入式微處理器來實現這一功能。但是,這種嵌入式微處理器使系統更復雜,而且成本更高

2012-08-12 12:28:42

1.安裝 IP 核

(1)打開工程,點擊菜單欄中【tools】 下的【IP Compiler】。

IP Compiler

(2)在彈出的 IP Compiler 界面中,選擇【File】下

2023-06-26 10:41:47

通用的IP核,使得用戶可輕松集成屬于自己的專用功能;但對于一些特定的外設,沒有現成可用的IP核,如液晶模塊CBGl28064等。用戶可通過自定義邏輯的方法在SOPC設計中添加自定義IP核。在實際應用中

2019-08-06 08:29:14

和PCIE之間有什么聯系,敬請關注我們的連載系列文章。在本篇文章中暫時先不講解AXI4協議,先來分享例化AXI4的自定義IP核詳細步驟。一、 新建工程為了節省篇幅,新建工程部分就不詳細講解,以下為我們

2019-12-13 17:10:42

很多人都說QUARYUSII中的IP核是收費的,不可以直接用的,其實不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對大家有點幫助。 1.使用 (1)首先建立工程,這個就不

2019-06-03 09:09:51

請問一下ATAN ip核中的輸出為什么經常出現3F800000?而且我的輸入是很多零中插著一個有效值,但是很多情況下的輸出是連著有兩個不為零的輸出啊?其中第一個還是固定的80000000???很無助啊 。。。。好人一生平安!!!!

2017-04-14 15:40:46

S32G2 聚四氟乙烯

S32G2是ip核還是外設?

如果是ip核,是否可以集成到其他SoC中?

謝謝

2023-06-02 08:04:53

,支持MII、GMII、RGMII、SGMII和TBI接口。在PG051當中為我們進行了詳細的介紹。但光看這文檔效率太低,我們還是在應用種去理解吧。該模塊可以是對協議的具體解析了,需要我們了解TCP/IP協議棧。3.1 IP核的配置 對于該核的配置相對來說還是比較簡單的,如下...

2021-07-22 07:26:36

USB_OTG_IP核中AMBA接口的設計與FPGA實現

2012-08-06 11:40:55

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實現高清圖像轉標清圖像(具體就是1080p50轉576i30

2015-04-13 14:12:18

按鈕是灰色的 情況) 在 Tcl console中 執行如下一條命令即可: upgrade_ip [get_ips] 以上兩種方法均不能解決時,使用第三種方法。 3 工程另存為 至此IP解封。

2021-01-08 17:12:52

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

WCDMA無線接口技術第5章 WCDMA無線接口技術在WCDMA系統中,移動用戶終端UE通過無線接口上的無線信道與系統固定網絡相連,該無線接口稱為Uu接口,是WCDMA系統中

2009-09-18 16:48:46

請問哪位高手有ise軟件中的各個ip核的功能介紹

2013-10-08 16:41:25

我在planahead中產生ip核時總會有個warning去不掉如下[sim 0] Verilog simulation file type 'Behavioral' is not valid

2012-10-09 11:24:30

本帖最后由 ys_1*****8201 于 2016-5-19 14:16 編輯

Quartus IP核破解在完成quartus軟件安裝之后,一般都要進行一個軟件破解。對于一般的需求來說

2016-05-19 14:13:09

2.5MHz 振幅0-5V 的正弦信號,請問 data 端口應該輸入怎樣的信號?如果有Altera IP核相關的詳解資料推薦下更好。多謝了。

2014-10-28 12:34:41

在quartusII中,應用fft ip核時,variable streaming 模式下的bit-reverse(位翻轉)是什么意思?煩勞詳細幫助新手解釋一下,不甚感激

2017-01-09 10:55:59

數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。使用Verilog調用IP

2018-05-15 12:05:13

通過Quartus II 軟件創建PLL IP核。首先,要新建一個工程,這個方法在之前的帖子中已經發過,不會的可以查看前面的相關帖子。創建好自己的工程:打開如下的菜單

2016-09-23 21:44:10

本文介紹一款USB OTG IP核的設計與實現,該設備控制器可作為IP核用于SoC系統中,完成與主機控制器的通信,并能與普通的USB從設備進行通信。

2021-04-29 06:47:00

隨著電路規模不斷擴大,以及競爭帶來的上市時間的壓力,越來越多的電路設計者開始利用設計良好的、經反復驗證的電路功能模塊來加快設計進程。這些電路功能模塊被稱為IP(Intellectual Property)核。

2019-11-04 07:40:53

本文介紹在使用Arm DesignStart計劃開放的處理器核搭建SoC并通過FPGA實現的過程中所用工具軟件(不介紹如何操作),理清“軟件編程”和“硬件編程”的概念,熟悉SoC設計的流程。軟硬件

2022-04-01 17:48:02

剛剛接觸IP核做FFT,現在用的是FFTV9.0,已經建立了一個IP核,但是如何仿真呢?是用quartus自帶軟件,還是要用MATLAB?抑或其他?我用的自帶軟件,但是什么也沒有出來。正確的辦法應該怎樣呢,謝謝指點。

2011-04-21 10:22:31

最近在做一個FIR低通濾波器,利用Matlab 產生濾波系數,導入到Quartus中,再利用其中的FIR IP核進行濾波器設計,在采用分布式全并行結構時,Modelsim 仿真有輸出;如果改為分布式

2018-07-05 08:33:02

quartus ii9.0創建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調用這些IP核,這幾個文件全部要添加嗎?

2013-07-02 17:20:01

嗨,我想在EDK中使用ISE中提供的PCI Express IP核,這意味著我應該將所有ISE IP核的verilog模塊導入EDK。這是可能的,如果可能的話請發送相關文件。謝謝&問候,Madhu.B

2020-03-24 08:14:50

標準,因此,開發統一的IP核接口標準對提高IP核的復用意義重大。本文簡單介紹IP核概念,然后從接口標準的角度討論在SoC設計中提高IP核的復用度,從而簡化系統設計和驗證的方法,主要討論OCP(開放核協議

2019-06-11 05:00:07

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

實現的RTL級設計,與具體實現工藝無關,相比于固核和硬核具有較大的靈活性,在FPGA中定制PCI接口軟核實現PCI接口控制具有明顯的優勢:可以在單片FPGA中同時完成PCI接口和用戶邏輯的設計,縮減成

2018-12-04 10:35:21

模型;然后合理劃分各摸塊功能規范,制定各模塊之間的接口協議與標準;再設計出一系列通用的IP核;最后把所需的通用IP核搭建整合在一起構成完整的智能傳感器系統。 智能傳感器IP核設計與SOC構建 &

2008-08-26 09:38:34

基于DSP核控制的SoC系統是由哪些部分組成的?基于DSP核控制的SoC系統該如何去設計?

2021-06-18 09:42:47

我畢業設計要做一個基于FPGA的IP核的DDS信號發生器,但是我不會用DDS的IP核,有沒有好人能發我一份資料如何用IP核的呀。我的瀏覽器下載不了網站上的資料,所以只能發帖求幫忙了。

2015-03-10 11:46:40

Implement頁面中,可以對FPGA存儲器或乘法器相關的資源進行選擇配置。在配置頁面左側,可以查看IP接口(IP Symbol)、實現信號位寬細節(ImplementationDetails

2019-08-10 14:30:03

,設計的USB協議層模塊各功能達到了預期目標、整體性能良好。此IP core可以廣泛應用于各種USB設備接口、通信轉接器件,也可以集成在SOC中,作為系統芯片總線接口。文中設計的USB IP已成功地應用于

2018-11-21 11:30:06

穩定性和可擴展性的固件結構。 2 USB2.0設備接口IP核的設計USB2.0設備接口芯片IP核分為硬件和固件兩大部分。其中硬件部分主要完成USB2.0協議中的鏈路層功能;而固件除協助硬件完成USB2.0

2018-12-03 15:24:04

通用的IP核,使得用戶可輕松集成屬于自己的專用功能;但對于一些特定的外設,沒有現成可用的IP核,如液晶模塊CBGl28064等。用戶可通過自定義邏輯的方法在SOPC設計中添加自定義IP核。在實際應用中

2019-08-05 07:56:59

告沒被運行的“邊際”(cornercase)。IP提供商必須提供一個進行接口完全驗證所需的邊角情況表。在開發過程中,協議制表器將幫助SoC團隊決定哪些“邊際”情況需要繼續驗證。一旦開發結束,它同時確保通知

2021-07-03 08:30:00

導航系統SoC芯片設計的要求有什么?如何構建基于LEON開源軟核的SoC平臺?

2021-05-27 06:18:16

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據

2022-02-08 07:08:01

HiI致力于研究在FPGA / Spartan 3E上連接打印機的研究項目。我可以獲得打印機接口IP核,或者沒有這樣的核心。如果可能,請幫助我。感激地以上來自于谷歌翻譯以下為原文HiI work

2019-07-04 06:32:58

on Chip)是以嵌入式系統為核心,以IP復用技術為基礎,集軟、硬件于一體的設計方法。使用IP復用技術,將UART集成到FPGA器件上,可增加系統的可靠性,縮小PCB板面積;其次由于IP核的特點

2019-08-20 07:53:46

本文在分析OpenCores網站提供的一款OC8051IP核的基礎上,給出了一種仿真調試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

的經驗幾乎為0,因此我想就如何解決這個問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉換VHDL中的C代碼(我現在有一些經驗)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

工欲善其事,必先利其器。在電子技術飛速發展的今天,熟練使用相關工具軟件是學習SoC的必經之路。但是,由于SoC是一個完整的系統,既包含處理器核、總線、外設等硬件,也包含處理器需要執行的指令,所以

2022-07-13 15:04:56

有人知道為什么MIG IP核中的AXI協議。為什么沒有AXI_WID這個信號呢。

2018-04-13 09:22:30

所搭的IP軟核的通訊協議與總線支持的通訊協議(ICB)不同怎么轉換?

2023-08-17 07:05:35

://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw提取碼:ld9c1概述Vivado標準IP核的移植可謂簡單至極。簡單3步,拷貝IP文件夾到當前工程目錄下;在Vivado的IP Sources中

2019-09-04 10:06:45

數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。使用Verilog調用IP

2018-05-16 11:42:55

,輸出才是正確的。我知道實際設計中肯定不是這么做的,我想到的處理方法是:1.兩個IP核都可以選擇輸出ready信號,所有可以等兩個都ready之后才進行加法操作。2.在第二個IP上加19個時鐘的延時,這樣

2021-06-19 11:06:07

請教大神怎樣使用ARM DesignStart計劃開放的處理器核搭建SoC系統呢?

2022-07-29 15:01:05

請問Altera RAM IP核怎么使用?

2022-01-18 06:59:33

設計。本人剛剛接觸FPGA,對IP核的理解也是一知半解,是說比如我在verilog中,不能使用+,-,*,/,而必須自己親自設計,只可以用& ,|,!,^這些運算是么?當然我知道IP核遠遠不止我提到的這些,但是最基本的+,-,/,*肯定都不可以使用是吧。謝謝大家了!

2018-04-06 20:46:11

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設計?

2021-04-28 06:10:23

我有興趣購買“Xilinx Zynq-7000 SoC ZC702評估套件”我想知道成像/視頻IP核是否包含在主板附帶的軟件開發中。謝謝---------- Khlitoshi

2019-09-05 09:48:00

(Intellectual Property)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短

2019-07-29 08:33:45

開放核協議—IP核在SoC設計中的接口技術

2019-05-27 09:52:01

控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個發展趨勢。許多公司推薦使用現成的或經過

2019-04-12 07:00:09

本文討論了以IP(Intellectual Property)內核為中心的開放式IP 核接口協議(OCP Open CoreProtocol),包括協議特性以及基于OCP 協議的SoC(System on Chip)中設計與驗證等,并在此基礎上提出了基于OC

2009-12-04 11:39:53 14

14 本文討論了以IP(Intellectual Property)內核為中心的開放式IP 核接口協議(OCP Open CoreProtocol),包括協議特性以及基于OCP 協議的SoC(System on Chip)中設計與驗證等,并在此基礎上提出了基于OC

2009-12-14 10:48:11 21

21 摘 要:本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。 引言隨著半導體技術的發展,深亞微米工

2006-03-24 13:31:58 661

661

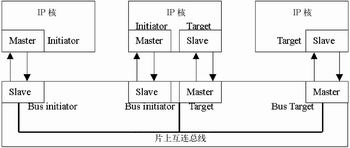

的接口標準,因此,開發統一的IP核接口標準對提高IP核的復用意義重大。本文簡單介紹IP核概念,然后從接口標準的角度討論在SoC設計中提高IP核的復用度,從而簡化系統設計和驗證的方法,主要討論OCP(開放核協議)。 圖1 OCP工作原理示意圖 圖2 讀/寫操作

2017-11-06 11:30:08 0

0

電子發燒友App

電子發燒友App

評論