鎖相環 (PLL) 是電子系統中最通用、最靈活和最有價值的電路配置之一,因此在許多應用中都有使用。它用于時鐘重定時和恢復,作為頻率合成器和可調諧振蕩器,僅舉幾個例子。因此,在包括無線電接收器和測試設備在內的許多 RF 設備項目中都可以找到 PLL。根據其具體實現,它可以服務于近直流到 GHz 和更高的頻率,在系統和電路中發揮許多關鍵作用。

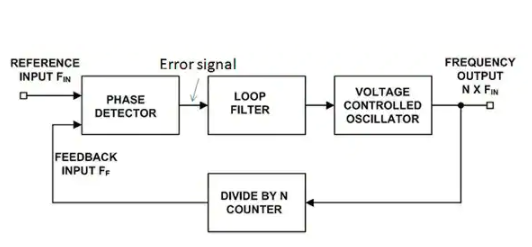

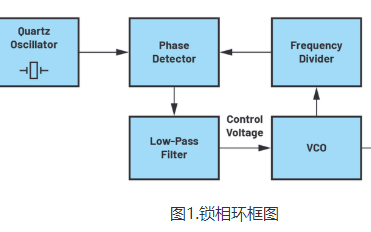

PLL 是閉環(負反饋)架構,基本 PLL 由以下模塊組成(圖 1):

圖 1:基本 PLL 是一個閉環負反饋系統,其中參考信號和 VCO 輸出之間的誤差用于校正該輸出;低通濾波器是建立環路動態的關鍵要素。

相位/頻率檢測器 (PFD)(通常簡稱為相位檢測器 PD)將輸入信號與參考信號進行比較,并產生與其相位差成正比的誤差信號(請記住,相位和頻率密切相關,因為頻率是相位的時間導數);相位檢測器的輸出通常進入電荷泵,將小電流差轉換為更大的電壓

一個低通濾波器 (LPF),它對誤差信號的頻譜進行整形;這種濾波器的設計通常是工程科學和直觀藝術的結合,并且是設置 PLL 操作的許多動態的主要因素

輸出相位/頻率由誤差信號控制的壓控振蕩器 (VCO)

VCO 輸出端的可選分頻器,它使 PLL 以參考頻率的倍數 N 生成頻率;N 可以是整數,許多 PLL 設計支持小數 N 非整數除法

VCO(和分頻器,如果使用)的輸出進入相位/頻率檢測器以完成反饋環路。在操作中,誤差信號隨著相位差的增加而增加。這會以相反方向驅動 VCO 相位,從而減少誤差信號。結果,輸出的相位被鎖定到另一個輸入的相位。

當 PLL 輸出密切跟蹤輸入并且誤差信號較小且相對穩定時,PLL 被稱為“鎖相”或簡稱為“鎖相”。根據應用,系統中使用的 PLL 系統的輸出要么是 VCO 的輸出,要么是 VCO 的控制信號。

當然,PLL 最初是在 1920 年代左右使用真空管設計的。隨著 1970 年代第一款大眾市場 PLL 作為 IC Signetics NE565 用于 0.001 Hz 至 500 kHz 工作頻率的推出,它們的受歡迎程度顯著擴大。雖然這部分現在顯然已經過時(Signetics 早已不復存在),但其數據表已存檔并可在線獲取1。

PLL 可以使用模擬、數字或混合信號電路構建。早期的 PLL 是全模擬的,帶有模擬鑒相器、低通濾波器、VCO 和可選的分頻器;除法器很快升級為數字除法器,以允許整數和小數整數除法。數字 PLL 現在用升降計數器代替相位檢測器,該計數器在數字域中執行類似功能,并且還可以使用數字濾波器,誤差信號驅動直接數字合成器作為 VCO。

由于其內部結構的模塊化、廣泛使用和廣泛應用,PLL 是莎士比亞或詹姆斯喬伊斯作品的工程對應物,因為它已成為無數文章、論文和書籍的主題。他們通過廣泛的定性討論和高度詳細的定量模型對 PLL 進行了廣泛的分析;幾乎所有此類分析都始于 Gardner 和 Viterbi 的經典著作2,3。

可用的技術論文涵蓋了 PLL 的性能,包括每個功能塊中的多種噪聲、抖動、漂移、非線性、失真和其他電路缺陷,以及多種輸入信號的性能。其中包括在時域和頻域中檢查 PLL 操作的論文;一些專注于簡單的一階模型,而另一些則使用高度復雜的模型來捕捉 PLL 電路和信號的許多真實世界的細微之處。

PLL 參數滿足應用目標

與大多數電子電路一樣,有一些基本參數適用于幾乎所有應用,有些在特定情況下更為關鍵。通過調整相位檢測器、低通濾波器、VCO 和分頻器的一些設計細節,PLL 設計可以在這些參數之間權衡性能,以最好地滿足應用優先級。頂級因素包括:

工作頻率:PLL 及其 VCO 的標稱、自由運行頻率

工作范圍:PLL 和 VCO 將工作的頻率跨度。這包括 PLL 可以獲取信號并實現鎖定的拉入范圍,以及一旦實現它可以保持鎖定的更寬范圍

轉換或捕獲時間:PLL 捕獲并鎖定在操作外部限制的信號所花費的時間,這在很大程度上由低通濾波器決定;帶寬較窄的濾波器具有較長的捕獲時間,但會限制噪聲和抖動,而帶寬較寬的濾波器具有更快的響應,但允許更多噪聲通過 PLL 系統

噪聲和抖動:由 PLL 的元件添加并因此出現在其輸出端的任何噪聲或抖動,即使是完美的信號也是如此。整體噪聲品質因數 (FOM) 以 dBc/Hz 表示,有幾種不同類型的 FOM

死區:當相位/頻率檢測器的兩個輸入非常接近時,檢測器可能看不到這一點,因此不會產生錯誤輸出;這有點類似于電子滯后或機械靜摩擦

許多其他因素也可能適用于不同應用中的 PLL,例如無雜散動態范圍 (SFDR)、失真、截距和溫度系數;完整的列表可能很長。

PLL IC 在頻率、性能、集成度方面不斷提高

為了實現給定應用的最佳性能因素組合,PLL 用戶將購買并連接單獨的模塊:相位/頻率檢測器、定制濾波器、VCO 和其他元件。當然,模塊和混合設備制造商很快通過組合多個單獨的 IC 芯片和分立元件,提供完整的 PLL 作為完全表征的單元。

然而,對更高頻率的無線系統的需求,例如對軟件定義無線電、智能手機、雷達系統和許多其他應用的需求,一直激勵 IC 供應商開發能夠產生高性能單片 PLL 的工藝和設計。其中許多集成了大部分或所有功能塊(取決于頻率和所需的性能),從而減少了設計時間、風險、電路板空間和功耗。

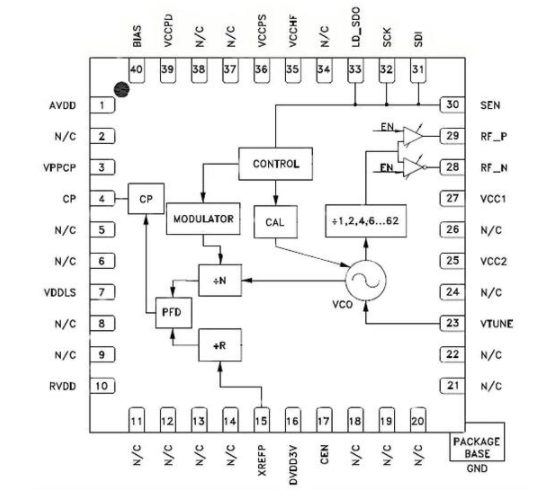

例如,Hittite(現為 Analog Devices 的一部分)的HMC830LP6GE PLL是一個小數 N PLL,工作頻率范圍為 25 MHz 至 3 GHz。它針對蜂窩/4G 基礎設施、中繼器和毫微微蜂窩以及通信測試設備,以及具有 -110 dBc/Hz 的超低帶內相位噪聲、-227 dBc/Hz 的 FOM 和低于 180 fsec 的 rms 抖動的其他應用。

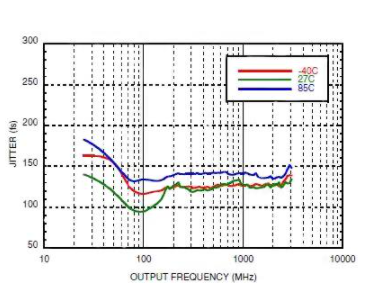

該 IC 包括一個集成 VCO(圖 2),傳統上它一直是最難集成的功能,同時仍能在高頻下實現高整體性能。與大多數 PLL 一樣,數據手冊有十多個詳細圖表,顯示了 PLL 在各種條件下的許多方面的性能。圖 3 顯示了 PLL 在不同溫度下工作范圍內的集成 rms 抖動。

圖 2:Analog Devices 的 HMC830LP6GE 代表了過去幾年的趨勢:將 VCO 與 PLL 的其余部分一起放入 IC 中,同時擴展頻率范圍且不影響品質因數。

圖 3:PLL 數據表通常有許多性能圖表,例如 HMC830LP6GE 的這張圖表,顯示了 -40?C、27?C 和 85?C 時的 rms 抖動 (fsec) 與頻率的關系;請注意在該范圍內的性能穩定性。

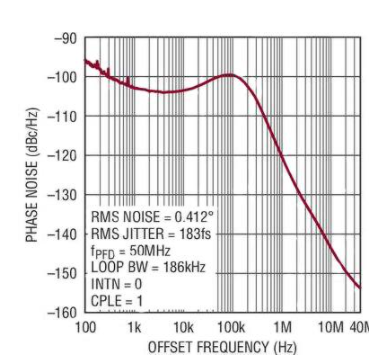

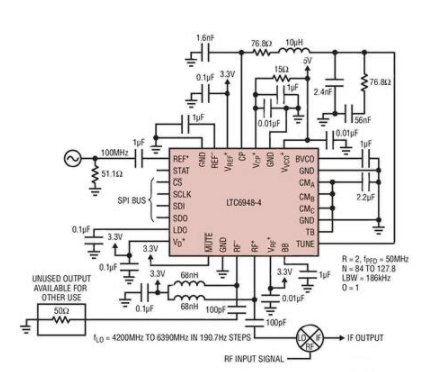

另一個具有集成 VCO 的 PLL 是凌力爾特公司的LTC6948,它是一款 370 MHz 至 6.39 GHz 小數 N 器件,還具有超低噪聲。它還包括一個參考分頻器、相位/頻率檢測器、電荷泵、分數反饋分頻器和 VCO 輸出分頻器。歸一化帶內相位噪底 FOM 為 -226 dBc/Hz,寬帶輸出相位噪底為 –157 dBc/Hz(圖 4)。

圖 4:除其他參數外,Linear Technology 的 LTC6948 數據表還包括歸一化帶內相位本底噪聲 FOM 和寬帶輸出本底相位噪聲;后者在最高頻率下從 –100 dBc/Hz 下降到 –157 dBc/Hz。

它支持高達 425 MHz 的參考輸入頻率,以實現快速頻率切換。該IC非常適合無線基站(LTE、WiMAX、W-CDMA、PCS)等應用;微波數據鏈路和軍用/安全無線電,它可以用作高速、可調諧 6.39 GHz 寬帶接收器的核心(圖 5)。

圖 5:即使是高度集成的 IC 也需要無源元件支持,正如該基于 LTC6948 的高速、可調諧 6.39 GHz 寬帶接收器的原理圖所示。

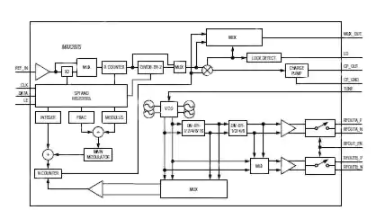

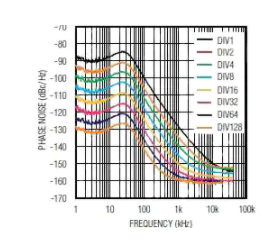

Maxim Integrated 的 MAX2870是一款 23.5 MHz 至 6 GHz PLL,帶有小數/整數 N 合成器和 VCO(圖 6)。該設備通過覆蓋 3 GHz 至 6 GHz 的多個 VCO 實現其超寬頻率,可以自動選擇或在用戶控制下(通過串行接口)選擇;用戶提供環路濾波器和參考。相位/頻率檢測器在整數 N 模式下工作至 105 MHz,在小數 N 模式下工作至 50 MHz,并接受高達 200 MHz 的參考頻率。PLL 在多個分頻器設置中顯示出出色的 6.0 GHz 相位噪聲性能(圖 7)。應用包括無線基礎設施、測試和測量、衛星通信和無線局域網。

圖 6:Maxim Integrated 的 MAX2870 通過使用多個內部 VCO 實現了 6 GHz 額定值,這些 VCO 可以自動選擇或由用戶主動選擇。

圖 7:PLL 供應商再次提供了詳細的性能規格,例如 MAX2870 在工作帶寬內的相位噪聲圖,具有不同的分頻系數。

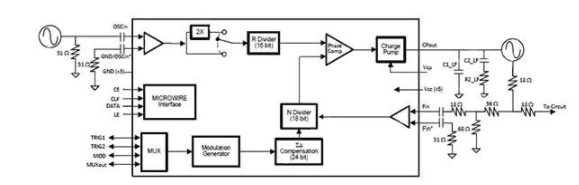

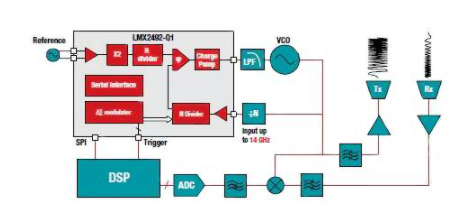

盡管Texas Instruments LMX2492小數分頻 PLL(圖 8)不包括集成 VCO,但它使用外部 VCO 可在 500 MHz 至 14 GHz 范圍內工作;其 FOM 為 -227 dBc/Hz。當與合適的環路分頻器結合使用時,它可以用作 77 GHz 汽車雷達系統的核心(圖 9);它還包括針對這一重點應用的斜坡/啁啾生成。

圖 8:Texas Instruments LMX2492 PLL 不包括 VCO,但在 -227 dBc/Hz 的 FOM 下達到 14 GHz 性能。

圖 9:LMX2492 面向 77 GHz 汽車雷達等應用,具有雷達所需的集成斜坡和啁啾功能。

由于其 200 MHz 相位檢測器響應,該 PLL 還可用于非雷達應用,例如移動無線、緊湊型射頻、雷達模塊、微波回程、示波器、頻譜分析儀、陸地移動無線電和軟件定義無線電。盡管其額定頻率很高,但該 IC 采用 3.15 至 3.45 V 電源供電,耗散電流僅為 60 mA。

除了 RF 性能之外,許多 PLL 現在還包括 SPI 或 I 2 C 串行接口,因此系統處理器可以設置和更改一些 PLL 參數,例如增益、濾波器帶寬或范圍。這使軟件能夠調整給定電路中的這些因素以滿足不斷變化的場景,或者允許在多個設計中使用相同的組件。

概括

幾十年來,PLL 一直是許多用于通信、合成、時鐘、信號生成和信號恢復應用的電子系統的關鍵部分。新 IC 正在將頻率、噪聲和抖動性能方面的性能規范推向新的水平,同時將更多功能集成到單個設備中。通過在環路設計本身內添加數字功能,或作為建立 PLL 工作點的控制功能,PLL 的多功能性和靈活性進一步增強。

參考:

Signetics NE565 數據表

Gardner, Floyd M. (2005),Phaselock 技術(第 3 版),Wiley-Interscience,ISBN 978-0-471-43063-6

Viterbi, Andrew J.,連貫通信原理,McGraw-Hill。

電子發燒友App

電子發燒友App

評論