?

? ? ?摘要

?

論述伺服驅(qū)動(dòng)控制器的實(shí)現(xiàn)方法,通過(guò)對(duì)ARM+FPGA+DSP架構(gòu)的多CPU控制器的具體分析將其原理和優(yōu)勢(shì)展現(xiàn)出來(lái);這種架構(gòu)控制器系統(tǒng)分工明確,提高了算法的實(shí)時(shí)性;提高了控制器對(duì)外接口EtherCAT的實(shí)時(shí)性;提高了系統(tǒng)的穩(wěn)定性。這種架構(gòu)方案在天津電氣科學(xué)研究院有限公司的伺服驅(qū)動(dòng)器產(chǎn)品中進(jìn)行了實(shí)驗(yàn),現(xiàn)場(chǎng)的應(yīng)用取得了良好的效果,體現(xiàn)出這種技術(shù)的現(xiàn)實(shí)意義。

?

1、引言?

伺服驅(qū)動(dòng)器是用來(lái)控制伺服電機(jī)的一種控制器,一般是通過(guò)位置、速度和力矩三種方式對(duì)電機(jī)進(jìn)行控制,實(shí)現(xiàn)高精度的系統(tǒng)定位。

?

目前,伺服控制器CPU的架構(gòu)主要有:

?

1、單CPU架構(gòu)ARM(AcornRISCMachine)控制器;

?

2、單CPU架構(gòu)DSP(DigitalSignalProcess)控制器;

?

3、ARM+FPGA+DSP架構(gòu)的多CPU控制器。

?

方法3是目前最先進(jìn)的架構(gòu),前兩種方法都有局限性。方法1和方法2這種單CPU架構(gòu)的控制器,一個(gè)CPU集算法、采集控制、通訊、顯示功能于一體,當(dāng)算法復(fù)雜度和實(shí)時(shí)性要求高時(shí)往往會(huì)顧此失彼。而方法3的架構(gòu)中各個(gè)CPU的分工明確,ARM負(fù)責(zé)通信和顯示功能,DSP負(fù)責(zé)算法運(yùn)算,F(xiàn)PGA負(fù)責(zé)采集和控制。方法3的技術(shù)瓶頸是滿足伺服控制器的實(shí)時(shí)性要求需要幾個(gè)CPU之間的高速數(shù)據(jù)通信,因此,如果能夠找到一個(gè)高速的通信方式完全可以發(fā)揮各個(gè)CPU的特性,就像一個(gè)多核CPU在工作一樣。

?

本研究基于ARM+FPGA+DSP架構(gòu),采用并口通信的方法用于幾個(gè)CPU之間的內(nèi)部高速通信;此外伺服驅(qū)動(dòng)器作為伺服系統(tǒng)的一部分還需要和主控器和編碼器進(jìn)行高速通信,來(lái)滿足整個(gè)伺服系統(tǒng)的實(shí)時(shí)性要求,本架構(gòu)采用EtherCAT和高速485接口用于控制器和其他設(shè)備進(jìn)行高速通信,描述了系統(tǒng)的原理架構(gòu)和軟件設(shè)計(jì)架構(gòu)。

?

?

2.多CPU架構(gòu)控制器原理分析?

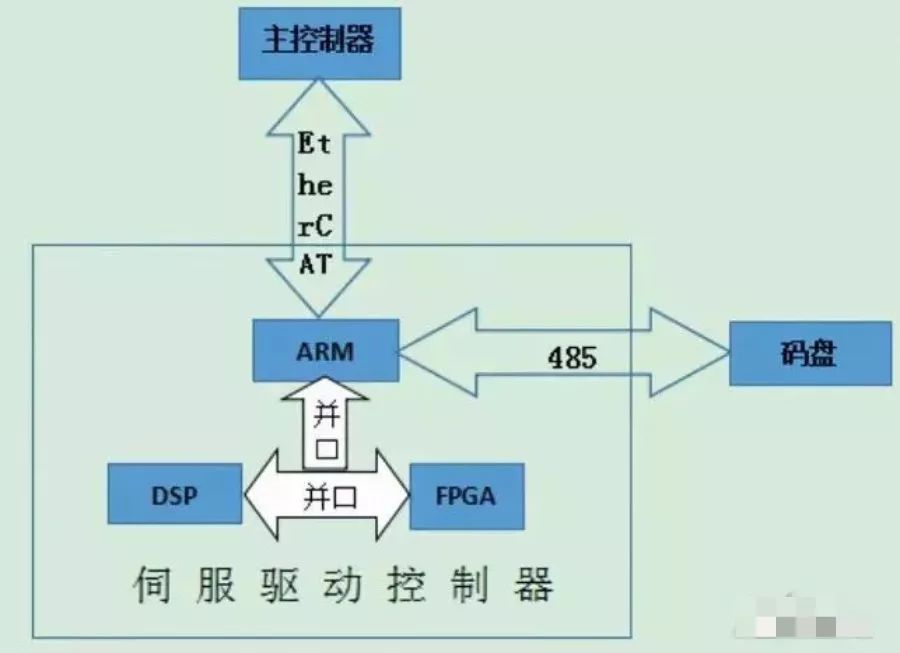

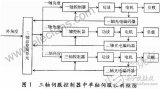

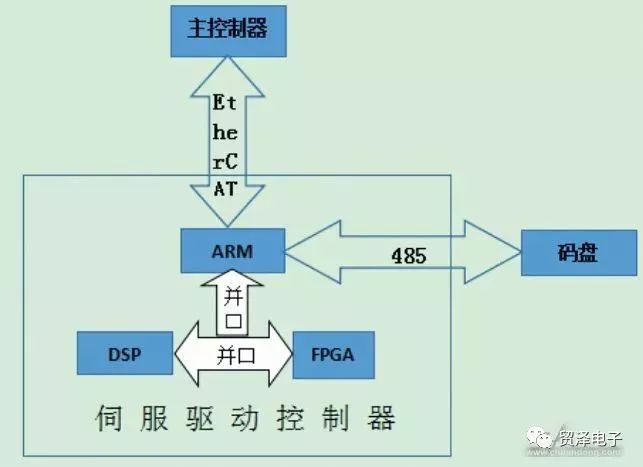

2.1 此架構(gòu)的控制器中ARM負(fù)責(zé)通信和顯示功能,DSP負(fù)責(zé)算法運(yùn)算,F(xiàn)PGA負(fù)責(zé)采集和控制,如圖1所示。FPGA采集相電壓、相電流等物理量通過(guò)并口傳給DSP;ARM通過(guò)EtherCAT接收主控制器命令,通過(guò)高速485采集碼盤的速度和位置等信息,通過(guò)并口傳給FPGA中轉(zhuǎn)下再傳到DSP;DSP中執(zhí)行伺服控制的算法,利用FPGA和ARM中采集的數(shù)據(jù)進(jìn)行計(jì)算,把計(jì)算結(jié)果再通過(guò)并口傳給FPGA和ARM,由FPGA和ARM進(jìn)行相關(guān)的控制操作。

?

圖1 ?多 CPU 架構(gòu)控制器結(jié)構(gòu)圖

?

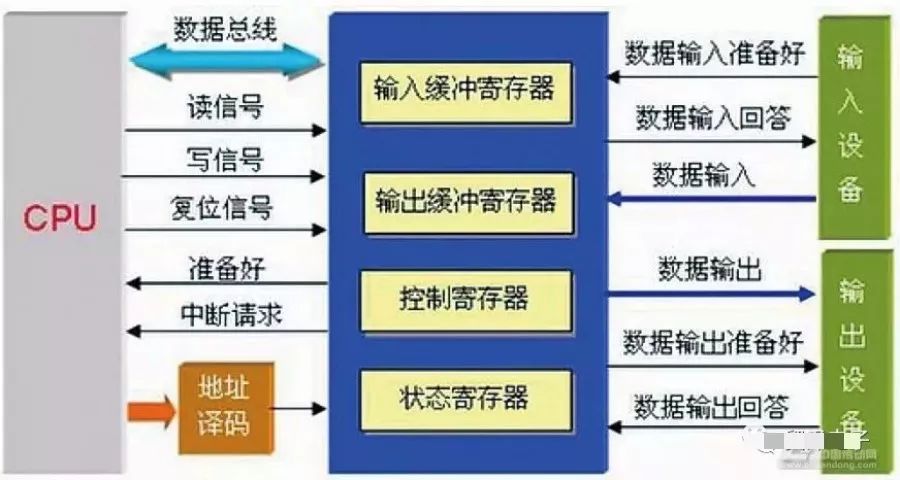

2.2 此架構(gòu)控制器中幾個(gè)CPU之間的雙口RAM通信:用雙口RAM中各位數(shù)據(jù)都是并行傳送的,它通常是以字節(jié)(8位)的整數(shù)倍為單位進(jìn)行數(shù)據(jù)傳輸,能完成數(shù)據(jù)的輸入和輸出。用雙口RAM通信的原理如2所示。用雙口RAM通信具有各數(shù)據(jù)位同時(shí)傳輸,傳輸速度快、效率高的特點(diǎn),多用在實(shí)時(shí)、快速的場(chǎng)合。

?

圖2 ?用雙口RAM通信原理圖

?

2.3 此架構(gòu)控制器的對(duì)外接口有EtherCAT和高速485。

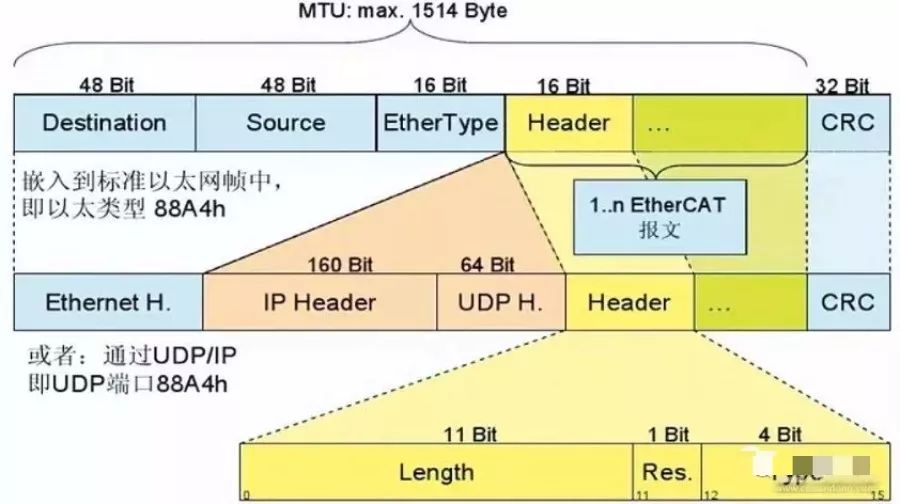

碼盤的接口一般采用485接口,所以本控制器也采用485的接口,用DMA來(lái)實(shí)現(xiàn);伺服控制器與主控制之間的接口有EtherCAT和PROFINET等協(xié)議,本控制器采用應(yīng)用比較廣的EtherCAT接口。實(shí)時(shí)以太網(wǎng)EtherCAT是由倍福開(kāi)發(fā)的一種工業(yè)以太網(wǎng)技術(shù)。它以高速率、高有效數(shù)據(jù)利用率、完全符合以太網(wǎng)標(biāo)準(zhǔn)、刷新周期短、同步性能好等優(yōu)勢(shì),在伺服通訊領(lǐng)域中得到越來(lái)越多的應(yīng)用。其原理如圖3所示。

?

圖3 ?EtherCAT報(bào)文

?

3.多CPU架構(gòu)控制器硬件設(shè)計(jì)?

3.1控制器ARM的設(shè)計(jì)

主控制器ARM通過(guò)STM32F407芯片完成上節(jié)介紹的與FPGA的并口通信、EtherCAT通信、485通信。STM32F407屬于高端的32位ARM微控制器,該系列芯片是意法半導(dǎo)體(ST)公司出品,其內(nèi)核是Cortex-M4。本次設(shè)計(jì)充分利用其資源,實(shí)現(xiàn)了并口通信、therCAT通信、485通信。

?

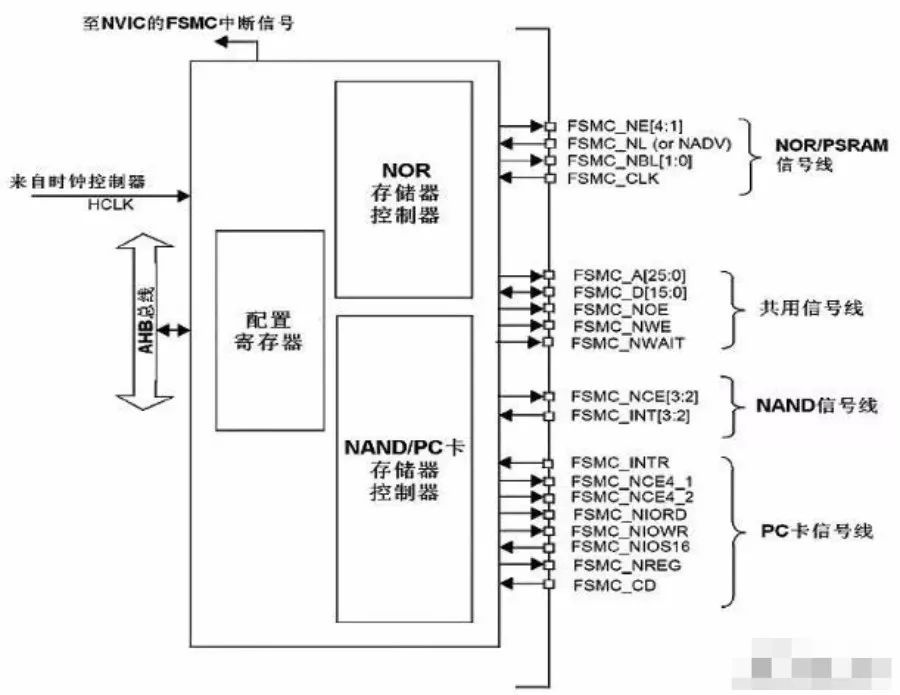

圖4 ?FSMC框圖

?

并口通信:STM32F407具有FSMC功能,靈活的靜態(tài)存儲(chǔ)器控制器(FSMC)是內(nèi)置大容量的外部存儲(chǔ)器控制器,使用這個(gè)控制器,STM32可以與FPGA或者存儲(chǔ)器進(jìn)行并口通信。FSMC產(chǎn)生所有驅(qū)動(dòng)這些存儲(chǔ)器(把FPGA當(dāng)做存儲(chǔ)器來(lái)操作)的信號(hào)時(shí)序:16個(gè)數(shù)據(jù)線和16個(gè)地址線,原理如圖4所示。

?

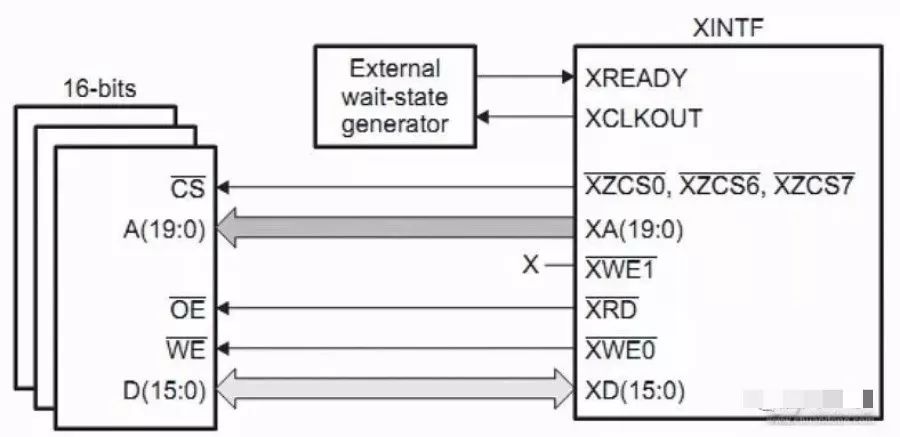

圖5 ?數(shù)據(jù)總線XINTF連接框圖

?

EtherCAT通信和485通信:EtherCAT通信通過(guò)芯片ET1100來(lái)實(shí)現(xiàn),ET1100是一款強(qiáng)大的EtherCAT從站控制器ESC專用芯片,ET1100與ARM的接口采用SPI的方式;485通信速度為2.5Mbps,采用DMA的方式來(lái)實(shí)現(xiàn),DMA的具體實(shí)現(xiàn)方法在下章軟件設(shè)計(jì)中詳述。

?

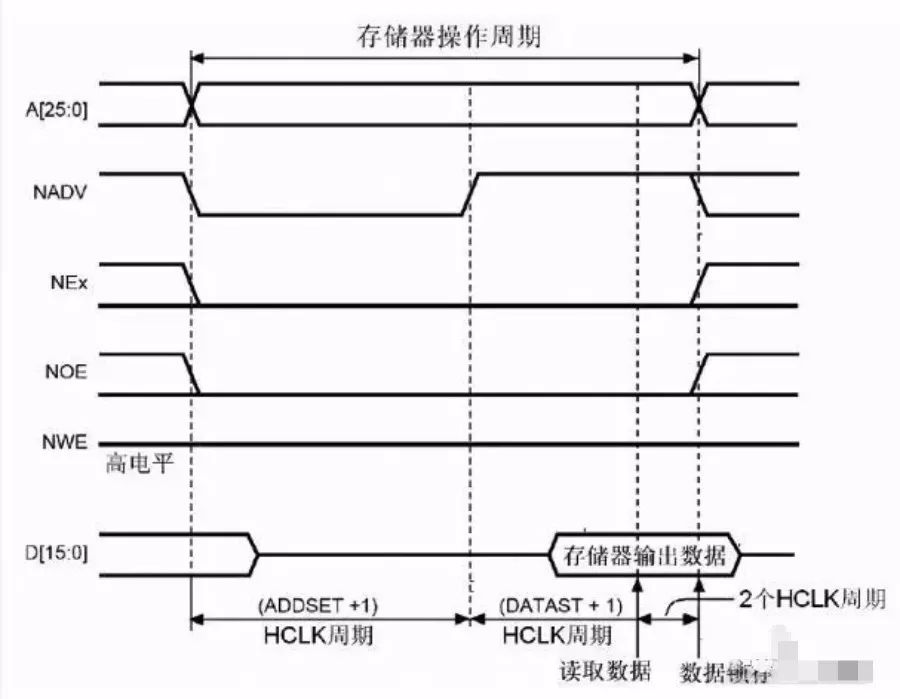

圖6讀操作時(shí)序

?

3.2控制器FPGA和DSP的并口通信設(shè)計(jì)

?

FPGA采用Altera的CycloneIV系列FPGA,具有低成本、低功耗的特點(diǎn),高達(dá)532個(gè)用戶I/O,支持高達(dá)200MHz的DDR2SDRAM接口;DSP采用TMS320C28346,通過(guò)XINTF連接FPGA,實(shí)現(xiàn)雙向并口通信。DSP的輸入和輸出采用中斷控制,當(dāng)FPGA準(zhǔn)備好數(shù)據(jù)后,向DSP發(fā)送中斷,DSP響應(yīng)中斷后讀取相應(yīng)地址的數(shù)據(jù)并向另外一段地址寫入數(shù)據(jù),F(xiàn)PGA等待60μs開(kāi)始讀數(shù)據(jù)。這樣就能夠完成兩個(gè)芯片的并行通信。TMS320C28346型DSP芯片有16位XINTF數(shù)據(jù)總線,做為系統(tǒng)外部接口,它可以與各種外部存儲(chǔ)器或者CPU實(shí)現(xiàn)無(wú)縫連接,如圖5所示。在此系統(tǒng)中,將它與FPGA的16個(gè)用戶可定義I/O管腳相連,用于實(shí)現(xiàn)16位并行數(shù)據(jù)的通信。TMS320C28346芯片可編程通用輸入/輸出引腳,任選一個(gè)和FPGA的用戶I/O管腳相連,作為DSP的讀寫中斷。

?

4.多CPU架構(gòu)控制器軟件設(shè)計(jì)?

4.1控制器ARM的軟件設(shè)計(jì)

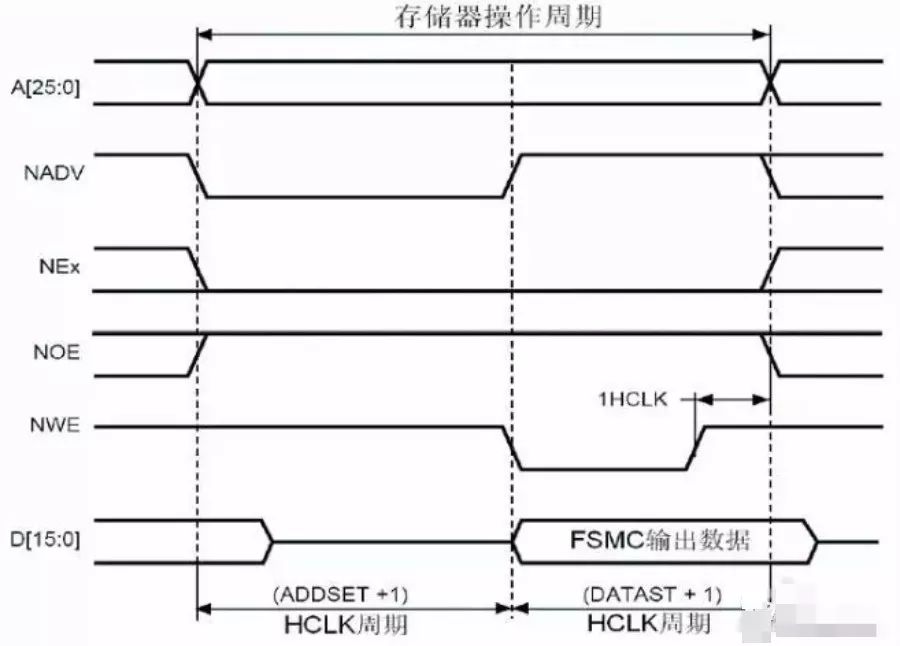

控制器中ARM與FPGA的并口通信用FSMC來(lái)實(shí)現(xiàn),采用非總線復(fù)用的異步NOR閃存的方式來(lái)驅(qū)動(dòng),讀時(shí)序如圖6所示,寫時(shí)序如圖7所示。

?

圖7??寫操作時(shí)序

?

并口通信的地址選擇使用了FSMC的BANK1的子板塊2,具體程序代碼如下:

??

p.FSMC_AccessMode=FSMC_AccessMode_A;

FSMC_NORSRAMInitStructure.FSMC_Bank=FSMC_Bank1_NORSRAM2;

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM2,ENABLE);

?

ARM與FPGA通信觸發(fā)由外部中斷來(lái)觸發(fā),當(dāng)FPGA準(zhǔn)備好數(shù)據(jù)后給ARM一個(gè)中斷,中斷周期為120μs,其中前60μs用于ARM從并口地址讀取數(shù)據(jù)并且把要傳給FPGA的數(shù)據(jù)寫入相應(yīng)地址,后60μs用于FPGA從并口地址讀取數(shù)據(jù),程序代碼如下:

?

pBuf=(s16*)EXT_SRAM_ADDR+31;

for(i=31;i<91;i++)//read

{FPGA_TO_ARM[i]=*pBuf++;}

pBuf=(s16*)EXT_SRAM_ADDR+41;

for(i=41;i<61;i++)//write

{*pBuf++=(FPGA_TO_ARM[i]+1);}

?

ARM與碼盤通信通過(guò)485來(lái)實(shí)現(xiàn),通信速度為2.5Mbps,由于速度快采用一般的中斷方式很難滿足需求,本系統(tǒng)采用DMA來(lái)實(shí)現(xiàn),程序代碼如下:

?

DMA_InitStructure.DMA_PeripheralBaseAddr=(uint32_t)(&(USART3->DR));//串口3接收DMA

?

DMA_InitStructure.DMA_Memory0BaseAddr=(uint32_t)UART3_DMA_RxBuffer;

?

DMA_InitStructure.DMA_PeripheralBaseAddr=(uint32_t)(&(USART3->DR));//串口3發(fā)送DMA

?

DMA_InitStructure.DMA_Memory0BaseAddr=(uint32_t)UART3_DMA_TxBuffer;

?

4.2控制器FPGA的軟件設(shè)計(jì)

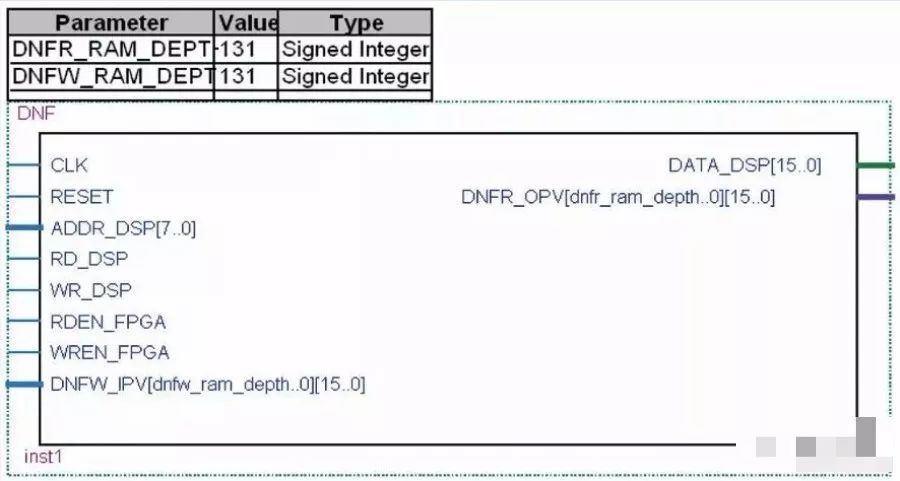

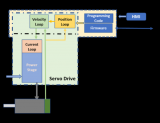

FPGA與DSP并行總線通訊模塊用于FPGA與DSP之間的并行總線數(shù)據(jù)交換,其中包含兩段獨(dú)立的地址空間,一個(gè)空間用于DSP讀FPGA內(nèi)部數(shù)據(jù)通道,另一個(gè)空間用于DSP向FPGA寫數(shù)據(jù)通道。程序使用ALTERA提供的雙口RAM的IP核。程序模塊圖如圖8所示。

?

圖8 ?FPGA程序模塊圖

?

FPGA與DSP并行總線通訊模塊主時(shí)鐘CLK的頻率應(yīng)是DSP總線讀寫頻率的4倍以上,一般選取120M,這個(gè)時(shí)鐘由FPGA內(nèi)部的PLL鎖相環(huán)生成。由于DSP的地址總線一般為16位以上,ADDR_DSP連接DSP地址總線的低位。RD_DSP連接DSP讀使能,WR_DSP連接DSP寫使能,如果有片選信號(hào),DSP讀寫使能信號(hào)需要與片選信號(hào)取或后再與WR_DSP和RD_DSP連接。

?

4.3控制器DSP的軟件設(shè)計(jì)

DSP28346芯片通過(guò)外部接口(XINTF)來(lái)讀寫外擴(kuò)存儲(chǔ)單元,本系統(tǒng)中即為FPGA的雙口RAM空間。DSP28346的XINTF是一個(gè)非復(fù)用的異步總線。在配置XINTF時(shí),應(yīng)該檢測(cè)內(nèi)部XTIMCLK所需要的與SYSCLKOUT有關(guān)的比例。通過(guò)寫XINTFCNF2寄存器的XTIMCLK位,可以將TIMCLK配置成與SYSCLKOUT相等或者等于SYSCLKOUT/2。XINTF的所有訪問(wèn)從XCLKOUT的上升沿開(kāi)始,而外部邏輯受到XCLKOUT時(shí)鐘的控制。通過(guò)寫XINTFCNF2寄存器的CLKMODE位,可將XCLKOUT配置成與內(nèi)部XINTF時(shí)鐘XTIMCLK成比例的頻率。程序代碼如下:

?

XintfRegs.XINTCNF2.bit.XTIMCLK=0;

XintfRegs.XINTCNF2.bit.WRBUFF=3;

XintfRegs.XINTCNF2.bit.CLKOFF=0;

XintfRegs.XINTCNF2.bit.CLKMODE=0;

XintfRegs.XINTCNF2.bit.BY4CLKMODE=1;

XintfRegs.XTIMING6.bit.XWRLEAD=3;

XintfRegs.XTIMING6.bit.XWRACTIVE=5;

XintfRegs.XTIMING6.bit.XWRTRAIL=2;

XintfRegs.XTIMING6.bit.XRDLEAD=3;

XintfRegs.XTIMING6.bit.XRDACTIVE=5;

XintfRegs.XTIMING6.bit.XRDTRAIL=2;

XintfRegs.XTIMING6.bit.X2TIMING=0;

XintfRegs.XTIMING6.bit.USEREADY=1;

XintfRegs.XTIMING6.bit.READYMODE=1;

?

5.結(jié)論?

市面上的伺服驅(qū)動(dòng)器CPU的架構(gòu)主要有單ARM控制器和單DSP控制器。單ARM控制器方案在通信和控制方面存在優(yōu)勢(shì),但是復(fù)雜算法在實(shí)現(xiàn)的時(shí)候往往會(huì)因?yàn)檫\(yùn)算耗時(shí)而降低整個(gè)系統(tǒng)實(shí)時(shí)性;單DSP控制器方案中在算法中存下優(yōu)勢(shì),但是在對(duì)外通信和控制方面往往會(huì)實(shí)現(xiàn)起來(lái)比較復(fù)雜。采用ARM+FPGA+DSP架構(gòu)的多CPU控制器方案完全解決了上述兩種方法的弊端,充分發(fā)揮了各個(gè)CPU的優(yōu)勢(shì)。本文論述的架構(gòu)在本公司的伺服驅(qū)動(dòng)器產(chǎn)品中進(jìn)行試驗(yàn)和應(yīng)用,證明了“ARM+FPGA+DSP架構(gòu)的多CPU控制器架構(gòu)”的可行性和技術(shù)優(yōu)勢(shì)。

?

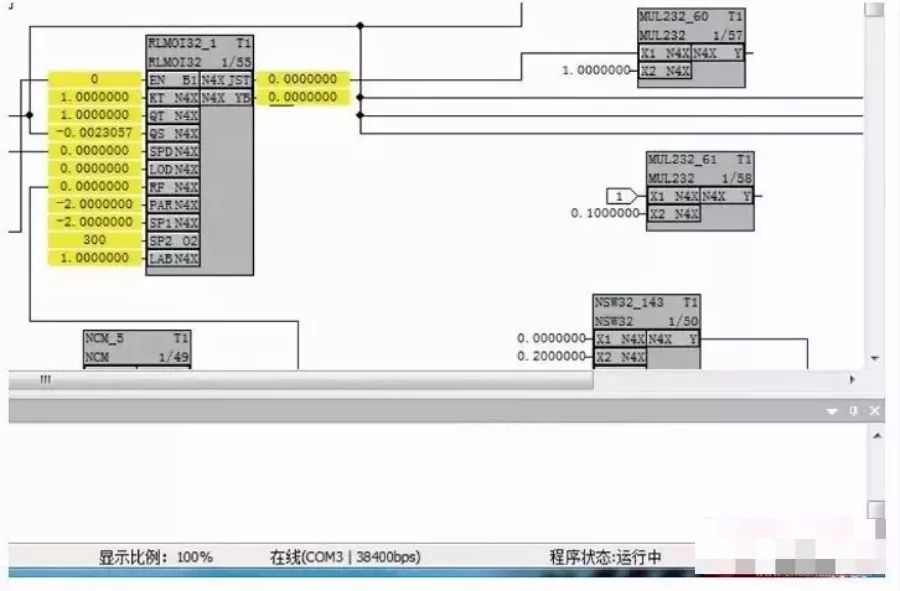

圖9 ?CPU算法在線仿真圖

?

如圖9中的紅色標(biāo)記框圖所示,整個(gè)伺服驅(qū)動(dòng)器系統(tǒng)的CPU使用率在75.22%(A:空跑時(shí)優(yōu)先級(jí)最低的計(jì)數(shù)器個(gè)數(shù);B滿算法運(yùn)行時(shí)優(yōu)先級(jí)最低計(jì)數(shù)器的個(gè)數(shù);CPU使用率=(A-B)/A*100),此CPU架構(gòu)達(dá)到了控制CPU使用率和提高系統(tǒng)效率的目標(biāo)。

?

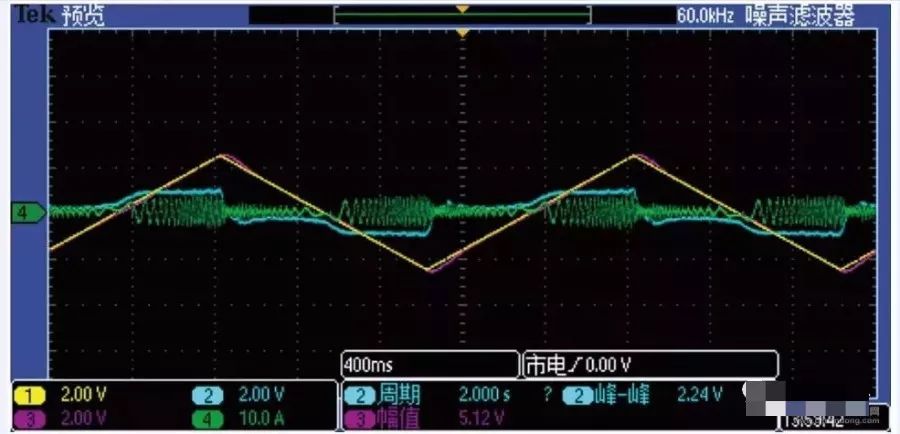

圖10

?

如圖10中的離線慣量辨識(shí)2s周期(0.5轉(zhuǎn)速)PI不變時(shí)跟隨情況,通道1是轉(zhuǎn)速給定,通道2是電磁轉(zhuǎn)矩,通道3是實(shí)際轉(zhuǎn)速,通道4是實(shí)際A相電流。速度采集首先通過(guò)ARM的高速485采集碼盤數(shù)據(jù),并通過(guò)并口傳給DSP和FPGA,經(jīng)過(guò)算法處理再把數(shù)據(jù)下發(fā)給碼盤,整個(gè)閉環(huán)過(guò)程通過(guò)并口傳輸,滿足了伺服驅(qū)動(dòng)器的算法實(shí)時(shí)性要求,此CPU架構(gòu)達(dá)到了提高整個(gè)系統(tǒng)實(shí)時(shí)性的目標(biāo)。

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論