引言

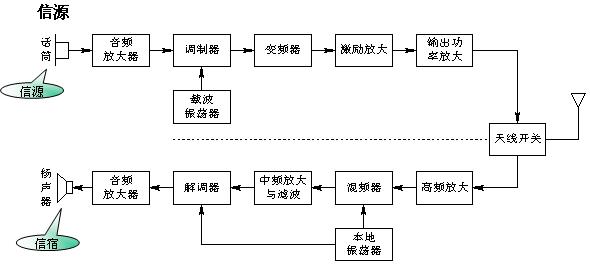

隨著頻率資源的日趨緊張,短距離無線通信按窄帶化趨勢發展。無線數傳模塊一般由微處理器和收發芯片組成,本文所設計的窄帶數傳模塊的微處理器采用了STM32F103ZE芯片,收發芯片選用了TI公司新推出的CC1120,CC1120通過SPI串行總線協議與MCU相連接。同時,采用了可移植、可植入ROM、可裁剪、搶占式的實時多任務操作系統μC/OS—III作為軟件平臺。

1 系統硬件電路

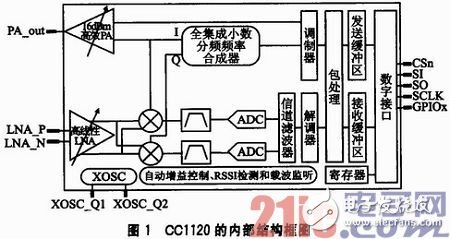

1.1 CC1120的內部結構

CC1120是TI公司專為經濟高效的無線系統在低功耗和低電壓操作下,實現數據傳輸而設計的一款完全集成的單芯片無線收發器。該芯片主要應用于ISM(工業、科學和醫療)以及SRD(短程設備)頻帶。CC1120的主要特性有:體積小,超低功耗,可配置數據速率(1.2~200kbps),可編程控制輸出功率(步長為0.5 dB,最高功率16 dBm),接收機靈敏度高(1.2 kbps數據速率下為123 dBm),還支持2FSK、2GFSK、4FSK、4GFSK、MSK、ASK、OOK及模擬FM多種調制方式等。

CC1120的內部結構框圖如圖1所示。CC1120具有一個低功耗IF接收機,低噪聲放大器(LNA)將接收到的RF、信號放大,并在求積分(I和Q)過程中被降壓轉換至中頻(IF)。在IF下,I/Q信號被ADC數字化。自動增益控制(AGC)、精確信道濾波和調制解調位/數據包同步均以數字方式完成。CC1120的發射器部分基于RF頻率直接合成,頻率合成器包括一個完全片上LC VCO和一個90°相位轉換器,用來在接收模式下向降壓轉換混頻器生成I和Q本振信號。一個4線SPI串行接口用于配置數據和緩沖區存取。數字基帶包括了對信道配置、數據包處理以及數據緩沖的支持。

1.2 CC1120的配置特性

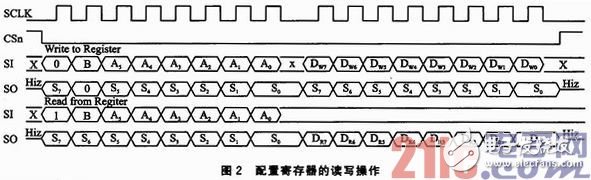

配置寄存器的讀、寫操作時序如圖2所示。通過一個4線串行SPI兼容接口(SI、SO、SCLK和CSn)可對CC1120進行配置,該接口還可用于讀取和寫入緩沖數據。SPI接口上的所有數據傳輸均以最高位開始。

SPI接口上的所有事務均以一個報頭字節作為開始,該字節包含一個R/W位、一個突發存取位(B)以及一個6位地址(A5~A0),報頭字節幀格式如圖3所示。在SPI總線上傳輸數據期間,CSn引腳必須保持低電平,否則傳輸就會被取消。拉低CSn電平時,在開始傳輸該報頭字節以前,MCU必須等待,直到SO引腳變為低電平為止。這表明,芯片正在運行。除非芯片處在SLEEP或XOFF狀態,否則SO引腳總會在CSn變為低電平以后立即變為低電平。

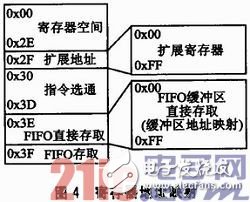

CC1120的寄存器空間主要作為CC1120的頻率、數據速率、中頻等大部分參數的配置。而擴展寄存器大部分為芯片配置輔助測試寄存器(只讀),少部分為配置寄存器(可讀寫)。指令選通用于芯片狀態切換和沖刷RX/TXFIFO。128字節TX FIFO和128字節RX FIFO均通過0x3F地址進行存取。當R/W位為0時,則TX FIFO被存取;當R/W位為1時,則RX FIFO被存取。其中,TXFIFO為只寫,而RX FIFO為只讀。寄存器地址映射如圖4所示。

1.3 硬件連接關系

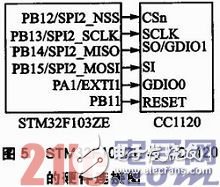

窄帶無線數據傳輸系統的STM32F103ZE與無線收發芯片的硬件連接關系如圖5所示。左側為STM32F103ZE,它是一個32位、基于ARM Cort ex—M3內核的無線收發芯片。除了正常工作模式外,還支持睡眠、待機、停機工作模式,當所有外設都處于工作模式時消耗36 mA,待機時下降到2μA。CC1120內部集成的SPI接口的傳輸速率最高可達到18 Mbps。

右側為無線收發芯片CC1120。CC1120的外部控制引腳主要有復位接口、SPI串行接口以及4個通用輸出引腳GPIO0~GPIO3。其中,4個通用輸出引腳在實際應用中,可以通過配置寄存器使它們為上層實時提供同步字或數據包收發狀態等應用。在硬件平臺上,CC1120的SPI串行接口(CSn、SCLK、SI、SO)分別連接到STM32F103ZE相應的4個SPI串行通信弓I腳(即SPI2_NSS、SPI2_SCLK、SPI2_MOSI、SPI2_ISO上)。通過這4根線,TM32F103ZE可以對CC1120進行參數配置、芯片狀態切換以及RX/TX FIFO的讀寫。由于CC1120只有SPI從模式,因此TM32F103ZE采用SPI主模式。另外,本方案還采用了1個通用數字輸出引腳GPIO0,用來實現數據包分組發送指示。同時,TM32F103ZE可以通過控制RESET引腳,復位無線收發芯片。

通信方式為SPI串行通信時,時鐘源由STM32F103ZE提供,通過配置處理器寄存器,SPI的SCLK時鐘頻率為4.5 MHz。通過TM32F103ZE內部的8位移位寄存器,實現CC1120與STM32F103ZE的串行數據交換。CSn引腳主要用來控制數據通信的同步性,通信期間要始終保證CSn引腳的電平為低。但是,需要注意的是CC1120的CSn引腳的時序并未完全遵照SPI時序規范,因此,STM32F103ZE的SPI2_NSS引腳需要設置成普通GPIO接口模式,并采用軟件控制方式。

2 軟件平臺

μC/OS—III實現了一個基于優先級調度的搶占式內核,并在這個內核之上提供了最基本的系統服務,例如信號量、郵箱、消息隊列、內存管理、中斷管理等,但它并不提供設備管理和文件系統管理。

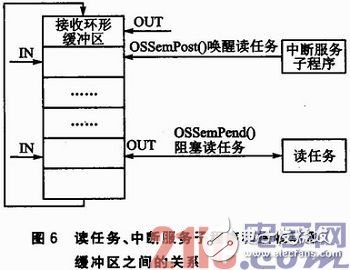

信號量用于控制共享資源的訪問,可用于中斷服務子程序與任務間、任務與任務間的同步。本設計中采用信號量機制來管理兩個共享資源,發送緩沖區和接收緩沖區。讀任務、中斷服務子程序和接收環形緩沖區之間的關系如圖6所示。圖中的共享資源為接收環形緩沖區,IN和OUT分別為入隊和出隊指針。當IN等于OUT時,則接收環形緩沖區為空,調用OSSemPend()阻塞讀任務;當IN不等于OUT時,如果讀任務被阻塞,則在中斷服務子程序中調用OSSemPost()喚醒讀任務。

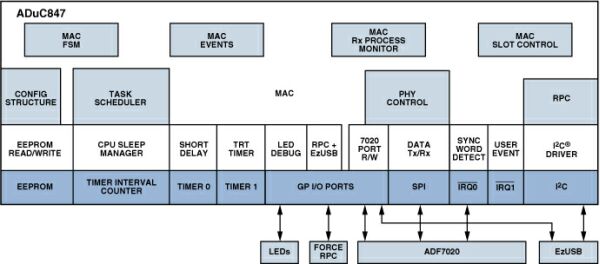

3 CC1120驅動實現

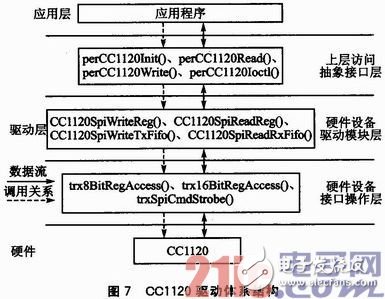

本文參考了國內研究者提出的μC/OS下通用驅動框架模型,將CC1120驅動架構模型劃分成上層訪問抽象接口層、硬件設備驅動模塊層和硬件設備接口操作層。其中,上層訪問抽象接口層通過對硬件平臺的抽象,可以在系統開發中向上層應用屏蔽硬件特征,從而實現軟/硬件的分離;硬件設備驅動模塊層是整個驅動框架的中間封裝層,通過該層的封裝,對上一層屏蔽了SPI硬件接口;而硬件設備接口操作層是實現對底層硬件SPI串行接口的功能操作,通過調用該層接口,可以實現CC1120提供的全部功能。

3.1 驅動體系結構

CC1120的驅動體系結構如圖7所示。上層訪問抽象接口層是驅動體系中的最高層,該模塊主要實現了數據包發送與接收功能,并對無線收發芯片的狀態進行控制和獲取RSSI值。其中,perCC1120Init()接口主要完成CC1120的初始化、啟動并配置芯片等功能;perCC1120Read()實現數據包的接收,以及對讀緩沖區的管理;perCC1120Wrire()實現數據包的發送,以及對寫緩沖區的管理;perCC1120Ioctl()實現了CC11 20的各個工作狀態的切換(包括休眠和喚醒)和獲取RSSI值。

硬件設備驅動模塊層實現對上層訪問抽象接口層操作,屏蔽了硬件SPI接口,提供了對CC1120的寄存器和FIFO的讀寫操作。其中,CC1120 SpiWriteReg()和CC1120SpiReadReg()分別提供了寄存器的寫和讀操作功能,屏蔽了8位和16位寄存器的區別;CC1120SpiWriteTxFifo()和CC1 120SpiReadRxFifo()提供了FIFO的連續寫和讀操作功能。

硬件設備接口操作層是對CC1120的硬件SPI接口的直接操作和軟件表達,該層為整個驅動模塊提供了SPI同步串行通信機制。其中,trx8 BitRegAccess()實現了8位寄存器的存取功能;trx16BitRegAccess()實現了16位寄存器的存取功能;trxSpiCmdStrobe()實現了芯片的指令選通功能,用于芯片工作狀態切換。

本文結合CC1120驅動體系結構,簡要介紹其主要功能,即數據包的收發。

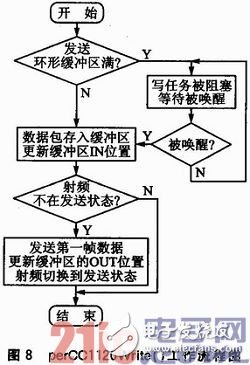

應用層發送數據包之前,先調用perCC1120Ioctl()獲取信道的RSSI值,當RSSI值低于信道忙碌的門限值時,則調用perCC1120Write()將需要發送的數據發送出去。perCC1120Write()的工作流程圖如圖8所示。本文使用了CC1120的通用GPIO0引腳,通過適當配置,該引腳電平會在發送或者接收完一個數據包時產生一個下降沿跳變。當上一包數據包發送完畢之后,GPIO0觸發中斷,STM32F103ZE進入中斷處理程序,將會發送寫緩沖區中的下一包數據包,直至發送緩沖區為空,再把CC1120置于空閑或休眠狀態。

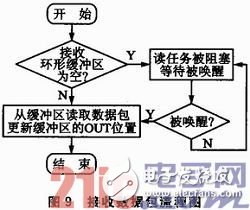

當上層不處于發送狀態時,CC1120都將置于接收狀態或增強型無線電喚醒狀態,當接收到一個數據包時,GPIO0引腳產生一個下降沿中斷,STM32F103ZE進入中斷處理程序,調用CC1120SpiReadRxFifo(),從接收緩沖RXFIFO中讀取數據包,并將其放入接收環形緩沖區中。如果接收環形緩沖區滿時,將放棄當前接收到的數據包。上層通過調用perCC1120Read()接口讀取接收到的數據包,當接收緩沖區為空時,將阻塞上層的讀取進程。perCC1120Read()的工作流程圖如圖9所示。

3.2 CC1120的配置要點

(1)寄存器配置軟件

針對CC1120的寄存器配置,TI公司提供了SmartRFStudio 7軟件。通過這個軟件可以對CC1120進行配置,以獲得最佳寄存器設置以及性能和功能評估。配置軟件根據用戶輸入的發射頻率、晶振頻率、符號速率等參數,生成相應的寄存器配置信息。

(2)數據包處理的硬件支持

CC1120內部支持的數據包處理方式有前導碼、同步字、地址過濾、CRC、數據白化、狀態字節、字節倒置等,同時,數據包長度類型支持固定長、可變長、無限長3種模式,可以通過手動配置PKT_CFG0~PKT_CFG2來實現。

(3)增強型無線電喚醒

在程序的實現過程中,當CC1120長時間沒有接收到數據時,則開啟增強型無線電喚醒功能(寄存器WOR_CFG0.RC_PD=0),并發送SWOR指令選通命令,將芯片工作狀態切換到睡眠狀態。CC1120將在MCU不干涉的前提下,周期性地從睡眠狀態中喚醒并監聽數據包的到來,從而降低系統的整體功耗。

(4)接收的信號強度指示

CC1120在接收狀態下,能連續地從RSSI狀態寄存器(RSSI0、RSSI1)中讀取到RSSI值,直到檢測到一個有效的同步字,其后RSSI讀取值將被凍結。通過設置寄存器AGC_CFG1.AGC_SYNC_BEHAVIOR,可以解除RSSI值被凍結的狀態。

(5)通用數字輸出引腳(GPIO0~GPIO3)

在實際應用中,可以通過寄存器(IOCFG0~IOCFG3)配置,為上層實時提供信道或數據包狀態等信息。本設計將寄存器IOCFG0的值設置為0x06,即利用了GPIO0引腳的電平跳變特點。當CC1120發送完或接收到一包數據包,觸發MCU端口產生中斷,并在中斷服務程序中進行寫入或讀取緩沖區TX/RX FIFO等操作,使STM32F103ZE有更多時間處理其他事務或處于休眠狀態,達到降低整個系統功耗的目的。

結語

基于μC/OS—III和CC1120的短距離窄帶無線數傳系統方案,可以實現低功耗、近距離、可靠的無線數據傳輸,具有成本低、可擴展性強、操作靈活簡單的特點。通過對CC1120和STM32F103ZE進行適當的配置,硬件能在無數據收發的狀態下,自動進入低功耗的睡眠或待機狀態,可以大大降低硬件系統的整體功耗。大量測試結果表明,該窄帶無線數據傳輸系統數據收發正常,整個系統運行穩定,具備RSSI檢測、休眠喚醒等相關功能。

電子發燒友App

電子發燒友App

評論