本文通過對一種控制芯片的測試,證明通過采用插入掃描鏈和自動測試向量生成(ATPG)技術,可有效地簡化電路的測試,提高芯片的測試覆蓋率,大大減少測試向量的數量,縮短測試時間,從而有效地降低芯片的測試成本。

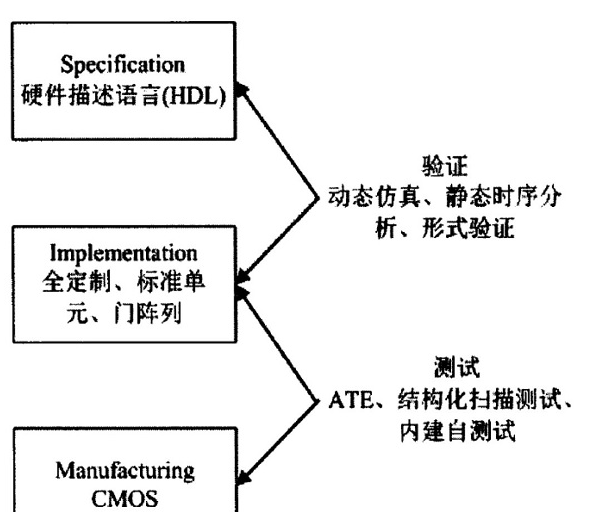

基于掃描的DFT方法掃描設計的基本原理

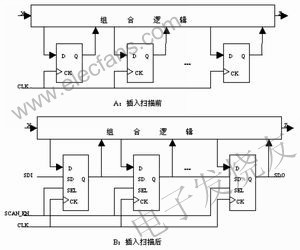

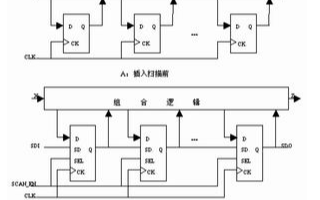

時序電路中時序元件的輸出不僅由輸入信號決定,還與其原始狀態有關,因此,對它的故障檢測比組合電路要困難的多。掃描設計就是將時序電路轉化為組合電路,然后使用已經很成熟的組合電路測試生成系統,來完成測試設計。

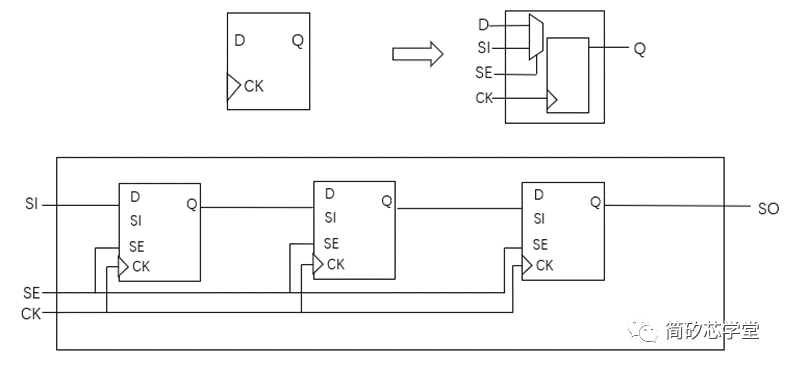

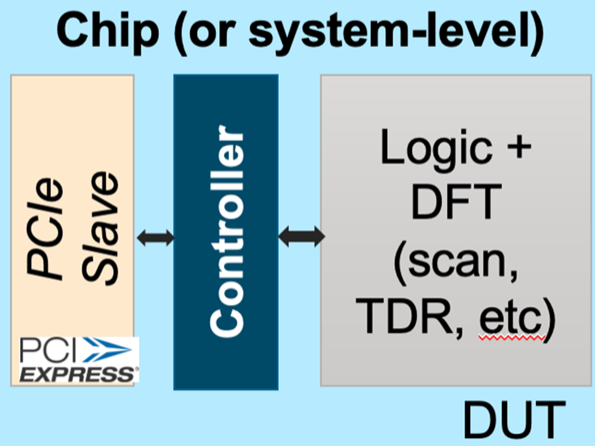

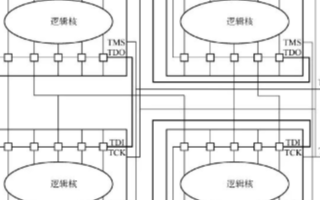

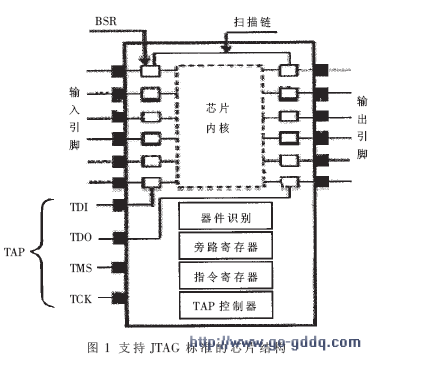

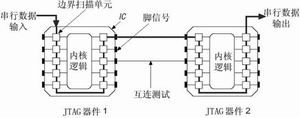

掃描設計可將電路中的時序元件替換為相應的可掃描的時序元件(也叫掃描觸發器),然后把它們串起來,形成一個從輸入到輸出的測試串行移位寄存器(即掃描鏈),以實現對時序元件和組合邏輯的測試。

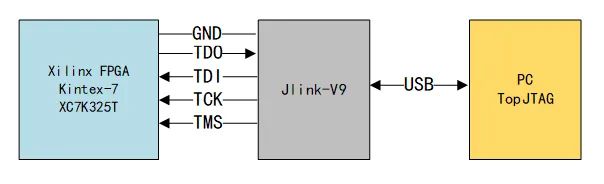

如圖1所示,采用掃描設計技術后,通過掃描輸入端,可以把需要的數據串行地移位到掃描鏈的相應單元中,以串行地控制各個單元;同時,也可以通過掃描輸出端串行地觀測它們。這樣就消除了時序電路的不可控制性和不可觀測性,提高了電路的可測性。需要注意的是,可測性設計的前提是不能改變原始設計的功能。

掃描設計的基本流程

掃描設計測試的實現過程是:

1) 讀入電路網表文件,并實施設計規則檢查(DRC),確保設計符合掃描測試的設計規則;

2) 將電路中原有的觸發器或者鎖存器置換為特定類型的掃描觸發器或者鎖存器(如多路選擇D觸發器),并且將這些掃描單元鏈接成一個或多個掃描鏈,這一過程稱之為測試綜合;

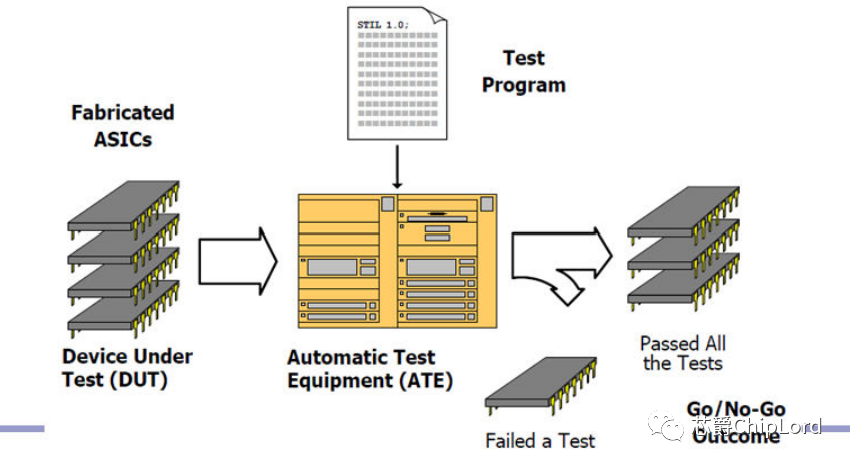

3) 測試向量自動生成(ATPG)工具根據插入的掃描電路以及形成的掃描鏈自動產生測試向量;

4) 故障仿真器(Fault Simulator)對這些測試向量實施評估,并確定故障覆蓋率情況。

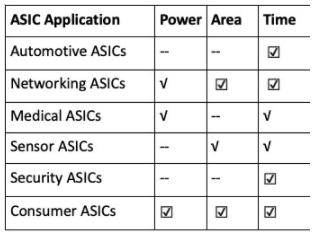

DFT對芯片的影響

DFT是為了簡化芯片測試而采用的技術,對芯片的功能沒有影響,但不可避免地會增加邏輯,對芯片產生一些影響。

對芯片面積的影響

DFT以增加邏輯來達到簡化測試的目的,增加的邏輯勢必會增加芯片面積。一般,采用DFT會增加10%"15%的芯片面積。

對芯片性能的影響

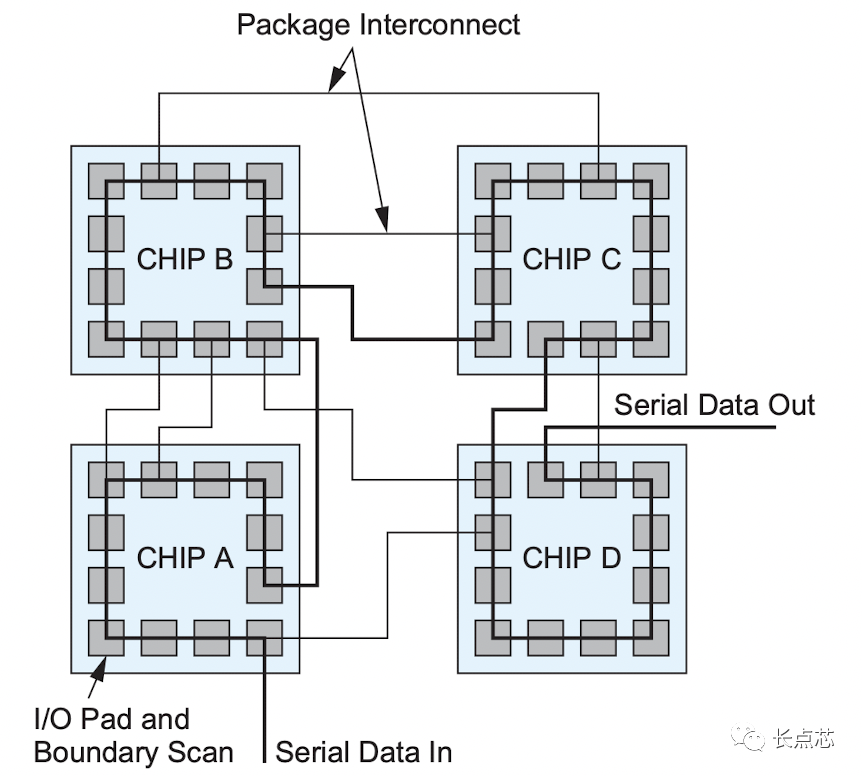

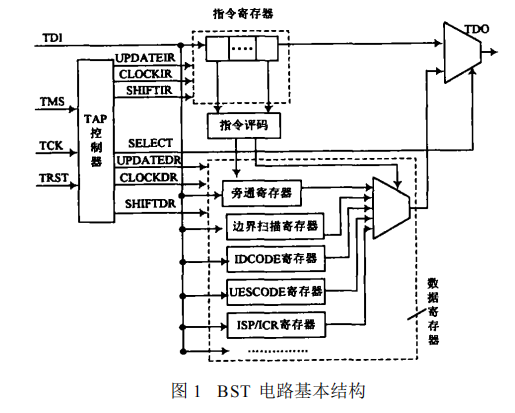

邊界掃描要在每個輸入輸出端口處插入邊界掃描寄存器(BSC),因此,在正常工作時,信號要多通過一個多路開關,這就帶來了額外延時,降低了芯片原本可以達到的工作頻率。

對芯片故障覆蓋率的影響

芯片測試的要求就是要盡可能地將有故障的芯片檢測出來,從而降低芯片的逃逸率(Escape)。DFT的目的在于方便測試,提高故障覆蓋率,從而降低逃逸率。故障覆蓋率并非越高越好,因為提高故障覆蓋率可能會大大增加測試成本,所以應該在測試成本與取得的逃逸率之間進行折衷。

對芯片上市時間的影響

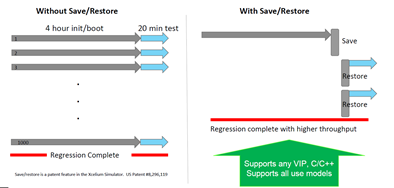

產品的上市時間對于企業至關重要,與芯片測試相關的影響上市時間的因素有:測試電路的設計時間、測試準備(ATPG,Test仿真)及工藝測試時間。

在上述因素中,測試電路設計時間的增加無疑會延遲芯片的上市時間,但DFT設計軟件的不斷完善能夠縮短該設計時間。測試準備包括測試向量的編寫和仿真,一個高效的測試向量集可以大大縮短工藝測試時間。若不采用DFT技術,就要付出相當長的時間來編寫測試向量集,而且,隨著VLSI的快速發展,由人工提供測試向量將越來越不現實。如果采用DFT技術,就可以縮短測試準備和工藝測試時間。因此,從總體上看,DFT是可以縮短芯片上市時間的。

兩種測試方法的比較

本文針對某一種控制芯片,對采用DFT和不采用DFT的兩種測試方法進行了比較,以說明DFT技術對芯片故障覆蓋率及測試向量集的影響。對芯片進行“結構測試”時的測試激勵來源有兩種:一種是直接根據芯片的功能測試激勵得到芯片的生產測試向量;另一種就是采用DFT技術,通過對設計插入掃描鏈,采用ATPG的方法得到測試向量。

不采用DFT技術的芯片測試測試工具與測試流程

Cadence公司的Verifault_XL工具可以統計一個測試向量集能測出多少故障,從而給出該測試向量集的故障覆蓋率。采用該工具的測試流程為:

1) 用芯片功能測試激勵中的部分激勵對芯片的RTL級代碼進行代碼覆蓋率的測試;

2) 在激勵中調用Verifault的系統任務,實現故障的管理、注入等工作;

3) 使用Verilog_XL運行本組測試激勵,得到Verifault統計結果;

4) 根據統計結果報告的故障覆蓋率調整測試激勵,直至達到滿足要求的故障覆蓋率;

5) 對達到要求的測試激勵進行測試向量的提取。

需要注意的是流程中第3步,由于受機器內存的限制,Verifault能復制的設計數量有限,為了驗證所有的prime故障,Verifault會重復進行多遍測試(pass),這是對Verifault仿真時間影響最大的因素。每測試完一遍,Verifault會報告一次統計結果。

測試結果

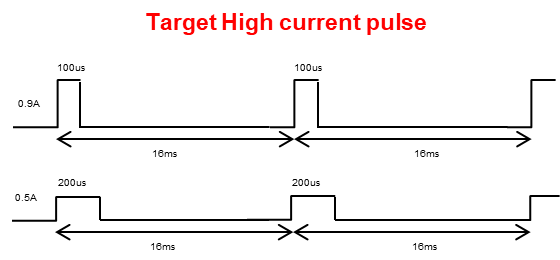

本文經過對測試激勵的不斷調整,最終可達到的最高故障覆蓋率為81.3%,在時鐘的下降沿提取測試向量,得到了超過88萬個的測試向量,其位數為54b。

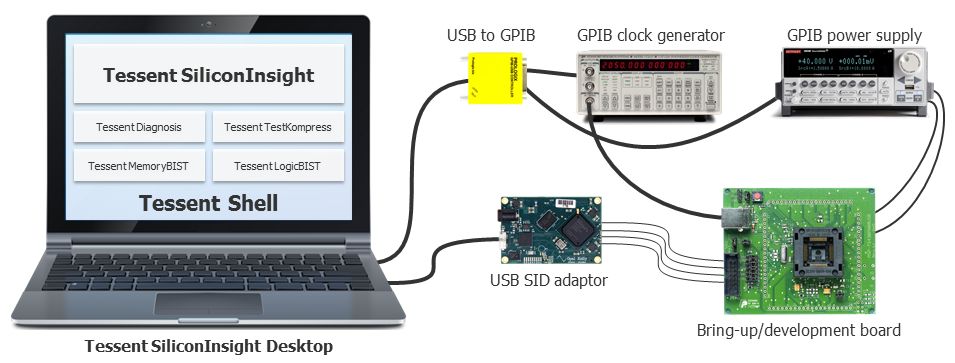

采用DFT技術的芯片測試測試工具與測試流程

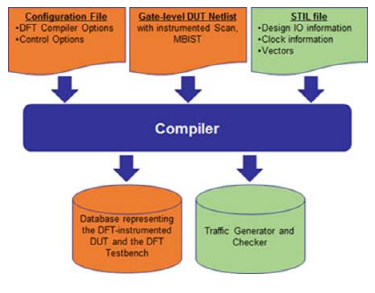

因為該芯片邏輯是全同步設計,所以采用ATPG+掃描鏈的DFT技術可以得到高效的測試向量集和較高的故障覆蓋率。Synopsys公司的DC和TetraMAX工具是完成該可測性設計的最佳選擇。

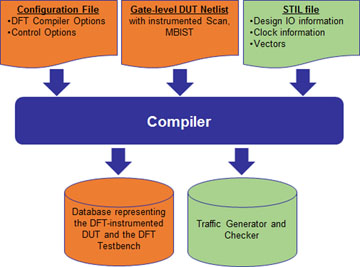

DC用來完成掃描鏈的插入,同時生成TetraMAX需要的約束文件(.spf文件)和插入掃描鏈后的網表文件。TetraMAX是用來實現ATPG的工具,需要與DC配合使用。 采用這些工具的測試流程為:

1) 首先把不符合可測性設計要求的邏輯模塊從邏輯內核中分離出來,保證邏輯內核的時鐘可以直接使用管腳輸入的時鐘,而非門生時鐘;

2) 增加test_en端口,以及一些必要的邏輯門;

3) 在綜合后的網表基礎上插入掃描鏈;

4) 使用TetraMAX做ATPG,生成測試向量;

5) 用得到的測試向量測試邏輯內核;

在最后一步中,由于TetraMAX生成測試激勵的時候,掃描鏈的數據是并行加載的,與實際情況不同,所以需要重新編寫測試激勵對得到的測試向量的可靠性進行測試。

測試結果

TetraMAX生成的測試向量共有324個,其位數為359b。測試覆蓋率達到92.86%。掃描器件的使用以及與DFT相關的附加邏輯的加入,導致了芯片面積的增長,據輸出報告可知,采用DFT技術后,芯片面積增加了大約13%。

結語

通過兩種測試方法的對比,可以看到,不采用DFT技術,不必增加邏輯,但僅使用功能驗證時的測試激勵可能無法達到要求的故障覆蓋率,而且測試深度(生產測試用向量)也容易超過測試機的存儲量。本文對該控制芯片進行測試時,如果不采用DFT技術,雖然測試覆蓋率可以達到80%以上,但測試向量卻高達80多萬,若以人工的方法修改測試向量,將大大延長芯片開發周期,推遲芯片上市時間。采用DFT技術雖然增加了芯片面積,但可以自動生成高效簡潔的測試向量,且故障覆蓋率能達到90%以上,極大地提高了芯片的測試效率,降低了測試成本。

電子發燒友App

電子發燒友App

評論