摘要:本文主要介紹了微型存儲(chǔ)測(cè)試系統(tǒng)在姿態(tài)測(cè)量中的設(shè)計(jì),結(jié)合飛行體在飛行時(shí)各種變化姿態(tài)的采集,編幀,存儲(chǔ)這一問(wèn)題,詳細(xì)地闡述了微型存儲(chǔ)測(cè)試系統(tǒng)的工作原理、系統(tǒng)組成、軟硬件設(shè)計(jì)以及所實(shí)現(xiàn)的性能指標(biāo);根據(jù)微型存儲(chǔ)測(cè)試系統(tǒng)的具體工作過(guò)程,結(jié)合大量的拋撒試驗(yàn),利用FPGA比較系統(tǒng)的設(shè)計(jì)和完善了微型存儲(chǔ)器的各個(gè)工作狀態(tài),提高了存儲(chǔ)器系統(tǒng)工作的可靠性,最后通過(guò)軟件對(duì)試驗(yàn)數(shù)據(jù)的讀取和分析,驗(yàn)證該微型測(cè)量系統(tǒng)的正確性。

概述

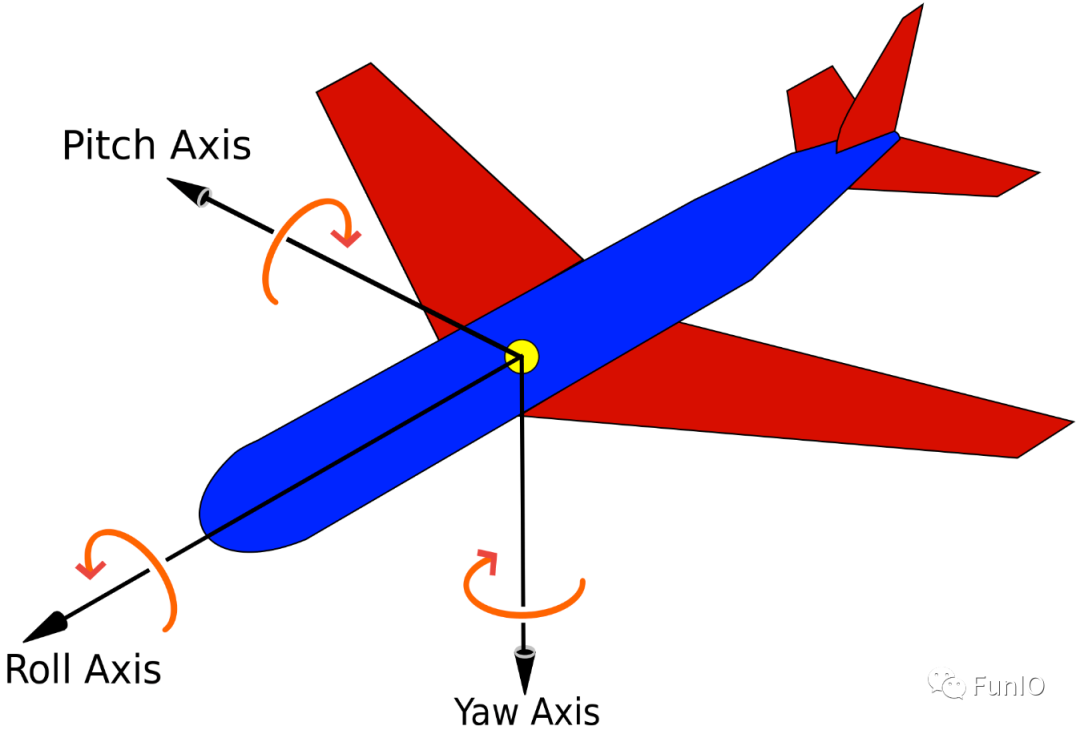

微型姿態(tài)測(cè)試系統(tǒng)在航天科技領(lǐng)域起著越來(lái)越重要的作用,對(duì)確定飛行體各種飛行姿 態(tài)有著重要的參考意義。在測(cè)試領(lǐng)域中,低功耗,小體積,噪聲小,大容量已是競(jìng)爭(zhēng)的主要 目標(biāo)。微型姿態(tài)測(cè)試系統(tǒng)主要用于飛行體拋撒后到落地前的三向角速度及線加速度參數(shù)的測(cè) 量、采集、編碼和記錄,并在飛行體硬回收后完成遙測(cè)數(shù)據(jù)的事后讀取和處理。

在本文的設(shè) 計(jì)中,飛行體姿態(tài)微型存儲(chǔ)器測(cè)試系統(tǒng)達(dá)到并滿足了傳統(tǒng)上難以勝任的高性能指標(biāo)和許多技 術(shù)上的苛刻要求,其中體積小,低功耗,抗過(guò)載性能高是本文設(shè)計(jì)的主要方面。從系統(tǒng)結(jié)構(gòu) 設(shè)計(jì)、電源設(shè)計(jì)以及狀態(tài)設(shè)計(jì)等環(huán)節(jié)保證了小體積、低功耗的設(shè)計(jì)要求,也提高了整個(gè)系統(tǒng) 的抗高過(guò)載性能。

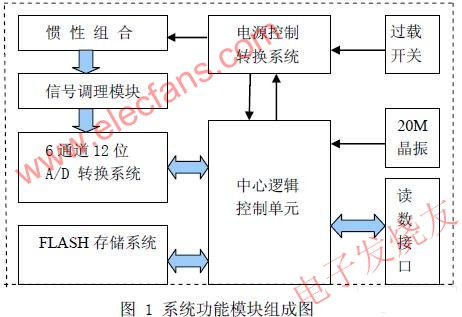

1 微型姿態(tài)存儲(chǔ)測(cè)量系統(tǒng)的模塊組成及工作原理[1] 如圖1 所示,為微型姿態(tài)存儲(chǔ)測(cè)量系統(tǒng)框圖。整個(gè)系統(tǒng)由過(guò)載開(kāi)關(guān)、慣性組合、電源控 制及變換電路、信號(hào)調(diào)理電路、A/D 轉(zhuǎn)換系統(tǒng)、中心控制邏輯單元、FLASH 存儲(chǔ)器和讀數(shù)接 口電路等組成。

飛行體在空中飛行中當(dāng)達(dá)到額定的過(guò)載量時(shí),系統(tǒng)將由過(guò)載開(kāi)關(guān)來(lái)觸發(fā)啟動(dòng)信號(hào),飛行 體的三維角速度及線加速度參數(shù)由慣性組合轉(zhuǎn)化為供記錄器采集的模擬信號(hào),記錄器將在 FPGA 中心控制單元的時(shí)序控制下對(duì)模擬信號(hào)進(jìn)行采集、編幀和存儲(chǔ),當(dāng)記錄器被收回時(shí), 將由地面檢測(cè)系統(tǒng)對(duì)存儲(chǔ)器的數(shù)據(jù)進(jìn)行讀取和事后處理。

電源控制及變換模塊接收到“啟動(dòng)”命令后,就將飛行體上裝載的電源經(jīng)轉(zhuǎn)化輸出給慣 性組合供電,同時(shí)將系統(tǒng)電池經(jīng)過(guò)變換輸出系統(tǒng)3.3V 給整個(gè)記錄裝置供電。信號(hào)調(diào)理模塊就是把慣性組合信號(hào)調(diào)理成可以被記錄裝置接收的0~3.3V 信號(hào),同時(shí)保證記錄裝置足夠的 輸入阻抗,即不影響被測(cè)信號(hào)的電氣特性。

6 通道12 位A/D 轉(zhuǎn)換系統(tǒng)的功能是在中心控制 邏輯模塊的控制下,按照12KHz 的采樣率對(duì)慣性組合送來(lái)的6 路信號(hào)進(jìn)行采集,并將采集到 的數(shù)據(jù)送到中心控制邏輯模塊中。

中心控制邏輯模塊是整個(gè)記錄裝置的核心部分,它的功能是對(duì)6 通道12 位A/D 轉(zhuǎn)換系 統(tǒng)送來(lái)的數(shù)據(jù)按順序采集后送入128M 容量的8 位 FLASH 存儲(chǔ)器中,其路采樣率為2KHz。

在 中心控制邏輯模塊開(kāi)始工作的同時(shí),就隨之發(fā)出“自保”命令給電源控制及變換模塊,以保 證電源控制及變換模塊即使在過(guò)載開(kāi)關(guān)再斷開(kāi)后仍能正常工作,即保證過(guò)載開(kāi)關(guān)的觸發(fā)有效 性。128M 容量的8 位FLASH 存儲(chǔ)模塊主要用于數(shù)據(jù)的存儲(chǔ),其容量為128M,數(shù)據(jù)位為8 位。 由于FLASH 存儲(chǔ)器具有掉電保持?jǐn)?shù)據(jù)的功能,所以不需要設(shè)計(jì)后備電池進(jìn)行掉電保護(hù)數(shù)據(jù)。 根據(jù)前面的技術(shù)指標(biāo)可知,128M 的容量遠(yuǎn)滿足所要求的存儲(chǔ)容量。

讀數(shù)接口模塊主要用于 記錄裝置檢測(cè)時(shí)和回收后數(shù)據(jù)的讀取。 2 微型存儲(chǔ)器系統(tǒng)的硬件設(shè)計(jì) 微型姿態(tài)存儲(chǔ)器測(cè)試系統(tǒng)對(duì)電源有苛刻的要求,因?yàn)榇藴y(cè)試系統(tǒng)由電池供電,根據(jù)低功 耗的設(shè)計(jì)原則,本設(shè)計(jì)采用了MAX8882 的低壓差電源控制芯片,對(duì)輸入3.5V~5V 電壓能同 時(shí)轉(zhuǎn)換出3.3V 和2.5 電壓,通過(guò)邏輯程序控制電源芯片可有效控制整個(gè)系統(tǒng)的耗電量。當(dāng) 啟動(dòng)電源控制系統(tǒng)時(shí),邏輯控制中心產(chǎn)生自保信號(hào)來(lái)控制MAX8882 的shutdown 使能端,使 整個(gè)系統(tǒng)正常供電。當(dāng)采集存儲(chǔ)過(guò)程完成時(shí),邏輯控制中心產(chǎn)生觸發(fā)信號(hào)來(lái)控制MAX8882 停止工作,從而整個(gè)系統(tǒng)處于節(jié)能狀態(tài)。

微型姿態(tài)存儲(chǔ)器的電路設(shè)計(jì)思路主要依據(jù)對(duì)飛行體的姿態(tài)參數(shù)進(jìn)行實(shí)時(shí)采集,編幀和存 儲(chǔ)這一思路進(jìn)行設(shè)計(jì),信號(hào)調(diào)理電路是將姿態(tài)模擬信號(hào)進(jìn)行分壓、濾波和跟隨運(yùn)放后傳送發(fā) 給模數(shù)轉(zhuǎn)換芯片, 模數(shù)轉(zhuǎn)換電路采用了美信公司的MAX1295 芯片,它是6 通道12 位精度逐 次逼近式的數(shù)模轉(zhuǎn)換器,采樣率為265Ksps,片內(nèi)集成了高性能的采樣保持電路和參考電壓 源。同時(shí)還具有較低的功耗和較高的信噪比,可以進(jìn)行內(nèi)部和外部的采樣模式設(shè)置,在本設(shè) 計(jì)中采用了外部采樣模式。

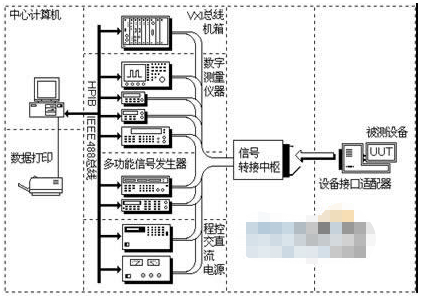

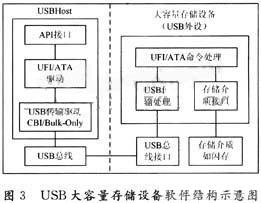

存儲(chǔ)系統(tǒng)采用了三星公司的K9F1G08 FLASH 存儲(chǔ)器,該芯片性能良好,封裝較小,為 微型化測(cè)試系統(tǒng)設(shè)計(jì)提供了便利,在邏輯中心的時(shí)序控制下,對(duì)存儲(chǔ)器進(jìn)行讀、寫(xiě)、擦除操 作,每種操作都采用了由FLASH 的狀態(tài)信號(hào)r/b 進(jìn)行中斷的方式。在寫(xiě)操作過(guò)程中,以8 位數(shù)據(jù)進(jìn)行存取,在存儲(chǔ)一頁(yè)數(shù)據(jù)時(shí)要進(jìn)行頁(yè)編程,大約要300us~700us ,等待r/b 狀態(tài) 信號(hào)的改變后進(jìn)入下一頁(yè)的存儲(chǔ),為了使采集和存儲(chǔ)的速度相匹配,在FPGA 內(nèi)部采用了8K Bits 的雙口RAM,在FLASH 存儲(chǔ)器進(jìn)行頁(yè)編程的時(shí)候進(jìn)行數(shù)據(jù)的緩存。在擦除操作過(guò)程中,對(duì) FLASH 存儲(chǔ)器要進(jìn)行塊擦除,擦除一塊時(shí)間要2ms~3ms,等待r/b 狀態(tài)信號(hào)的改變后進(jìn) 入下一塊的擦除。同樣在讀取數(shù)據(jù)操作中,每讀取一個(gè)字節(jié)都要等待r/b 的中斷,數(shù)據(jù)通過(guò) 檢測(cè)臺(tái)和USB 電纜傳給上位機(jī)。

本次設(shè)計(jì)的微型姿態(tài)存儲(chǔ)器測(cè)試系統(tǒng)的另一個(gè)主要突出點(diǎn)在于它的微型化 ,整個(gè)的記 錄器的各個(gè)芯片都采用了小型化的貼片封裝,電路板采用了四層板工藝制作,中間分別為電 源層和地層,不僅大大較小了記錄器的體積,同時(shí)對(duì)信號(hào)的隔離和抗干擾性也起到了一定的 積極作用。

3 邏輯流程圖設(shè)計(jì)

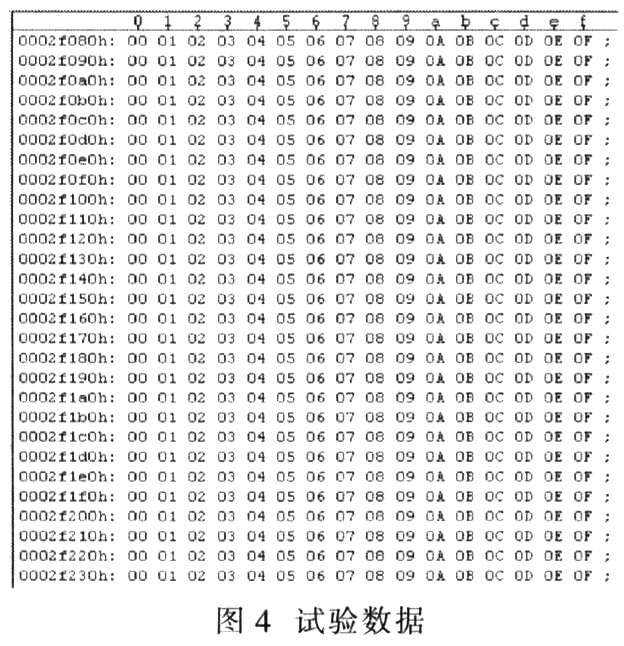

流程圖見(jiàn)圖2 所示,整個(gè)過(guò)程由過(guò)載開(kāi)關(guān)啟動(dòng)電源控制芯片以啟動(dòng)整個(gè)FPGA 的控制 時(shí)序,復(fù)位模塊由上位機(jī)復(fù)位,上電自動(dòng)復(fù)位和軟復(fù)位組合而成,當(dāng)啟動(dòng)整個(gè)系統(tǒng)時(shí),首先 要對(duì)系統(tǒng)初始化復(fù)位,同時(shí)定義一個(gè)觸發(fā)信號(hào)“esok”使初始化為“0”,以便觸發(fā)控制單元, 使系統(tǒng)進(jìn)入自檢狀態(tài),在自檢模塊中,F(xiàn)PGA 首先要從FLASH 存儲(chǔ)器第六頁(yè)連續(xù)讀取16 頁(yè)的 數(shù)據(jù),并判斷數(shù)據(jù)是否為“FF”,如果不是,則存儲(chǔ)器內(nèi)有數(shù)據(jù)存在,系統(tǒng)將停止在這個(gè)狀 態(tài);如果是則觸發(fā)信號(hào)“esok”為“1” 以啟動(dòng)A/D 采集數(shù)據(jù)模塊和FLASH 存儲(chǔ)數(shù)據(jù)模塊, 此時(shí),中心控制模塊在響應(yīng)采集模塊的中斷使A/D 模塊以16K 的采樣率往FPGA 內(nèi)部的雙口RAM 寫(xiě)數(shù)據(jù),同時(shí)FLASH 存儲(chǔ)模塊在中心控制模塊下,判斷并推進(jìn)RAM 的地址以讀取RAM 的 數(shù)據(jù),在數(shù)據(jù)不斷寫(xiě)入FLASH 存儲(chǔ)器的同時(shí)判斷數(shù)據(jù)容量是否達(dá)到指定的數(shù)據(jù)量,如果沒(méi)有, 則返回到FLASH 寫(xiě)狀態(tài)繼續(xù)存儲(chǔ)數(shù)據(jù),一旦達(dá)到,系統(tǒng)則觸發(fā)一個(gè)信號(hào)來(lái)控制電源模塊關(guān)閉 電源,使整個(gè)系統(tǒng)停止工作,以減小耗電量。當(dāng)插上讀數(shù)口時(shí)啟動(dòng)USB 在線,在上位機(jī)的控 制下,對(duì)FLASH 存儲(chǔ)器進(jìn)行讀取操作,以便對(duì)數(shù)據(jù)進(jìn)行事后分析和處理。

結(jié)束語(yǔ)

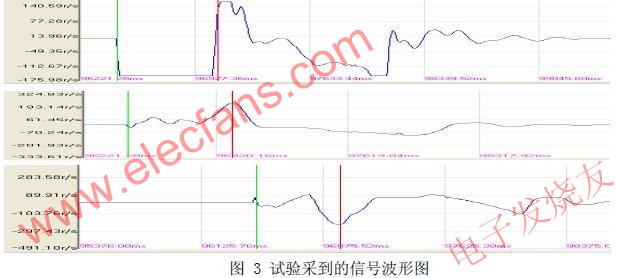

該微型姿態(tài)存儲(chǔ)測(cè)試系統(tǒng)工作性能良好,在拋撒試驗(yàn)中得到如圖3 所示的信號(hào),達(dá)到了 理論要求,成功的完成了飛行體姿態(tài)參數(shù)的采集和存儲(chǔ),通過(guò)多次試驗(yàn)證明,該微型測(cè)試系 統(tǒng)具有一定的工程應(yīng)用性并對(duì)其他測(cè)試設(shè)計(jì)有著重要參考意義。欲了解更多信息請(qǐng)登錄電子發(fā)燒友網(wǎng)(http://www.1cnz.cn)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論