頻率信號產生電路在FPGA中頻率控制模塊的控制下,產生高精度正弦主振信號和本振信號,分別用于光調制和混頻。此電路產生的信號要求頻率可調,且具有高的頻率穩定性和低的相位噪聲,相位抖動小,以保證最終的測量精度。

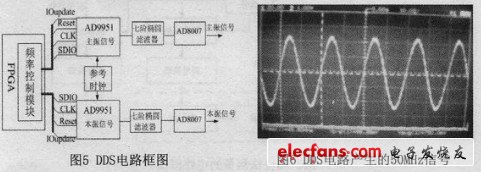

在本系統中,我們基于直接數字頻率合成(DDS)技術進行信號產生。DDS的實現,使用芯片AD9951。AD9951是一個可控的頻率合成芯片,具有32位頻率轉換字,最大合成頻率為160MHz。系統中采用兩塊AD9951,分別產生主振信號和本振信號。FPGA通過該芯片的控制端口,對其產生的信號頻率進行控制。其控制時序如圖4所示。

?

AD9951產生的頻率信號具有一定的雜散,系統中使用七階橢圓低通濾波器進行濾波,然后使用運算放大器AD8007進行信號放大。電路框圖如圖5所示。該電路產生的50MHz的正弦信號如圖6所示。

?

2.2.3 混頻鑒相電路

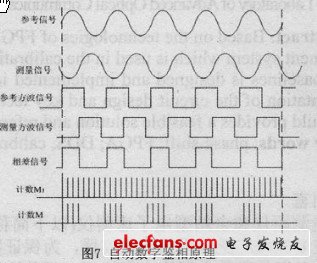

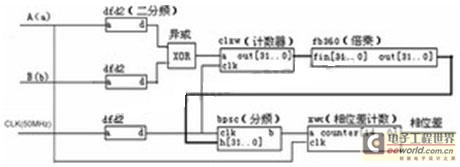

由于測量信號頻率較高,直接對其進行鑒相難以達到良好的鑒相精度,因而在系統中采用混頻的方法進行差頻鑒相。在差頻鑒相中,參考信號和測量信號同時與本振信號進行混頻,濾除混頻后高頻分量,得到混頻后低頻參考信號和混頻后低頻測量信號。混頻降低了信號頻率,但保持相位差不變,便于鑒相操作。相位差的檢測使用自動數字鑒相法。其原理如圖7所示。參考信號和測量信號通過過零比較,得到參考方波信號和測量方波信號。比較兩方波信號,得到兩者之間的相位差信號,然后使用高頻計數脈沖對相位差信號,然后使用高頻計數脈沖對相位差信號進行計數。設參考信號和測量信號的周期為f,高頻計數脈沖的頻率為fc,一個周期內的計數值為M,則相位差為:φ=2πMf /fc。為了減小偶然誤差,提高鑒相精度,可以對多個周期計數求平均。設N個周期的計數值為M",則φ=2πM"f/Nfc。

?

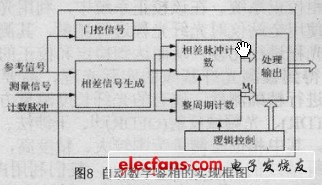

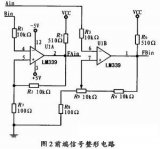

混頻電路的實現基于混頻器AD831。使用兩片AD831,分別用于參考信號與本振信號混頻及測量信號與本振信號混頻。混頻后使用芯片MAX274進行帶通濾波,得到混頻后的低頻正弦信號。然后通過基于MAX912的過零比較電路將正弦信號轉換為同相位差的方波信號,輸入到FPGA中進行鑒相。在FPGA中,利用多周期自動數字鑒相法,對相位差進行檢測。其實現框圖如圖8所示。

?

3 測量結果

在實際測量中,利用組合測尺頻率先后進行兩次測量。第一次取主振信號頻率為52MHz,本振信號頻率為51.99MHz;第二次取主振信號頻率為51MHz,本振信號頻率為50.99MHz。對應于混頻后信號頻率為10kHz。FPGA中鑒相高速計數脈沖頻率為50MHz。基于以上參數,對多段光纖進行測量。兩次測量的結果進行分析比較,可得到測量值。被測光纖的實際光程已由精密反射儀通過光學方法進行標定。測量結果如表1所示。

?

由以上測量結果可以看到,在一定的量程范圍內,基于相位法的測量系統,對光纖光程的測量誤差絕對值小于2mm。

4 結論

本文在FPGA、直接數字頻率合成(DDS)、自動數字鑒相等技術的基礎上,設計并實現了基于相位法的電路測量系統。實際測量結果表明,此測量系統在一定的量程范圍內,對光纖光程的測量誤差絕對值小于2mm。在此測量水平下,此測量系統可用于基于光纖的激光測距校正與檢定中,對其中的光纖基線進行測量和標定,這為光電測距儀和全站儀的室內檢定提供了一個可行的方案和參考。

本文所論述的相位法測量的電路實現是一個初步方案,在電路設計、系統優化和誤差分析等方面還需要做進一步的改進,以提高系統性能。

電子發燒友App

電子發燒友App

評論