實驗四、MAX+PLUSⅡ的層次設計

一? 實驗目的

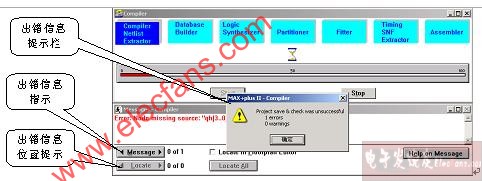

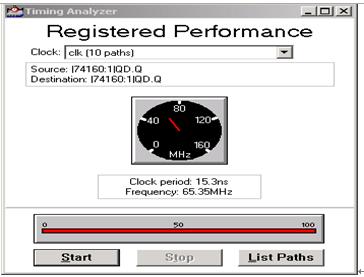

1進一步掌握MAX+PLUSⅡ的基本使用,包括設計的輸入、編譯和仿真。

2掌握MAX+PLUSⅡ的層次化設計方法。

二? 實驗設備與儀器

1?計算機

2? MAX+PLUSⅡ工具軟件

三? 實驗內容

1? 設計底層文件一個一位半加器。

2? 設計頂層文件一個一位全加器。

3? 設計頂層文件4位全加器。

4? 設計文件的層次顯示。

四? 實驗原理

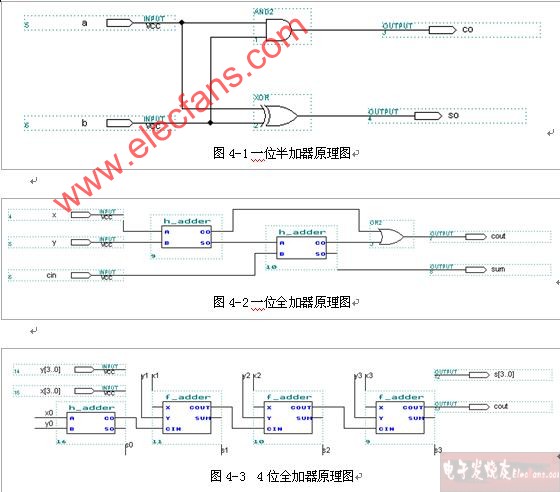

計算機中數的操作都是以二進制進位的,最基本的運算就是加法運算。按照進位是否加入,加法器分為半加器和全加大路兩種。計算機中的異或指令的功能就是求兩個操作數各位的半加和。一位半加器有兩個輸入和輸出,其電路原理如圖4-1所示。

表4-1? 半加器真值表

?

一? 實驗目的

1進一步掌握MAX+PLUSⅡ的基本使用,包括設計的輸入、編譯和仿真。

2掌握MAX+PLUSⅡ的層次化設計方法。

二? 實驗設備與儀器

1?計算機

2? MAX+PLUSⅡ工具軟件

三? 實驗內容

1? 設計底層文件一個一位半加器。

2? 設計頂層文件一個一位全加器。

3? 設計頂層文件4位全加器。

4? 設計文件的層次顯示。

四? 實驗原理

計算機中數的操作都是以二進制進位的,最基本的運算就是加法運算。按照進位是否加入,加法器分為半加器和全加大路兩種。計算機中的異或指令的功能就是求兩個操作數各位的半加和。一位半加器有兩個輸入和輸出,其電路原理如圖4-1所示。

表4-1? 半加器真值表

?

|

輸入 |

輸出 | ||

|

Bi |

Hi |

Ci | |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

一個半加電路的真值表如表4-1所示,根據真值表可得到半加器的函數表達式:

?????????

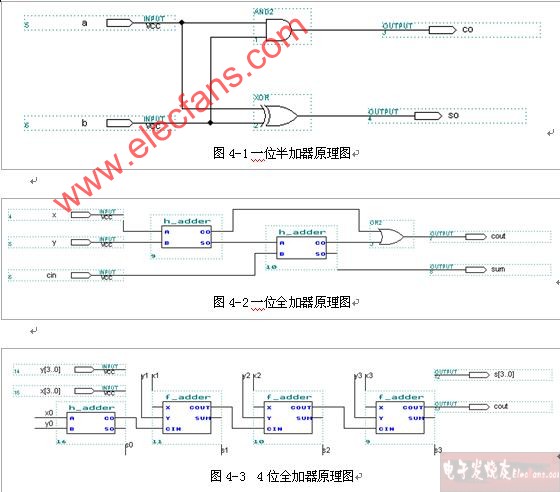

一位全加器由2個半加器組成,其電路原理如圖4-2所示。

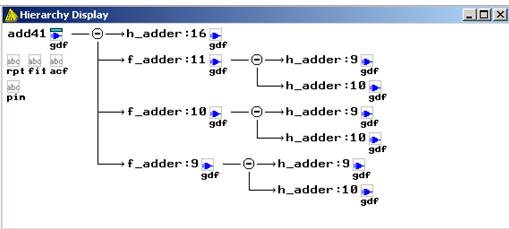

頂層設計文件4位全加器右4個全加器組成,其電路原理如圖4-3所示。

?????????

一位全加器由2個半加器組成,其電路原理如圖4-2所示。

頂層設計文件4位全加器右4個全加器組成,其電路原理如圖4-3所示。

五? 實驗步驟

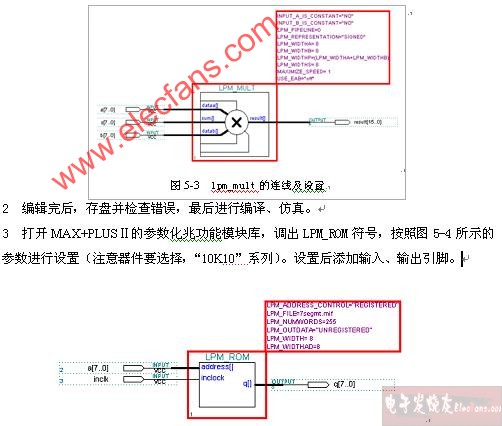

1? 設計底層文件,用圖形輸入法編輯一位半加器原理圖,如圖4-1所示。編輯完后,存盤并檢查錯誤,最后進行編譯、仿真并生成一個默認符號h_adder。

2? 設計頂層文件1,用已經生成的半加器符號編輯一個全加器。如圖4-2所示。編輯完后,存盤并檢查錯誤,最后進行編譯、仿真并生成一個默認符號f_adder。

3? 設計頂層文件2,用已經生成的全加器符號編輯一個4位全加器。如圖4-3所示。編輯完后,存盤并檢查錯誤,最后進行編譯、仿真并生成一個默認符號adder41。

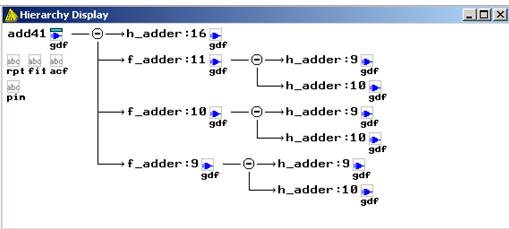

4? 在最頂層項目文件里打開層次顯示窗口可觀察adder41項目的層次結構。選擇菜單命令MAX+PLUSⅡ/Hierarchy Display(層次顯示)或單擊 按鈕,即打開層次顯示窗口,顯示出adder41的層次樹結構,如圖4-4所示。在層次結構圖中,可以清楚的看到adder41文件中包涵了1個h_adder符號和3個f_adder符號。而一個f_adder文件中又包涵了2個h_adder符號。

1? 設計底層文件,用圖形輸入法編輯一位半加器原理圖,如圖4-1所示。編輯完后,存盤并檢查錯誤,最后進行編譯、仿真并生成一個默認符號h_adder。

2? 設計頂層文件1,用已經生成的半加器符號編輯一個全加器。如圖4-2所示。編輯完后,存盤并檢查錯誤,最后進行編譯、仿真并生成一個默認符號f_adder。

3? 設計頂層文件2,用已經生成的全加器符號編輯一個4位全加器。如圖4-3所示。編輯完后,存盤并檢查錯誤,最后進行編譯、仿真并生成一個默認符號adder41。

4? 在最頂層項目文件里打開層次顯示窗口可觀察adder41項目的層次結構。選擇菜單命令MAX+PLUSⅡ/Hierarchy Display(層次顯示)或單擊 按鈕,即打開層次顯示窗口,顯示出adder41的層次樹結構,如圖4-4所示。在層次結構圖中,可以清楚的看到adder41文件中包涵了1個h_adder符號和3個f_adder符號。而一個f_adder文件中又包涵了2個h_adder符號。

圖4-4? adder41的層次結構顯示

?

六? 記錄實驗結果并完成實驗報告

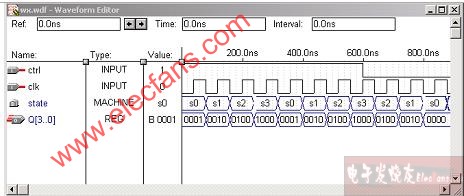

1?記錄并觀察 一位半加器的編譯和仿真結果。

2?記錄并觀察一位全加器的編譯和仿真結果。

3?記錄并觀察4位全加器的編譯和仿真結果。

4?打開層次顯示窗口可觀察adder41項目的層次結構。

1?記錄并觀察 一位半加器的編譯和仿真結果。

2?記錄并觀察一位全加器的編譯和仿真結果。

3?記錄并觀察4位全加器的編譯和仿真結果。

4?打開層次顯示窗口可觀察adder41項目的層次結構。

電子發燒友App

電子發燒友App

評論