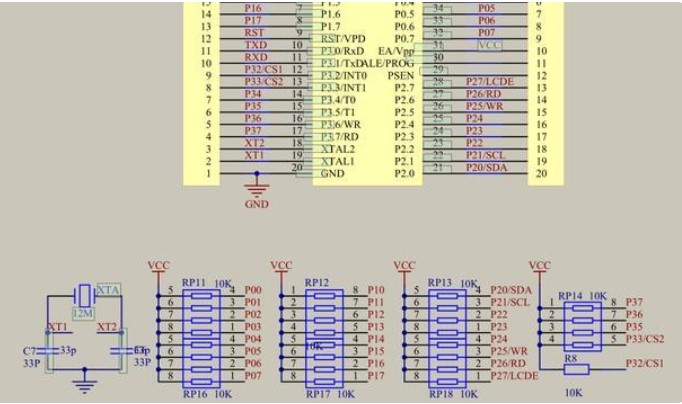

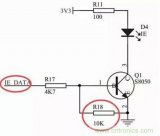

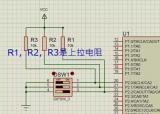

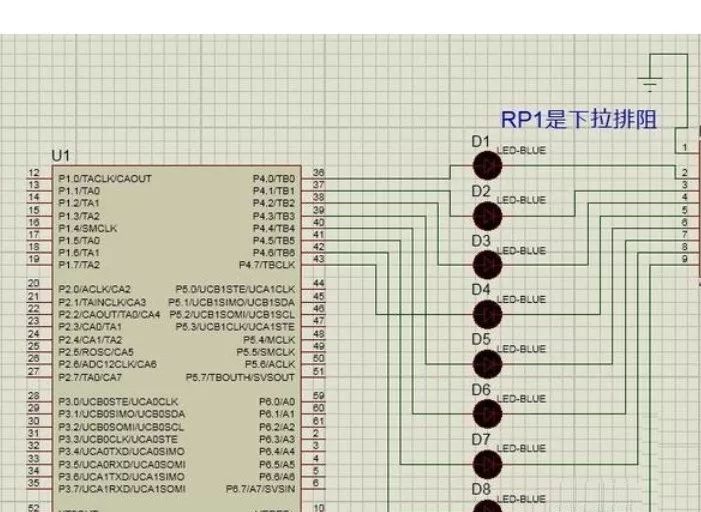

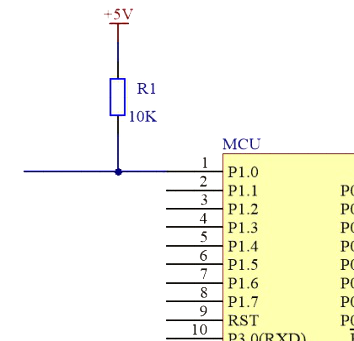

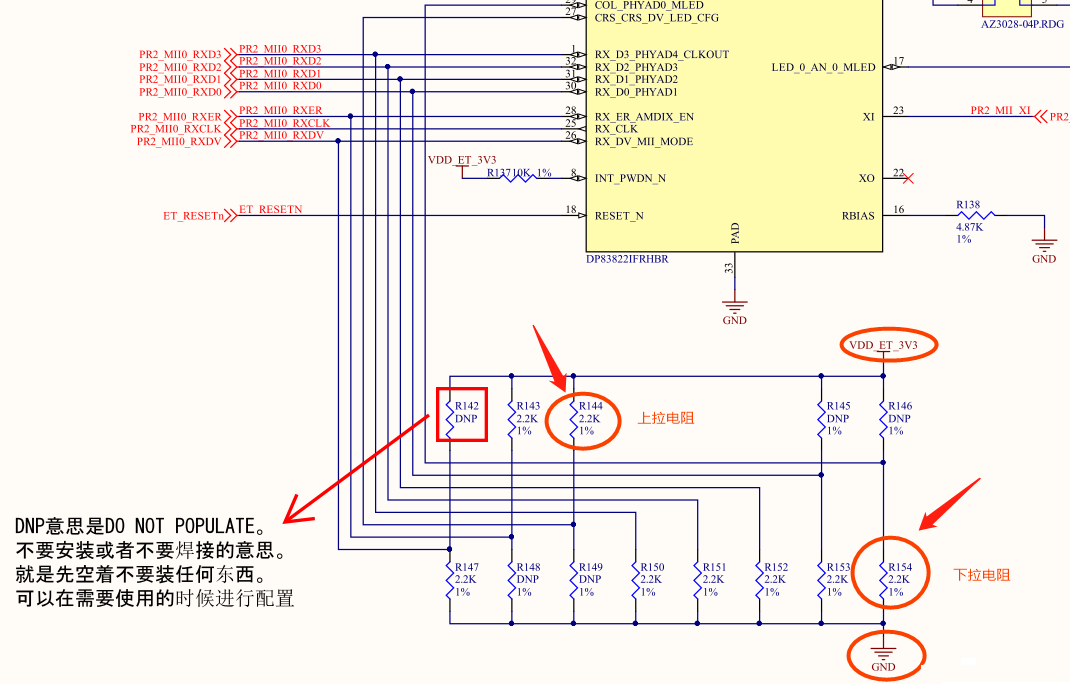

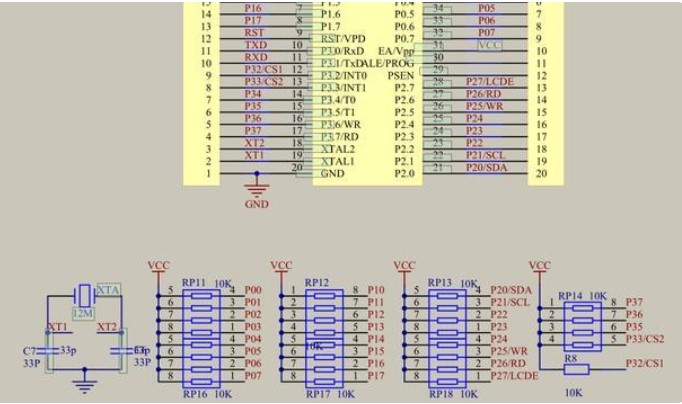

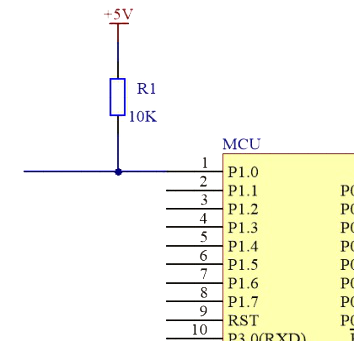

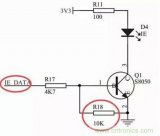

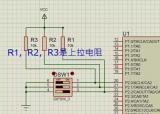

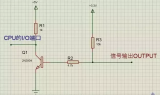

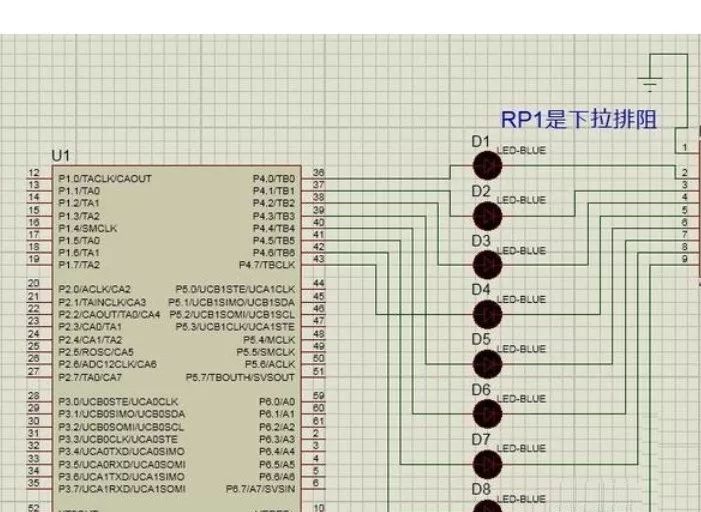

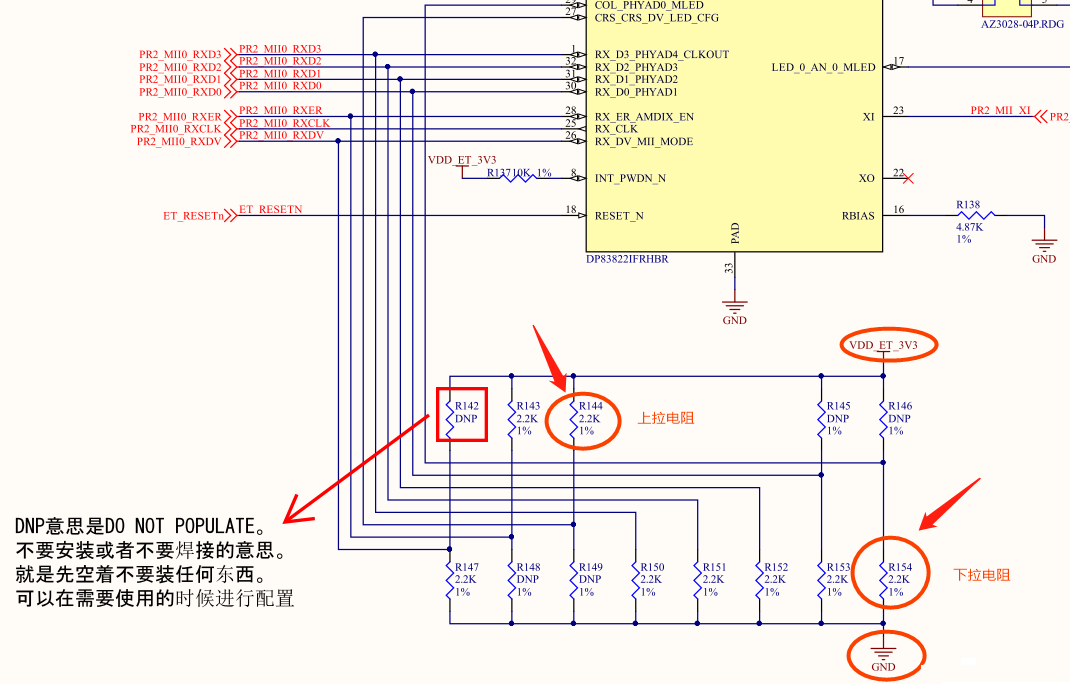

愛玩單片機的親們通常都會常見IO引腳接上拉電阻或下拉電阻的現象,如圖一中RP11、RP12、RP13、RP14均為上拉電阻,圖二中R18為下拉電阻。

2022-08-16 15:55:24 6532

6532

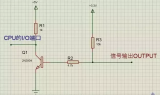

看下圖,R10和R7就是下拉電阻,這兩個電阻有什么作用呢?我們要先了解下什么是下拉電阻。

2022-11-23 09:26:53 1611

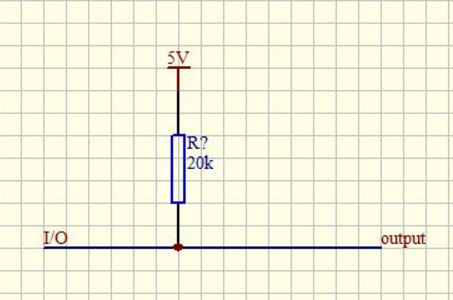

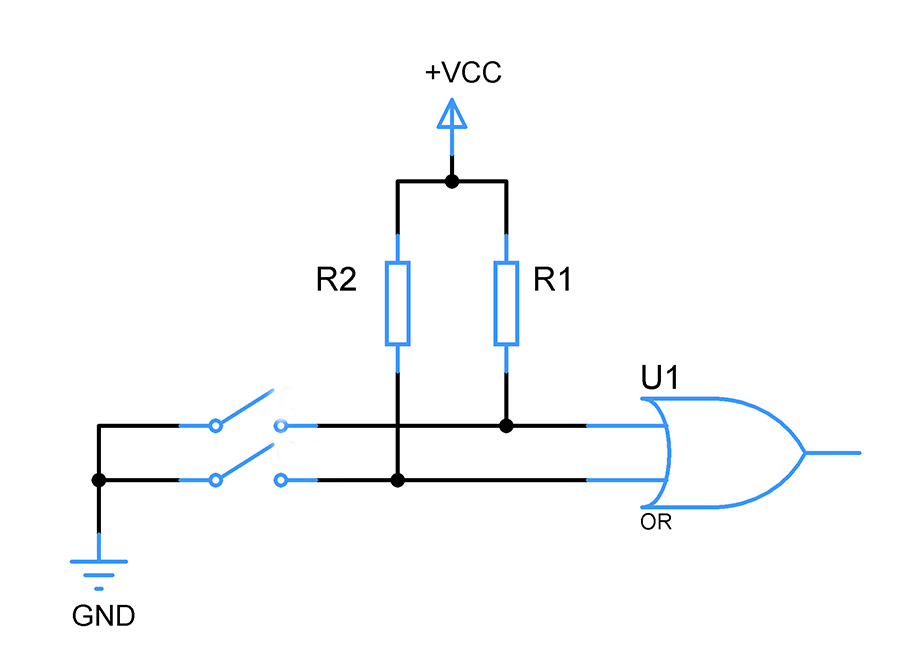

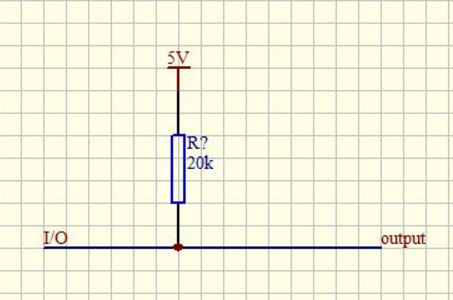

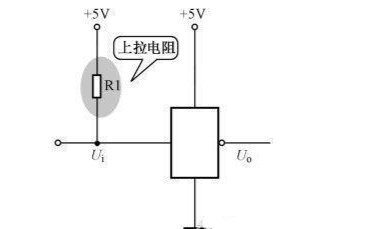

1611 一、上下拉電阻介紹 ??上拉電阻:將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平。作用:上拉是對器件注入電流;灌電流;當一個接有上拉電阻的IO端口設置為輸入狀態時,它的常態為高電平

2023-04-21 09:49:34 6887

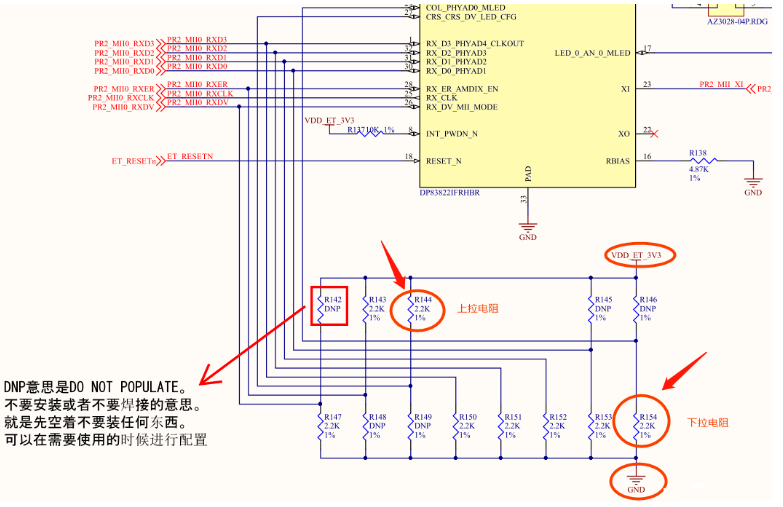

6887 什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。那么,上拉電阻和下拉電阻的用處和區別分別又是什么呢?

2023-05-26 10:16:01 1912

1912

電阻在電路中起限制電流的作用,而上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻,這兩者統稱為“拉電阻”,最基本的作用是:將狀態不確定的信號線通過

2023-06-07 15:20:05 1174

1174

電路設計中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會損壞電子器件。

2023-10-08 16:23:42 1186

1186

0電阻 上拉電阻 下拉電阻

2012-08-06 13:38:12

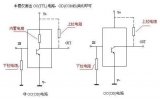

能力。 -------為OC門提供電流 2、定義: 上拉:通過一個電阻對電源相連。 下拉:通過一個電阻到地。 -------上拉就是將不確定的信號通過一個電阻嵌位在高電平!電阻同時起限流作用!下拉同理

2018-06-28 06:21:54

按下時,由于干擾,可能高也可能是低信號輸入。根據實際需要,為保證WK_UP不被按下時,STM32能夠確定檢測到IO口是低電平,所以設置接入下拉電阻。2、上拉電阻和下拉電阻上拉電阻...

2021-08-18 06:27:20

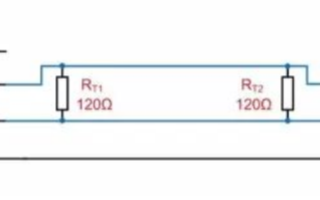

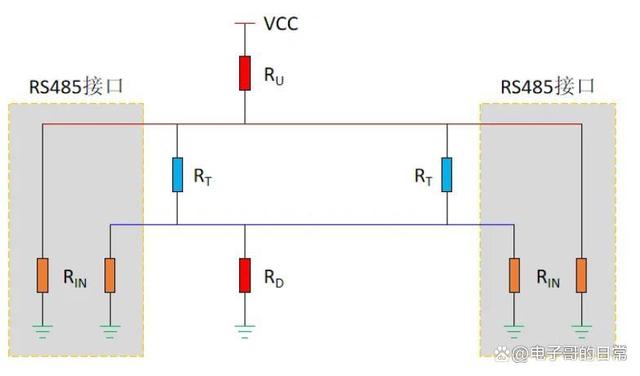

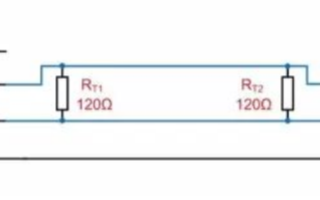

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2013-07-21 21:43:41

上、下拉電阻的作用電平兼容板內或板間器件信號電平特性各不相同,出于兼容性的考慮,須加上拉電阻以保證兼容性。當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般

2019-07-27 08:38:52

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2012-08-07 15:15:18

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2011-09-19 08:55:51

(上拉下拉電阻)所謂上拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與電源VCC相連,固定在高電平;同理下拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與地GND相連,固定

2022-01-14 08:44:01

上拉電阻與下拉電阻上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它

2021-12-13 07:08:22

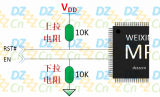

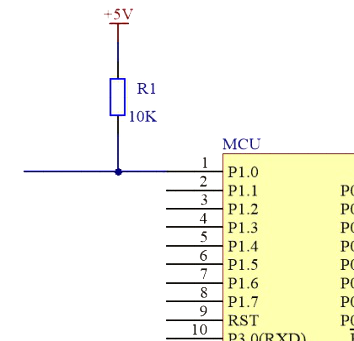

上拉電阻與下拉電阻用在什么場合? 答:用在數字電路中,存在高低電平的場合。 上拉電阻與下拉電阻怎么接線? 上拉電阻:電阻一端接VCC,一端接邏輯電平接入引腳(如單片機引腳) 下拉電阻:電阻一端接GND,一端接邏輯電平接入引腳(如單片機引腳)

2019-05-20 13:48:41

概述:上拉電阻:將一個不確定的信號(高或低電平),通過一個電阻與電源VCC相連,固定在高電平。下拉電阻:將一個不確定的信號(高或低電平),通過一個電阻與地GND相連,固定在低電平。上、下拉電阻的作用

2021-12-13 06:05:27

一句話:上拉電阻的目的是為了保證GPIO無信號輸入時輸入端的電平為高電平,相反的,下拉電阻是為了保證GPIO無信號輸入時輸入端的電平為低電平。不懂的具體可以看下面一、概念上拉電阻就是:將一個不確定

2022-01-14 09:16:39

上拉電阻和下拉電阻的區別及案列分析上拉電阻在一個信號未過來之前、默認(保證)該電位的電平信號是高電平,在信號過來后如果是高電平、那么保持高電平。如果過來低電平信號、那么輸出的信號就會變成低電平。改圖

2022-01-14 06:30:35

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2008-05-22 08:46:35

上拉電阻和下拉電阻上拉電阻(Pull-Up)所謂上拉電阻就是用一個電阻將VCC和單片機的IO口直接連接起來,目的是當IO在沒有輸出一個確定信號時將IO的電位鉗在一個高電平上。上拉電阻作用如下:1.當

2022-01-25 07:23:49

一、定義: 1、上拉就是將不確定的信號通過一個電阻嵌位在高電平!電阻同時起限流作用!下拉同理 2、上拉是對器件注入電流,下拉是輸出電流 3、弱強只是的阻值不同,沒有什么嚴格區分 4、對于

2018-10-19 16:30:19

下橋臂不能直通,如果它們都用同一個單片機來驅動,必須設置初始狀態.防止直通! 2、定義: l 上拉就是將不確定的信號通過一個電阻嵌位在高電平!電阻同時起限流作用!下拉同理! l 上拉是對器件注入

2019-06-27 05:55:08

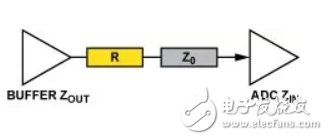

,提供泄荷通路。5、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

2016-09-27 09:20:11

本人遇到一個問題如下芯片的pcie的參考時鐘要求hcsl或者lvpecl電平,芯片內部存在onchip AC耦合電容在時鐘發出端,p&N分別下拉150ohm至gnd之后 ,33ohm匹配

2017-03-05 23:58:42

什么場合?答:用在數字電路中,存在高低電平的場合。上拉電阻與下拉電阻怎么接線?上拉電阻:電阻一端接VCC,一端接邏輯電平接入引腳(如單片機引腳)下拉電阻:電阻一端接GND,一端接邏輯電平接入引腳(如

2019-03-25 07:00:00

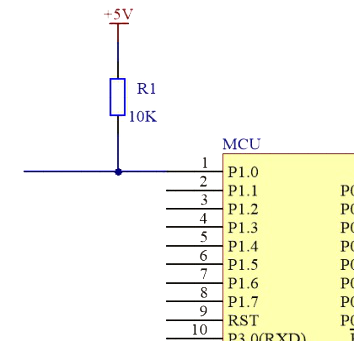

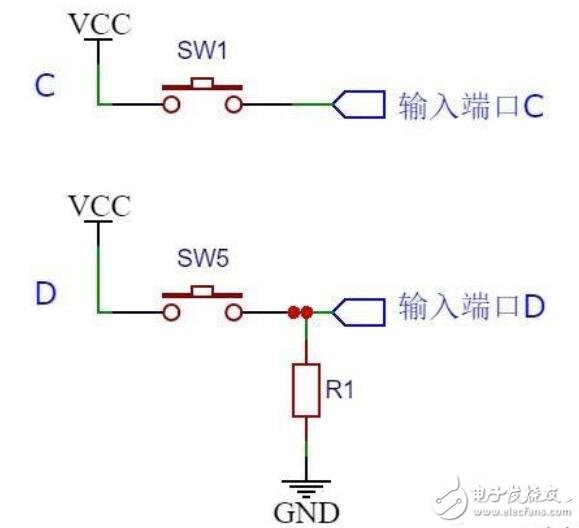

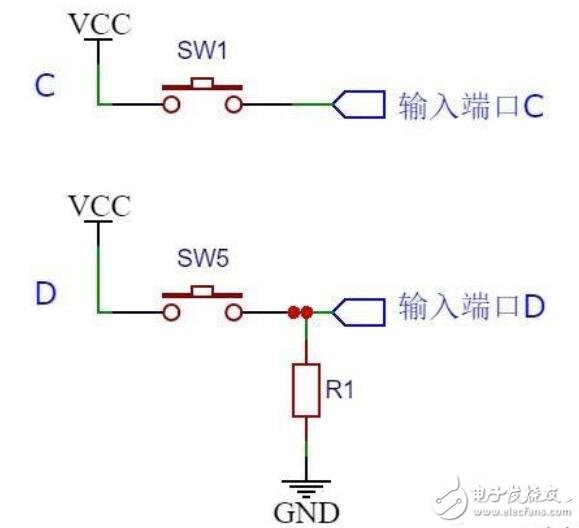

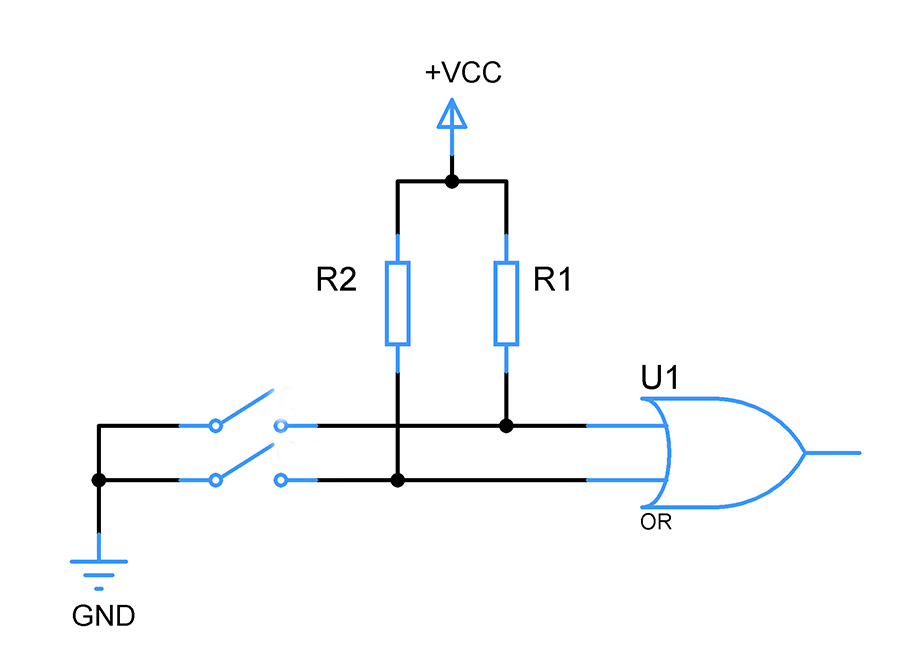

判斷上下拉電阻時,只需要看按鍵按下之前,兩端是高電平還是低電平。例如:R1這個電阻,一端接VCC,在按鍵按下之前兩端是高電平,所以它就是上拉電阻,是為了檢測低電平輸入。R2這個電阻,一端接GND,在按鍵按下之前,兩端是低電平,所以它就是下拉電阻,是為了檢測高電平輸入。...

2022-01-14 08:31:27

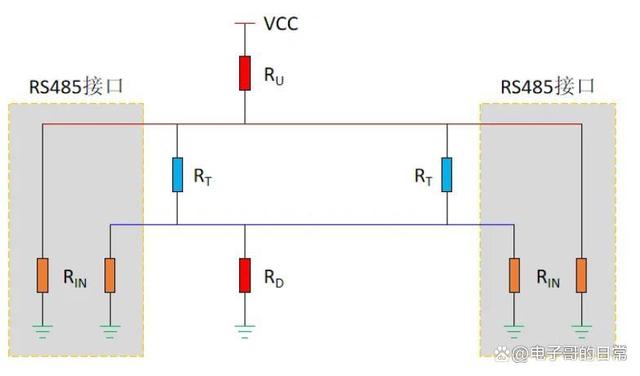

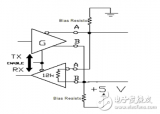

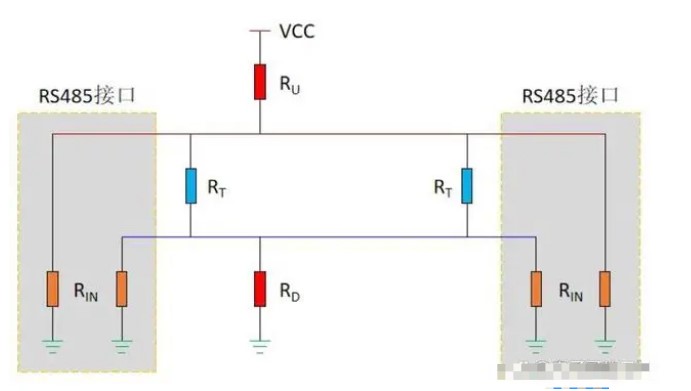

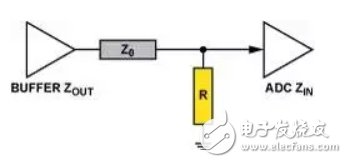

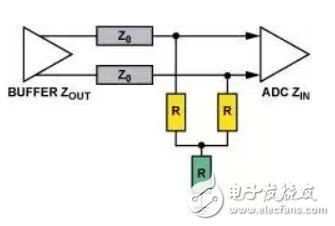

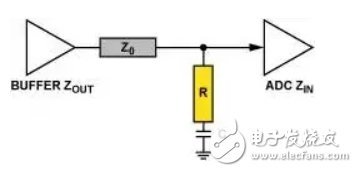

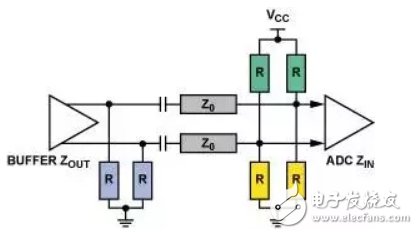

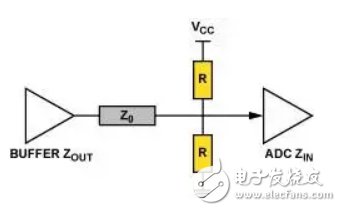

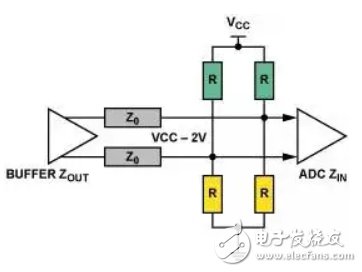

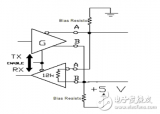

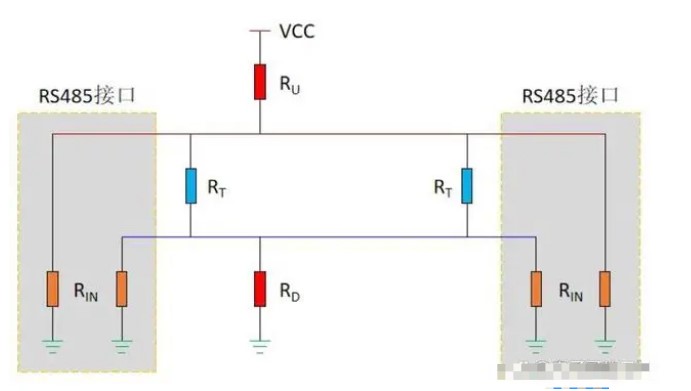

。二、什么情況下需要加上下拉電阻?當遇到信號反射問題時,通常會通過增加匹配電阻來避免信號反射,以1對1通信為例,如圖1所示。由于485總線通常使用特性阻抗為120Ω的雙絞線,因此在485總線的首尾兩端增加120Ω終端電阻來避免信號反射問題。

2019-05-21 07:10:59

。5、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾

2014-11-17 10:24:15

作者:一博科技高速先生成員孫小兵端接就是人為加入電阻來改善信號由于鏈路阻抗突變帶來的反射問題的一種方式,并且引入成本也較低,在很多場合都有運用。但是端接電阻擺放位置一直困惑大家,或許大家只知道串聯

2023-02-27 17:31:13

輸入阻抗,提供泄荷通路。5、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易

2014-08-21 09:56:08

前言:在一張原理圖中無論時上拉還是下拉都是非常普遍的,轉載此文章,可以很快的理解上拉電阻與下拉電阻的原理與作用。如果還沒有理解,可以參考上拉與下拉的原理與應用2者共同的作用是:避免電壓的“懸浮

2022-01-14 08:28:26

本帖最后由 科炬電子 于 2017-5-22 18:49 編輯

上拉電阻就是把不確空的信號通過一個電阻箝位在高電平,此電阻還起到限流的作用。同理下拉電阻是把不確定的信號箝位在低電平。上拉

2017-05-22 18:49:54

CMOS drivers信號· 適合低頻時鐘信號和非常短的走線· 下拉電阻CMOS 優勢:非常簡單(R = Z0)弱點:高功耗備注:不推薦· LVPECL優勢:· 簡單的3電阻解決方案。· 就節能而言稍好

2019-09-27 07:30:00

。(3)戴維寧端接戴維寧端接就是采用上拉電阻和下拉電阻來共同組成端接電路,使得戴維寧等效阻抗等于傳輸線的特征阻抗以實現阻抗匹配。戴維寧端接的優點是上拉電阻和下拉電阻都能用來吸收反射,在電路上沒有信號

2020-03-16 11:29:10

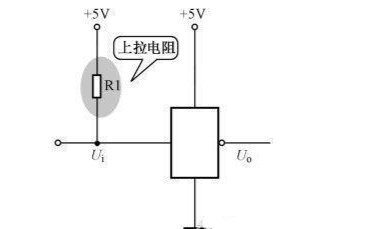

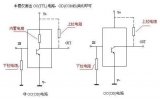

在數字電路的應用中,上拉電阻、下拉電阻起著穩定電路工作狀態的作用。圖1所示的反向器,輸入端Ui通過下拉電阻R接地,這樣在沒有高電平輸入時,可以使輸入端穩

2007-10-15 17:36:42 3211

3211 上拉電阻與下拉電阻

上下拉電阻: 1、當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),

2008-01-14 13:10:44 6297

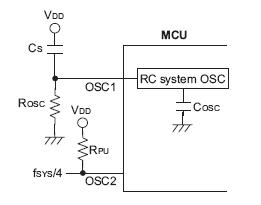

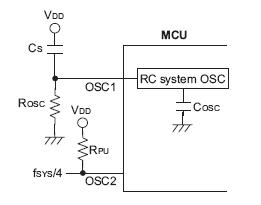

6297 單引腳下拉電阻型RC 振蕩器以下是外接下拉電阻的RC 振蕩器電路。

說

2008-10-24 16:03:51 979

979

什么是上拉電阻,什么是下拉電阻?它們的作用是什么?

上拉電阻一般是一端接電源,一端接芯片管腳的電路中的電阻,下拉電阻一般是指一端接芯片管

2009-06-28 10:13:44 111580

111580

上拉下拉電阻(zz)基礎知識

一、什么是上拉電阻?什么是下拉電阻?

上拉就是將不確定的信號通過

2009-11-23 09:16:09 5030

5030 上拉電阻和下拉電阻的選型和計算,根據不同情況選擇不同上下拉電阻的方法

2015-11-30 18:20:28 0

0 關于上拉電阻和下拉電阻的入門必知,新手要學

2016-02-17 11:21:25 0

0 上拉下拉電阻作用總結。

2016-05-19 16:40:52 60

60 電子專業單片機相關知識學習教材資料——上拉電阻與下拉電阻的應用,感興趣的小伙伴們可以瞧一瞧。

2016-09-13 17:46:48 0

0 上拉電阻、下拉電阻、限流電阻的原理和作用

2016-11-11 18:42:28 55

55 用在什么場合? 答:用在數字電路中,存在高低電平的場合。 上拉電阻與下拉電阻怎么接線? 上拉電阻:電阻一端接VCC,一端接邏輯電平接入引腳(如單片機引腳) 下拉電阻:電阻一端接GND,一端接邏輯電平接入引腳(如單片機引腳

2016-11-04 16:01:57 578

578

上拉電阻和下拉電阻的作用及選擇

2016-12-15 18:39:07 25

25 上拉電阻,與下拉電阻的分析

2017-07-24 16:40:20 70

70 所謂上,就是指高電平;所謂下,是指低電平。上拉,就是通過一個電阻將信號接電源,一般用于時鐘信號數據信號等。下拉,就是通過一個電阻將信號接地,一般用于保護信號。

2017-08-23 18:00:14 37288

37288

一、定義: 上拉就是將不確定的信號通過一個電阻鉗位在高電平!電阻同時起限流作用!下拉同理! 上拉是對器件注入電流,下拉是輸出電流;弱強只是上拉電阻的阻值不同,沒有什么嚴格區分;對于非集電極

2017-11-27 15:59:38 77866

77866

本文首先介紹了下拉電阻的作用,其次介紹了下拉電阻的原理以及典型電路,最后闡述了下拉電阻的選擇。

2018-08-22 17:51:37 63736

63736 管腳的電路中的電阻,下拉電阻一般是指一端接芯片管腳一端接地的電阻。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。

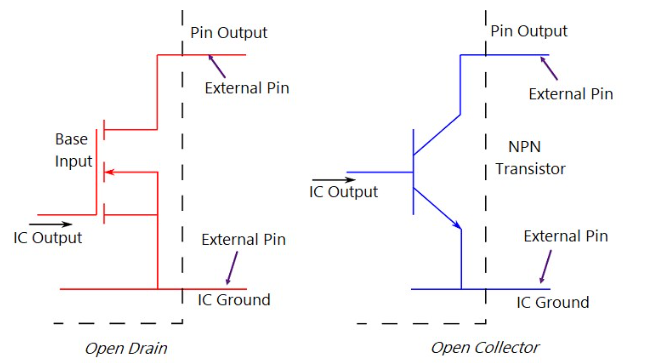

2018-08-30 18:33:16 127518

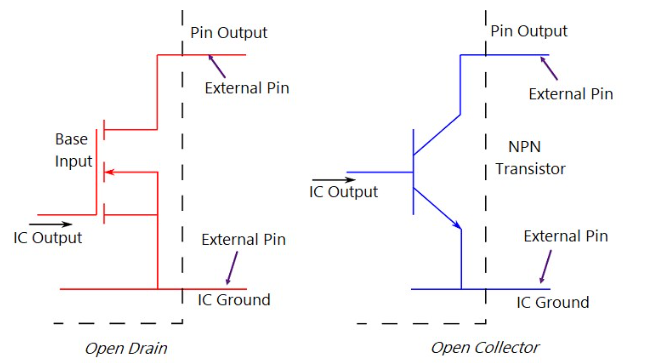

127518 因為單片機的輸出端都是開漏輸出的,就像三極管的集電極一樣,如果沒有上拉電阻它輸出不了高電平。而下拉電阻就是拉低電平,跟上面是相反的,不過在單片機中,一般都是要上拉電阻的多,很少有下拉電阻的單片機。

2018-09-11 08:59:27 9988

9988 上拉就是將不確定的信號通過一個電阻嵌位在高電平!“電阻同時起限流作用”!下拉同理!

2018-09-23 18:19:00 30379

30379 上拉電阻就是將不確定的信號通過一個電阻拉到高電平,同時此電阻也起到一個限流作用,下拉就是下拉到低電平。

2018-11-02 16:22:25 8495

8495 上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2018-12-24 08:00:00 15

15 因為單片機的輸出端都是開漏輸出的,就像三極管的集電極一樣,如果沒有上拉電阻它輸出不了高電平。而下拉電阻就是拉低電平,跟上面是相反的,不過在單片機中,一般都是要上拉電阻的多,很少有下拉電阻的單片機。

2019-01-22 16:06:33 10487

10487 在數字電路的應用中,時常會聽到上拉電阻、下拉電阻,上拉電阻、下拉電阻起著穩定電路工作狀態的作用。

2019-08-07 14:30:02 10000

10000

接電源正極的拉電阻稱之為上拉電阻,接電源負極的拉電阻稱之為下拉電阻;在數字電路的世界中只能識別“0”和“1”,加入上拉電阻,可以把未知狀態的電路控制為高電平“1”;加入下拉電阻,可以把未知狀態的電路控制為低電平“0”,可以有效的防止意外發生。

2019-09-07 10:01:44 18478

18478

詳解RS-485上下拉電阻的選擇

2020-02-27 15:33:50 5869

5869

在上拉電阻和下拉電阻的電路中,經常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經常會串一個電阻?

2020-04-28 14:17:04 11546

11546

輸入端如果是高阻狀態,或高阻抗輸入端處于懸空狀態,此時需要加上拉或下拉電阻,以免受到隨機電平的影響,進而影響電路工作。同樣,如果輸出端處于被動狀態,需要加上拉或下拉電阻,如輸出端僅僅是一個三極管的集電極,還可以提高芯片輸入信號的噪聲容限,增強抗干擾能力。

2020-05-29 15:52:51 13568

13568

,地到器件引腳上的電阻叫下拉電阻,作用是平時使該引腳為低電平。低電平引腳在IC內部與GND相連接;高電平引腳在IC內部與超大電阻相連接。 上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用,下拉同理。對于

2020-09-03 14:56:08 4172

4172 上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2021-01-02 17:01:00 4769

4769

電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻。

在上拉電阻和下拉電阻的電路中,經常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經常會串一個電阻?

2022-02-10 10:43:08 2420

2420

上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2021-02-20 14:20:15 7961

7961

AD9525: 8路LVPECL輸出低抖動時鐘發生器

2021-03-21 15:00:20 0

0 經常看到芯片設計手冊時,芯片外圍會有上拉或者下拉電阻還有一些無源器件。如何選擇正確值的上拉電阻和下拉電阻?上拉電阻和下拉電阻是如何確定?還是在選擇此類電阻的時候,有個特定的范圍?對上拉電阻和下拉電阻

2021-11-07 13:51:03 26

26 深入淺出上拉電阻下拉電阻淺談上下拉電阻思考:上下拉電阻有什么用呢?答:上下拉電阻的作用非常簡單,就是將一個不確定的信號確定下來。通過上拉電阻將不確定的信號鉗位到高電平,通過下拉電阻,將不確定的信號

2021-11-20 12:21:03 16

16 上拉電阻和下拉電阻上拉電阻(Pull-Up)所謂上拉電阻就是用一個電阻將VCC和單片機的IO口直接連接起來,目的是當IO在沒有輸出一個確定信號時將IO的電位鉗在一個高電平上。上拉電阻作用如下:1.

2021-12-01 09:21:05 11

11 判斷上下拉電阻時,只需要看按鍵按下之前,兩端是高電平還是低電平。例如:R1這個電阻,一端接VCC,在按鍵按下之前兩端是高電平,所以它就是上拉電阻,是為了檢測低電平輸入。R2這個電阻,一端接GND,在按鍵按下之前,兩端是低電平,所以它就是下拉電阻,是為了檢測高電平輸入。...

2022-01-14 14:00:34 19

19 上拉電阻、下拉電阻的一些理解最近在做課程設計,到了總結收尾階段,可愛的LBQ同學就提出了一個很可愛的問題。原文是如圖所示,其實LBQ同學的意思就是我們的實際電路是直接連51單片機的IO口的,沒有

2022-01-14 14:01:34 7

7 上拉電阻和下拉電阻的區別及案列分析上拉電阻在一個信號未過來之前、默認(保證)該電位的電平信號是高電平,在信號過來后如果是高電平、那么保持高電平。如果過來低電平信號、那么輸出的信號就會變成低電平。改圖

2022-01-14 14:02:34 26

26 一句話:上拉電阻的目的是為了保證GPIO無信號輸入時輸入端的電平為高電平,相反的,下拉電阻是為了保證GPIO無信號輸入時輸入端的電平為低電平。不懂的具體可以看下面一、概念上拉電阻就是:將一個不確定

2022-01-14 14:03:35 15

15 ,信號端口優選上拉電阻,上拉電阻時,在待機狀態下,源端常為高阻態,不加上下拉,輸入導線呈現天線效應,一旦管腳受到輻射干擾,管腳輸入狀態極易被感應發生變化。下拉電阻:平常狀態輸入表現為低電平,但輻射干擾進來后,會通過下拉電阻泄放到地,就會發生一個從 Low——Hight 的跳變,容易產生誤觸;上拉

2022-01-14 14:06:35 31

31 前言:在一張原理圖中無論時上拉還是下拉都是非常普遍的,轉載此文章,可以很快的理解上拉電阻與下拉電阻的原理與作用。如果還沒有理解,可以參考上拉與下拉

2022-01-14 14:07:36 22

22 (上拉下拉電阻)所謂上拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與電源VCC相連,固定在高電平;同理下拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與地GND相連,固定

2022-01-14 14:08:36 7

7 上拉下拉。電阻在電路上拉或者下拉,常見于單片機的IO端口,以及MOS的驅動輸出或者I2C這樣的信號上,有人選擇1K,有人選擇10K,有人選擇100K,那么我們在電路設計中,到底選擇多大的電阻比較合適

2022-01-14 14:09:36 3

3 上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2022-02-11 10:50:27 29

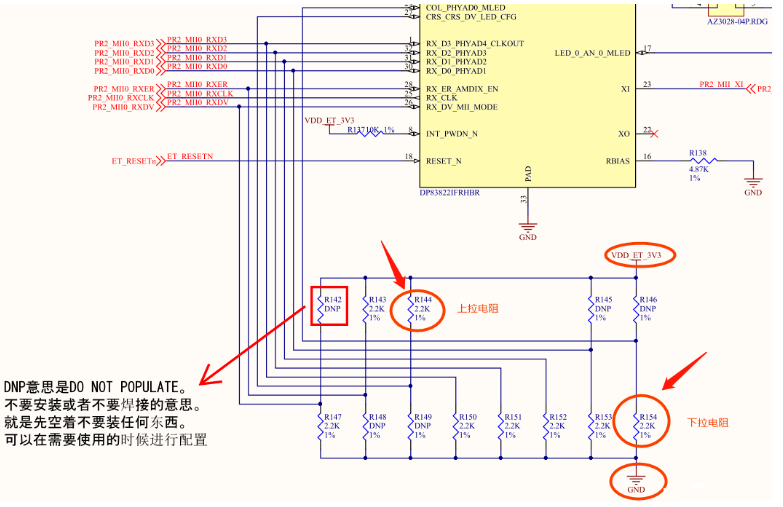

29 “上下拉電阻應用很簡單嗎?”那可不一定。電路設計中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會損壞電子器件。一般情況下,元器件需要上下拉的地方,加4.7K或10k,3.3K也行,甚至1K也可以,不會考慮太多。

2022-11-23 15:27:15 1511

1511

電路中有下拉電阻和上拉電阻,下拉電阻是把電阻的一端接地,把另一端的電位拉低,上拉電阻相反,電阻的一端接電源,把電阻另一端的電位拉至電源電位,那為什么需要上拉下拉電阻呢

2022-12-13 09:35:08 690

690 上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用,下拉同理。上拉電阻的作用主要是為集電極開路輸出型電路輸出電流通道。

2022-12-20 10:26:49 3857

3857 下拉就是接地,上拉就相當于升壓,提高驅動能力或者穩定性。 上拉電阻是用來解決總線驅動能力不足時提供電流的問題的。一般說法是上拉增大電流,下拉電阻是用來吸收電流(抵抗干擾)。 上拉是將電壓拉高,下拉

2023-02-23 16:20:02 1236

1236 上拉是用電阻將不確定的信號箝位到高電平,電阻器還充當限流器。同樣,下拉意味著通過電阻將不確定信號箝位到低電平。上拉是向器件輸入電流,下拉是輸出電流。

2023-03-08 15:24:00 5642

5642

電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻。

2023-03-17 15:51:07 2538

2538

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2023-05-31 13:57:02 1293

1293

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。

2023-06-09 09:57:29 2013

2013

電阻在電路中起限制電流的作用,而上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻,這兩者統稱為“拉電阻”,最基本的作用是:將狀態不確定的信號線通過

2023-06-10 14:17:53 1950

1950

上拉和下拉電阻是許多數字電路的組成部分。了解什么是上拉電阻或下拉電阻很重要?為什么將其用于數字電路?以及如何選擇這些的價值?本文將回答這三個問題,并讓您更好地了解它。

2023-06-18 15:25:17 3070

3070

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號

2023-06-29 17:04:31 7620

7620

本篇說明了在內置上拉電阻、下拉電阻的IC中,如果沒有規定上拉電阻、下拉電阻的電阻值時的計算方法。

2023-10-18 09:27:45 787

787 當使用上拉電阻和下拉電阻時,你需要理解它們的具體應用和原理以確保正確配置引腳,維持電平狀態,并避免電路問題。以下是更詳細的解釋:上拉電阻:作用:上拉電阻用于保持引腳的電平在邏輯高("

2023-10-30 08:00:54 661

661

電子發燒友網站提供《淺談上拉電阻下拉電阻的選擇原則.pdf》資料免費下載

2023-11-21 10:47:12 0

0 上拉電阻和下拉電阻的用處和區別? 上拉電阻和下拉電阻是電子電路中常用的兩種電阻配置方式,它們在電路中起到了關鍵的作用。下面將詳細介紹它們的用途和區別。 首先我們來介紹上拉電阻。上拉電阻是指將一個電路

2023-11-22 18:26:09 1008

1008 上拉電阻或下拉電阻是電路板維修技術中的兩個專業技術術語,在分析電路板中的電路控制原理時經常會用到上拉電阻或下拉電阻這兩個專業技術術語。

2024-02-03 12:26:59 282

282 電阻是如何實現上下拉功能的呢? 上下拉功能是指在電路中通過連接電阻來實現對信號的上拉和下拉控制。在數字電路中,上拉和下拉功能通常用于控制輸入端的電平狀態,確保輸入端在沒有外部信號輸入時能夠保持穩定

2024-02-04 09:32:18 160

160 上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。而下拉電阻是直接接到地上,接二極管的時候電阻末端是低電平,將不確定的信號通過一個電阻鉗位在低電平。

2024-02-29 12:39:46 143

143

電子發燒友App

電子發燒友App

評論