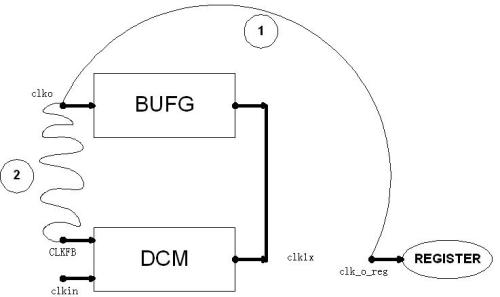

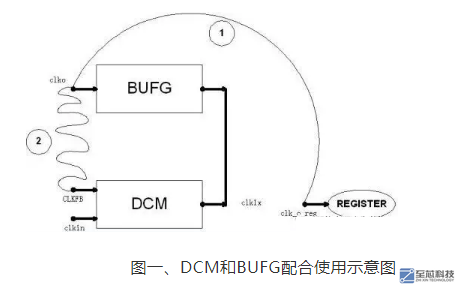

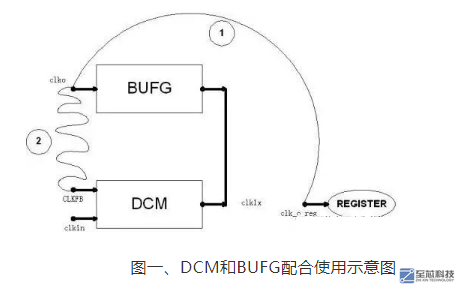

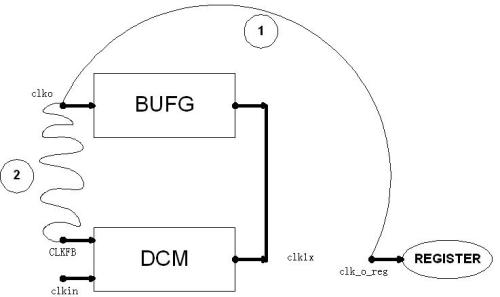

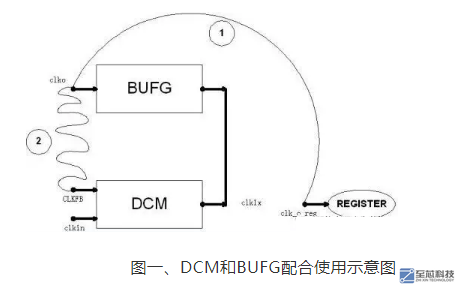

DCM一般和BUFG配合使用,要加上BUFG,應該是為了增強時鐘的驅動能力。DCM的一般使用方法是,將其輸出clk_1x接在BUFG的輸入引腳上,BUFG的輸出引腳反饋回來接在DCM的反饋時鐘

2018-05-11 03:53:00 1566

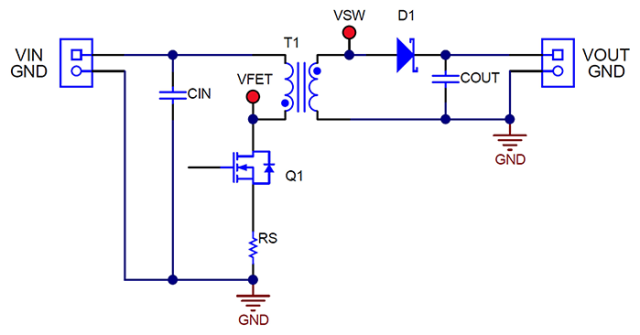

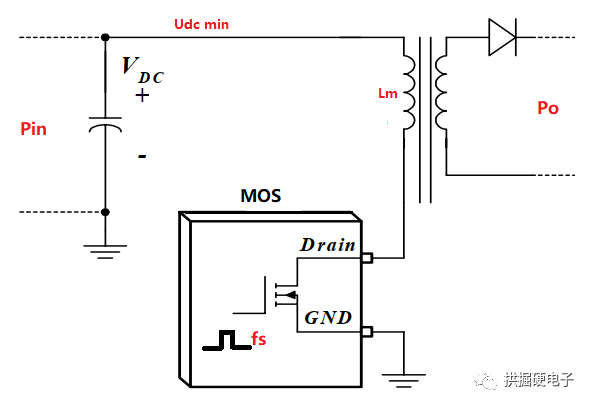

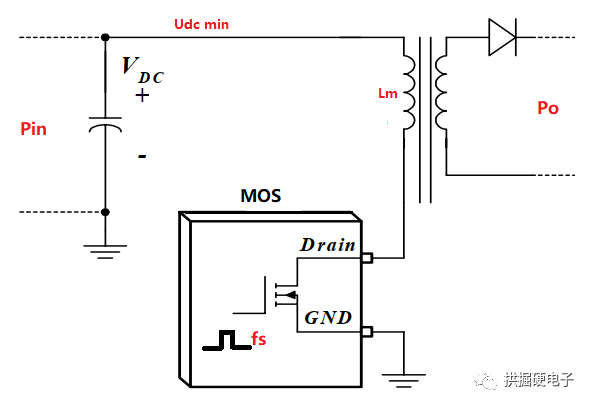

1566 表 1 詳細說明了 DCM 操作相對于 CCM 的特性。DCM 的一個關鍵屬性是具有較低的初級電感會降低占空比,而不管變壓器的匝數比如何。此屬性可讓您限制設計的最大占空比。如果您嘗試使用特定控制器

2022-08-08 09:48:57 2097

2097

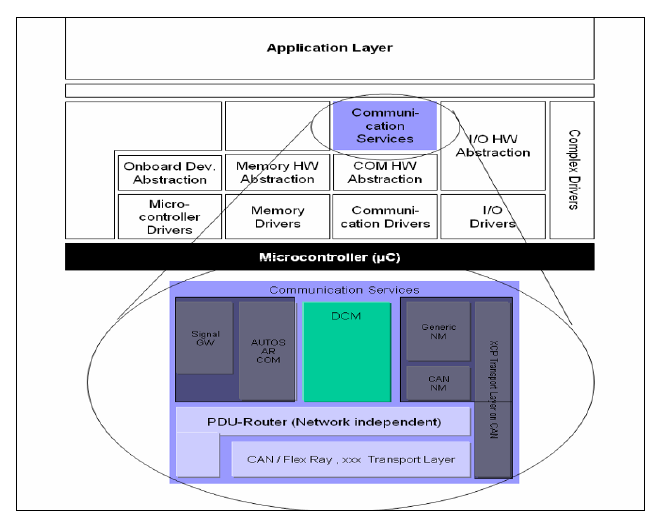

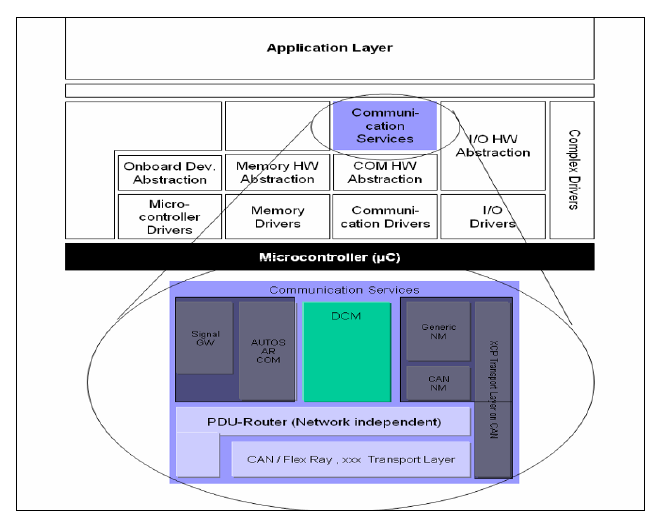

DCM全稱Diagnostic Communication Manager,它位于AUTOSAR基礎軟件的服務層,它的主要作用是為開發和生產階段提供與診斷儀交互的診斷服務。

2023-07-08 16:41:56 4205

4205

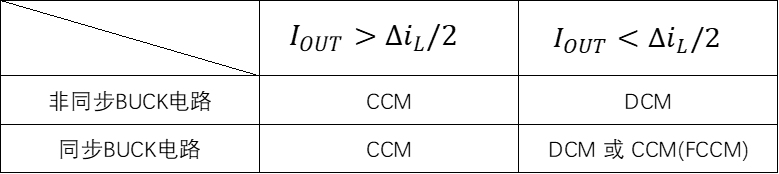

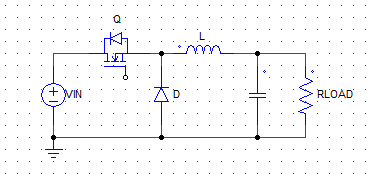

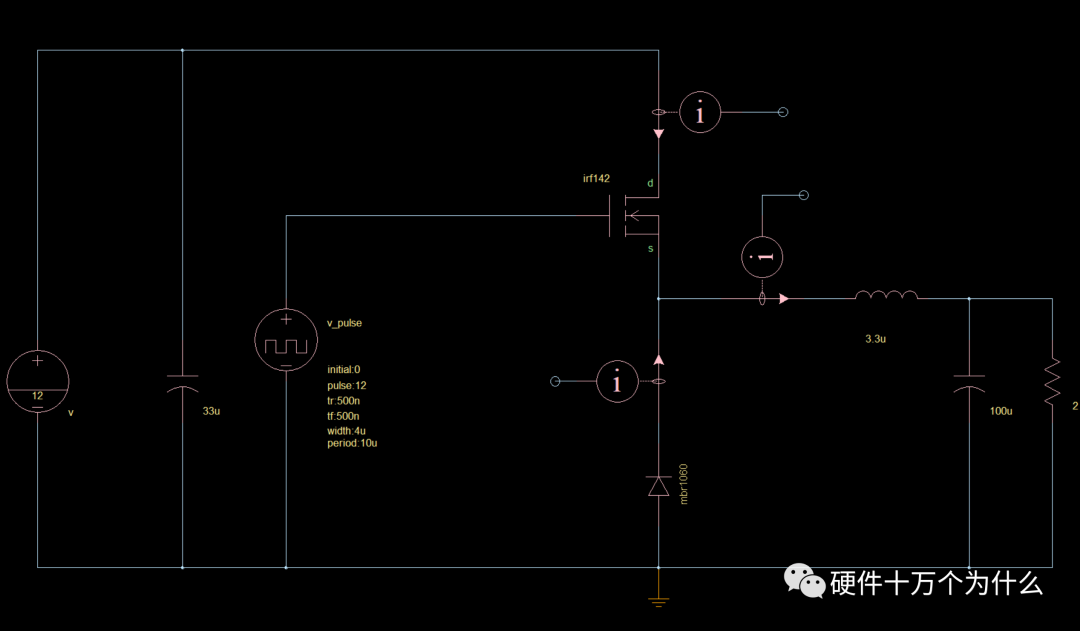

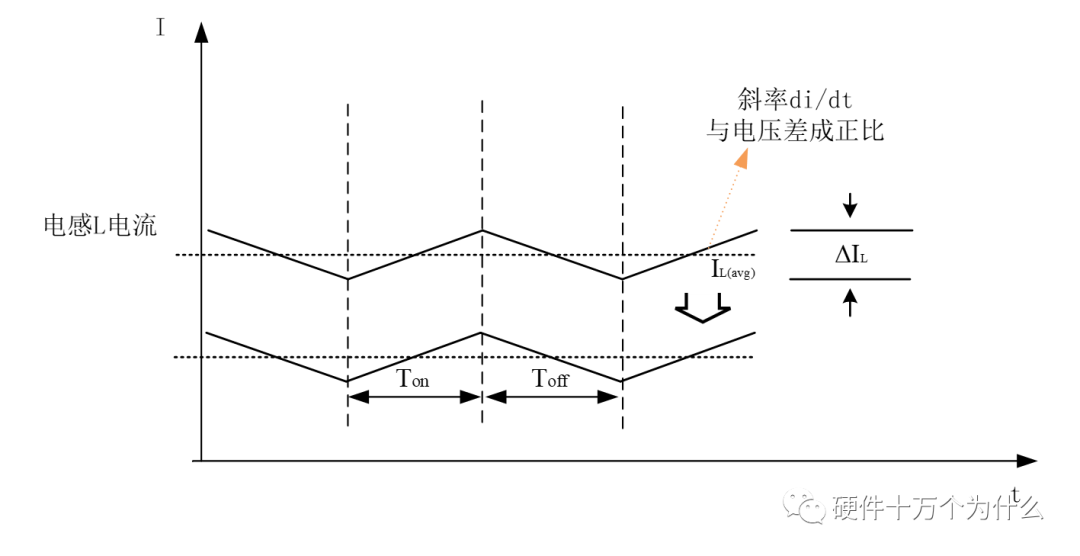

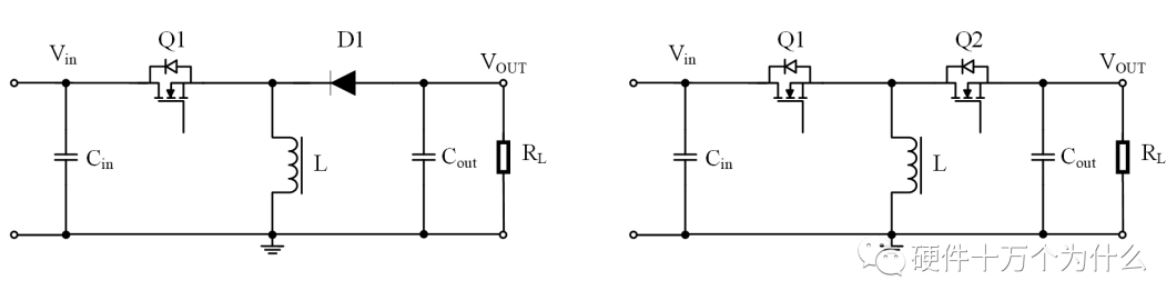

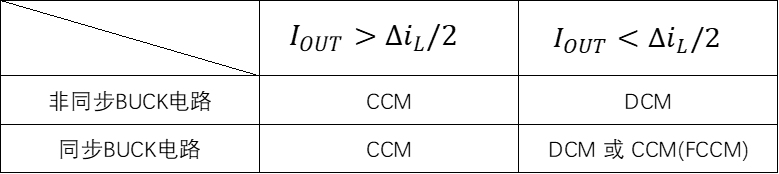

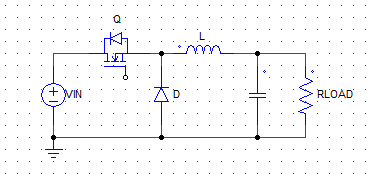

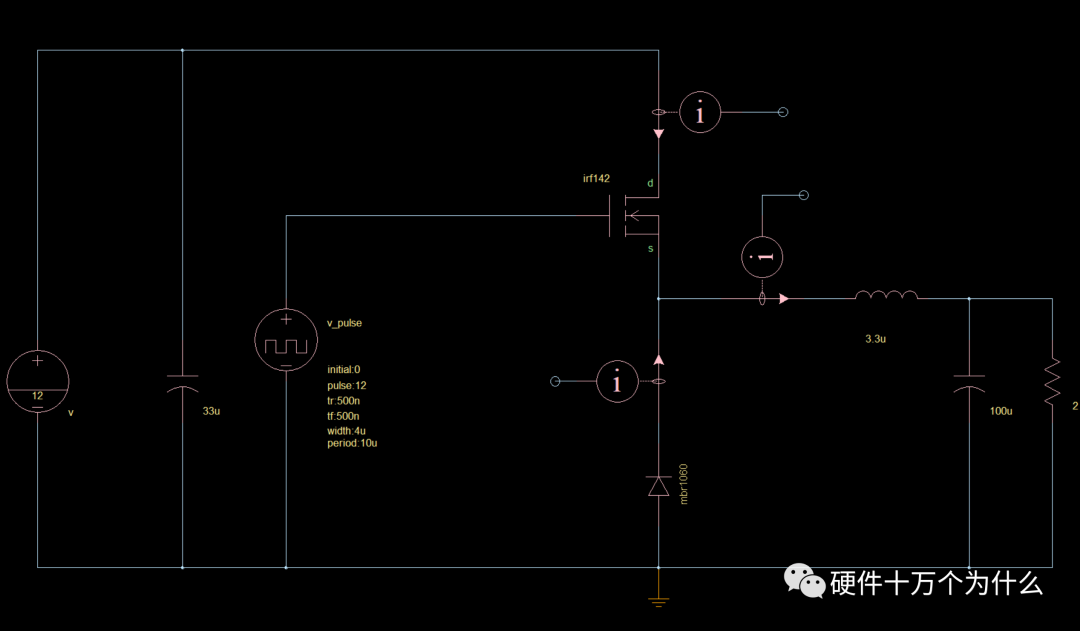

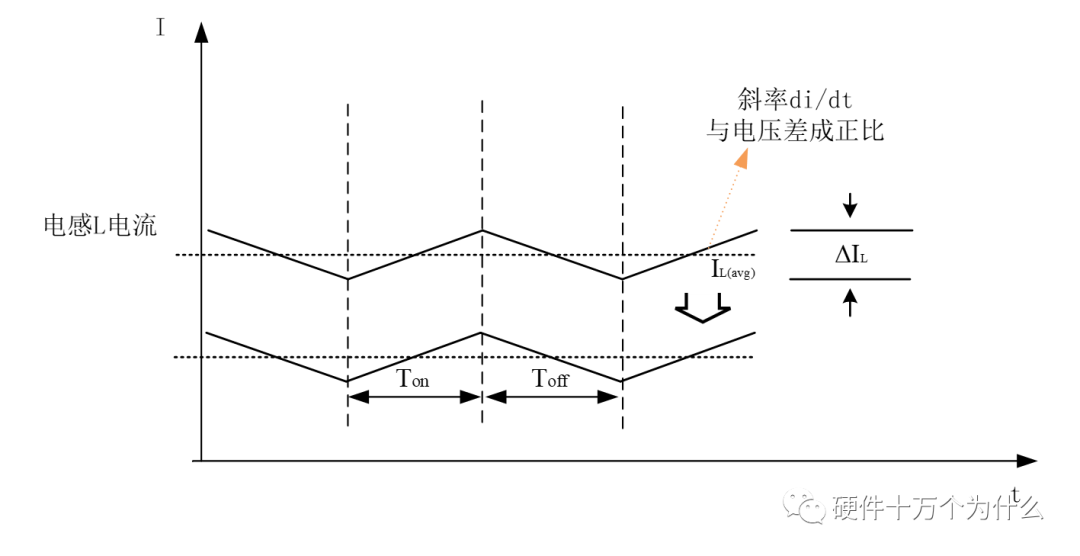

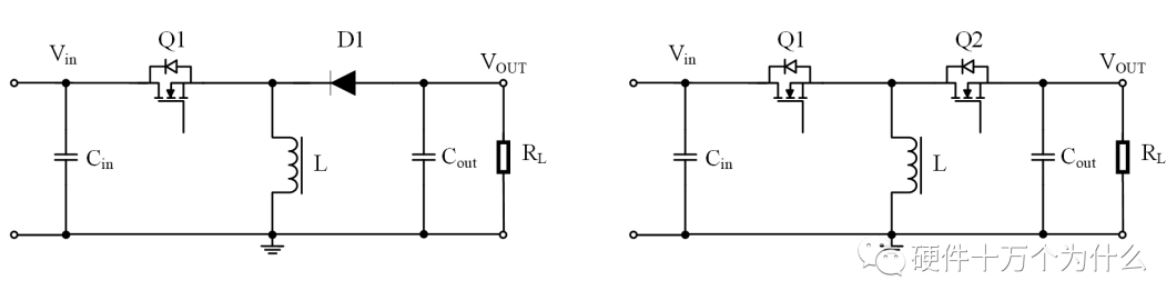

前文BUCK電路CCM與DCM的臨界條件是什么?中介紹了DCM與CCM的臨界條件。此文,介紹輕載條件下DCM與CCM的差異。

2023-12-12 15:37:59 679

679

最新 DCM 廣泛應用于需要更嚴格輸出穩壓的國防和工業應用。這些應用包括無人機、地面車輛、雷達、交通運輸以及工業控制等。DCM ChiP 現已開始提供軍用級版本,其可在零下 -55°C 的溫度下正常工作。

2019-02-18 13:37:34 4068

4068 1.DCM Boost PFC峰值電流控制,峰值電流基準包絡是輸入電壓與輸出補償信號的乘積,只是開通信號不是zcd,是固定頻率開通,頻率固定。2.看到很多論文上寫有DCM Boost PFC的控制方式,但未看到詳細的設計方案和控制芯片,請各位前輩答疑解惑,更期待相關資料的分享。

2021-05-25 21:45:14

喜我正在使用xilinx V5 XC5VSX50T板,我不得不動態更改DCM頻率。我在網上查了一下,文檔說我們可以使用drp模塊(動態重配置端口)來改變DCM的乘法/除法值。我想知道這個DRP模塊

2019-02-26 11:13:07

DCM-8W8P-K87

2023-03-28 13:54:48

嗨,我的項目合成確定,但在奇怪的錯誤實現中斷:地點:1012- 已發現時鐘IOB / DCM組件對未放置在最佳時鐘IOB / DCM站點對。時鐘組件放置在現場。如果將時鐘IO / DCM站點放置

2019-05-10 09:29:00

DCM17W5P1A7NK87

2023-03-23 02:28:08

DCM27W2S0L2

2023-03-23 02:28:11

DCM27W2S0L4

2023-03-23 02:28:13

DCM37S1A0NA197

2023-03-23 02:28:13

在我的項目中已經使用了virtex-5中的dcm_adv,但是有些東西。我不明白。我可以設置M = FF,D = 00到DRP。根據Fout = Fin×(M + 1)/(D + 1),當Fin

2019-02-22 10:36:32

有沒有人使用過DCM_ADV的狀態位(DO [3:0])?我沒有對DCM進行任何重新配置??,但我認為當我丟失輸入時鐘時,看看是否可以使用DCM_ADV狀態位進行通知會很有趣。到目前為止,即使我將

2020-06-01 07:06:05

1,什么是DCM斷續工作模式,CCM連續工作模式。

2021-11-12 07:12:59

延遲鎖相環(DLL)的數目不斷增加,最新的Virtex II器件最多可以提供16個全局時鐘輸入端口和8個數字時鐘管理模塊(DCM)。與全局時鐘資源相關的原語常用的與全局時鐘資源相關的Xilinx器件

2015-03-09 19:48:54

在DCM例化中,使用的VHDL語言,如下所示-- Insert DCM component declaration hereCOMPONENT mydcmPORT(CLKIN_IN

2012-09-20 11:11:32

DCM就是數字時鐘管理單元( Digital Clock Manager)。DCM 當中包含一個 DLL(延遲鎖定電路 Delay-Locked Loop),可以提供對時鐘信號的二倍頻和分頻功能

2018-08-31 09:08:22

嗨, 我在使用DCM時遇到了問題。我的要求實際上是將clk信號的頻率從50MHz降低到20MHz。在10個時鐘脈沖之后,dcm的輸出會顯示出來。我使用的是ISE版本12.1。FPGA系列

2019-01-30 08:59:50

最初,我設置了一個基于xc700a的項目,并在EVM板上完成了實驗。然后我將目標設備更改為xc200a,ISE在執行映射時發生錯誤,似乎DCM上出現故障。我刪除了DCM .xaw和生成的所有文件,并

2019-05-15 09:33:27

嗨,在我的設計中,我有一個dcm實例,在ucf文件中我有類似的東西:INST“U_1 / inst_DCM60M”LOC =“DCM_X2Y1”;我想向這個時鐘引入一個相移,但我想避免觸及源文件

2019-01-21 07:29:31

使用dcm_20Mhz_100Mhz DCM獲得100 MHz模塊。然后,來自第一DCM的CLKFX_OUT輸出用作第二DCM的輸入,以導出三個輸出時鐘clk_int,clk90_int

2020-05-01 15:08:50

嘿所有,我是DCM新手。我試圖給出一個變量。我在測試臺上有這個錯誤。“”實例test_b.uut.dcm.DCM_INST請求的相移= PHASE_SHIFT * PERIOD / 256 = 46

2019-02-27 11:37:37

我的軟件是Vivado 2013.2,設備是xc7k420tffg1156-3。當我使用板載125Mhz LVDS時鐘作為輸入并實例化MMCM時,我發現dcm_locked經常被置為無效

2020-07-16 09:55:28

嗨,當在Planahead 10.1中運行DRC檢查時,我收到此錯誤:位于DCM_ADV_X0Y5的DCM clock_divider_i連接到位于BUFGCTRL_X0Y25的BUFG

2020-06-02 13:49:29

所以這很奇怪而且很間歇。我有一個S6LX45的設計。它使用一個PLL和八個DCM。 8個DCM時鐘輸入來自饋送BUFIO2的GCLK引腳。 BUFIO2分頻器被禁用,DIVCLK輸出進入DCM的時鐘

2019-07-26 13:04:49

嗨,我在synplify下面收到一條錯誤消息。它顯示引腳osc27m_i驅動1個PAD和9個非PAD負載。但實際上它只驅動coregen生成的DCM模塊。 DCM粉絲到其他模塊。我不知道

2019-07-09 12:12:45

項目中用到了了rtthread dcm 數據持久化組件,但是在dcm_cache_save時報mkdir:/data failed但是這個錯誤日志不是本項目的代碼,經確認是dcm接口內部打印的日志

2022-01-27 06:43:20

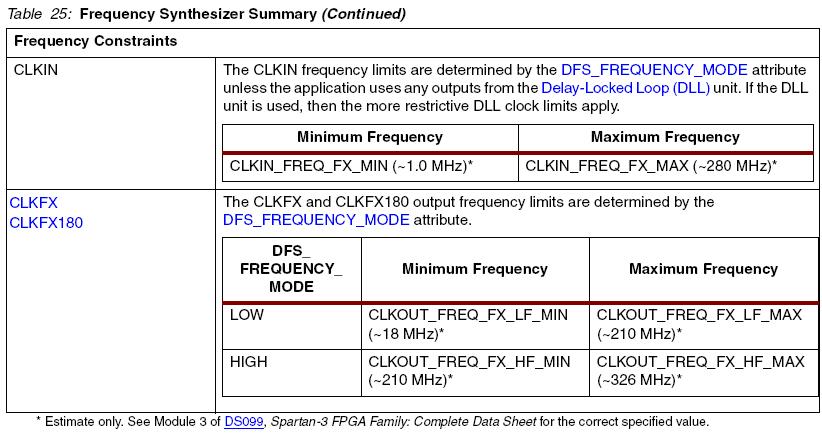

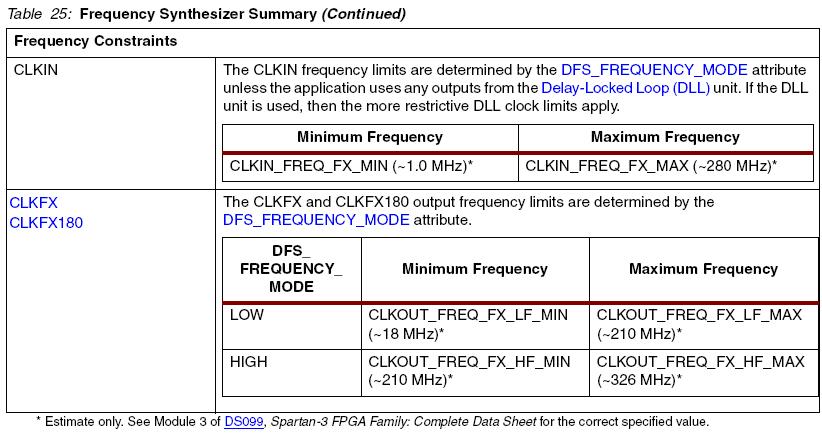

親愛的專家:在我的項目中,我需要使用幾個頻率,例如.2.048M,2.048 * 6M,512k,64k,8k。但我發現DCM限制了輸出頻率。我想知道為什么限制,我該怎么辦。非常感謝

2019-05-10 13:43:50

大家好。BUFG資源和DCM / PLL模塊在許多FPGA線路上使用專用時鐘布線資源。對于SerDes應用,我們使用BUFIO2來獲得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

親愛的先生,以下是來自ISE的錯誤消息。它向我展示了ISE無法將DCM置于設計中。為什么?它來自coregen的74.25Mhz到74.25Mhz pll。謝謝。錯誤:地點:293 - 以下1個組件

2019-08-05 09:10:28

Buck開關型調整器CCM和DCM定義CCM (ContinuousConduction Mode),連續導通模式:在一個開關周期內,電感電流從不會到0。或者說電感從不“復位”,意味著在開關周期

2021-10-29 09:03:35

你好!我是FPGA設計的新手。我想在我的項目中使用DCM,但是,在我執行Xilinx時鐘向導之后,沒有生成響應的vhdl文件。我想知道我該怎么生成這個vhdl文件。我還有其他步驟嗎?謝謝你的考慮

2019-01-15 10:22:23

最近在學習使用xilinx的DCM,想通過輸入10M通過兩級級聯得到30.72M的輸出,用第一個DCM的CLKFX作為第二個DCM的輸入,兩個DCM的M/D(分倍頻系數)分別為12/5和32/25

2013-11-17 21:56:15

大家好..我是xilinx的新手。實際上我需要知道如何使用DCM減少時鐘偏差,我還需要知道如何使用DCM來增加時鐘。謝謝和關心JITHESH A R

2020-06-09 09:09:29

大家好,在我的設計中,我使用DCM并將10Mhz轉換為100Mhz,因此我的設計可以在100Mhz上運行。使用100Mhz,我生成1 Mhz脈沖作為輸出(使用0到100的計數器生成1Mhz)。當我

2019-01-14 12:43:59

需要生成一個低速單端時鐘來測試非常慢的serdes通道(長篇故事為什么它如此低和單端)。我試圖在低頻模式下使用V5 DCM接受2.5MHz的輸入時鐘并產生15MHz-17.5MHz。當我使用GUI

2020-06-15 16:11:09

我想從DCM創建兩個同步時鐘,19.2MHz和38.4MHz。必須使用CLKFX生成其中一個時鐘(比如說38.4MHz時鐘)。由于DCM沒有CLKFX / 2輸出,我必須使用另一個DCM來產生

2019-05-17 13:03:29

大家好, 任何人都可以幫我找到“Zynq(7系列FPGA-XC7Z045FFG900)DCM中DCM的最小相位分辨率?如果有人知道,請幫忙!

2020-08-27 16:17:41

我正在使用3 dcm模塊一個dcm駕駛另外兩個我正在使用核心生成器來生成dcm模塊但在生成程序文件時,它顯示出一些錯誤我嘗試通過添加緩沖區但不起作用來糾正這個錯誤以上來自于谷歌翻譯以下為原文i am

2019-07-15 15:03:19

GPIF通信和50MHz。我還使用DCM(由48MHz時鐘驅動)創建270度移位時鐘,以獲得正確的信號讀/寫成一些靜態SRAM和另一個DCM創建一個20MHz時鐘(從50MHz時鐘)來控制脈沖的產生

2019-07-19 12:49:34

你好在DCM中有一個RESET輸入引腳。我已將RESET引腳指定為分配RESET = ~LOCKED // DCM鎖定,希望這將使RESET從開始起至少保持三個時鐘周期。當我使用這種類型的賦值

2019-06-06 07:23:45

你好,我寫了一個簡單的代碼,由兩個計數器組成,從15開始倒計時。兩個時鐘都按計劃運行。接下來我想在代碼中實現DCM,以便將時鐘信號相移90度并在32MHz下運行它們。我已成功將DCM代碼實現到現有

2019-02-27 10:24:57

嗨,我們在這里有一個Spartan6設備,想知道我們是否可以在DCM保持復位期間使用DCM的狀態輸出。在啟動時,我們希望將DCM保持在重置狀態。順便說一句,我必須說保持DCM的邏輯在另一個時鐘域

2019-05-15 08:34:51

嗨,我已經使用FPGA工作了幾年,但我還沒有意識到是否強制使用DCM復位。我正在開發SP6,ISE14.7上的代碼。到目前為止,我曾經使用下面的電路 - 在VHDL中 - 有或沒有檢查和控制

2019-07-26 14:37:23

你好我希望模擬DCM。用matlab可以嗎?謝謝費薩爾以上來自于谷歌翻譯以下為原文Hi I wish to simulate DCM . Is it possible with matlab ? Thanks Faisal

2019-05-27 10:31:36

嗨,大家好,我總是使用我的設計之一,DCM提供3種不同的時鐘頻率。最近我決定在前一個版本中并行添加一個DCM,現在不再遵守時序約束。這是怎么可能的,因為新的DCM并行而不是關鍵路徑?

2019-07-31 07:31:07

大家好,我正在嘗試實現一個可以處理內部高時鐘頻率的serdes,即。 1.2 GHz,當處于DDR模式時,我到目前為止所做的是將DCM輸入時鐘連接到25 MHz晶振時鐘并將其乘以8以獲得連接到DDR

2019-08-02 06:10:13

(Digital Clock Manager) 數字時鐘管理器主要功能1. 分頻倍頻:DCM可以將[url=]輸入[/url]時鐘進行multiply或者divide,從而得到新的[url=]輸出[/url

2015-09-24 15:04:16

(tx_clk_0),. O(CLKIN_IBUFG));//來自具有LOCKED控制的DCM的輸出BUFGCE BUFGCE_INST_0(.O(tx_clk_1),. CE(LOCKED_OUT),. I

2019-03-25 13:56:30

你好,我使用Spartan 3E。我想要900KHz。所以我使用DCM(核心發生器)產生18MHz,然后除以20.它效果很好,輸出= 900KHz。(50MHz- > DCM +分區

2019-05-17 14:06:21

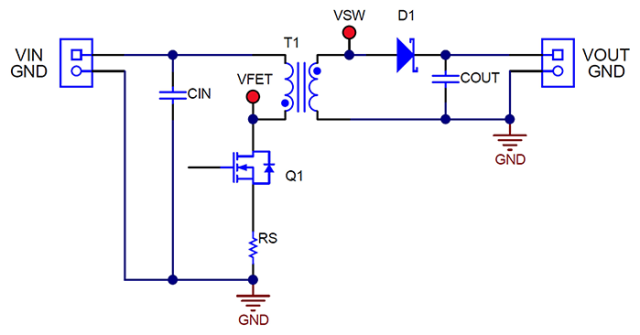

和Boost PFC轉換器一樣,反激式PFC轉換器工作在DCM模式時的固有特點是:輸出電壓調節采用電壓型PWM控制時9穩態占空比Du為常數(即導通時間Ton為常數),輸人電流接近于正弦波。

2009-12-03 11:29:13 74

74 DCM使用手冊

Using Digital Clock Managers (DCMs) in Spartan-3 FPGAs

DCMs integrate advanced clocking

2010-02-09 15:32:42 11

11 為了應用FPGA中內嵌的數字時鐘管理(DCM)模塊建立可靠的系統時鐘。首先對DCM的工作原理進行分析,然后根據DCM的工作原理給出了一種DCM動態重配置的設計方法。DCM動態重配置設計是利

2010-07-28 17:03:52 28

28 反激DCM模式RCD參數計算

這里首先提供幾篇應用手記上的計算方法,然后對其進行改進對比,然后在仿真中對比實際結果。

2009-11-21 11:03:44 4430

4430 DCM主要功能1. 分頻倍頻:DCM可以將輸入時鐘進行multiply或者divide,從而得到新的輸出時鐘。2. 去skew:DCM還可以消除clock的skew,所謂skew就是由于傳輸引起的同一時鐘到達

2010-06-05 11:48:09 7865

7865

DCM概述??? DCM內部是DLL(Delay Lock Loop(?)結構,對時鐘偏移量的調節是通過長的延時線形成的。DCM的參數里有一個PHASESHIFT(相移),可以從0變到255。所以我們可以假設

2010-06-05 12:09:07 2419

2419

DCM600-690V線路保護系列 DCM-611系列低壓智能配電終端主要用于低壓690V以下智能化配電系統的三相或單相配出回路;集合全面的三相電量測量/保護/顯示、數字輸入/輸出與網絡通訊于一身

2011-06-30 13:33:54 547

547 DCM631低壓備自投系列 DCM-631系列低壓備投控制裝置主要用于690V以下低壓電源相互切換場合。不受功率限制,具有接線簡單,穩定可靠的特性。 【DCM-631B】分段備自投裝置(母聯自投) 1、電

2011-06-30 13:05:23 1596

1596 本文介紹了XiLinx FPGA中DCM的結構和相關特性,提出了一種基于XiLinx FPGA的DCM動態重配置的原理方法,并給出了一個具體的實現系統。系統僅通過外部和......

2012-05-25 13:42:50 39

39 DCM3電梯門控制器操作手冊

2016-06-17 17:40:49 0

0 For high-speed differential signal line/general signal line DCM series

2016-08-24 16:30:34 2

2 開關電源CCM及DCM工作模式,感興趣的小伙伴可以看看。

2016-08-30 17:02:35 70

70 DCM:即 Digital Clock Manager 數字時鐘管理,關于DCM的作用: 顧名思義DCM的作用就是管理,掌控時鐘的專用模塊。

2017-02-11 11:30:40 1270

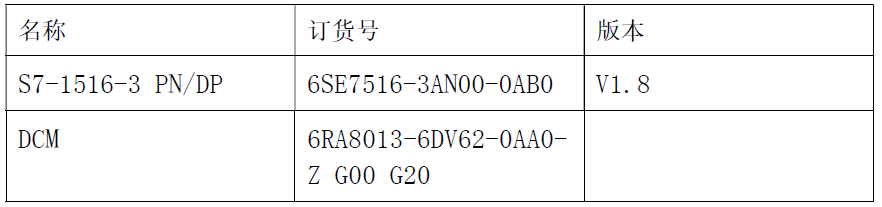

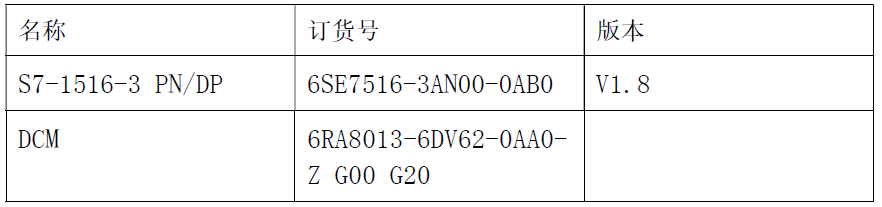

1270 S7-1200通過增加CM 1243-5 DP主站模塊可以與SINAMICS DCM之間通過PROFIBUS DP進行周期通訊,通過調用功能塊DPWR_DAT/DPRD_DAT可實現S7-1200對SINAMICS DCM數據的周期性寫入和讀取。

2017-09-29 16:58:36 9

9 什么叫DCM(Digital Clock Management)? DCM內部是DLL(Delay Lock Loop(?)結構,對時鐘偏移量的調節是通過長的延時線形成的。DCM的參數里有一個PHASESHIFT(相移),可以從0變到255。

2018-07-15 11:28:00 4759

4759 FPGA看上去就是一個四方形。最邊緣是IO Pad了。除去IO Pad,內部還是一個四方形。四個角上各趴著一個DCM。上邊緣和下邊緣中間則各趴著一個全局Buffer的MUX。這樣的好處是四個DCM的輸出可以直接連接到全局Buffer的入口。

2018-05-05 10:38:00 5276

5276

有些FPGA學習者,看Xilinx的Datasheet會注意到Xilinx的FPGA沒有PLL,其實DCM就是時鐘管理單元。 1、DCM概述 DCM內部是DLL(Delay Lock Loop結構

2018-05-25 15:43:53 7884

7884

今天有個小伙伴留言說不明白 CCM 和 DCM 之間的區別,要如何區分這兩種模式,我之前在網絡上有看到一份關于 CCM 和 DCM 這兩者之間的判別及分析的材料,個人感覺講的還是比較到位的,所以

2020-10-29 19:09:59 4814

4814 Buck變換器的DCM穩態關系說明。

2021-06-10 16:29:30 17

17 Boost變換器的CCM/DCM小信號傳遞函數介紹。

2021-06-21 09:30:39 33

33 電流模式DCM反激變換電路的建模和設計(2020空間電源技術學術研討會)-電流模式DCM反激變換電路的建模和設計? ? ? ? ? ? ? ? ? ??

2021-08-31 14:05:38 9

9 反激變換器DCM與CCM模式的優缺點(羅馬仕電源技術偏執狂價格)-反激變換器DCM與CCM模式的優缺點 ? ? ? ? ? ??

2021-08-31 15:18:48 71

71 DCM-633/DCM-635系列電源無擾動快速切換裝置(也稱廠用電快速切換裝置),適用于石化、鋼鐵、冶金、熱電廠或發電廠廠用電系統電源的無擾動切換。

2021-09-02 14:20:04 2225

2225 開關電源CCM和DCM工作模式(通信電源技術 期刊查稿)-開關電源CCM和DCM工作模式,有需要的可以參考!

2021-09-15 17:42:57 44

44 VICOR?DCM?ChiP是隔離穩壓DC-DC的轉換器,能夠 在不穩壓的寬度范圍內輸入運轉,形成隔離輸出。VICOR通過高頻率零電壓開關(ZVS)網絡結構,DCM轉換器為各種各樣輸入電壓范圍提供

2021-11-09 15:55:09 814

814 FPGA-DCM使用詳解(通信電源技術期刊編輯部電話)-該文檔為FPGA-DCM使用詳解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,

2021-09-28 11:22:17 6

6 Xilinx-DCM的使用方法技巧(長城電源技術(深圳有限公司)-該文檔為Xilinx-DCM的使用方法技巧講解文檔,是一份還算不錯的參考文檔,感興趣的可以參考參考,,,,,,,,,,,,,

2021-09-28 12:46:41 12

12 1,什么是DCM斷續工作模式,CCM連續工作模式。

2021-11-07 12:51:00 26

26 項目中用到了了rtthread dcm 數據持久化組件,但是在dcm_cache_save時報mkdir:/data failed但是這個錯誤日志不是本項目的代碼,經確認是dcm接口內部打印的日志

2021-12-03 18:06:08 6

6 ./oschina_soft/dcm2niix.zip

2022-05-30 09:39:59 1

1 前段時間去一家公司面試電源工程師,研發部的老大問了這么一個問題——BUCK的CCM與DCM哪個模式下的環路更容易穩定?

2023-03-17 11:52:43 2880

2880

反激開關電源的連續模式CCM和不連續模式DCM的差異,主要體現在變壓器設計上。這篇文章展開說明DCM將影響反激電源哪些技術參數。

2023-06-25 11:20:39 1506

1506

S7-1500與SINAMICS DCM之間通過 PROFINET IO可進行周期性通訊,通過TIA組態,該通訊可通過調用功能塊“DPWR_DAT/DPRD_DAT”實現S7-1500對 SINAMICS DCM數據的周期性寫入和讀取。

2023-07-11 14:15:39 768

768

簡介:固定頻率升壓轉換器非常適合于以恒流模式驅動LED串。這種轉換器采用不連續導電模式(DCM)工作,能夠有效地用于快速調光操作,提供比采用連續導電模式(CCM)工作的競爭器件更優異的瞬態響應

2023-11-09 08:31:36 0

0 Buck電路的CCM、DCM、BCM模式

2023-11-24 15:42:36 334

334

Boost電路的CCM模式與DCM模式

2023-11-24 15:44:42 2084

2084

反極性Buck-Boost的CCM模式和DCM模式

2023-11-24 15:55:11 547

547

BUCK電路輕載條件下DCM與CCM的差異有哪些? 在討論BUCK電路輕載條件下DCM(不連續導通模式)與CCM(連續導通模式)的差異之前,我們首先要了解BUCK電路的工作原理和兩種不同的工作模式

2024-01-31 18:18:44 537

537

電子發燒友App

電子發燒友App

評論