儀表和測(cè)量系統(tǒng)的設(shè)計(jì)者需要低抖動(dòng)、無(wú)雜散的信號(hào),以提供所需的信噪比 (SNR) 或誤差矢量幅度 (EVM),以滿(mǎn)足日益苛刻的客戶(hù)要求。同時(shí),他們也面臨著減少電路板面積以及設(shè)計(jì)成本和復(fù)雜性的巨大壓力。后者對(duì)于縮短開(kāi)發(fā)時(shí)間以滿(mǎn)足不斷縮小的上市時(shí)間窗口至關(guān)重要。

為了應(yīng)對(duì)眾多的應(yīng)用挑戰(zhàn),工程師們需要將他們的儀器和測(cè)量時(shí)鐘解決方案從傳統(tǒng)的定制分立設(shè)計(jì)過(guò)渡到更加集成的解決方案。實(shí)現(xiàn)這一目標(biāo)的一個(gè)重要步驟是使用一個(gè)集成的平移鎖相環(huán) (PLL)。它允許傳統(tǒng)的壓控振蕩器 (VCO) 信號(hào)進(jìn)行頻率上變頻,同時(shí)充分保持固定的外部本地振蕩器 (LO) 的抖動(dòng)和相位噪聲。

本文討論了平移環(huán)在實(shí)現(xiàn)業(yè)界最低積分相位噪聲方面的作用。通過(guò)舉例,本文介紹了 Analog Devices 的 ADF4401A 平移環(huán)系統(tǒng)級(jí)封裝 (TL SiP),并展示了它如何通過(guò)輸出信號(hào)的亞十飛秒 (fs) 均方根寬帶綜合抖動(dòng)能力和增強(qiáng)隔離度來(lái)滿(mǎn)足性能要求,同時(shí)也滿(mǎn)足了設(shè)計(jì)者的集成度、成本、復(fù)雜性和上市時(shí)間需求。

傳統(tǒng) PLL 與平移環(huán)操作

平移環(huán)的主要目的是產(chǎn)生一個(gè)鎖定在輸入?yún)⒖夹盘?hào)上的輸出信號(hào),與傳統(tǒng)的 PLL 相比,其帶內(nèi)相位噪聲大大降低。

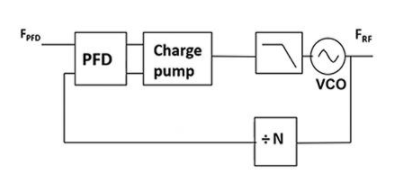

一個(gè)標(biāo)準(zhǔn)的 PLL 由一個(gè)反饋系統(tǒng)組成,包含一個(gè)相位頻率檢測(cè)器 (PFD)、充電泵、低通濾波器 (LPF) 、VCO 和一個(gè)反饋分頻器 N(圖 1)。

圖 1:標(biāo)準(zhǔn) PLL 鎖定到一個(gè)較低頻率 (FPFD) 參考,并產(chǎn)生一個(gè)輸出頻率 (FRF)。(圖片來(lái)源:Bonnie Baker)

PFD 對(duì)輸入?yún)⒖夹盘?hào)的相位和反饋信號(hào)的相位進(jìn)行比較,并產(chǎn)生一系列與它們之間的相位誤差成比例的脈沖。充電泵接收 PFD 脈沖并將其轉(zhuǎn)換為電流源或電流阱脈沖,進(jìn)而調(diào)整 VCO 的頻率,使其上升或下降。LPF 去除所有脈沖的高頻能量,并將其轉(zhuǎn)換為 VCO 可以使用的電壓。VCO 的輸出信號(hào)通過(guò) N 分頻器反饋給 PFD 塊,完成這個(gè)環(huán)。

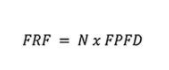

圖 1 的頻率傳遞函數(shù)是用公式 1 計(jì)算的。

等式 1

其中 FRF 是輸出頻率

N 是反饋分壓器的比率(可以是整數(shù)或分?jǐn)?shù))。

FPFD 是 PFD 頻率

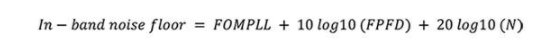

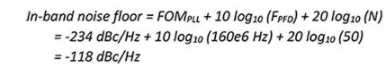

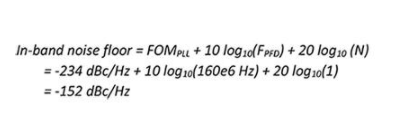

圖 1 的帶內(nèi)噪聲基底是用公式 2 計(jì)算的。

等式 2

其中 FOMPLL 是 PLL 的帶內(nèi)相位噪聲基底品質(zhì)因數(shù) (FOM)

考慮一個(gè)實(shí)例,帶內(nèi)相位噪聲基底 FOM 為 -234 分貝/赫茲 (dB/Hz);PFD 頻率 (FPFD) 為 160 兆赫茲 (MHz),輸出頻率 (FRF) 為 8 千兆赫茲 (GHz)。

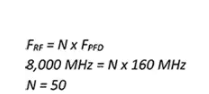

對(duì)于這個(gè)系統(tǒng),公式 1 用來(lái)計(jì)算 N 的值:

公式 2 用于計(jì)算帶內(nèi)噪聲基底:

在上面的計(jì)算中,N 分頻器對(duì)整個(gè)帶內(nèi)噪聲基底的貢獻(xiàn)很大,有 20log10 (50) ,相當(dāng)于 34dB。N 值較小會(huì)降低帶內(nèi)噪聲基底;但是,它也會(huì)降低輸出頻率。那么,我們?nèi)绾萎a(chǎn)生一個(gè)高輸出頻率并保持較低的環(huán)路增益 (N)?

圖 2:對(duì)于本例中的標(biāo)準(zhǔn) PLL,與 N=1 的黃色下圖相比,反饋分壓器的噪聲 (20log10 (N)) 比帶內(nèi)噪聲高出 34dB。(圖片來(lái)源:Bonnie Baker)

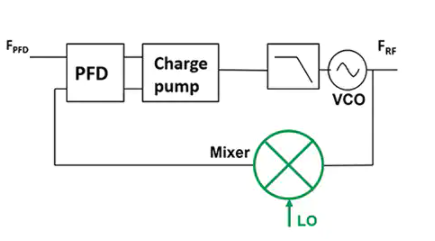

解決這個(gè)問(wèn)題的辦法是用一個(gè)下變頻混合級(jí)取代 N 分頻器(圖 3)。

圖 3:平移環(huán)使用混頻器將 VCO 頻率向下轉(zhuǎn)換為 PFD 頻率,而不是使用傳統(tǒng)的反饋分頻器。(圖片來(lái)源:Bonnie Baker)

在圖 3 中,混頻器取代了反饋 N 分頻器,導(dǎo)致回路增益等于 1 (N=1)。這種操作將大大減少反饋回路對(duì)帶內(nèi)噪聲基底的影響。對(duì)于帶內(nèi)噪聲的計(jì)算,N 的值現(xiàn)在等于 1。使用公式2,修改后的系統(tǒng)的帶內(nèi)噪聲基底如下。:

新的帶內(nèi)噪聲顯示出 34dBc/Hz 的改善。

在圖 3 中,混頻器依賴(lài)于一個(gè)極低噪聲 LO,稱(chēng)為偏移 LO。FLO ± FRF 必須等于 FPFD 以實(shí)現(xiàn)鎖定。

在平移環(huán)結(jié)構(gòu)中,偏移 LO 的相位噪聲對(duì)于在射頻輸出端實(shí)現(xiàn)最佳性能非常重要。由于這個(gè)原因,工程師們通常會(huì)在壓控表面聲波 (SAW),或振蕩器 (VCSO),或梳狀發(fā)生器,或介質(zhì)諧振器 (DRO) 的基礎(chǔ)上設(shè)計(jì)一個(gè)偏移 LO。注意:如需獲得偏移 LO 的設(shè)計(jì)支持,請(qǐng)聯(lián)系 Analog Devices。

平移環(huán)的挑戰(zhàn)

傳統(tǒng)上,低噪聲平移環(huán)的設(shè)計(jì)涉及眾多電路塊的實(shí)現(xiàn),導(dǎo)致設(shè)計(jì)復(fù)雜,通常體積龐大,靈活性有限。此外,整個(gè)電路必須針對(duì)目標(biāo)操作進(jìn)行驗(yàn)證和特征化。例如,一個(gè)主要的設(shè)計(jì)關(guān)注點(diǎn)是對(duì)射頻輸出信號(hào)的 LO 泄漏(LO 與射頻隔離)。這對(duì)工程師來(lái)說(shuō)是一個(gè)需要解決的重大挑戰(zhàn)。對(duì)于傳統(tǒng)的設(shè)計(jì),工程師們通常會(huì)進(jìn)行多次設(shè)計(jì)迭代,以實(shí)現(xiàn)優(yōu)化的性能和合適的隔離。

圖 3 顯示了 ADF4401A 是如何整合主要電路塊以提供一個(gè)完全特征化的解決方案,并消除了傳統(tǒng)上與平移環(huán)設(shè)計(jì)中的性能和隔離有關(guān)的困難領(lǐng)域。這種可編程的解決方案能夠讓工程師在第一次努力時(shí)就實(shí)現(xiàn)優(yōu)化的性能,并加快上市速度。

評(píng)估 ADF4401A

ADF4401A 旨在幫助工程師縮短高性能儀器上市所需的時(shí)間,使用的頻率生成解決方案的射頻帶寬為 62.5 MHz 至 8 GHz。通過(guò)使用下變頻混頻器,ADF4401A 具有非常低的帶內(nèi)噪聲,在 100 Hz 到 100 MHz 的寬帶抖動(dòng)約為 9 飛秒 (fs)。ADF4401A 內(nèi)部的設(shè)計(jì)和布局技術(shù)使之典型無(wú)雜散動(dòng)態(tài)范圍達(dá)到 90 dBc。與傳統(tǒng)的分立設(shè)計(jì)相比,18 x 18 x 2.018 毫米 (mm) 的封裝尺寸大大減少了電路板空間。

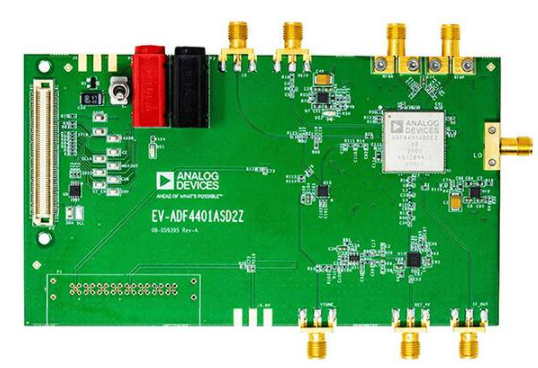

為了評(píng)估該器件的性能,設(shè)計(jì)人員可以使用 EV-ADF4401ASD2Z 評(píng)估板(圖 4)。該板包括一個(gè)完整的平移環(huán),包括一個(gè)外部 PFD (HMC3716)、一個(gè)有源濾波器 (LT6200) 和一個(gè)復(fù)用器 (ADG1609)。

圖 4:用于 ADF4401A 平移環(huán)模塊的 EV-ADF4401ASD2Z 評(píng)估板包括一個(gè)外部 PFD、一個(gè) USB 接口和穩(wěn)壓器。(圖片來(lái)源:Analog Devices)

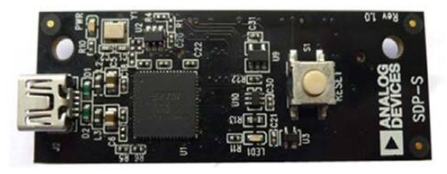

EV-ADF4401ASD2Z 包括帶有集成 VCO 的 ADF4401A TL SiP、一個(gè)環(huán)路濾波器 (5MHz)、一個(gè) PFD、一個(gè) USB 接口和電壓穩(wěn)壓器。此外,EV-ADF4401ASD2Z 需要 EVAL-SDP-CS1Z (SDP-S) 系統(tǒng)演示平臺(tái) (SDP)(串行)控制器板(圖 5)。該板提供了一個(gè)從 PC 到 EV-ADF4401ASD2Z 的 USB 連接,因此可以對(duì)其進(jìn)行編程。EV-ADF4401ASD2Z 套件中不提供該控制器板。

圖 5:需要 EVAL-SDP-CS1Z(或 SDP-S)控制器板來(lái)提供從 EV-ADF4401ASD2Z 到 PC 的 USB 連接,以便進(jìn)行編程。(圖片來(lái)源:Analog Devices)

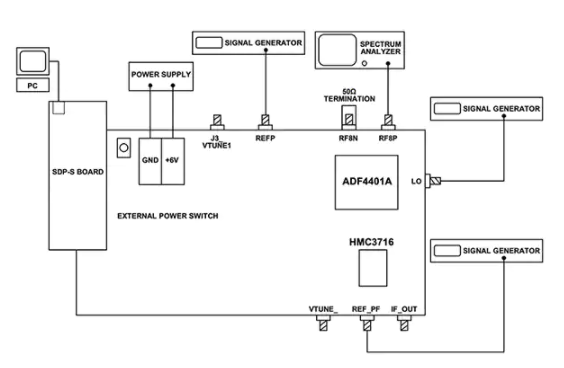

圖 6 顯示了 EV-ADF4401ASD2Z 系統(tǒng)的物理連接。相關(guān)分析 | 控制 | 評(píng)估 (ACE) 軟件控制著 TL SiP 功能。電源來(lái)自外部的 6 伏電源。

圖 6:EV-ADF4401ASD2Z 安裝圖顯示了評(píng)估 ADF4401A 所需的設(shè)備和連接,包括 SDP-S 控制板、PC、電源、信號(hào)發(fā)生器和頻譜分析儀。(圖片來(lái)源:Analog Devices)

建議與該評(píng)估板一起使用的設(shè)備包括一臺(tái) Windows PC、一臺(tái)頻譜分析儀或信號(hào)源分析儀,以及三個(gè)信號(hào)發(fā)生器。

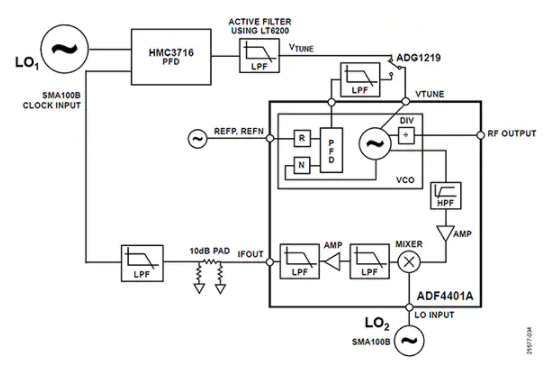

EV-ADF4401ASD2Z 的方框圖顯示了 ADF4401A 模塊,以及 Analog Devices 的 HMC3716 PFD、LT6200 運(yùn)算放大器和 ADG1219 SPDT 開(kāi)關(guān)(圖 7)。

圖 7:EV-ADF4401ASD2Z 評(píng)估板框圖顯示了支持 AD4401A 平移環(huán)的關(guān)鍵部件。(圖片來(lái)源:Analog Devices)

使用能夠在高頻下工作的 PFD 是至關(guān)重要的,因?yàn)檫@可以最大限度地減少對(duì)分頻器的需求,分頻器會(huì)降低帶內(nèi)噪聲響應(yīng)。Analog Devices 的 HMC3716 的 1.3 GHz 相位比較頻率能力使之非常適合用于 ADF4401A 的中頻范圍。這種電路能夠同時(shí)比較頻率和相位,因此不需要額外的電路來(lái)將頻率引導(dǎo)到預(yù)定的輸出頻率。HMC3716 成為外部 PFD,完成偏移環(huán)。HMC3716 的高頻工作范圍和超低的相位噪聲基底使其有可能設(shè)計(jì)出寬頻帶環(huán)路濾波器。

在圖 7 中,具有 LPF 配置的 LT6200 運(yùn)算放大器衰減了高頻尖峰,而 ADG1219 開(kāi)關(guān)完成了系統(tǒng)的平移環(huán)。

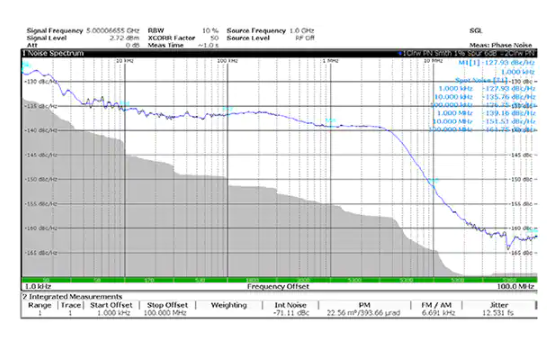

圖 8 所示為 EV-ADF4401ASD2Z 評(píng)估板產(chǎn)生的帶內(nèi)噪聲圖和抖動(dòng)測(cè)量。

圖 8:5 GHz 輸出的單邊帶相位噪聲,外部 HMC3716 參考為 500MHz,外部 LO 為 4.5GHz。(圖片來(lái)源:Analog Devices)

在圖 8 中,LO2 和 HMC3716 輸入是一個(gè) SMA100B 射頻和微波信號(hào)發(fā)生器。該評(píng)估板的 LO2 帶內(nèi)噪聲約為 -135 dBc/Hz,在最高 300kHz 的低偏移量下是很明顯的。LO2、ADF4401A 模塊、HMC3716 PFD 和環(huán)路濾波器帶來(lái)的帶內(nèi)噪聲約為 -140 dBc/Hz。內(nèi)部相位噪聲出現(xiàn)在 5MHz 和 50MHz 之間,該評(píng)估板的相位噪聲基底大約為 -160dBc/Hz。這些因素加在一起,總計(jì)產(chǎn)生 12.53 fs 的 rms 抖動(dòng)。

結(jié)語(yǔ)

高速儀器系統(tǒng)需要極低抖動(dòng)的時(shí)鐘,以確保輸出數(shù)據(jù)不受影響。工程師們面臨的挑戰(zhàn)是,找到能夠構(gòu)建高速千兆赫時(shí)鐘系統(tǒng)的合適設(shè)備。ADF4401A 平移環(huán)大大簡(jiǎn)化了構(gòu)建時(shí)鐘系統(tǒng)的器件選擇,它提供了一個(gè)緊湊的模塊,確保了在更高頻率下的低抖動(dòng),同時(shí)也減少了電路板空間、成本和上市所需時(shí)間。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論