摘要

本文首先主要介紹了TI 的新一代時鐘產(chǎn)品LMK0480X 的holdover 功能和指標,以及在新一代的無線C-RAN 網(wǎng)絡(luò)中的應(yīng)用。通過對LMK0480X holdover 的指標分析,證明LMK04808 完全滿足通信網(wǎng)絡(luò)的時鐘倒換的需求。

1、Holdover 功能的引入

在目前的通信系統(tǒng)當中,無論是有線還是無線,都是一個時鐘同步系統(tǒng)。參考時鐘從宿源端通過網(wǎng)絡(luò)傳遞給系統(tǒng)中的各個設(shè)備;為了提高系統(tǒng)中各個設(shè)備的穩(wěn)定性,同時為了提高系統(tǒng)中設(shè)備對于不同應(yīng)用的靈活性,一般都有超過一路的參考時鐘輸入到設(shè)備中。當設(shè)備中的時鐘單元在這些輸入的參考時鐘中切換時,要使時鐘單元的輸出要保持性能和時鐘的穩(wěn)定性,這就要求時鐘電路具備holdover 功能,支持參考時鐘hitless 切換。

以往的模擬時鐘電路中所謂的holdover 功能,只是當發(fā)生時鐘切換時,鑒相器的電荷泵被強制輸出到VCC/2;但某些情況下,時鐘鎖定時的電荷泵電壓和VCC/2 差別比較大,這樣在時鐘切換的過程中,輸出時鐘的跳變可能會超出系統(tǒng)所能允許的范圍,造成系統(tǒng)的時序紊亂。

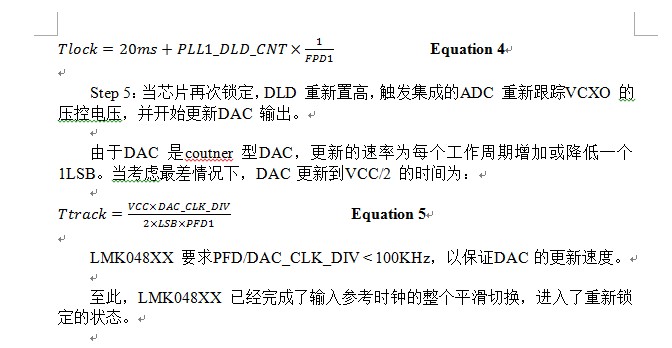

在TI 最新的時鐘去抖芯片LMK048XX 系列中,增加了電荷泵電壓跟蹤電路;這個電路實時采樣電荷本電壓并且保存更新到芯片的集成DAC 上;當芯片在輸入時鐘切換的過程中,電荷泵電壓輸出切換到DAC 的輸出上,這樣在參考時鐘切換前后,壓控電壓變化非常微小,保證了系統(tǒng)時鐘的穩(wěn)定性。

LMK0480XX 系列時鐘器件的Holdover 功能是真正的hitless switch,下面的章節(jié)將詳細介紹holdover 的整個過程及相關(guān)的指標。

2、LMK0480x 系列產(chǎn)品holdover 功能介紹

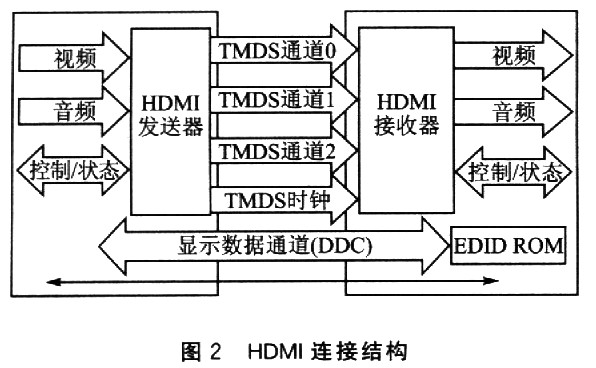

LMK048xx 系列是TI 推出的新一代時鐘去抖芯片,采用了兩級鎖相環(huán)級聯(lián)的架構(gòu)。第一級鎖相環(huán),利用窄帶環(huán)路濾波器和外部VCXO,主要完成對輸入?yún)⒖紩r鐘去抖;第二級環(huán)路濾波器主要利用高性能的內(nèi)部鎖相環(huán)生成系統(tǒng)需要的各種時鐘。上文提到的Holdover 功能是第一級鎖相環(huán)具備的功能。

Figure 1 LMK0480X holdover 架構(gòu)

上圖是LMK048XX holdover 的功能框圖。其中,CLKin0 和CLKin1 分別是來自網(wǎng)絡(luò)的兩個參考時鐘,選擇一路作為時鐘芯片以及系統(tǒng)的主時鐘。當網(wǎng)絡(luò)設(shè)備發(fā)生主從倒換或者業(yè)務(wù)切換時,時鐘芯片的參考時鐘也隨之切換。觸發(fā)參考時鐘切換的條件可以為a. PLL1 的DLD 狀態(tài),b.外部管腳的硬件控制,c. 內(nèi)部寄存器控制。下面的討論我們假定切換是以PLL1 的DLD 狀態(tài)觸發(fā)的。

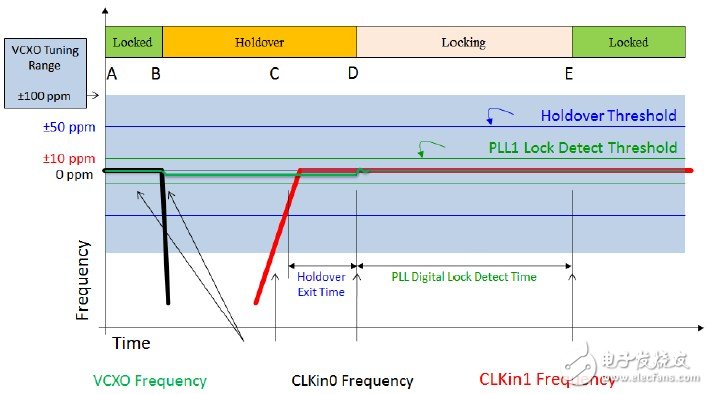

當LMK048XX holdover 功能使能時,一個完整的參考切換過程如下圖所示,主要分為如下幾個步驟:

Figure 2 LMK0480X holdover 流程

Step1: PLL1 正常鎖定在CLKin0, PLL1 DLD 為高;LMK048XX 集成的counter ADC 跟蹤VCXO 的壓控電壓并更新集成的counter DAC, 更新的速率為PDF/DAC_CLK_DIV,每個更新周期內(nèi)上升或下降一個LSB。

Step2:當CLKin0 由于某些原因丟失或出現(xiàn)比較大的頻率誤差時,PLL1 的鑒相誤差超過鎖定窗口(PLL1_WND_SIZE),DLD 為低;DLD 為低時,ADC 停止跟蹤壓控電壓及更新DAC,DAC 的輸出保持在最后鎖定時的壓控電壓;DLD 拉低同時觸發(fā)LMK048XX 進入holdover 狀態(tài),內(nèi)部開關(guān)切換VCXO 的壓控電壓到DAC 輸出。

3、Holdover 功能的參數(shù)設(shè)置

3.1 Holdover 功能的配置

使用holdover 功能,必須首先Holdover_Mode = Enable;在絕大多數(shù)的應(yīng)用場景,內(nèi)部的DAC 輸出需要跟蹤 VCXO Vtune 電壓,所以EN_Track = 1; 并且跟蹤電路的正常工作需要在PLL1 鎖定之前設(shè)置EN_Track =1;否則,當PLL1 鎖定之后,設(shè)置EN_Track=1 并不能使DAC 輸出跟蹤Vtune 電壓。

DAC 的電壓也可以是手動設(shè)置,此時需要EN_MAN_DAC = 1;同時LMK0480X 提供了兩個寄存器,DAC_Low_Trip 和DAC_High_Trip, 用于設(shè)置DAC 輸出電壓的上下門限。

觸發(fā)芯片進入holdover 狀態(tài),可以是以下任一條件:

? Force_holdover = 1;

? PLL1 失鎖 或DLD =0;

? Vtune 或DAC 跟蹤電壓超出DAC_Low_Trip 和DAC_High_Trip;

在使用的過程中,需要根據(jù)不同的系統(tǒng)需求選擇合適的holdover 觸發(fā)條件;從目前來看,大部分應(yīng)用場景選擇PLL1 失鎖或DLD = 0 觸發(fā)holdvoer 狀態(tài)。

最后還需要配置Holdover_DLD_CNT 以及DAC_CLK_DIV,這兩個寄存器的功能在第二章中已經(jīng)介紹。

3.2 Holdover 參數(shù)配置的注意事項

當系統(tǒng)上電開始工作是, CLKin0 或CLKin1 來自光纖的恢復(fù)時鐘, 性能并不穩(wěn)定。若Holdover_DLD_CNT 和PLL1_DLD_CNT 值設(shè)置比較小,LMK0480X 很容易進入鎖定狀態(tài),本地時鐘VCXO鎖定CLKin 輸入信號,同時DAC 開始跟蹤VCXO 的Vtune 電壓;但前面提到,通常CLKin 在剛開始工作時并不穩(wěn)定,某些情況下CLKin 的輸入可能漂出VCXO 的頻率調(diào)整范圍,導(dǎo)致器件重新失鎖并進入holdover 狀態(tài),并且此時holdover 輸出電壓可能為3.3V 或0V;在這之后,CLKin 的頻率漸趨穩(wěn)定,但CLKin 的頻率和VCXO(Vtune = 0V 或 3.3V)的頻率不能滿足退出holdover 的條件,出現(xiàn)了LMK0480X 無法退出holdover 的情況。如下圖PartA 部分所示。因此,在holdover 功能電路設(shè)計中,通常適當?shù)脑黾覲LL1_DLD_CNT 和HOLDOVER_DLD_CNT 的值,使得退出和鎖定的判決條件更為苛刻,只有當CLKin 穩(wěn)定時,才會退出holdover,進入鎖定。如下圖PartB 部分所示。

另一方面,在第二章中分析得到,當PLL1_DLD_CNT 和HOLDOVER_DLD_CNT 的值過大時,會影響時鐘切換的整個時長,所以在應(yīng)用中,PLL1_DLD_CNT 和HOLDOVER_DLD_CNT 值得選取,是一個折中的過程;同時也可以通過芯片的配置流程對這個問題加以改善。

Figure 3 上電時參考時鐘和holdover 關(guān)系

4、Holdover 功能在無線RRU 中應(yīng)用的需求分析

4.1 C-RAN 網(wǎng)絡(luò)架構(gòu)的優(yōu)勢

隨著電信業(yè)務(wù)的蓬勃發(fā)展與用戶行為的不斷變化,無線接入網(wǎng)正面臨著前所未有的挑戰(zhàn):大量站點導(dǎo)致高能耗,網(wǎng)絡(luò)的資本支出與運維成本逐年增高;站點資源難以獲取;復(fù)雜的網(wǎng)絡(luò)環(huán)境致使無線覆蓋質(zhì)量不高,潮汐效應(yīng)導(dǎo)致部分基站利用率低下……面對技術(shù)、成本、資源和安全等多個問題 ,2010 年4 月,中國移動提出新一代綠色無線接入網(wǎng)架構(gòu)C-RAN。

Figure 4 RAN 網(wǎng)絡(luò)架構(gòu)

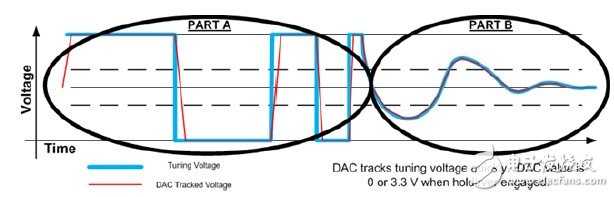

C-RAN 架構(gòu)是在分布式基站基礎(chǔ)上的進一步創(chuàng)新,通過基帶集中處理(Centralized)、協(xié)作式無線電技術(shù)(Collaborative)以及實時云架構(gòu)(Cloud),實現(xiàn)網(wǎng)絡(luò)資源共享以及動態(tài)的網(wǎng)絡(luò)負載均衡,實現(xiàn)無線接入網(wǎng)的綠色高效(Clean)并面向未來平滑演進,提供更大的帶寬和更靈活的多標準運營支持,如圖4 所示。

4.2 C-RAN 網(wǎng)絡(luò)中環(huán)形倒換對時鐘指標的要求

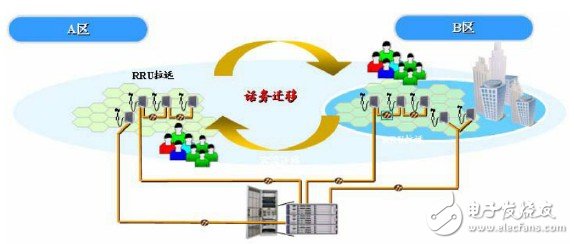

在C-RAN 組網(wǎng)中,如圖5,基帶集中RRU 拉遠需要光纖互聯(lián),采用多級級聯(lián)和環(huán)形組網(wǎng),一方面各站點RRU 通過光纖接入環(huán)采用環(huán)形組網(wǎng)方式接入BBU,有效節(jié)省光纖資源,另一方面這種組網(wǎng)結(jié)構(gòu)支持環(huán)網(wǎng)倒換保護功能,充分保證網(wǎng)絡(luò)安全和可靠性,即當任何一段光纖意外損壞或者鏈路中任一個RRU損壞, 會自動倒換到反向鏈路, 從而不會影響上級或下級RRU 的正常工作。

Figure 5 C-RAN 環(huán)形布網(wǎng)

RRU 級聯(lián)系統(tǒng)在正常工作中,每個RRU 的系統(tǒng)參考時鐘來自上一級RRU;當RRU 在完成環(huán)網(wǎng)倒換過程中, RRU 的系統(tǒng)參考時鐘的來源也會切換,從切換前的來自上一級RRU 切換到另一側(cè)的RRU;在整個切換的過程中,系統(tǒng)時鐘必須保持一定的穩(wěn)定度和準確度,從而保證現(xiàn)有用戶不掉話,保證通話MOS和數(shù)據(jù)業(yè)務(wù)吞吐率。

以TD-LTE 系統(tǒng)為例,基站具體的時鐘需求如下:

不同基站間空口同步信號相對時間誤差小于+/-1.5us;

基站空口載波頻率穩(wěn)定度優(yōu)于+/-0.05ppm;

基站輸入抖動容限不小于±200ns;

BBU+多級RRU 串連級聯(lián)時空口相對傳輸輸出接口的時間精度小于±300ns;

在時鐘切換的過程中,需要確保數(shù)字部分的FIFO 不要溢出,同時也要考慮頻率誤差帶來的空口同步誤差,小于系統(tǒng)的要求+/-300ns。

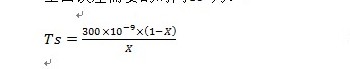

假定在切換過程中,頻率誤差為X*10e6 ppm, 每幀長度為Tf,則造成300ns 的空口誤差需要的時間Ts 為:

Equation 6

Equation 6

假定X = 6, Tf = 0.01 S, 則Ts = 0.3 S, 即整個切換過程必須在0.3 S 內(nèi)完成,否則頻率誤差可能造成空口的同步誤差,造成TD 系統(tǒng)的收發(fā)切換紊亂。同理,假設(shè)FIFO 的工作時鐘是Fclk,當FIFO 深度為1 時,造成一個碼片誤差的時間Te 為:

Equation 7

Equation 7

當FIFO = 491.52MHz 時,Te = 2mS. 可以看到這個要求是相當苛刻的;但這個問題可以通過增加FIFO 的深度來解決。當FIFO 深度為1000 時,Te = 2 S;但繼續(xù)增加FIFO 深度已經(jīng)沒有意義,因為瓶頸已經(jīng)變成了Ts。

通過同時可以看到,當提高切換過程中的頻率穩(wěn)定度,降低頻率誤差,可以延長切換過程需要的時間;反之,如果切換過程中頻率度很差,則必須快速完成切換,否則很容易造成客戶斷鏈掉話。

根據(jù)第二章中介紹的LMK048XX 系列的介紹的holdover 功能,假定PLL1_WND_SIZE = 40nS, FPD1 =1.024MHz, Holdover_DLD_CNT = 4096,PLL1_DLD_CNT = 4096,DAC_CLK_DIV = 32,在整個切換過程中,總共用時為0.053(Texit _ holdover ) + 0.024(Tlock ) +0.016(Ttrack ) = 0.093s, 在切換過程中輸出時鐘的精度保持在0.5ppm。根據(jù)前面討論的C-RAN 系統(tǒng)需求(切換時間《0.3s,頻率精度《1ppm),LMK048XX 完全可以滿足環(huán)形網(wǎng)絡(luò)系統(tǒng)在倒換情況下的時鐘精度需求。

5、總結(jié)

本文主要介紹了LMK048XX 系列時鐘的holdover 功能。通過對C-RAN 系統(tǒng)時鐘切換需求的舉例分析,證明LMK0480XX 的holdover 功能真正的實現(xiàn)了hitless switch,完全可以滿足通信系統(tǒng)的時鐘切換功能,大大簡化了通信系統(tǒng)的時鐘單元的設(shè)計難度和成本。

6、參考資料

1. LMK04800 Datasheet

電子發(fā)燒友App

電子發(fā)燒友App

評論