本文主要帶領(lǐng)大家來了解一下分頻器的計算和調(diào)整,首先來了解一下分頻器原理及是分頻點(diǎn),其次詳細(xì)了解分頻器計算的順序以及調(diào)整方法。

2018-05-29 09:59:00 120326

120326

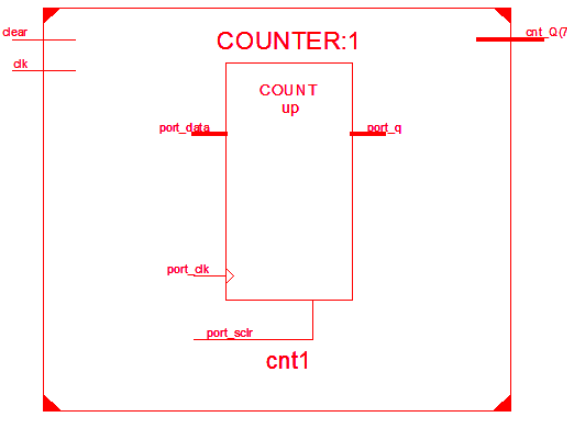

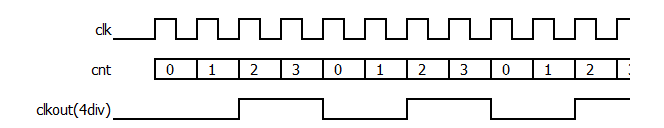

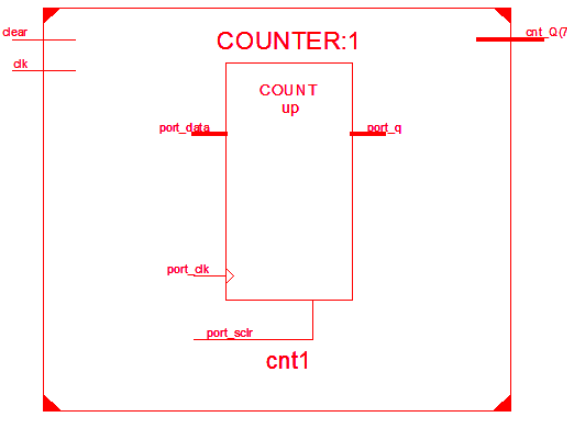

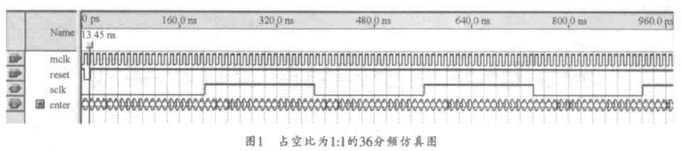

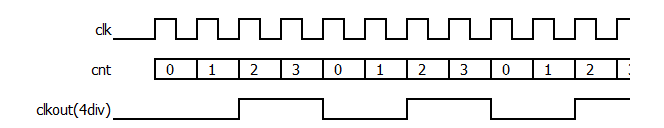

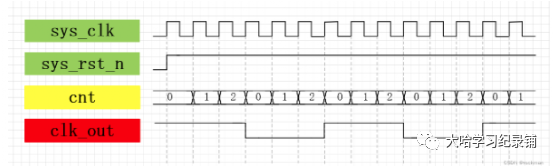

前言: 偶數(shù)分頻容易得到:N倍偶數(shù)分頻,可以通過由待分頻的時鐘觸發(fā)計數(shù)器計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,輸出時鐘進(jìn)行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,使得下一個時鐘從零開始計數(shù)。以此循環(huán)下去

2020-12-28 15:49:20 2620

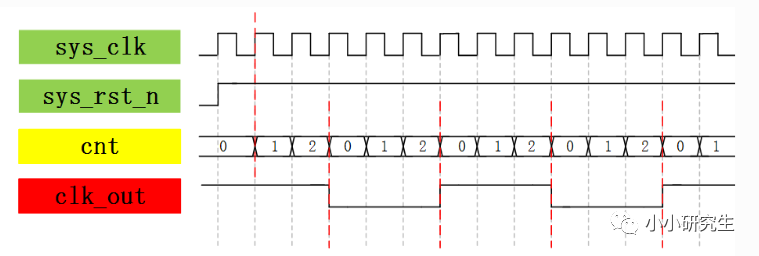

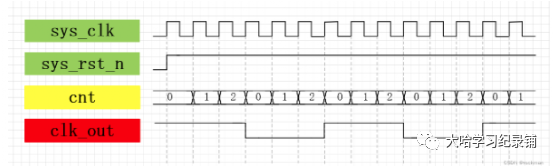

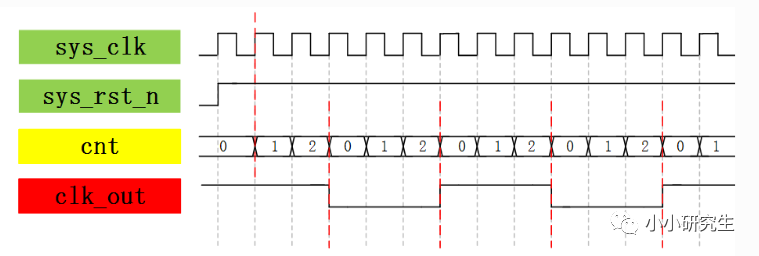

2620 假設(shè)時鐘分頻是N,則設(shè)置一個計數(shù)器,計數(shù)長度是N(即從0計數(shù)到N-1),然后在計數(shù)器為計數(shù)到(N-1)/2的時候,翻轉(zhuǎn)一下分頻時鐘信號。

2020-11-06 13:59:47 9658

9658

分頻就是用同一個時鐘信號通過一定的電路結(jié)構(gòu)轉(zhuǎn)變成不同頻率的時鐘信號。

2024-03-06 17:13:32 384

384

時鐘分頻電路實現(xiàn)精講

2013-04-18 12:07:20

時鐘分頻電路精講

2013-07-11 09:37:52

時鐘樹寄存器配置詳解

2021-08-12 06:06:13

詳解STM32的時鐘系統(tǒng)STM32的時鐘樹時鐘信號推動單片機(jī)內(nèi)各個部分執(zhí)行相應(yīng)的指令,時鐘就像人的心跳一樣。 STM32本身十分復(fù)雜,外設(shè)非常多,任何外設(shè)都需要時鐘才能啟動,但并不是所有的外設(shè)都需要

2021-08-19 06:33:34

如何配置模塊的時鐘分頻?

2024-02-05 06:01:59

CC3200 工作在定時器捕獲模式下,如何進(jìn)行定時器時鐘分頻。

當(dāng)我運(yùn)行SDK中 timer_cc例程時加入

MAP_TimerPrescaleSet(TIMERA2_BASE,TIMER_A,80);//需要1M Hz時鐘

捕獲的數(shù)據(jù)始終是80 MHz時鐘的數(shù)據(jù)。

2018-06-23 07:06:54

在查閱CPLD設(shè)計的相關(guān)資料的時候,看到有文章說過當(dāng)時鐘晶振超過20M的時候,最好采用流水線操作現(xiàn)在我用的EPM240T100C5才用的是50M的晶振那么我可不可以將時鐘先分頻,然后將分頻后的時鐘

2013-04-25 09:39:35

clk_out_div6;//6分頻時鐘輸出;reg [1:0] cnt;//計數(shù)寄存器regclk_out_div6;//時鐘輸出寄存器 always@(posedge clk or negedge rest_n)beginif(!rest_n) //復(fù)位信號 begincnt

2016-03-30 11:35:51

學(xué)習(xí)高手的FPGA編程程序,發(fā)現(xiàn)他寫的程序怎么這么冗余呢?懷著疑問,直到第二次閱讀另一高手的FPGA程序,才開始懷疑是自己錯了,原來使用時鐘使能而不直接使用分頻時鐘是原因的。查閱相關(guān)資料整理了一下

2018-08-08 11:13:26

BCSCTL2設(shè)置,第三位置1,選擇XT2CLK作為SMCLK時鐘,將第二位和第一位置1,使分頻比為8TACTL = 0x01D3;//定時器A控制寄存器設(shè)置,第二位置1:清除;第4、5位置1、0

2015-05-20 17:35:21

STM32時鐘分頻系數(shù)的知識點(diǎn)匯總,絕對實用

2021-12-15 07:01:54

的時鐘源,系統(tǒng)時鐘可選擇為PLL輸出、HSI或者HSE。系統(tǒng)時鐘的做大頻率為72MHz,它通過AHB分頻器分頻后送給個模塊使用,AHB分頻器可選擇1、2、4、8、16、32、64、128、256、512

2018-07-19 03:40:25

PLL(鎖相環(huán)電路):負(fù)責(zé)時鐘倍頻功能時鐘通道與流向、分頻完全獨(dú)立的多個時鐘:STM32含有多個相互獨(dú)立的時鐘。時鐘框圖詳解總體配置2套獨(dú)立時鐘:HSx和LSx純內(nèi)部:HSI、LSI內(nèi)外部:HSE、LSE純外部:OSC_IN、OSC32_INPLL2個可選PLL源(PLLSRC控制)倍頻可

2021-08-19 07:46:14

STM32時鐘樹案例詳解時鐘樹直接使用HSI作為時鐘源使用配置相應(yīng)的結(jié)構(gòu)體,最后調(diào)用HAL_RCC_OscConfig(), 和HAL_RCC_ClockConfig()初始化時鐘

2021-08-20 06:11:55

原文地址:STM32的時鐘樹深入詳解作者:蔡志威在STM32上如果不使用外部晶振,OSC_IN和OSC_OUT的接法如果使用內(nèi)部RC振蕩器而不使用外部晶振,請按照下面方法處理:1)對于100腳或

2021-08-23 07:38:32

和adi_sport_ConfigFrameSync中的分頻系數(shù)是多少?

2. adi_sport_ConfigClock這里的時鐘分頻系數(shù)和pcg clk的分頻系數(shù)有什么關(guān)聯(lián),比如1中的時鐘是由內(nèi)部pcg生成的,pcg該如何配置,sport是否需要配置?

2023-11-28 07:27:37

今天做了下十進(jìn)制加法計數(shù)器,用DE2做的,可是不會添加50M內(nèi)部時鐘分頻模塊,將分頻后的1秒時鐘作為計數(shù)時鐘,在這請教下各位前輩。代碼如下:LIBRARY IEEEUSE

2013-05-16 19:59:24

在FPGA的設(shè)計中一直都擔(dān)任著很重要的角色,而說到分頻,我相信很多人都已經(jīng)想到了利用計數(shù)器計數(shù)來得到想要的時鐘頻率,但問題是僅僅利用計數(shù)器來分頻,只可以實現(xiàn)偶數(shù)分頻,而如果需要三分頻、五分頻、七分頻

2019-12-11 10:15:33

實時時鐘 (RTC) 是一個獨(dú)立的 BCD 定時器/計數(shù)器,提供具有可編程鬧鐘中斷功能的日歷時鐘/日歷,可用于管理所有低功耗模式的自動喚醒單元。在配置RTC時鐘時預(yù)分頻器是關(guān)鍵指標(biāo),通過配置預(yù)分頻

2021-08-13 09:10:46

截取的RTC內(nèi)部框圖,從圖中我們可以看到,RTCCLK經(jīng)過20位分頻器RTC_DIV分頻后得到日歷的1Hz時鐘,所以我們只需要配置RTC_DIV就行了,分頻公式為RTC_CLK/(RTC_DIV+1

2021-08-29 21:36:46

定時器時鐘分頻因子和預(yù)分頻系數(shù)區(qū)別1、定時器時鐘分頻因子ClockDivision是決定數(shù)字濾波器采樣頻率的參數(shù)。之后在使用輸入捕獲濾波器時這些參數(shù)會被用到,可以根據(jù)硬件情況配置濾波。2、預(yù)分頻系數(shù)

2021-08-09 07:37:47

嗨,大家好 .......我正在尋找描述.......... GTS,GSR&時鐘分頻復(fù)位你能幫幫我嗎以上來自于谷歌翻譯以下為原文 hi guys ....... i'm looking

2019-01-09 10:42:15

基于特定的開發(fā)板上的時鐘策略:倍頻/分頻系數(shù)需要在使能 PLL 之前進(jìn)行配置,所以需要在 Open PLL 之前將所有系統(tǒng)的時鐘分頻器系數(shù)以及PLL的倍頻系數(shù)配置好。整個時鐘的配置流程如下所示:(1

2021-08-23 09:12:44

RTC時鐘要求提供1HZ的時鐘,HSE配置為RTC時鐘源, 主要配置系統(tǒng)時鐘, 使能HSE。然后設(shè)置好HSE分頻、RTC_PRER分頻寄存器的值。計算如下:??STM32F7xx的可編程預(yù)分

2022-05-13 15:19:08

模塊,如內(nèi)核、閃存、存儲器和外設(shè),這些模塊需要在不同頻率下運(yùn)行。它們的最大運(yùn)行速率可能受到所使用的實現(xiàn)技術(shù)、實施架構(gòu)、功率目標(biāo)、以及IP訪問時間等因素的限制。時鐘分頻器電路是必不可少的,它可以從主鎖相環(huán)

2012-12-11 14:43:20

【STM32】系統(tǒng)時鐘RCC詳解(超詳細(xì),超全面)1什么是時鐘時鐘是單片機(jī)運(yùn)行的基礎(chǔ),時鐘信號推動單片機(jī)內(nèi)各個部分執(zhí)行相應(yīng)的指令。時鐘系統(tǒng)就是CPU的脈搏,決定cpu速率,像人的心跳一樣 只有有了

2021-08-12 06:40:46

請給位共同討論DSP2812中死區(qū)控制單元的時鐘分頻是指對CPU時鐘還是高速外設(shè)時鐘分頻?看到論壇里說的很亂,大家討論一個正確的結(jié)果。

2018-08-19 06:31:35

ATtiny13系統(tǒng)時鐘可通過設(shè)置時鐘預(yù)分頻寄存器CLKPR來分頻

2020-11-11 07:03:03

(注:文中的x為數(shù)字)初始化1.TIMx的外設(shè)時鐘使能RCC->APB1ENR |= 1 ARR = arr;3.設(shè)定預(yù)分頻器的值在設(shè)定預(yù)分頻器的值之前,先理解這里的預(yù)分頻器與時鐘系統(tǒng)里

2021-08-18 07:54:36

我知道的是,每個IP都可以編程來選擇它的時鐘源,預(yù)分頻是什么意思?分頻的目的又是什么呢?

2024-01-17 07:34:27

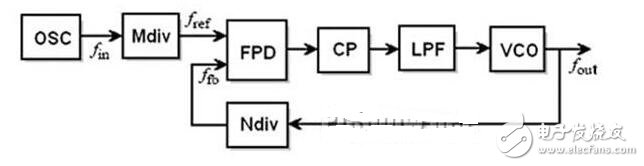

議程PLL介紹及小數(shù)分頻鎖相環(huán)的優(yōu)點(diǎn)小數(shù)分頻鎖相環(huán)的錯誤使用小數(shù)分頻鎖相環(huán)詳解參考雜散及如何減少雜散總結(jié)

2010-05-28 14:58:36 0

0

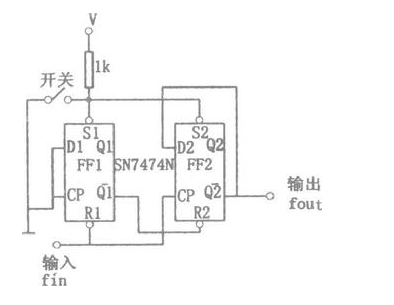

供數(shù)字時鐘使用的+5000分頻器電路

2009-01-13 20:07:47 1089

1089

具有奇次和偶次分頻的分頻器

2009-04-11 10:22:12 880

880

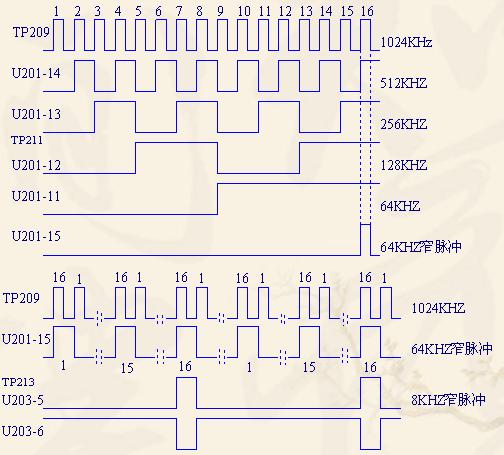

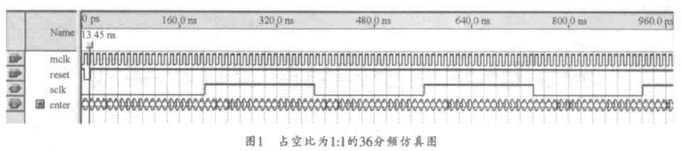

摘要:介紹了為PET(正電子發(fā)射斷層掃描儀)的前端電子學(xué)模塊提供時間基準(zhǔn)而設(shè)計的一種新型高頻時鐘扇出電路。該電路利用FPGA芯片來實現(xiàn)對高頻時鐘的分頻

2009-06-20 12:41:04 1238

1238

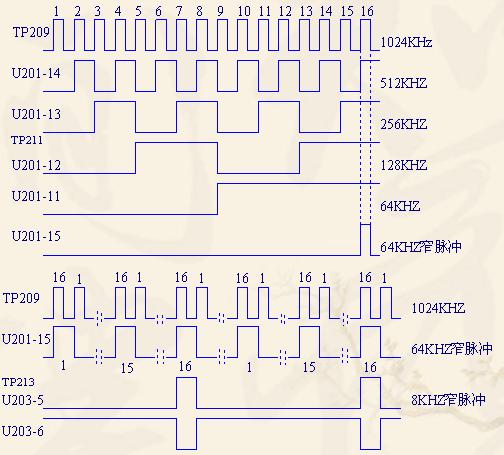

時鐘分頻及定時變換電路

2009-10-11 10:35:51 2033

2033

時鐘是SOC或塊級設(shè)計最重要的組成部分之一,本文闡述了目前SOC中各種可配置時鐘分頻器邏輯的實施方案,強(qiáng)調(diào)了各自的問題、優(yōu)勢及局限性。

2013-01-09 10:12:48 2890

2890

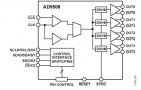

ADI最近發(fā)布了一款時鐘緩沖器和分頻器IC(集成電路)AD9508,該電路結(jié)合了高速、極低抖動(12 kHz至20 MHz頻段為41 fs)及可選分頻功能。

2013-02-21 11:31:00 4020

4020

用 Verilog實現(xiàn)基于FPGA 的通用分頻器的設(shè)計時鐘分頻包括奇數(shù)和偶數(shù)分頻

2016-07-14 11:32:47 45

45 分頻器是FPGA設(shè)計中使用頻率非常高的基本設(shè)計之一,盡管在目前大部分設(shè)計中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來進(jìn)行時鐘的分頻,倍頻以及相移。

2017-02-11 12:33:40 10916

10916 分頻器是FPGA設(shè)計中使用頻率非常高的基本設(shè)計之一,盡管在目前大部分設(shè)計中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來進(jìn)行時鐘的分頻,倍頻以及相移。

2017-02-11 13:36:36 12409

12409

基于MSP430功能模塊詳解系列之——系統(tǒng)時鐘

2017-10-12 16:40:43 5

5 )或內(nèi)部高速時鐘HSI(high speed internal)或內(nèi)部低速時鐘LSI(low speed internal)提供。這里以內(nèi)部高速時鐘舉例,內(nèi)部高速時鐘HSI經(jīng)過HSIDIV分頻,得到

2017-11-15 08:48:12 29503

29503

配置STM8外部時鐘(寄存器)步驟:1.設(shè)置外部時鐘寄存器CLK_ECKR是對其寫0xB4。2.設(shè)置外部時鐘分頻,CLK_CKDIVR低三位是外部時鐘分頻系數(shù)設(shè)置。3.使能外部時鐘向CLK_ECKR寫0x01。

2017-11-15 09:05:11 19006

19006

單片機(jī)都是有時鐘振蕩器的。還有定時器,看門狗,程序計數(shù)器等等。如果看門狗或者定時器所要求的脈沖速度比較時鐘脈沖慢,那么,就要利用分頻器進(jìn)行分頻,以得到你所要求的脈沖速率。分頻因子就是在定時器時鐘進(jìn)入

2017-11-15 10:07:22 18147

18147

STM32中有一個全速功能的USB模塊,其串行接口引擎需要一個頻率為48MHz的時鐘源。該時鐘源只能從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當(dāng)需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。

2017-11-30 09:14:18 6833

6833

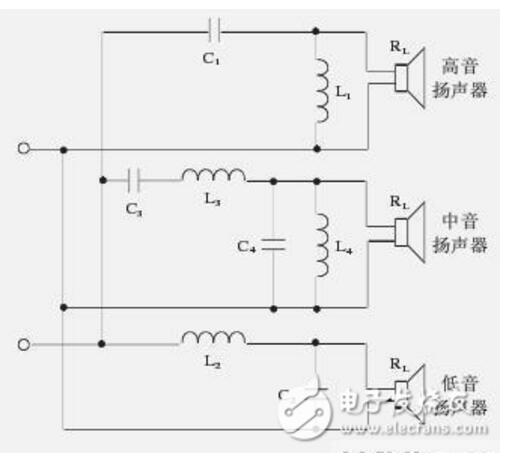

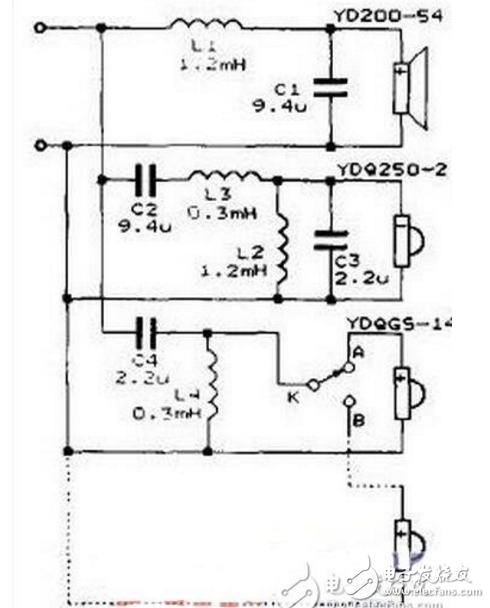

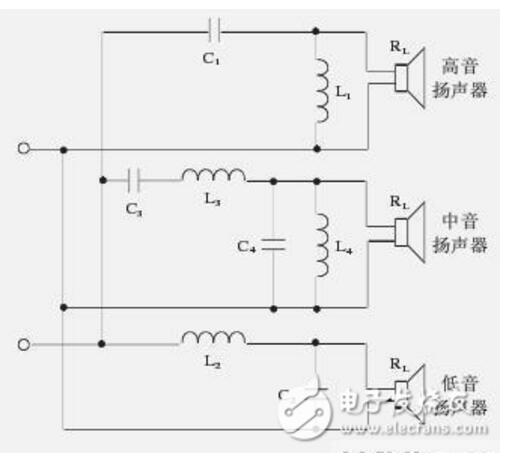

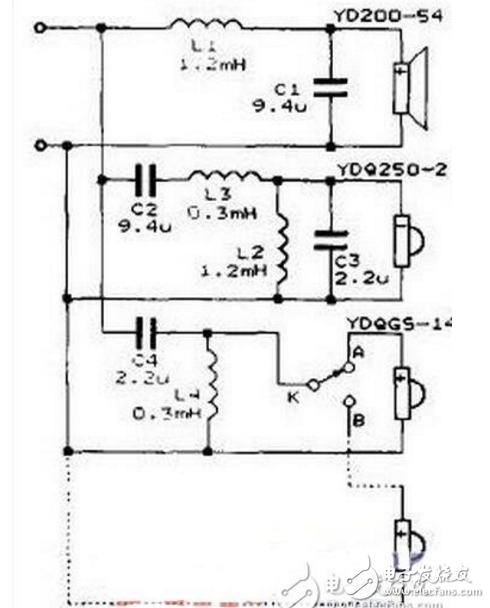

本文主要介紹了音響二分頻器電路圖(六款模擬電路設(shè)計原理圖詳解)。分頻器就是一個由電容器和電感線圈構(gòu)成的濾波網(wǎng)。高音通道只讓高頻信號經(jīng)過而阻止低頻信號;低音通道正好相反,只讓低音經(jīng)過而阻止高頻

2018-02-01 10:08:01 246621

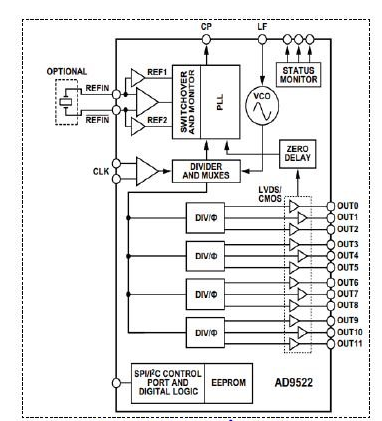

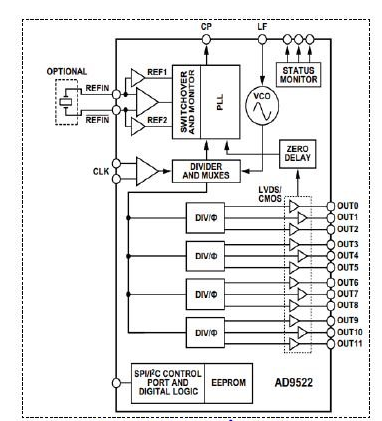

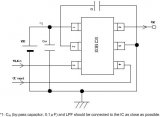

246621 在集成度高度發(fā)展的今天,不能靠多個晶振源來解決問題,而且一旦晶振固定那么它的靈活性和可移植性必然受到很大影響,所以一些時鐘分頻芯片應(yīng)運(yùn)而生,今天我們將舉一個很有代表性的AD9522時鐘分頻芯片的典型應(yīng)用來達(dá)到一個拋磚引玉的作用。

2018-03-16 16:31:00 11548

11548

本文主要介紹了電子分頻器電路圖大全(六款電子分頻器電路設(shè)計原理圖詳解)。從工作原理看,分頻器就是一個由電容器和電感線圈構(gòu)成的濾波網(wǎng)。高音通道只讓高頻信號經(jīng)過而阻止低頻信號;低音通道正好相反,只讓低音

2018-03-02 09:41:17 123621

123621

如輸出到稱為HCLK、FCLK的時鐘,還直接輸出到SDIO外設(shè)的SDIOCLK時鐘、存儲器控制器FSMC的FSMCCLK時鐘,和作為APB1、APB2的預(yù)分頻器的輸入端。GPIO外設(shè)是掛載在APB2

2018-04-03 08:45:51 19520

19520

本文主要詳解什么是激勵器、分頻器、均衡器、壓縮限幅器,最后還介紹了均衡器與激勵器的區(qū)別,具體的跟隨小編一起來了解一下。

2018-05-28 15:10:19 4787

4787 本文主要詳解音箱、揚(yáng)聲器、分頻器、功放,首先介紹了音箱的組成、原理、分類及性能指標(biāo),其次介紹了揚(yáng)聲器的原理和使用方法,最后詳細(xì)的闡述了分頻器、功放的原理及作用,具體的跟隨小編一起來了解一下。

2018-05-29 11:24:35 6767

6767 輸入端分頻因子(M)可從1~2047的分頻范圍內(nèi)進(jìn)行選擇;輸出端分頻因子(N)可從1~4095的分頻范圍內(nèi)進(jìn)行選擇。輸出頻率在1MHz~100MHz的范圍內(nèi),輸入時鐘為8kHz~36MHz的標(biāo)準(zhǔn)時鐘。在內(nèi)部可進(jìn)行微調(diào),在少量外置部件的條件下動作。

2018-08-15 11:16:30 6671

6671

分頻器是FPGA設(shè)計中使用頻率非常高的基本單元之一。盡管目前在大部分設(shè)計中還廣泛使用集成鎖相環(huán)(如altera的PLL,Xilinx的DLL)來進(jìn)行時鐘的分頻、倍頻以及相移設(shè)計,但是,對于時鐘要求

2019-08-07 08:00:00 9033

9033

偶數(shù)倍分頻器的實現(xiàn)非常簡單,只需要一個計數(shù)器進(jìn)行計數(shù)就能實現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時鐘觸發(fā)計數(shù)器進(jìn)行計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,將輸出時鐘進(jìn)行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,以使下一個時鐘開始從零計數(shù)。

2019-02-01 01:49:00 1029

1029

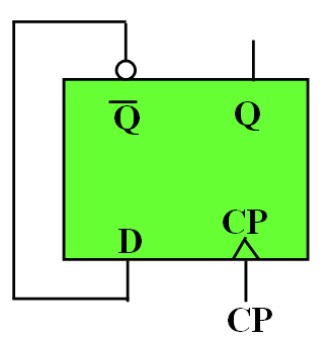

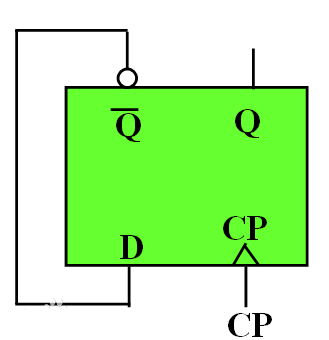

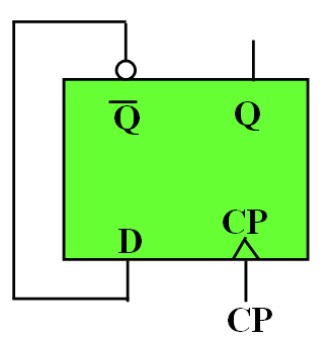

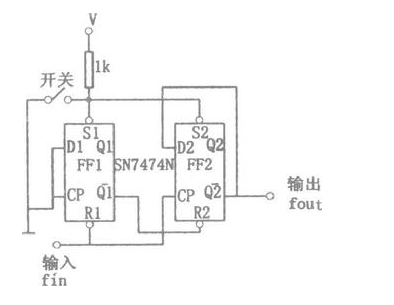

分頻就是用同一個時鐘信號通過一定的電路結(jié)構(gòu)轉(zhuǎn)變成不同頻率的時鐘信號。而二分頻就是通過有分頻作用的電路結(jié)構(gòu),在時鐘每觸發(fā)2個周期時,電路輸出1個周期信號。

2019-10-08 09:05:00 22246

22246

從分頻方式看可以分為兩種,一種是主動分頻(PassiveCrossover),或者叫電子分頻,也可以叫外置分頻、有源分頻;另一種是被動分頻 (ActiveCrossover),或者叫功率分頻,也可以叫內(nèi)置分頻、無源分頻。

2019-10-08 10:37:42 11681

11681

通常情況下,時鐘的分頻在FPGA設(shè)計中占有重要的地位,在此就簡單列出分頻電路設(shè)計的思考思路。

2020-07-10 17:18:03 2192

2192 對于分頻系數(shù)為 10 的分頻器, 本例的輸入時鐘系統(tǒng) 50M 時鐘(clk_50M), 輸出為十分頻時鐘(f_50) 。設(shè)計方法為,通過設(shè)置一個 3 位的計數(shù)寄存器(cnt)來實現(xiàn),每個時鐘周期的上升沿計數(shù)一次, 當(dāng)計數(shù)寄存器數(shù)到 4 的時候, 將輸出分頻信號取反即可得到 10 分頻的輸出。

2020-10-28 08:00:00 1

1 電子發(fā)燒友網(wǎng)站提供《NB7V33MMNGEVB 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:06:41 5

5 電子發(fā)燒友網(wǎng)站提供《NB7L32MMNEVB 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:21:59 2

2 電子發(fā)燒友網(wǎng)站提供《SY89876L 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:22:31 10

10 電子發(fā)燒友網(wǎng)站提供《SY89873L 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:23:10 5

5 電子發(fā)燒友網(wǎng)站提供《NB6L239MNEVB/D 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:23:51 13

13 電子發(fā)燒友網(wǎng)站提供《SY89872U 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:24:21 1

1 電子發(fā)燒友網(wǎng)站提供《SY89871U 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:25:53 6

6 電子發(fā)燒友網(wǎng)站提供《SY89875U 時鐘分頻器參考設(shè)計.pdf》資料免費(fèi)下載

2020-12-31 05:27:06 4

4 程序?qū)崿F(xiàn)對輸入時鐘信號的7分頻介紹。

2021-03-17 14:59:23 11

11 AD9510:1.2 GHz時鐘分配IC,PLL內(nèi)核,分頻器,延遲調(diào)整,8路輸出

2021-03-21 15:32:58 11

11 AD9508:1.65 GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調(diào)整

2021-03-21 15:45:30 2

2 AD9515:1.6 GHz時鐘分配IC、分頻器、延遲調(diào)整、雙輸出數(shù)據(jù)表

2021-04-13 14:38:52 9

9 電子發(fā)燒友網(wǎng)為你提供理解STM32系統(tǒng)時鐘和分頻資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-20 08:43:42 11

11 LTC6954:低相位噪聲、三輸出時鐘分布分頻器/驅(qū)動器數(shù)據(jù)表

2021-05-19 13:19:44 4

4 AD9515 1.6 GHz時鐘分配IC,分頻器,延遲調(diào)整,雙輸出數(shù)據(jù)表

2021-06-16 17:13:16 12

12 最小系統(tǒng)1,、供電電路2、復(fù)位電路3、時鐘:外部晶振(2個)4、Boot啟動模式選擇5、下載電路(JTAG)6、后背電池時鐘詳解:在STM32中,有五個時鐘源,為HSI、HSE、LSI、LSE

2021-11-17 15:36:02 12

12 DCO頻率配置 MCLK,SMCLK時鐘源選擇,分頻配置 時鐘信號選擇

2021-11-25 09:36:04 40

40 【STM32】系統(tǒng)時鐘RCC詳解(超詳細(xì),超全面) 原創(chuàng) ...

2021-11-30 12:21:07 13

13 一、RCC是什么?

RCC: Reset Clock Control,時鐘和復(fù)位控制器

二、RCC的主要作用

1、設(shè)置系統(tǒng)時鐘SYSCLK

2、設(shè)置AHB分頻因子(決定HCLK等于

2022-02-11 15:38:08 5

5 有關(guān)小數(shù)分頻的資料,用于時鐘芯片設(shè)計,十分經(jīng)典。

2022-10-24 11:48:44 0

0 偶數(shù)倍分頻器的實現(xiàn)非常簡單,只需要一個計數(shù)器進(jìn)行計數(shù)就能實現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時鐘觸發(fā)計數(shù)器進(jìn)行計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,將輸出時鐘進(jìn)行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,以使下一個時鐘開始從零計數(shù)。

2022-11-21 09:41:24 751

751 時鐘使能電路是同步設(shè)計的基本電路,在很多設(shè)計中,雖然內(nèi)部不同模塊的處理速度不同,但由于這些時鐘是同源的,可以將它們轉(zhuǎn)化為單一時鐘處理;在ASIC中可以通過STA約束讓分頻始終和源時鐘同相

2023-01-05 14:00:07 949

949 初學(xué) Verilog 時許多模塊都是通過計數(shù)與分頻完成設(shè)計,例如 PWM 脈寬調(diào)制、頻率計等。而分頻邏輯往往通過計數(shù)邏輯完成。本節(jié)主要對偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻以及小數(shù)分頻進(jìn)行簡單的總結(jié)。

2023-03-29 11:38:40 3108

3108

時鐘分頻電路(分頻器)在IC設(shè)計中經(jīng)常會用到,其目的是產(chǎn)生不同頻率的時鐘,滿足系統(tǒng)的需要。 比如一個系統(tǒng),常規(guī)操作都是在1GHz時鐘下完成,突然要執(zhí)行一個操作涉及到模擬電路,所需時間是us量級的,顯然用1GHz(周期是1ns)的時鐘進(jìn)行操作是不合適的。

2023-04-25 14:46:25 5332

5332

上一篇文章時鐘分頻系列——偶數(shù)分頻/奇數(shù)分頻/分?jǐn)?shù)分頻,IC君介紹了各種分頻器的設(shè)計原理,其中分?jǐn)?shù)分頻器較為復(fù)雜,這一篇文章IC君再跟大家聊聊分?jǐn)?shù)分頻的具體設(shè)計實現(xiàn)。

2023-04-25 14:47:44 1028

1028

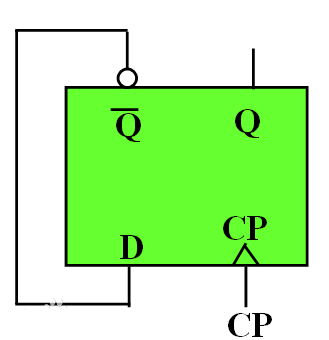

采用觸發(fā)器反向輸出端連接到輸入端的方式,可構(gòu)成簡單的 2 分頻電路。

2023-05-30 17:21:29 1189

1189

板載晶振提供的時鐘信號頻率是固定的,不一定滿足需求,因此需要對基準(zhǔn)時鐘進(jìn)行分頻。要得到更慢的時鐘頻率可以 分頻 ,要得到更快的時鐘頻率可以 倍頻 。我們有兩種方式可以改變頻率,一種是 鎖相環(huán) (PLL,后面章節(jié)會講解),另一種是用 Verilog代碼描述。

2023-06-23 16:52:00 1149

1149

基于FPGA的高頻時鐘的分頻和分頻設(shè)計

2023-08-16 11:42:47 0

0 為什么單片機(jī)內(nèi)置時鐘源不經(jīng)過pll也可以分頻?? 單片機(jī)內(nèi)置時鐘源不經(jīng)過PLL也可以實現(xiàn)分頻,原因在于單片機(jī)內(nèi)置時鐘源自帶分頻器,可以通過軟件設(shè)置分頻系數(shù)來控制內(nèi)部時鐘頻率。 在單片機(jī)內(nèi)部,通常會

2023-09-02 15:12:45 597

597 時鐘分頻電路通過將輸入的高頻時鐘信號分頻,生成較低頻率的時鐘信號。它通常基于計數(shù)器和邏輯門實現(xiàn),用于將高頻時鐘信號分解成系統(tǒng)所需的各種頻率。

2023-09-14 14:53:57 4894

4894 通過一個標(biāo)志信號作為偶6分頻的工作時鐘(可靠,常用)

2023-10-10 14:23:52 205

205

分頻器設(shè)計 一:分頻器概念 板載時鐘往往 是 有限個( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在設(shè)計中需要其他時鐘時,板載時鐘不滿足時,需要對板載時鐘進(jìn)行分頻 / 倍頻,目的

2023-11-03 15:55:02 471

471

其實這個分頻時鐘切換很簡單,根本不需要額外的切換電路。一個共用的計數(shù)器,加一點(diǎn)控制邏輯,就可以了,而且可以實現(xiàn)2到16任意整數(shù)分頻率之間的無縫切換。

2023-12-14 15:28:56 257

257

鎖相環(huán)整數(shù)分頻和小數(shù)分頻的區(qū)別是什么? 鎖相環(huán)(PLL)是一種常用的電子電路,用于將輸入的時鐘信號與參考信號進(jìn)行同步,并生成輸出信號的一種技術(shù)。在PLL中,分頻器模塊起到關(guān)鍵作用,可以實現(xiàn)整數(shù)分頻

2024-01-31 15:24:48 312

312

電子發(fā)燒友App

電子發(fā)燒友App

評論