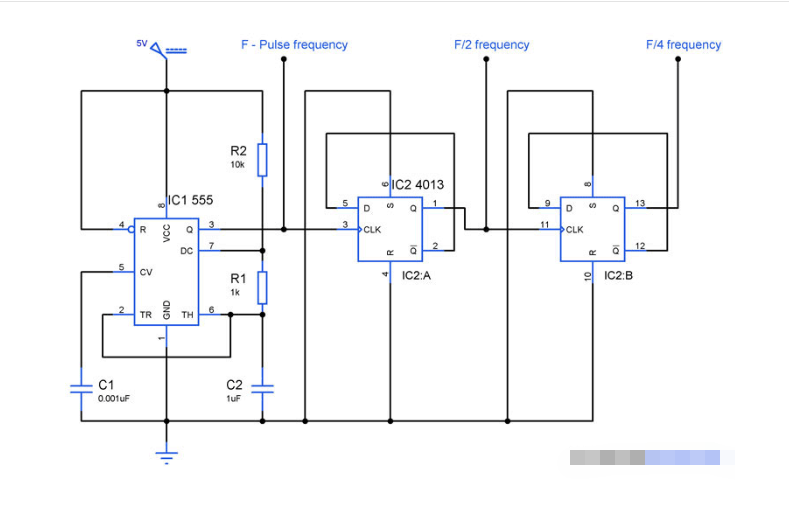

的OCC。像是拔牙操作一類的分頻我們今天不討論。今天討論的任意分頻器在許多的數字IC設計與FPGA面試筆試題中都有考察,所以在實(tou)現(xue)了以后做本次學習記錄,供大家參考。1. 先入為主 我們來宏觀的看本次分頻器的內容,會比較容易理解。關鍵功能點的電路如圖1所示:...

2022-02-09 07:34:15

畢設題目 :75mhz雙路時鐘緩沖器,求助

2021-02-27 21:45:00

本帖最后由 gk320830 于 2015-3-7 18:17 編輯

跪求 !!分頻系數在一定范圍內可調的分頻器電路圖》。。

2013-08-29 18:19:29

請問有哪種可編程分頻器芯片啊?適合高頻,幾十兆到500兆。

2017-08-05 15:00:15

分頻器EDA設計代碼···僅供參考···

2013-12-09 12:26:46

1.65 GHz時鐘扇出緩沖器,帶輸出分頻器和延遲調整

2023-03-28 18:12:34

AKD8181D,AK8181時鐘扇出緩沖器評估板。因此,很容易評估DC / AC特性并確認產品功能

2020-08-25 15:26:54

。

CANCLKCON(CAN時鐘控制寄存器)中還有CANCLKDIV(CAN時鐘分頻器選擇位),其范圍為1 - 128。

據我所知,CANCLKDIV 什么也沒做。我只使用普通的 CAN,而不是 CAN-FD

2024-01-22 06:36:03

分頻器模塊實現的基本原理就是設計一個工作在系統時鐘下的計數器,循環地遞減或者遞加計數,在某個計數的固定值將輸出翻轉,即可實現時鐘分頻的功能。例如,實驗板上的系統時鐘是 50MHz,而所需的讀寫周期

2018-11-15 09:25:35

SY89871U,GB以太網交換機時鐘分頻器評估板。 SY89871U,可編程LVPECL時鐘分頻器評估板

2019-02-19 09:32:47

SY89873L,GB以太網交換機時鐘分頻器評估板。 SY89873L,可編程LVPECL時鐘分頻器評估板

2019-02-20 09:27:40

SY89874U,GB以太網交換機時鐘分頻器評估板。 SY89874U,可編程LVPECL時鐘分頻器評估板

2019-02-20 09:42:21

HMC905LP3E分頻器產品介紹HMC905LP3E詢價熱線HMC905LP3E現貨HMC905LP3E代理王先生 深圳市首質誠科技有限公司, HHMC905LP3E是一款SiGe BiCMOS

2018-10-17 15:49:04

NB6L239MNEVB / D,SONET時鐘分頻器評估板。 NB6L239是差分接收器到差分LVPECL時鐘分頻器。電路板功能輸出啟用輸出控制

2019-02-20 09:29:49

NB7V32MMNGEVB,差分時鐘分頻器評估板。 NB7V32M是一個差分2分頻時鐘分頻器,具有異步復位功能。差分時鐘輸入包含內部50歐姆端接電阻,可接受LVPECL,CML和LVDS邏輯電平

2019-02-20 09:41:47

跪求大神相告,在protel99se中哪個庫中有分頻器

2014-06-24 16:08:41

“外設時鐘”Pclk,而沒有指定使用哪個 APBx 為每個 SPIx 提供時鐘。也與上述相關:手冊討論了 SPI 時鐘的預分頻器,但是,CubeMX 不提供為 SPI2 設置預分頻器的選項。看起來有些

2022-12-15 06:57:22

`請問什么是音頻緩沖器?`

2019-08-23 16:27:28

會退出總線繁忙狀態和失敗。 出于好奇,我嘗試將時鐘頻率配置為 400MHz 并使用分頻器 2 來獲得 200M 的值。 我想知道 RFDR 中的這個值表示什么以及誰負責更新? 如果我使用分頻器值 3,則操作成功,RFDR[0] 值為 0x80,依此類推各種循環序列的變化。

2023-04-03 09:01:11

這種方式只消耗不多的邏輯單元就可以達到對時鐘的操作目的。2、整數倍分頻器的設計2.1 偶數倍分頻 偶數倍分頻器的實現非常簡單,只需要一個計數器進行計數就能實現。如需要N分頻器(N為偶數),就可以由待分頻

2014-06-19 16:15:28

【摘要】:介紹了基于FPGA的任意分頻系數的分頻器的設計,該分頻器能實現分頻系數和占空比均可以調節的3類分頻:整數分頻、小數分頻和分數分頻。所有分頻均通過VHDL語言進行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數

2019-10-08 10:08:10

Prescaler:定時器預分頻器設置,時鐘源經該預分頻器才是定時器時鐘,它設定 TIMx_PSC寄存器的值。可設置范圍為 0 至 65535,實現 1 至 65536 分頻

2021-08-19 06:47:20

基于特定的開發板上的時鐘策略:倍頻/分頻系數需要在使能 PLL 之前進行配置,所以需要在 Open PLL 之前將所有系統的時鐘分頻器系數以及PLL的倍頻系數配置好。整個時鐘的配置流程如下所示:(1

2021-08-23 09:12:44

NB6L239MNEVB,工業用時鐘分頻器評估板。 NB6L239是差分接收器到差分LVDS時鐘分頻器。電路板功能輸出啟用輸出控制

2019-02-20 06:26:41

NB7V33MMNGEVB,差分時鐘分頻器評估板。 NB7V33M是一個4分頻時鐘分頻器,具有異步復位功能。差分時鐘輸入包含內部50歐姆端接電阻,可接受LVPECL,CML和LVDS邏輯電平

2019-02-21 09:44:22

是否有評估板的外部(FPGA外部)時鐘分頻器而不是使用DCM或PLL?問候,半

2020-03-16 09:11:44

實現功能:能對12MHZ以上的方波信號進行分頻另一疑問:占空比20%經過分頻器分頻后,占空比會變嗎?

2021-09-24 10:33:52

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測量時鐘緩沖器的附加抖動。為什么抖動很重要?在當今數據通信、有線及無線基礎設施以及其它高速應用等高級系統中,時鐘抖動是整體系統性能的關鍵因素。要

2018-09-13 14:38:43

模塊,如內核、閃存、存儲器和外設,這些模塊需要在不同頻率下運行。它們的最大運行速率可能受到所使用的實現技術、實施架構、功率目標、以及IP訪問時間等因素的限制。時鐘分頻器電路是必不可少的,它可以從主鎖相環

2012-12-11 14:43:20

NB7L32MMNEVB,用于SONET的20000MHz時鐘分頻器的評估板。評估板旨在便于快速評估NB7L32M GigaComm時鐘驅動器

2019-02-20 09:30:29

DC1075A,演示電路1075是用于高速ADC的時鐘分頻器。每個組件包括一個時鐘分頻器,后面是一個用于產生尖銳時鐘邊沿的重定時級

2019-02-21 09:45:45

我想對2GHz的正弦波(相位噪聲很低)進行16分頻,分頻出來的125M信號輸入給FPGA,想選用ADi的分頻器實現分頻功能,我有以下幾個問題:1.我查了ADi的分頻器,分為(1)時鐘分頻器,(2

2019-01-11 13:39:43

我打算使用AD9269進行信號采集,關于時鐘分頻器這塊,我不需要進行內部的分頻,只需要根據我外部輸入時鐘頻率工作就可以,在控制管腳SYNC這一塊,芯片手冊上說通過數字輸入控制,但是不希望進行數字輸入

2018-10-10 10:32:15

PWM預分頻器、分頻器和定時器的分辨率是多少?

2020-12-07 06:07:09

與傳統的時鐘緩沖器相比,高速運算放大器有哪些優勢?怎樣去設計一個靈活的時鐘緩沖器?

2021-04-14 06:35:37

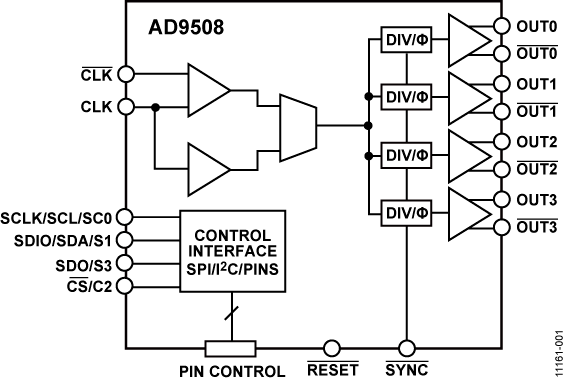

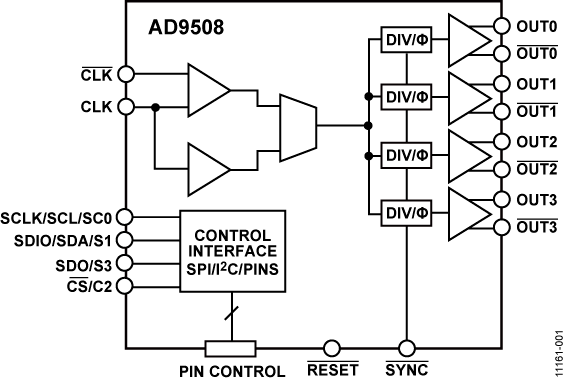

如圖,AD9508的差分輸入靈敏度要求在360到2200 mVpp,共模電壓在1.05V左右。我們設計的電路如下圖:其中OCXOUT為恒溫晶振輸出,作為AD9508的外接信號源,通過巴倫轉換為差分信

2018-08-22 07:57:37

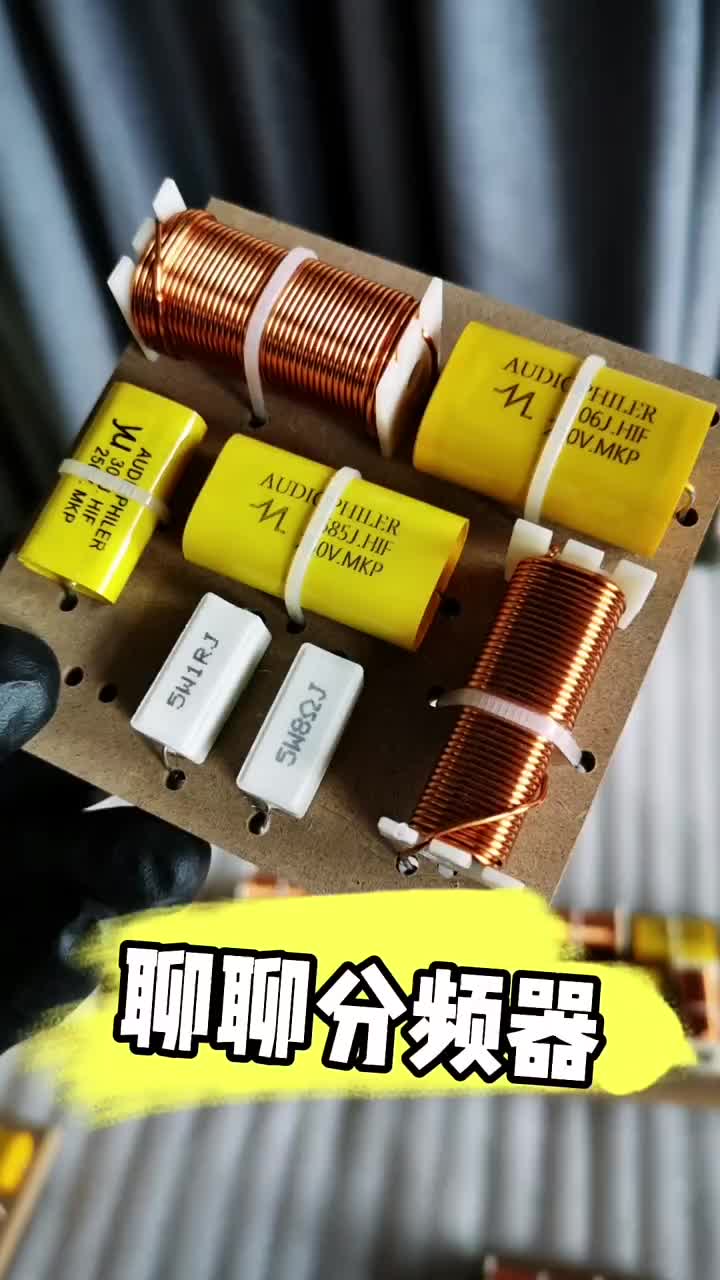

分頻器的使用問題音響技術分頻器是一種可以將聲音信號分成若干個頻段的音響設備。我們知道,聲音的頻率范圍是在20Hz—20kHz之間,祈望僅使用一只揚聲器就能夠保證放送、20Hz—20kHz這樣寬頻

2019-11-01 09:10:30

`音箱分頻器電感的制作分頻器線圈用線均為0.1mm. 電感量(mH)圈數0.3900.35950.51140.651300.81431.01601.51952.02213.0284漆包線在φ32mm骨架上多層平繞,繞好后脫胎用線扎緊`

2013-08-30 22:12:50

(注:文中的x為數字)初始化1.TIMx的外設時鐘使能RCC->APB1ENR |= 1 ARR = arr;3.設定預分頻器的值在設定預分頻器的值之前,先理解這里的預分頻器與時鐘系統里

2021-08-18 07:54:36

`請問高速緩沖器是什么?`

2019-08-23 16:32:59

具有分頻器的 5/10 路輸出時鐘緩沖器 Function Differential Additive RMS jitter (Typ) (fs) 200 Output

2022-11-30 16:59:28

具有 8 個 LVDS 輸出的 1.6GHz 高性能時鐘緩沖器、分頻器和分配器 Function Clock divider, Differential Additive RMS

2022-11-30 16:59:30

具有 8 個 LVPECL 輸出的 1.6GHz 高性能時鐘緩沖器、分頻器和分配器 Function Differential, Fanout Additive RMS jitter

2022-11-30 16:59:30

具有 3 個 LVDS 和 5 個 LVPECL 輸出的 1.6GHz 高性能時鐘緩沖器、分頻器和分配器 Function Differential, Fanout Additive

2022-11-30 16:59:31

具有可編程分頻器的時鐘緩沖器,LVPECL I/O 和 LVCMOS 輸出 Function Clock divider, Fanout Additive RMS jitter

2022-12-02 13:46:54

具有可編程分頻器的 1:3 LVPECL 時鐘緩沖器 Function Differential, Fanout Additive RMS jitter (Typ) (fs

2022-12-02 13:46:55

1:3 LVPECL 時鐘緩沖器 + LVCMOS 輸出 + 可編程分頻器 Function Clock divider, Fanout Additive RMS jitter

2022-12-02 13:46:56

定阻型功率分頻器的設計與制作(三)-二階功率分頻器

2009-12-02 15:48:19 76

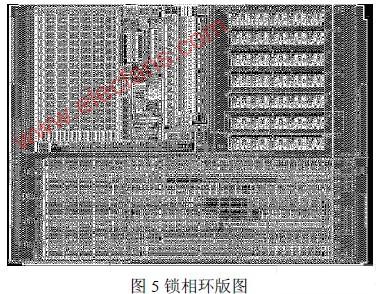

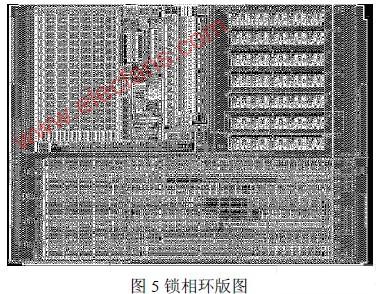

76 給出基于0.13μm CMOS工藝、采用單時鐘動態負載鎖存器設計的四分頻器。該四分頻器由兩級二分頻器級聯而成,級間采用緩沖電路實現隔離和電平匹配。后仿真結果表明其最高工作頻

2010-12-29 18:00:34 34

34

供數字時鐘使用的+5000分頻器電路

2009-01-13 20:07:47 1089

1089

分頻系數可變的分頻器

2009-04-11 10:18:26 1206

1206

具有奇次和偶次分頻的分頻器

2009-04-11 10:22:12 880

880

TI推出正弦至正弦波時鐘緩沖器

日前,德州儀器 (TI) 宣布推出業界最小型 4 通道、低功耗、低抖動正弦至正弦波時鐘緩沖器。作為正弦波時鐘緩沖器系列產品中的首款

2009-11-30 10:53:51 815

815 什么是分頻器 分頻器介紹

分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放

2010-02-05 17:51:10 3676

3676 ADI 公司推出低功耗射頻預分頻器-- ADF500x 射頻預分頻器電路工作頻率可達 18GHz,功耗非常低,可與業界領先的 ADI PLL 合成器配套使用

&nbs

2010-05-11 16:27:21 580

580 1 引言

本文在傳統鎖相環結構的基礎上進行改進,設計了一款用于多路輸出時鐘緩沖器中的鎖相環,其主 要結構包括分頻器、鑒頻鑒相器(PFD)、電荷泵、環路濾波器

2010-08-17 15:33:59 1035

1035

用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 45

45 The AD9508 provides clock fanout capability in a design that emphasizes low jitter to maximize

2017-10-19 13:26:20 14

14 分頻器分為主動式、被動式、脈沖分頻器三種。主動式電子分音器的原理就是要把適當頻率訊號傳給適當的單體,被動式分音器“功能、用途”是介于擴大器與喇叭之間,由于單一喇叭無法達到“全頻段響應”,脈沖分頻器利用漢穩態電路的計數功能實現分頻的電路,又稱為數字分頻器。

2018-01-10 15:36:20 10793

10793 本文首先介紹了什么是分頻器,其次闡述了音箱箱體及音箱分頻器結構和原理,最后介紹了音箱分頻器特點和作用。

2018-05-25 17:47:16 11413

11413

本文首先介紹了分頻器的分類及電子分頻器的工作原理,其次介紹了主動分頻器的優缺點,最后介紹了被動分頻器的優缺點,具體的跟隨小編一起來了解一下。

2018-05-28 14:52:31 47204

47204 電子發燒友網為你提供ADI(ti)AD9508相關產品參數、數據手冊,更有AD9508的引腳圖、接線圖、封裝手冊、中文資料、英文資料,AD9508真值表,AD9508管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:53:34

電子發燒友網站提供《NB7V33MMNGEVB 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:06:41 5

5 電子發燒友網站提供《NB7L32MMNEVB 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:21:59 2

2 電子發燒友網站提供《SY89876L 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:22:31 10

10 電子發燒友網站提供《SY89873L 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:23:10 5

5 電子發燒友網站提供《NB6L239MNEVB/D 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:23:51 13

13 電子發燒友網站提供《SY89872U 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:24:21 1

1 電子發燒友網站提供《SY89871U 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:25:53 6

6 電子發燒友網站提供《SY89875U 時鐘分頻器參考設計.pdf》資料免費下載

2020-12-31 05:27:06 4

4 AD9508 Evaluation Software Full Install

2021-02-19 09:40:09 2

2 AD9508 IBIS Model

2021-03-09 12:27:12 0

0 AD9510:1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出

2021-03-21 15:32:58 11

11 AD9508:1.65 GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調整

2021-03-21 15:45:30 2

2 AD9512:1.2 GHz時鐘分配IC,1.6 GHz輸入,分頻器,延遲調整,五輸出數據表

2021-03-22 19:53:41 13

13 AD9508評估軟件Web安裝

2021-04-09 10:09:51 0

0 AD9515:1.6 GHz時鐘分配IC、分頻器、延遲調整、雙輸出數據表

2021-04-13 14:38:52 9

9 AD9573:PCI-Express時鐘發生器IC,PLL內核,分頻器,雙輸出數據表

2021-05-08 20:05:05 5

5 AD9508 IBIS型號

2021-05-30 14:31:06 0

0 AD9508評估軟件完全安裝

2021-06-02 12:20:01 0

0 AD9508評估板是一款緊湊、易于使用的平臺,可用來評估AD9508的全部特性。本用戶指南將重點說明AD9508評估板和軟件。AD9508是一款靈活的高性能1:4時鐘緩沖器。每個輸出具有一個可編程分頻器,可通過SPI/I2C編程或Sx引腳綁定設置。AD9508采用2.5 V和3.3 V電源電壓工作。

2021-06-08 17:50:56 6

6 AD9515 1.6 GHz時鐘分配IC,分頻器,延遲調整,雙輸出數據表

2021-06-16 17:13:16 12

12 IDT 還提供另一個更簡單的 CMOS 緩沖器系列,即5PB11xx系列,由五個時鐘扇出緩沖器成員組成,其中最后兩位數字代表輸出數量。這些緩沖器是非常高性能、低抖動、低偏移和傳播延遲、非常低功耗的直接 CMOS 扇出緩沖器。

2022-05-05 15:41:13 1500

1500

什么是時鐘緩沖器(Buffer)?時鐘緩沖器(Buffer)參數解析 什么是時鐘緩沖器(Buffer)?我們先把這個概念搞清楚。 時鐘緩沖器就是常說的Clock Buffer,通常是指基于非PLL

2022-10-18 18:36:54 18409

18409

時鐘緩沖器選型目錄

2021-11-19 16:38:53 789

789

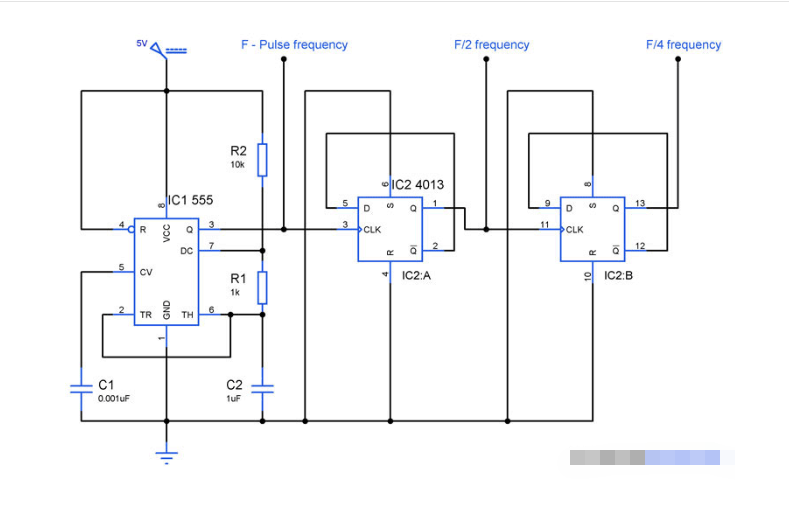

曾經遇到過這樣一種情況,即您只有一個特定頻率的信號源,需要獲取多個頻率的信號。如果是,這種電路可能是您需要在設計中使用的電路。上述電路是一個分頻器,能夠通過一定的因素對輸入時鐘頻率進行分頻。該分頻器

2023-07-02 11:47:17 791

791

分頻器設計 一:分頻器概念 板載時鐘往往 是 有限個( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在設計中需要其他時鐘時,板載時鐘不滿足時,需要對板載時鐘進行分頻 / 倍頻,目的

2023-11-03 15:55:02 471

471

電子發燒友App

電子發燒友App

評論