FIR 濾波器廣泛應(yīng)用于數(shù)字信號處理中,主要功能就是將不感興趣的信號濾除,留下有用信號。##全并行FIR濾波器結(jié)構(gòu)

2014-06-27 10:02:56 8178

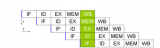

8178 流水線是為了提高效率,能并發(fā)同時進行多個任務(wù)。

2023-09-05 15:39:56 1112

1112

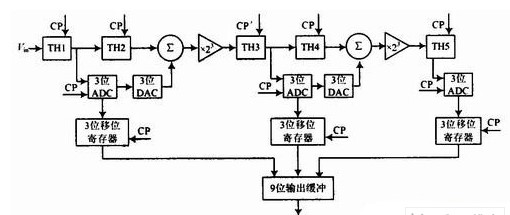

低采樣速率ADC仍然采用逐次逼近(SAR)、積分型結(jié)構(gòu)以及最近推出的過采樣ΣΔADC,而高采樣速率(幾百MSPS以上)大多用閃速ADC及其各種變型電路。然而,最近幾年各種各樣的流水線ADC已經(jīng)在速度

2023-09-26 10:24:32 434

434

本篇博文描述的是通過將 URAM 矩陣配置為使用流水線寄存器來實現(xiàn)最佳時序性能的方法

2019-07-26 16:01:44 5883

5883

時不同頻率分量的疊加的相位情況和輸入時有變化,得到的通帶信號產(chǎn)生失真。iir濾波器有以下幾個特點:1 iir數(shù)字濾波器的系統(tǒng)函數(shù)可以寫成封閉函數(shù)的形式。2 iir數(shù)字濾波器采用遞歸型結(jié)構(gòu),即結(jié)構(gòu)上帶有反饋環(huán)路

2018-03-12 13:21:07

的線性相位濾波器IIR濾波器有以下幾個特點:1、IIR數(shù)字濾波器的系統(tǒng)函數(shù)可以寫成封閉函數(shù)的形式。2、IIR數(shù)字濾波器采用遞歸型結(jié)構(gòu),即結(jié)構(gòu)上帶有反饋環(huán)路。IIR濾波器運算結(jié)構(gòu)通常由延時、乘以系數(shù)

2016-08-08 08:49:32

的性能要去較高。圖1 FIR濾波原理圖 IIR濾波器定義:IIR濾波器是無限脈沖響應(yīng)濾波器,又稱遞歸型濾波器,即結(jié)構(gòu)上帶有反饋環(huán)路。特點:IIR數(shù)字濾波器的系統(tǒng)函數(shù)可以寫成封閉函數(shù)的形式,具有反饋回路

2019-06-27 04:20:31

;FIR 濾波器的系統(tǒng)函數(shù)為多項式;FIR 濾波器具有線性相位。實現(xiàn)同樣參數(shù)的濾波器,FIR比IIR需要的階數(shù)高,因此計算量大。目前,FIR 數(shù)字濾波器的設(shè)計方法主要是建立在對理想濾波器頻率特性做某種近似的基礎(chǔ)上。設(shè)計方法有窗函數(shù)法,等波紋設(shè)計法(Equiripple)和最小二乘法 (Least

2021-08-17 06:19:17

對于fir濾波器,已經(jīng)在前面的文章中記錄了仿制DIY&關(guān)于MATLAB中濾波器設(shè)計工具的使用心得記錄),其設(shè)計和實現(xiàn)都非常簡單。如果在嵌入式系統(tǒng)中可以滿足且有必要實時iir運算,那么

2021-12-22 08:29:40

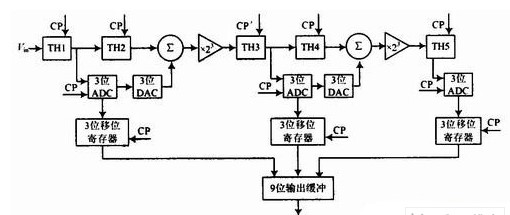

實現(xiàn)FPGA數(shù)字下變頻的多類濾波器分組級聯(lián)技術(shù)分析1 引 言 本文針對以下高效算法做了總結(jié),進行合理的分組級聯(lián)并引入流水線技術(shù)以便于在FPGA上實現(xiàn)。數(shù)字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

型結(jié)構(gòu)FIR,實現(xiàn)時可以采用并行結(jié)構(gòu)、串行結(jié)構(gòu)、分布式結(jié)構(gòu),也可以直接使用Quartus和Vivado提供的FIR IP核。本篇先介紹并行FIR濾波器的Verilog設(shè)計。設(shè)計參考自杜勇老師

2020-09-25 17:44:38

本文介紹了流水線ADC的內(nèi)部結(jié)構(gòu)和工作原理。

2021-04-22 06:56:00

圖中的DFG(Data Flow Graph)節(jié)點已經(jīng)標(biāo)出了傳輸延遲,求該電路中流水線寄存器的最佳放置位置?求問大神解答這個題

2021-11-20 11:02:57

流水線技術(shù)基本原理是什么?設(shè)計DSP流水線應(yīng)注意哪些問題?

2021-04-28 06:10:03

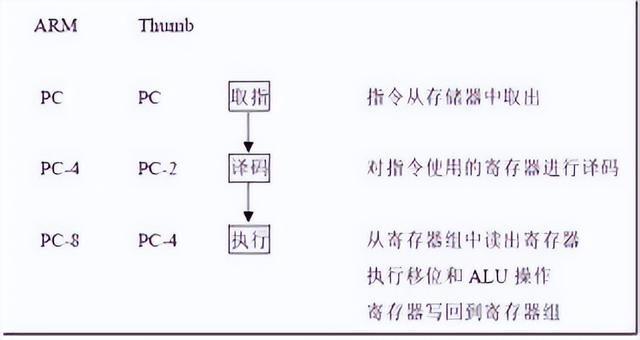

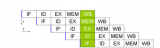

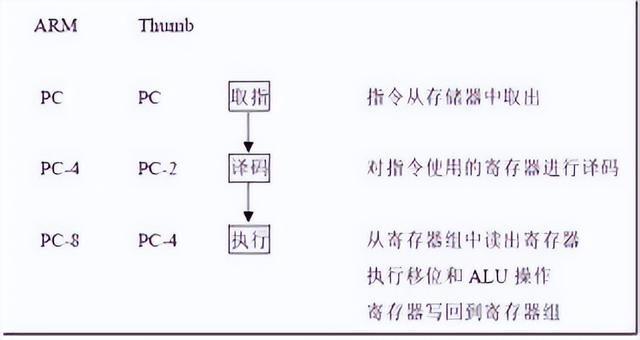

什么是ARM流水線流水線(Pipelining)是 RISC(精簡指令集)處理器用來執(zhí)行指令的機制,通過獲取指令來加速執(zhí)行,而其他指令同時被解碼和執(zhí)行。這反過來又允許內(nèi)存系統(tǒng)和處理器連續(xù)工作。每個

2022-04-11 17:23:19

設(shè)計的算法,如第一條中表述的流水線設(shè)計就是將組合邏輯系統(tǒng)地分割,并在各個部分(分級)之間插入寄存器,并暫存中間數(shù)據(jù)的方法。針對處理器中的流水線結(jié)構(gòu)。比如,比如 5—6 個不同功能的電路單元組成一條指令處理

2020-10-26 14:38:12

形式,分為直接型、級聯(lián)型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結(jié)構(gòu)、并行結(jié)構(gòu)、分布式結(jié)構(gòu)。本案例實現(xiàn)了具有線性相位的半串行結(jié)構(gòu)的FIR濾波器。所謂串行結(jié)構(gòu),即串行實現(xiàn)濾波器的累加運算,將每級延時

2017-08-02 17:35:24

QY-JDYT25數(shù)控模組化生產(chǎn)流水線綜合系統(tǒng)有什么作用?QY-JDYT25數(shù)控模組化生產(chǎn)流水線綜合系統(tǒng)是由哪些部分組成的?QY-JDYT25數(shù)控模組化生產(chǎn)流水線綜合系統(tǒng)有哪些特點?

2021-07-09 08:41:58

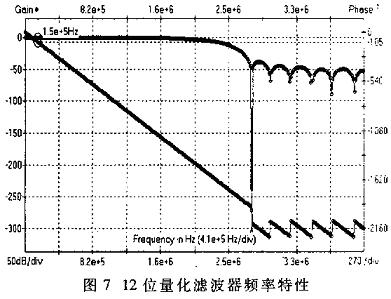

第37章FIR濾波器的實現(xiàn) 本章節(jié)講解FIR濾波器的低通,高通,帶通和帶阻濾波器的實現(xiàn)。 37.1 FIR濾波器介紹 37.2 Matlab工具箱生成C頭文件 37.3 FIR低通濾波器

2015-07-11 10:58:15

濾波器,即有限脈沖響應(yīng)濾波器,顧名思義,是指單位脈沖響應(yīng)的長度是有限的濾波器。而根據(jù)FIR濾波器的結(jié)構(gòu)形式,分為直接型、級聯(lián)型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結(jié)構(gòu)、并行結(jié)構(gòu)、分布式

2017-04-14 15:20:31

如何理解fpga流水線

2015-08-15 11:43:23

前段時間發(fā)了個關(guān)于fpga的PID實現(xiàn)的帖子,有個人說“整個算法過程說直白點就是公式的硬件實現(xiàn),用到了altera提供的IP核,整個的設(shè)計要注意的時鐘的選取,流水線的應(yīng)用”,本人水平有限,想請教一下其中時鐘的選取和流水線的設(shè)計應(yīng)該怎么去做,需要注意些什么,請大家指導(dǎo)一下。

2015-01-11 10:56:59

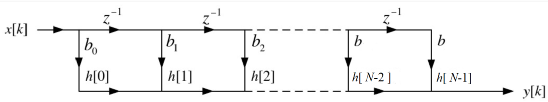

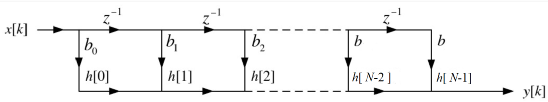

數(shù),濾波器階數(shù)為N-1。由上式可得到FIR濾波器在FPGA中的實現(xiàn)結(jié)構(gòu),如圖1所示,主要由延遲單元Z-1、乘法器和累加器組成。此結(jié)構(gòu)為直接型FIR濾波器結(jié)構(gòu),也稱橫向結(jié)構(gòu)(transverse)。FIR結(jié)構(gòu)

2021-12-15 06:30:00

本帖最后由 eehome 于 2013-1-5 09:50 編輯

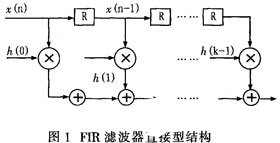

基于FPGA的FIR濾波器設(shè)計與實現(xiàn) 文章研究基于FPGA、采用分布式算法實現(xiàn)FIR濾波器的原理和方法,用

2012-08-11 15:32:34

系統(tǒng)兼具實時性和靈活性,而現(xiàn)有設(shè)計方案(如DSP)則難以同時達到這兩方面要求。而使用具有并行處理特性的FPGA實現(xiàn)FIR濾波器,具有很強的實時性和靈活性,因此為數(shù)字信號處理提供一種很好的解決方案。

2019-11-04 08:08:24

本文設(shè)計的FFT處理器,基于FPGA技術(shù),由于采用移位寄存器流水線結(jié)構(gòu),實現(xiàn)了兩路數(shù)據(jù)的同時輸入,相比傳統(tǒng)的級聯(lián)結(jié)構(gòu),提高了蝶形運算單元的運算效率,減小了輸出延時,降低了芯片資源的使用。

2021-04-28 06:32:30

本文首先介紹了FIR濾波器和脈動陣列的原理,然后設(shè)計了脈動陣列結(jié)構(gòu)的FIR濾波器,畫出電路的結(jié)構(gòu)框圖,并進行了時序分析,最后在FPGA上進行驗證。結(jié)果表明,脈動陣列的模塊化和高度流水線的結(jié)構(gòu)使FIR

2021-04-20 07:23:59

流水線模數(shù)轉(zhuǎn)換器(ADC)有哪些優(yōu)點?流水線ADC中常用的運算放大器有哪些?流水線ADC的放大器結(jié)構(gòu)及工作原理是什么?

2021-04-22 06:18:28

此示例顯示如何設(shè)計低通FIR濾波器。這里介紹的許多概念可以擴展到其他響應(yīng),如高通,帶通等。FIR濾波器被廣泛使用,因為它們具有強大的設(shè)計算法,以非遞歸形式實現(xiàn)時的固有穩(wěn)定性,可以輕松實現(xiàn)線性

2018-08-23 10:00:16

FIR濾波器的原理及結(jié)構(gòu)是什么基于分布式算法的FIR濾波器的實現(xiàn)

2021-05-08 08:39:41

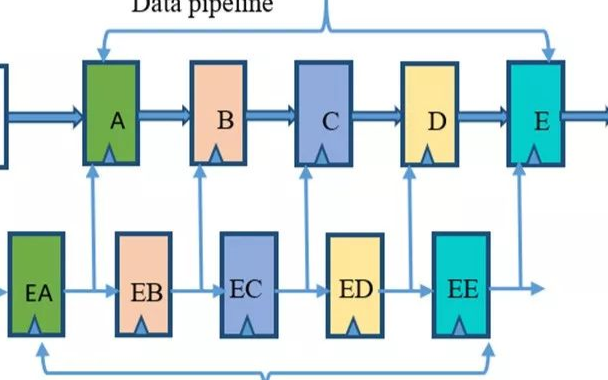

并行流水結(jié)構(gòu)FIR的原理是什么基于并行流水線結(jié)構(gòu)的可重配FIR濾波器的FPGA實現(xiàn)

2021-04-29 06:30:54

本文以實現(xiàn)抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實現(xiàn)FIR抽取濾波器的設(shè)計方法。

2021-05-07 06:02:47

濾波器獲得了更廣泛的應(yīng)用。FIR濾波器有多種設(shè)計和實現(xiàn)方法,最為常用的是基于分布式算法的FIR濾波器設(shè)計。

2019-08-23 06:39:46

濾波器獲得了更廣泛的應(yīng)用。FIR濾波器有多種設(shè)計和實現(xiàn)方法,最為常用的是基于分布式算法的FIR濾波器設(shè)計。

2019-08-27 07:16:54

本文將簡單介紹另一種數(shù)字濾波器——IIR濾波器的原理,詳細介紹使用Verilog HDL設(shè)計直接型IIR濾波器的方法。數(shù)字濾波器數(shù)字濾波器從實現(xiàn)結(jié)構(gòu)上劃分,有FIR和IIR兩種。FIR的特點是:線性

2020-09-27 09:22:58

: 2.1 FIR數(shù)字濾波器與流水線結(jié)構(gòu) 現(xiàn)代微處理器、數(shù)字信號處理器、高速數(shù)字系統(tǒng)設(shè)計中都廣泛應(yīng)用了流水線(Pipelining)技術(shù),其核心設(shè)計思想是把一個周期內(nèi)執(zhí)行的邏輯操作分成幾步較小的操作,在

2011-02-24 14:20:18

性能為目標(biāo)。從此以后,流水線技術(shù)也被有效地應(yīng)用到CISC處理器的設(shè)計中。Intel i486是IA32體系結(jié)構(gòu)中的第一個流水線實現(xiàn)。Digital的VAX和Motorola的M68K的流水線版本在商業(yè)上也

2023-03-01 17:52:21

的作用;即DF(Digital Filter)是由差分方程描述的一類特殊的離散時間系統(tǒng)。它的功能是把輸入序列通過一定的運算變換成輸出序列。不同的運算處理方法決定了濾波器的實現(xiàn)結(jié)構(gòu)的不同。35.1.2

2016-09-29 08:23:26

轉(zhuǎn)dsp系列教程 本章節(jié)講解FIR濾波器的低通,高通,帶通和帶阻濾波器的實現(xiàn)。 37.1 FIR濾波器介紹 37.2 Matlab工具箱生成C頭文件 37.3 FIR低通濾波器設(shè)計 37.4 FIR

2016-09-29 08:32:34

。

FIR濾波器

一、定義:

FIR濾波器是有限長單位沖激響應(yīng)濾波器,又稱為非遞歸型濾波器,是數(shù)字信號處理系統(tǒng)中最基本的元件,它可以在保證任意幅頻特性的同時具有嚴格的線性相頻特性,同時其單位抽樣響應(yīng)

2023-05-29 16:47:16

與過去工廠管理模式相比,現(xiàn)代企業(yè)更注重品質(zhì)與效率特別是服務(wù)制造業(yè)。目前在同行業(yè)里普遍推行的理念是智能工廠( Smartfactory),其解決方案主要以智能自動化流水線 電子看板系統(tǒng) 來實現(xiàn)。該系統(tǒng)

2019-10-05 20:03:08

在ARM中,關(guān)于 LDR流水線,分支流水線,中斷流水線,其和 PC 之間的關(guān)系一直沒整明白,求大神詳解!!!

2019-04-30 07:45:25

FIR濾波器的原理及結(jié)構(gòu)是什么基于分布式算法的FIR濾波器的實現(xiàn)

2021-04-30 06:03:00

根據(jù)FIR濾波器的結(jié)構(gòu)形式,分為直接型、級聯(lián)型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結(jié)構(gòu)、并行結(jié)構(gòu)、分布式結(jié)構(gòu)。本案例實現(xiàn)了具有線性相位的半串行結(jié)構(gòu)的FIR濾波器。所謂串行結(jié)構(gòu),即串行實現(xiàn)

2017-05-23 10:11:26

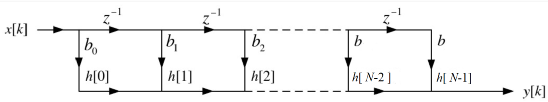

這一節(jié)主要講解一下轉(zhuǎn)置型FIR濾波器實現(xiàn)。 FIR濾波器的單位沖激響應(yīng)h(n)可以表示為如下式: 對應(yīng)轉(zhuǎn)置型結(jié)構(gòu)的FIR濾波器,如圖1所示,抽頭系數(shù)與上一節(jié)中講解直接型FIR濾波器的實例

2019-06-28 08:22:02

并網(wǎng)接口,容易產(chǎn)生諧振尖峰,影響整個系統(tǒng)的穩(wěn)定性。鑒于此,本文提出了一種基于LCL型濾波器的光伏并網(wǎng)逆變器的設(shè)計方案,該方案對光伏并網(wǎng)逆變器的直接轉(zhuǎn)矩控制策略進行了分析研究,通過仿真測試表明該逆變器

2018-09-29 16:39:11

提出了一種開關(guān)電容流水線結(jié)構(gòu)A/D轉(zhuǎn)換器(ADC)的速度分析方法。流水線結(jié)構(gòu)ADC的速度取決于其級電路中開關(guān)電容反饋放大器的建立速度。根據(jù)流水線結(jié)構(gòu)的特點,推導(dǎo)出輸入等效階

2008-12-03 13:02:29 30

30 針對并行爬蟲系統(tǒng)在多任務(wù)并發(fā)執(zhí)行時所遇到的模塊間負載平衡問題,提出流水線負載平衡模型(PLB),將不同的任務(wù)抽象為獨立模塊而達到各模塊的處理速度相等,采用多線程的方式

2009-03-31 10:19:30 19

19 流水線結(jié)構(gòu)的高效SAR快視成像處理器

2009-05-08 17:16:47 23

23 并行FIR濾波器具有速度快、容易設(shè)計的特點,但是要占用大量的資源。在多階數(shù)的亞高頻系統(tǒng)設(shè)計中,使用并

2009-07-21 16:55:06 0

0 本文綜合介紹了基于FPGA 軟件Quartus II 和MATLAB 的FIR 濾波器的設(shè)計仿真,將兩大軟件綜合運用后大大縮減了設(shè)計研發(fā)的時間,在算法結(jié)構(gòu)上利用了流水線等優(yōu)化方式。

2009-11-30 14:21:09 117

117 使用軟件仿真硬件流水線是很耗時又復(fù)雜的工作,仿真過程中由于流水線的沖突而導(dǎo)致運行速度緩慢。本文通過對嵌入式處理器的流水線, 指令集, 設(shè)備控制器等內(nèi)部結(jié)構(gòu)的分析和

2009-12-31 11:30:21 9

9 FIR并行濾波器設(shè)計

數(shù)字濾波器可以濾除多余的噪聲,擴展信號頻帶,完成信號預(yù)調(diào),改變信號的特定頻譜分量,從而得到預(yù)期的結(jié)果。數(shù)字濾波器在DVB、

2008-01-16 09:47:09 1270

1270

基于流水線技術(shù)的并行高效FIR濾波器設(shè)計

基于流水線技術(shù),利用FPGA進行并行可重復(fù)配置高精度的FIR濾波器設(shè)計。使用VHDL可以很方便地改變濾波器的系數(shù)和階數(shù)。在DSP中采用

2009-03-28 15:12:27 737

737

摘要: 提出了一種采用現(xiàn)場可編碼門陣列器件(FPGA)并利用窗函數(shù)法實現(xiàn)線性FIR數(shù)字濾波器的設(shè)計方案,并以一個十六階低通FIR數(shù)字濾波器電路的實現(xiàn)

2009-06-20 14:05:46 1057

1057

什么是流水線技術(shù)

流水線技術(shù)

2010-02-04 10:21:39 3702

3702 采用DSPBuilder的FIR濾波器的方案實現(xiàn)

1.引言

在信息信號處理過程中,如對信號的過濾、檢測、預(yù)測等,都要使用濾波器,數(shù)字濾波器是數(shù)字信號處

2010-03-04 17:09:38 738

738

流水線中的相關(guān)培訓(xùn)教程[1]

學(xué)習(xí)目標(biāo)

理解流水線中相關(guān)的分類及定義;

2010-04-13 15:56:08 869

869 流水線中的相關(guān)培訓(xùn)教程[3]

(1) 寫后讀相關(guān)(RAW:Read After Write) (命名規(guī)則) :j 的執(zhí)行要用到 i 的計算結(jié)果,當(dāng)它們在流水線中重疊執(zhí)行時,j 可

2010-04-13 16:02:57 773

773 流水線中的相關(guān)培訓(xùn)教程[4]

下面討論如何利用編譯器技術(shù)來減少這種必須的暫停,然后論述如何在流水線中實現(xiàn)數(shù)據(jù)相關(guān)檢測和定向。

2010-04-13 16:09:15 4272

4272 本文通過改變通常FIR處理結(jié)構(gòu),有效地節(jié)省了資源,只使用了一套乘加器,一套FIR濾波器結(jié)構(gòu),就完成了兩套FIR濾波器的功能,

2011-05-13 09:32:32 4233

4233

基于流水線技術(shù),利用FPGA進行并行可重復(fù)配置高精度的 FIR濾波器 設(shè)計。使用VHDL可以很方便地改變濾波器的系數(shù)和階數(shù)。在DSP中采用這種FIR濾波器的設(shè)計方法可以充分發(fā)揮FPGA的優(yōu)勢。

2011-07-18 17:09:28 63

63 cpu流水線技術(shù)是一種將指令分解為多步,并讓不同指令的各步操作重疊,從而實現(xiàn)幾條指令并行處理,以加速程序運行過程的技術(shù)。

2011-12-14 15:29:24 4476

4476 描述了基于FPGA的FIR濾波器設(shè)計。根據(jù)FIR的原理及嚴格線性相位濾波器具有偶對稱的性質(zhì)給出了FIR濾波器的4種結(jié)構(gòu),即直接乘加結(jié)構(gòu)、乘法器復(fù)用結(jié)構(gòu)、乘累加結(jié)構(gòu)、DA算法。在本文中給

2012-11-09 17:32:37 121

121 電鍍流水線的PLC控制電鍍流水線的PLC控制電鍍流水線的PLC控制

2016-02-17 17:13:04 35

35 裝配流水線控制系統(tǒng)設(shè)計

2016-12-17 15:26:59 13

13 一種改進運放共享結(jié)構(gòu)的11位流水線ADC設(shè)計

2017-01-07 20:49:27 3

3 基于位并行DA結(jié)構(gòu)的高速FIR濾波器_周云

2017-01-07 21:39:44 4

4 FIR濾波器,即有限脈沖響應(yīng)濾波器,顧名思義,是指單位脈沖響應(yīng)的長度是有限的濾波器。而根據(jù)FIR濾波器的結(jié)構(gòu)形式,分為直接型、級聯(lián)型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結(jié)構(gòu)、并行結(jié)構(gòu)、分布式結(jié)構(gòu)。本案例實現(xiàn)了具有線性相位的半串行結(jié)構(gòu)的FIR濾波器。

2017-04-20 14:42:14 2186

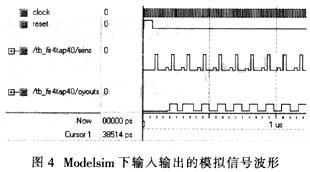

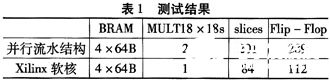

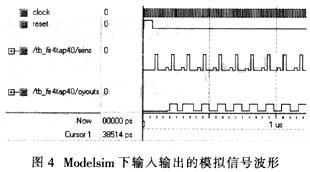

2186 摘要:有限沖擊響應(yīng)(FIR)濾波器是數(shù)字通信系統(tǒng)中常用的基本模塊。文章設(shè)計了一種流水結(jié)構(gòu)的FIR濾波器,通過FPGA對其進行硬什加速控制。仿真結(jié)果驗證了所設(shè)計的FIR流水結(jié)構(gòu)濾波器功能的正確性

2017-11-18 06:15:02 1259

1259

線性相位FIR濾波器的對稱性減小了硬件規(guī)模;利用分割查找表的方法減小了存儲空間;采用并行分布式算法結(jié)構(gòu)和流水線技術(shù)提高了濾波器的速度,在FPGA上實現(xiàn)了該濾波器。

2017-11-24 15:17:27 2942

2942 分是采用分布式算法設(shè)計基于FPGA的實現(xiàn)結(jié)構(gòu),完全避免了乘法運算,資源優(yōu)化性高;第三部分通過對FPGA的濾波器設(shè)計方案進行仿真驗證,并與使用Matlab模擬濾波算法產(chǎn)生的波形進行比較,兩者能夠達到幾乎一致,得出電路設(shè)計合理,濾波效果達標(biāo)的結(jié)論。

2017-12-07 16:22:09 6

6 本文針對快速、準(zhǔn)確選擇參數(shù)符合項目要求的濾波器設(shè)計方法的目的,通過系統(tǒng)的介紹有限脈沖響應(yīng)( Finite Impulse Response,FIR)濾波器的原理、結(jié)構(gòu)形式以及幾種FIR濾波器設(shè)計方法

2017-12-21 14:53:14 14

14 本文將討論處理器的一個重要的基礎(chǔ)知識:流水線。熟悉計算機體系結(jié)構(gòu)的讀者一定知道,言及處理器微架構(gòu),幾乎必談其流水線。處理器的流水線結(jié)構(gòu)是處理器微架構(gòu)最基本的一個要素,猶如汽車底盤對于汽車一般具有基石性的作用,它承載并決定了處理器其他微架構(gòu)的細節(jié)。

2018-04-08 08:16:00 21822

21822

顏色表示了不同階段的可配置性或可編程性:綠色表示該流水線階段是完全可編程控制的,黃色表示該流水線階段可以配置但不是可編程的,藍色表示該流水線階段是由GPU固定實現(xiàn)的,開發(fā)者沒有任何控制權(quán)。實線表示該shader必須由開發(fā)者編程實現(xiàn),虛線表示該Shader是可選的.

2018-05-04 09:16:00 3613

3613

本文詳細講述了通過Matlab工具設(shè)計FIR線性相位濾波器的方法, 并針對聲波信號設(shè)計了優(yōu)于傳統(tǒng)結(jié)構(gòu)的流水線CSD-DA結(jié)構(gòu), 該結(jié)構(gòu)具有較明顯的速度和面積優(yōu)勢。文中也通過仿真實驗證實了設(shè)計的合理性

2018-08-12 09:33:37 3958

3958

在基本A/D轉(zhuǎn)換結(jié)構(gòu)中,有些具備高速性能,有些具備高精度性能,沒有能夠同時達到高速高精度的要求。流水線ADC的出現(xiàn)在一定程度上解決了這個難題。流水線結(jié)構(gòu)可以在采樣速度和轉(zhuǎn)換精度之間取得較好的平衡。圖1是三級流水線ADC的結(jié)構(gòu)。

2019-06-08 09:39:00 2492

2492

第一部分什么是流水線 第二部分什么時候用流水線設(shè)計 第三部分使用流水線的優(yōu)缺點 第四部分流水線加法器舉例 一. 什么是流水線 流水線設(shè)計就是將組合邏輯系統(tǒng)地分割,并在各個部分(分級)之間插入寄存器

2018-09-25 17:12:02 4370

4370 自動化流水線是一個統(tǒng)稱,包括組裝流水線、皮帶流水線、鏈板線、插件線等等,主要通過自動化系統(tǒng)來操作運行,不需要人工操作。

2019-05-22 06:06:00 6328

6328 流水線的平面設(shè)計應(yīng)當(dāng)保證零件的運輸路線最短,生產(chǎn)工人操作方便,輔助服務(wù)部門工作便利,最有效地利用生產(chǎn)面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置時應(yīng)考慮流水線的形式、流水線安裝工作地的排列方法等問題。

2019-11-28 07:07:00 2039

2039 流水線在工業(yè)生產(chǎn)中扮演著重要的角色,優(yōu)化流水線直接關(guān)系著產(chǎn)品的質(zhì)量和生產(chǎn)的效率,因此成為企業(yè)不得不關(guān)注的話題。

2019-11-28 07:05:00 2088

2088 流水線又稱為裝配線,一種工業(yè)上的生產(chǎn)方式,指每一個生產(chǎn)單位只專注處理某一個片段的工作。以提高工作效率及產(chǎn)量;按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2019-11-28 07:04:00 3232

3232 流水線在工廠生產(chǎn)線上運用非常廣泛。從產(chǎn)品原料到最終產(chǎn)品,工廠中的生產(chǎn)過程都是由各個生產(chǎn)工站實現(xiàn)。工站與工站之間的轉(zhuǎn)運,就是通過流水線實現(xiàn)。

2020-06-04 10:22:14 8336

8336

L倍,其中L為并行的路數(shù),并且運算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運算做了浮點仿真驗證。然后用經(jīng)典符號數(shù)表示以及優(yōu)化定點濾波器系數(shù),并針對濾波器系數(shù)設(shè)計了流水線結(jié)構(gòu)。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 15

15 L倍,其中L為并行的路數(shù),并且運算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運算做了浮點仿真驗證。然后用經(jīng)典符號數(shù)表示以及優(yōu)化定點濾波器系數(shù),并針對濾波器系數(shù)設(shè)計了流水線結(jié)構(gòu)。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 7

7 本文介紹一種基于SoPC的FIR濾波器設(shè)計方案,設(shè)計流程如圖l所示。該設(shè)計方法程序簡單,調(diào)試方便,得到的FIR濾波器精確度高。

2021-03-24 09:18:27 2712

2712

按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2021-07-05 11:12:18 6087

6087

,每個子過程由專門的功能部件來實現(xiàn)。? 把多個處理過程在時間上錯開,依次通過各功能段,這樣,每個子過程就可以與其他的子過程并行進行。流水線中的每個子過程及其功能部件稱為流水線的級或段,段與段相互連接形成流水線。流水線的段數(shù)稱為流水線的深度。二、表示流水線的表示方法:時空圖? 時空圖從時間和空間兩

2021-10-20 20:51:14 6

6 1989 年推出的 i486 處理器引入了五級流水線。這時,在 CPU 中不再僅運行一條指令,每一級流水線在同一時刻都運行著不同的指令。這個設(shè)計使得 i486 比同頻率的 386 處理器性能提升了不止一倍。

2022-09-22 10:04:23 1258

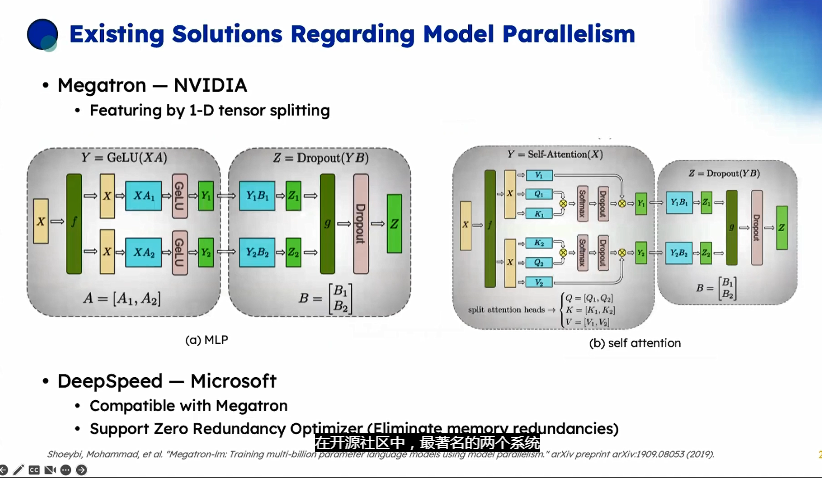

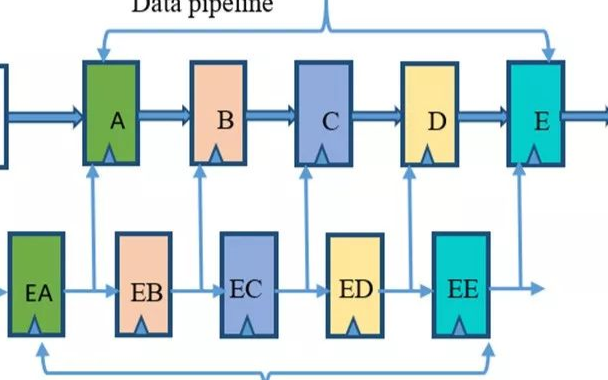

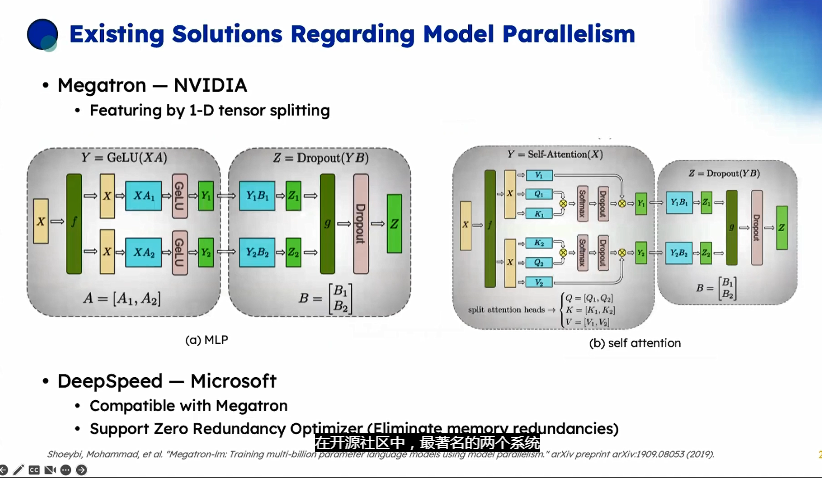

1258 張星并行和流水線并行技術(shù)通常被描述為模型并行,在開源社區(qū)中,最著名的兩個系統(tǒng)是NVIDIA的Megatron- M和Microsoft的DeepSpeed。

2023-03-23 17:21:29 1395

1395

FIR(Finite Impulse Response)濾波器是一種有限長單位沖激響應(yīng)濾波器,又稱為非遞歸型濾波器。FIR 濾波器具有嚴格的線性相頻特性,同時其單位響應(yīng)是有限長的,因而是穩(wěn)定的系統(tǒng),在數(shù)字通信、圖像處理等領(lǐng)域都有著廣泛的應(yīng)用。

2023-03-27 11:33:53 618

618

jenkins 有 2 種流水線分為聲明式流水線與腳本化流水線,腳本化流水線是 jenkins 舊版本使用的流水線腳本,新版本 Jenkins 推薦使用聲明式流水線。文檔只介紹聲明流水線。

2023-05-17 16:57:31 613

613 本文介紹了設(shè)計濾波器的FPGA實現(xiàn)步驟,并結(jié)合杜勇老師的書籍中的并行FIR濾波器部分進行一步步實現(xiàn)硬件設(shè)計,對書中的架構(gòu)做了復(fù)現(xiàn)以及解讀,并進行了仿真驗證。

2023-05-24 10:57:36 653

653

點擊上方 藍字 關(guān)注我們 本文將回顧對稱 F IR ? 濾波器 的高效 FPGA 實現(xiàn)的注意事項。 本文將推導(dǎo)對稱 FIR 濾波器的模塊化流水線結(jié)構(gòu)。我們將看到派生結(jié)構(gòu)可以使用? Xilinx

2023-05-26 01:20:02 441

441

FIR(Finite Impulse Response)濾波器是一種有限長單位沖激響應(yīng)濾波器,又稱為非遞歸型濾波器。

2023-06-01 11:11:34 821

821

![]()

電子發(fā)燒友App

電子發(fā)燒友App

評論