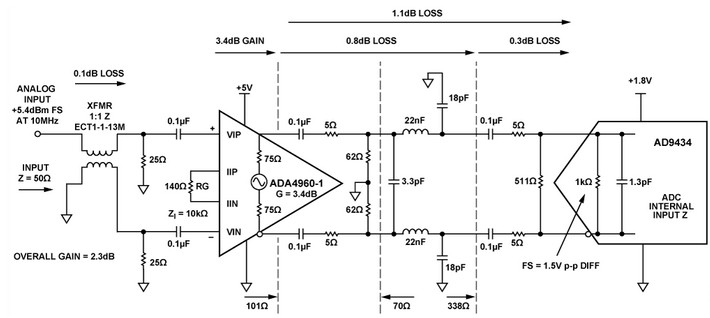

本部分說明放大器/ADC與濾波器的接口設計的一般方法。為了實現最佳性能(帶寬、SNR、SFDR等),必須考慮放大器和ADC對該一般電路的一些設計限制:

放大器應具有數據手冊針對最佳性能而推薦的合適直流負載。

放大器與濾波器提供的負載之間必須使用大小合適的串聯電阻,這是為了防止通帶中出現不合需要的峰化現象。

ADC的輸入應通過外部并聯電阻降低,并且應使用合適的串聯電阻將ADC與濾波器隔離。此串聯電阻也能降低峰化。

圖5所示的一般化電路適用于大多數高速差分放大器/ADC接口,將用作討論的基礎。這種設計方法利用多數高速ADC相對較高的輸入阻抗和驅動源(放大器)相對較低的阻抗,通常可以最大程度地降低濾波器的插入損耗。

基本設計流程如下:

選擇ADC外部端接電阻RTADC,使得RTADC 和RADC 的并聯阻抗介于200 Ω和400 Ω之間。

根據經驗和/或ADC數據手冊建議選擇RKB ,通常在5 Ω與36 Ω之間。

通過下式計算濾波器負載阻抗:

ZAAFL = RTADC || (RADC + 2RKB)

選擇放大器外部串聯電阻RA。如果放大器差分輸出阻抗在100 Ω至200 Ω之間,則RA。應小于10 Ω。如果放大器輸出阻抗為12 Ω或更小,則RA。應介于5 Ω和36 Ω之間。

選擇RTAMP ,使得放大器的總負載ZAL對于所選的特定差分放大器是最佳的,計算公式如下:

ZAL = 2RA + (ZAAFL || 2RTAMP)

計算濾波器源阻抗:

ZAAFS = 2RTAMP || (ZO + 2RA)

利用濾波器設計程序或表格,以及源阻抗ZAAFS 、負載阻抗ZAAFL、濾波器類型、帶寬、階數等,設計濾波器。帶寬應比采樣速率的一半高大約40%,以確保DC至fs/2頻率范圍內的平坦度足夠好。

程序產生的最終并聯電容值應減去ADC內部電容CADC。程序會給出差分并聯電容的值CSHUNT2 ,最終共模并聯電容為CAAF2 = 2(CSHUNT2 – CADC)。

完成上述初步計算后,應快速檢查一下電路的下列項目。

CAAF2的值應比 CADC大好幾倍,至少應為10 pF。這是為了最大程度地降低濾波器對 CADC變化的敏感度。

ZAAFL 與 ZAAFS 的比值應等于或小于7左右,使得該濾波器在大多數濾波器表格和設計程序的限制以內。

CAAF1的值至少應為5 pF,以便最大程度地降低濾波器對寄生電容和組件變化的敏感度。

電感 LAAF的值應合理,至少應有數nH。

某些情況下,濾波器設計程序提供的解決方案可能不止一個,特別是對于高階濾波器。此時應選擇組件值組合最為合理的一種解決方案。此外,所選的配置應結束于并聯電容,以便能與ADC輸入電容結合。

電路優化技術和權衡

該接口電路的參數相互影響,因此,幾乎無法優化電路的所有關鍵特性(帶寬、帶寬平坦度、SNR、SFDR、增益等)。然而,通過改變 RA 和 RKB,可以最大程度地降低通常出現在帶寬響應中的峰化。

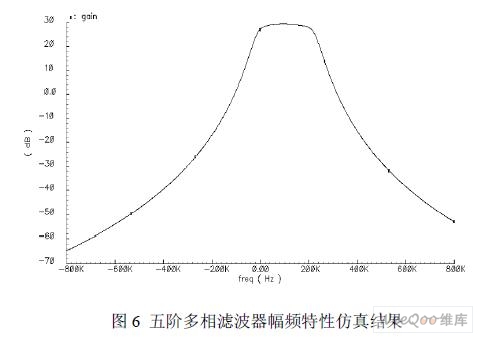

請注意圖6中通帶峰化如何隨著輸出串聯電阻RA的值提高而降低。但是,此電阻的值越高,信號衰減就越大,放大器必須驅動更大的信號以填充ADC的滿量程輸入范圍。

RA 的值也會影響SNR性能。較大的值一方面會降低帶寬峰化,但另一方面,往往也會略微提高SNR,因為驅動ADC滿量程所需的信號電平更高。

ADC輸入端串聯電阻RKB的選擇應能最大程度地降低ADC內部采樣電容的任何殘余電荷注入引起的失真。提高此電阻往往也會降低帶寬峰化。

但是,提高 RKB 會使信號衰減增大,放大器必須驅動更大的信號以填充ADC的輸入范圍。優化通帶平坦度的另一個辦法是少許改變濾波器并聯電容CAAF2。

ADC輸入端接電阻RTADC的選擇一般應使ADC凈輸入阻抗介于200 Ω和400 Ω之間。降低其值會降低ADC輸入電容的影響,并且可能使濾波器設計更加穩定,但不利的一面是會增大電路的插入損耗。提高其值也會降低峰化。

圖6. 通帶平坦度性能與放大器輸出串聯電阻RA的關系

要在這些因素之間取得平衡可能比較困難。本設計對每個參數一視同仁,因此,所選的值代表了所有設計特點的接口性能。某些設計中,根據系統要求,可能會選擇不同的值,以便優化SFDR、SNR或輸入驅動電平。

本設計的SFDR性能取決于兩個因素:圖1所示的放大器和ADC接口組件值,以及AD9467通過內部寄存器的內部前端緩沖偏置電流設置。表1和圖4所示的最終SFDR性能數值是在按照AD9467數據手冊所述優化SFDR之后獲得的。

該特定設計中可以權衡的另一個因素是ADC滿量程設置。對于利用此設計(優化SFDR)獲得的數據,ADC滿量程差分輸入電壓設置為2 V p-p。滿量程輸入范圍變為2.5 V p-p可以使SNR性能提高大約1.5 dB,但會略微降低SFDR性能。輸入范圍由載入AD9467內部寄存器的值設置,詳情參見數據手冊。

注意,本設計中的信號通過0.1 μF電容交流耦合,以便抑制放大器、其端接電阻與ADC輸入端之間的共模電壓。有關共模電壓的更多信息,請參閱AD9467數據手冊。

無源組件和PCB寄生效應考慮

該電路或任何高速電路的性能都高度依賴于適當的PCB布局,包括但不限于電源旁路、受控阻抗線路(如需要)、組件布局、信號布線以及電源層和接地層。有關高速ADC和放大器的PCB布局布線詳細信息,請參閱教程MT-031 和 MT-101。

濾波器中的無源組件應使用低寄生效應的表貼電容、電感和電阻。所選的電感為Coilcraft 0603CS系列。濾波器使用的表貼電容為5%、C0G、0402型,以確保穩定性和精度。

常見變化

針對要求較窄帶寬、較低功耗的應用,可以使用差分放大器 ADL5561 。ADL5561的帶寬為2.9 GHz,功耗僅40 mA。如果要求更低的功耗和帶寬,也可以使用ADA4950-1 ,其帶寬為1 GHz,功耗僅10 mA。如需更高的帶寬,可以使用6 GHz差分放大器ADL5565,它與上述器件引腳兼容。

電路評估與測試

本電路使用修改的AD9467-250EBZ 電路板和基于 HSC-ADC-EVALCZ FPGA的數據采集板。這兩片板具有對接高速連接器,可以快速完成設置并評估電路性能。修改的AD9467-250EBZ板包括本筆記所述的評估電路,HSC-ADC-EVALCZ數據采集板與Visual Analog評估軟件一起使用,此外還使用SPI控制軟件器來適當控制ADC并采集數據。

電子發燒友App

電子發燒友App

評論