自從馬可尼發明無線電以來,無線通信技術一直向著不斷提高數據速率和傳輸距離的方向發展。而當前被廣泛研究的ZigBee 技術則正是一種為人們提供廉價的、極低復雜度、低成本和低功耗的低速率無線通信技術。這種無線技術具有功耗低、數據傳輸可靠、網絡容量大、兼容性好、安全性能高、成本低和時延短等特點受到廣泛歡迎。

ZigBee 名字來源于蜂群使用的賴以生存和發展的通信方式,蜜蜂通過跳ZigZag 形狀的舞蹈來通知發現的食物源的位置、距離和方向等信息,以此作為該技術的名稱。ZigBee 過去又稱為“HomeRF Lite”、“RF-EasyLink”或“FireFly”無線電技術,現統一稱為ZigBee技術。目前ZigBee技術被廣泛應用于物聯網系統,如智能家居、煤礦監控、電梯物聯網等,ZigBee電路設計的好壞直接影響物聯網系統運行的穩定性和可靠性。

ZigBee 兼容的產品工作在IEEE802.15.4 的PHY 上,其頻段是免費開放的,分別為2.4GHz(全球)、915MHz(美國)和868MHz(歐洲)。本文研究的技術采用的ZigBee產品工作頻段為2.4GHz,該頻段比傳統信號傳輸速度高出許多倍,因此板卡的設計要求也復雜很多。采用傳統的PCB設計經驗是無法滿足該射頻板的要求,我們需要采用針對射頻電路板的新技術--信號完整性仿真技術。

1微帶線阻抗匹配仿真與計算

1.1特征阻抗定義

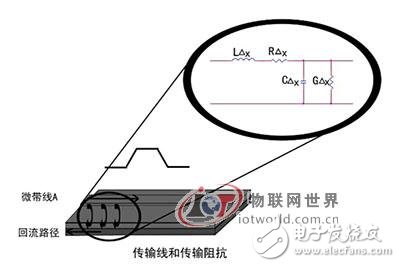

對于高速電路來講,當我們討論傳輸線時,不僅要考慮由于高速信號而引入的新的頻率因素,還要考慮由于高速信號傳輸而形成的不同的電路結構。理論上講,傳輸線是由傳輸信號的信號線,即圖中的微帶線A,和該信號構成參考回流路徑構成的。這種結構,是由傳輸線上的信號特征決定的,再次強調,我們討論的不是導線上直流穩態的靜電場分析,我們面臨的問題是在高速信號傳輸過程中瞬時電磁場的交替建立過程。所以,請特別注意,能夠為信號線提供回流路徑的不僅僅是通常意義的地平面,任何能夠和信號線之間建立電磁場聯系的導體,都能夠和信號線之間建立傳輸線。而我們研究的對象是所有這些傳輸線結構中,能夠最有效提供回流路徑的那對傳輸線結構。正如下圖中所示的那樣,對于高速信號的傳輸線,其能量的傳播是依靠電磁場在傳輸介質上的交替變化完成的,那么它的傳輸路徑包含了:微帶線本身、回流路徑、以及微帶線和回流路徑之間的介質。所以,對于一個特定的傳輸線而言,信號線和回流路徑之間構成的是一個雙端口網絡。而其阻抗,即是構成等效電路的各個因素的綜合結果。

當理解了這樣的信號傳輸結構之后,就不難理解分辨傳輸線阻抗和電阻的區別了。當談到傳輸線的阻抗時,是絕對不能用導體A的電阻來替代的,它實質是在該傳輸介質中某一點上所建立的電場及流經該點的電流之間的關系,所構成的傳輸介質上的電場。因此談到傳輸線的阻抗,讀者一定要建立起“兩個導體”的結構概念,而不僅僅是那個顯而易見的微帶線A。缺少了參考回流路徑,單一的微帶線A是無法建立電場的。

當信號在傳輸線上傳輸時,每向前傳輸一個最小單元的等效電路,都要在所經過的路徑上建立相應的電磁場,并且有一定的電流流經等效電路。這個最小單元的等效電路構成的阻抗,相對傳輸線來講,就是此時此刻的瞬時阻抗。如果信號在此傳輸線上傳輸時,每個瞬時阻抗都完全一致,那么就將瞬時阻抗定義為該傳輸線的特征阻抗。

1.2微帶線概念

在PCB中,微帶線是一種用電介質將導線與接地面隔開的傳輸線。印制跡線的厚度、寬度和跡線與接地面間介質的厚度,以及電介質的介電常數,決定微帶線的特征阻抗的大小。

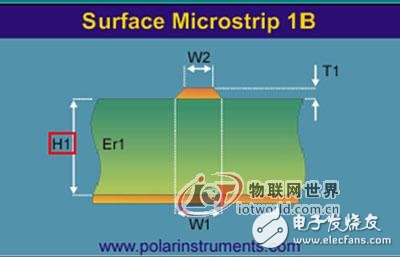

微帶線的幾何結構如圖-1所示,導帶的寬度W印在薄的接地的介質基片上。

圖-1

W1和W2:傳輸線上下表面寬度;

T1:傳輸線的銅厚,如一盎司;

H1:介質的厚度;

底面銅皮為傳輸線的參考平面,可為地平面也可以是電源平面。

根據“IPC-2141”規范,推薦的使用的微帶線參數計算公式如下:公式-1

微帶線特征阻抗計算公式:

Z0 ={87/[sqrt(Er+1.41)]}*ln[5.98H/(0.8W+T)] 公式-1

其中,W為線寬,T為走線的銅皮厚度,H為走線到參考平面的距離,Er是PCB板材質的介電常數。此公式必須在0.1《(W/H)《2.0,并且1《(Er)《15。

微帶線的寬度W越大,微帶線的特征阻抗Z0就越低。近似公式在微帶線寬度W遠大于介質厚度t時的精度較高,否則就需要加以修正。當W與t相當時,誤差約為百分之幾到百分之十幾。其中微帶線的寬度W遠大于介質厚度t也正是當前PCB工藝所能實現的。

但對于PCB設計工程師來說,要控制PCB微帶線的特征阻抗,如果依靠上述公式計算非常不方便。在前些年,沒有專業的特征阻抗仿真軟件,當PCB需要做阻抗匹配時工程師要花費很多時間來計算微帶線的模型。后來POLAR SI8000軟件的誕生給阻抗匹配計算帶來了巨大的便利,目前全球大約有一半以上的PCB廠家都采用該軟件計算PCB傳輸線的特征阻抗。該軟件不僅使用簡單,阻抗匹配精度高,軟件提供了多種PCB傳輸線的模型。本文僅介紹如何用SI8000設計ZigBee模塊微帶線的特征阻。

因ZigBee射頻信號傳輸線的模型為微帶線,并且特征阻抗為50歐姆,根據PCB廠家的實際工藝要求,如果銅的厚度為1盎司,只需通過SI8000軟件計算出該微帶線的寬度即可控制該微帶線的特征阻抗。

具體步驟:運行SI8000軟件,界面如下圖-2所示,選擇微帶線的模型為:Surface Microstrip 1B。第一層到第二層的厚度H1為4.5mil,微帶線的上下線寬相差(W1-W2)1mil,上表面線寬設為7mil,則下表面線寬8mil,介電參數為4.2,銅厚為1盎司,計算出來微帶線特征阻抗正好為51歐姆,滿足±10%的誤差要求。

圖-2

2 射頻輸出微帶線特征阻抗為何要匹配

在高頻信號傳輸途徑,特征阻抗必須始終保持一致,一旦傳輸途徑的特征阻抗有突變,就會因阻抗突變引起的信號完整性問題。典型的信號完整性問題就是信號反射、信號過沖,更嚴重會引起振鈴。表現出的問題為信號傳輸波形發生扭曲、信號邊沿出現過沖、信號輸出功率變小、EMI輻射超標等問題。下面我們通過Hyper Lynx信號完整性仿真軟件,介紹2.4G射頻板阻抗不匹配引起的幾種問題。

Hyper Lynx仿真軟件是PADS公司開發的一款信號完整性仿真軟件,該軟件主要用于高速電路設計的仿真與應用。該軟件可以仿真信號傳輸線的特征阻抗、傳輸線EMI輻射、傳輸線磁場分布情況、傳輸線時序等很多問題,該軟件為高速電路設計帶來了極大的方便。

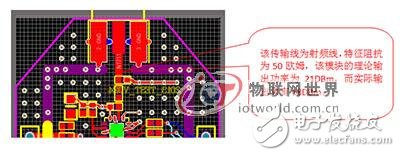

本人在設計2.4G ZIGBEE模塊時,第一版因射頻輸出線特征阻抗沒有計算好,導致該模塊輸出功率偏小,EMI輻射超標且模塊的接收靈敏度較低。第一版模塊如下圖-3所示

圖-3

2.1阻抗不匹配導致射頻信號輸出功率變小

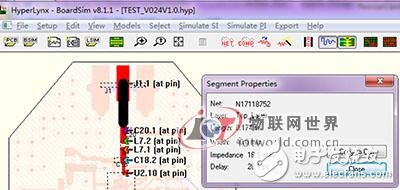

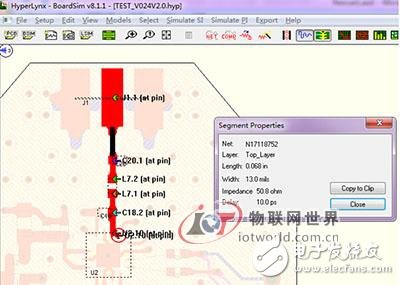

利用Hyper Lynx仿真軟件計算圖-3模塊的射頻傳輸線,特征阻抗值為16.5歐姆,如下圖-4,

圖-4

通過圖-4可以得知,該傳輸線的特征阻抗的實際值和理論值偏離過大,導致射頻信號輸出時引起信號完整性問題,最直觀的表現就是輸出功率偏小。理論值為21DBm,實際值為18DBm,也就是說這根傳輸線上損失功率為3DBm。為了驗證我們的分析是否正確,通過網絡分析儀直接測量PCB板的射頻傳輸線的損耗值。經測量,該值為2.95DBm,剛好符合分析結果。

2.2阻抗不匹配導致射頻板接收靈敏度降低

我們再對該板卡做接收靈敏度測量,經測量,該板卡接收靈敏度,比市場上其他公司設計的模塊的接收靈敏度低。該模塊采用的運放的接收靈敏度值為-115DBm,而實際測量下來只有-107DBm。初步分析,可能是因傳輸線的阻抗不連續、阻抗突變引起的信號波形失真,最終導致接收靈敏度降低。只要通過支持2.4GHz的示波器看一下該板子的實際輸出波形即可,如果信號有失真,則分析的結果就沒有問題。但是,目前很少能找到速度超過1GHz的示波器,要找到2.4GHz的示波器就更難了。不過雖然2.4GHz的示波器實物不好找,我們可以通過仿真軟件來驗證該問題。

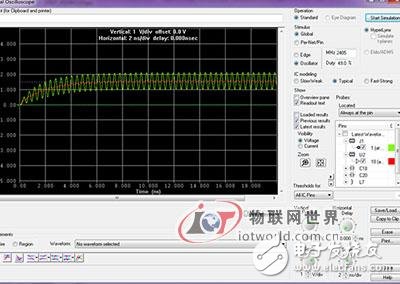

Hyper Lynx仿真軟件有個高速示波器仿真功能,通過該軟件,可以對該傳輸線在2.4G頻段的信號進行波形仿真,結果如圖-5所示,紅線為理論輸出波形,綠線為實際輸出波形,不難發現該波形有明顯的震蕩,和我們預期的分析結果相符合。

圖-5

2.3阻抗不匹配導致射頻板EMI輻射超標

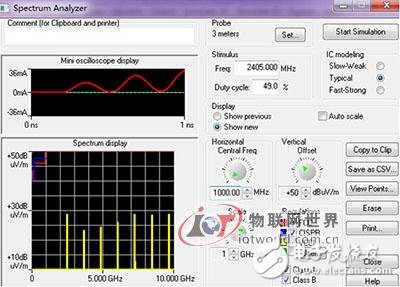

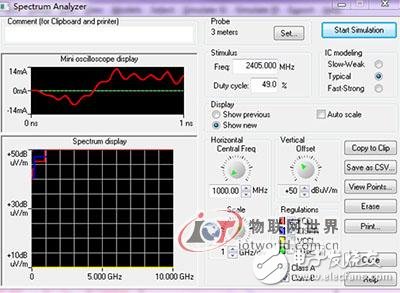

同樣,對該板子做EMI輻射測試,發現該板子的EMI輻射在2.4GHz到5GHz的范圍超過CE標準。通過Hyper Lynx仿真軟件的虛擬頻譜分析儀仿真結果如下圖-6所示。

圖-6

圖中黃色凸起代表EMI輻射在不同頻段的分量,很明顯EMI輻射從2.4G開始一直到10GHz都很強。

綜上所述,因特殊阻抗不匹配,導致第一版2.4GHz射頻板存在以下三個問題:

1、輸出功率小;

2、接收靈敏度低;

3、EMI輻射超出CE標準。

重新計算好傳輸線特征阻抗,改版后的特征阻抗如下圖-7所示,特征阻抗值為50.8歐姆。

圖-7

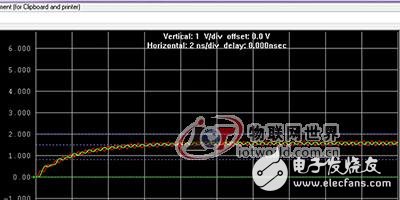

板子傳輸線的波形仿真如下圖-8所示,實際輸出波形幾乎和理論波形相同。

圖-8

再對板子進行EMI輻射仿真,結果如圖-9所示,新板子在10GHz范圍內EMI輻射幾乎看不到。

圖-9

經過測量,改版后的射頻板的輸出功率大于20DBm,接收靈敏度也比之前板子的高,EMI輻射也滿足各種標準的要求。

3 微帶線特征阻抗為何要滿足50歐姆

ZigBee射頻PA輸出的特征阻抗為50歐姆,天線的特征阻抗也為50歐姆,此時只有傳輸線的特征阻抗為50歐姆時,信號輸出功率最大,并且產生的信號完整性問題也最少。

4 結束語

眾所周知,ZigBee無線射頻技術被廣泛應用于物聯網系統中,但2.4G ZigBee射頻板設計難度相對要高,需要注意的問題也比較多,因此在一定程度上限制了該技術的應用范圍。如果在設計的過程中能夠掌握一些好的仿真工具,這樣可以提高設計的效率,降低設計風險,從而減少產品的開發周期,最終達到減少開發費用的目的。Hyper Lynx仿真軟件的推出給高速電路設計帶來了很大的便利,通過該軟件可以縮短產品的開發周期,可以在PCB設計就能得知電路板存在的許多EMC問題,提前預防產品存在的風險。

電子發燒友App

電子發燒友App

評論