高速數(shù)字電路的仿真

介紹了專用于高速數(shù)字電路的仿真工具Hyperlynx,并使用它對(duì)高速數(shù)字電路中的阻抗匹配、傳輸線長(zhǎng)度

2009-03-20 14:11:39 1275

1275

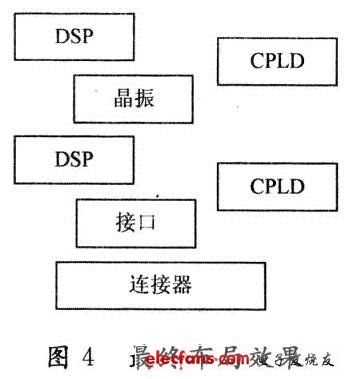

由于本系統(tǒng)是由多片ADSP-TS101組成的系統(tǒng),所以由40 MHz晶振產(chǎn)生的時(shí)鐘信號(hào)不能直接接到各DSP和FPGA,而應(yīng)該通過(guò)驅(qū)動(dòng)后再接到各DSP,且時(shí)鐘信號(hào)到各DSP的距離應(yīng)該盡可能接近。本系統(tǒng)

2020-11-02 10:36:31 2146

2146

用于多處理TigerSHARC系統(tǒng)的集群總線通信的詳細(xì)信號(hào)完整性和時(shí)序分析。該系統(tǒng)由8個(gè)ADSP-TS101S器件,一個(gè)主處理器和SDRAM組成,其集群總線運(yùn)行頻率為100MHz。包括仿真結(jié)果和物理

2019-08-30 09:24:28

數(shù)字電路-數(shù)字時(shí)鐘電路設(shè)計(jì) 希望大家喜歡。

2016-12-06 09:46:39

數(shù)字電路設(shè)計(jì)與Verilog HDL

2015-07-16 16:21:19

在數(shù)字電子技術(shù)基礎(chǔ)課程中,數(shù)字電路設(shè)計(jì)的數(shù)學(xué)基礎(chǔ)是布爾函數(shù),并利用卡諾圖進(jìn)行化簡(jiǎn)。卡諾圖只適用于輸入比較少的邏輯函數(shù)的化簡(jiǎn)。數(shù)字電路的設(shè)計(jì)方法是:組合電路設(shè)計(jì):提出問(wèn)題→確定邏輯關(guān)系→列真值表→邏輯

2019-02-27 11:55:00

華為的培訓(xùn)資料主要描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用。通過(guò)列舉很多的實(shí)例,作者詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴流、串?dāng)_和輻射噪音等問(wèn)題。

2012-08-14 20:26:07

【簡(jiǎn)介】本書從高速數(shù)字電路的定義談起,介紹了傳輸線的基本理論,并涉及到了如何運(yùn)用Grounding/Guard降低噪聲等內(nèi)容,還以高速數(shù)字電路電氣特性,如串?dāng)_、反射及時(shí)鐘脈沖不對(duì)稱等為例,闡述了一些

2017-12-12 08:51:55

《高速數(shù)字電路設(shè)計(jì)及EMC設(shè)計(jì)》分享。

2015-08-04 11:50:33

目 錄1. 高速數(shù)字電路設(shè)計(jì) 51.1何謂高速數(shù)字信號(hào)? 51.2微帶線、帶狀線的概念 51.2.1微帶線(Microstrip

2009-10-03 10:57:13

高速數(shù)字電路設(shè)計(jì)的幾個(gè)基本概念高速數(shù)字電路設(shè)計(jì)的基本要求是什么

2021-04-27 06:19:05

高速DAP仿真器 BURNER

2023-03-28 13:06:20

FPGA CPLFPGA CPLD 數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享FPGA/CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享摘要:在數(shù)字電路的設(shè)計(jì)中,時(shí)序設(shè)計(jì)是一個(gè)系統(tǒng)性能的主要標(biāo)志,在高層次設(shè)計(jì)方法中,對(duì)時(shí)序控制的抽象度也相應(yīng)

2012-08-11 10:17:18

本帖最后由 xianer317 于 2014-6-21 19:34 編輯

FPGA/CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享

2014-06-21 19:33:20

是行之有效的,通過(guò)許多設(shè)計(jì)實(shí)例證明采用這種方式可以使電路的后仿真通過(guò)率大大提高,并且系統(tǒng)的工作頻率可以達(dá)到一個(gè)較高水平。FPGA數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享[hide][/hide]

2012-03-05 16:33:30

FPGACPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享

2012-08-07 21:46:49

關(guān)于數(shù)字電路設(shè)計(jì)的一些經(jīng)驗(yàn)

2015-03-17 21:27:38

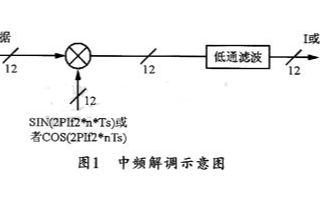

處理所要求的大數(shù)據(jù)吞吐能量、強(qiáng)數(shù)據(jù)計(jì)算能力,需要尋求一種基于高速數(shù)字電路的解決途徑。 TS101是美國(guó)AD公司最新推出的TigerSHARC系列DSP芯片,采用DMA引擎,主要針對(duì)嵌入式實(shí)時(shí)

2019-07-22 06:29:35

高的應(yīng)用,可以使用普通串行口作為通訊鏈路。在本系統(tǒng)中,由于采用多片高性能浮點(diǎn)數(shù)字信號(hào)處理器ADSP-TS101作為處理器,產(chǎn)生了大量的處理結(jié)果,并且要求實(shí)時(shí)傳輸處理結(jié)果,傳輸速度必須達(dá)到1 MB/s

2019-04-30 07:00:08

本帖最后由 gk320830 于 2015-3-5 07:26 編輯

華為高速數(shù)字電路設(shè)計(jì)-華為黑魔書

2012-08-28 17:04:52

簡(jiǎn)介:專門為電路設(shè)計(jì)工程師寫的。描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用。通過(guò)列舉很多的實(shí)例,詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴流、串?dāng)_和輻射噪音等問(wèn)題。這些東西在以前時(shí)間里大家都是

2018-01-22 17:32:54

本帖最后由 gk320830 于 2015-3-5 00:03 編輯

華為《高速數(shù)字電路設(shè)計(jì)教材》

2012-08-20 13:23:04

華為《高速數(shù)字電路設(shè)計(jì)教材》這本書是專門為電路設(shè)計(jì)工程師寫的。主要描述模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用

2014-09-01 23:09:11

華為《高速數(shù)字電路設(shè)計(jì)教材》這本書是專門為電路設(shè)計(jì)工程師寫的。主要描述模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用

2014-09-01 23:20:19

本帖最后由 午夜的沉默 于 2015-3-14 22:14 編輯

哪位有ADSP TS101S 芯片的Cadence原理圖封裝啊跪求 ..

2015-03-14 22:13:20

基于labview實(shí)現(xiàn)數(shù)字電路的仿真

2012-05-10 15:26:09

本帖最后由 eehome 于 2013-1-5 10:02 編輯

就算作一個(gè)數(shù)字電路設(shè)計(jì),附有 protuse仿真圖還有 相關(guān)用到的資料

2012-06-08 14:12:12

FPGA芯片是由哪些部分組成的?如何去實(shí)現(xiàn)一種基于FPGA芯片的可重構(gòu)數(shù)字電路設(shè)計(jì)?

2021-11-05 08:38:57

高速數(shù)字信號(hào)的阻抗匹配有什么作用?傳輸線長(zhǎng)度對(duì)高速數(shù)字電路的設(shè)計(jì)有什么影響?如何對(duì)高速數(shù)字電路進(jìn)行仿真測(cè)試?

2021-04-21 06:00:00

求一個(gè)解決系統(tǒng)中主處理器在較高工作頻率300 MHz下穩(wěn)定工作的問(wèn)題,以及在兩個(gè)主芯片之間和主芯片與數(shù)據(jù)存儲(chǔ)芯片之間數(shù)據(jù)高速互聯(lián)的問(wèn)題,提高系統(tǒng)的性能,滿足設(shè)計(jì)要求的基于ADSP-TS101高速信號(hào)處理系統(tǒng)。

2021-04-12 06:39:56

射頻和數(shù)字電路設(shè)計(jì)的區(qū)別是什么?

2021-05-18 06:05:19

怎么實(shí)現(xiàn)基于可編程邏輯器件的數(shù)字電路設(shè)計(jì)?

2021-05-06 08:36:18

大家好,我是電子愛(ài)好者新手,現(xiàn)在想學(xué)點(diǎn)數(shù)字電路設(shè)計(jì)。剛把數(shù)字電路這么課程學(xué)完。我想學(xué)電路設(shè)計(jì),不知道如何下手。比如FPGA什么的,這些都怎么開始學(xué)習(xí)啊。請(qǐng)知情者指點(diǎn)下。謝謝

2013-08-02 08:17:31

[獵頭職位]國(guó)家重要芯片研發(fā)中心職位:數(shù)字電路設(shè)計(jì)工程師【崗位職責(zé)】負(fù)責(zé)USB、MIPI等高速接口IP或AD/DA的數(shù)字電路設(shè)計(jì)【任職資格】1.電子工程、微電子等相關(guān)專業(yè)碩士以上學(xué)歷,兩年以上

2015-02-27 10:52:58

為什么淘寶上這本書的銷量那么低?有其他數(shù)字電路設(shè)計(jì)的實(shí)用書也可以推薦~謝謝!

2017-10-19 17:18:52

實(shí)踐技能差,無(wú)法達(dá)到高職教育人才培養(yǎng)的要求〔2)0 2開設(shè)數(shù)字電路設(shè)計(jì)性實(shí)驗(yàn)采取的措施 通過(guò)多年來(lái)的實(shí)驗(yàn)教學(xué)改革實(shí)踐,證明了開設(shè)設(shè)計(jì)性實(shí)驗(yàn)有利于鞏固課堂所學(xué)的理論知識(shí);有利于提高學(xué)生電子系統(tǒng)設(shè)計(jì)能力

2012-10-25 11:59:02

ADSP-TS101 是ADI 公司新一代高性能浮點(diǎn)DSP,開始應(yīng)用在高速數(shù)據(jù)采集和處理系統(tǒng)中。TS101 外部總線接口可編程,方便和各種總線外設(shè)接口。本文結(jié)合TS101 與同步FIFO、SDRAM 和FPGA 的接

2009-08-11 09:49:31 28

28 基于LabVIEW的數(shù)字電路設(shè)計(jì)和仿真

數(shù)字電路設(shè)計(jì)和仿真是電子工程領(lǐng)域的基本技術(shù)。介紹了基于LabV IEW的數(shù)字電路設(shè)計(jì)和仿真的原理和方法,比較了其與專業(yè)EDA軟

2010-03-30 16:09:49 123

123 本書是專門為電路設(shè)計(jì)師工程師寫的

它主要描述模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用

1-3章分別介紹了模擬電路術(shù)語(yǔ)、邏輯門高速特性和標(biāo)準(zhǔn)高速電路測(cè)量

2010-06-23 18:02:57 63

63 流水線技術(shù)在高速數(shù)字電路設(shè)計(jì)中的應(yīng)用

2010-07-17 16:37:21 6

6 這本書是專門為電路設(shè)計(jì)工程師寫的。它主要描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用。通過(guò)列舉很多的實(shí)例,作者詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴

2010-11-08 16:49:54 0

0 高速數(shù)字電路設(shè)計(jì)

關(guān)于高速數(shù)字電路的電氣特性,設(shè)計(jì)重點(diǎn)大略可分為三項(xiàng) : Ø 正時(shí) (Timing) :由于數(shù)字電路大多依據(jù)時(shí)脈信號(hào)來(lái)做信號(hào)間的同

2007-10-16 17:22:57 2746

2746 高速數(shù)字電路設(shè)計(jì)電容選型首選法則及實(shí)例分析關(guān)鍵詞:去耦(decouple)、旁路(Bypass)、等效串聯(lián)電感(ESL)、等效串聯(lián)電阻(ESR)、高速電路設(shè)計(jì)、電源完

2009-02-10 14:08:12 1387

1387 數(shù)字電路設(shè)計(jì)

關(guān)于高速數(shù)字電路的電氣特性,設(shè)計(jì)重點(diǎn)大略可分為三項(xiàng):

正時(shí)(Timing) :由于數(shù)字電路大

2009-08-26 19:08:06 2665

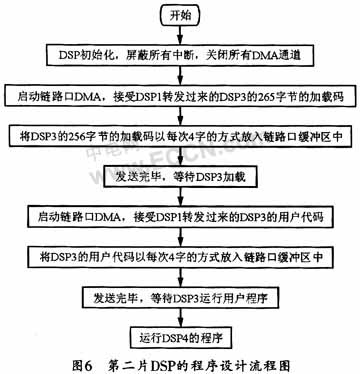

2665 多片TS101S的加載引導(dǎo)設(shè)計(jì)分析及實(shí)現(xiàn)

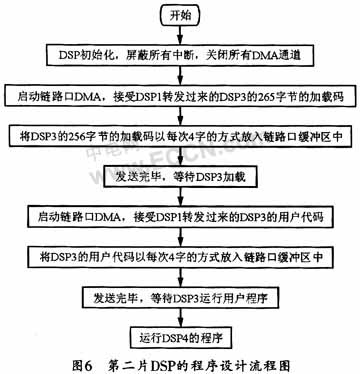

0 引言ADSP-TS101S數(shù)字信號(hào)處理器是美國(guó)ADI公司推出的TigerSHARC系列中的一款具有極高性能的靜態(tài)超標(biāo)量處理器。該處理器已

2010-03-31 10:20:26 1319

1319

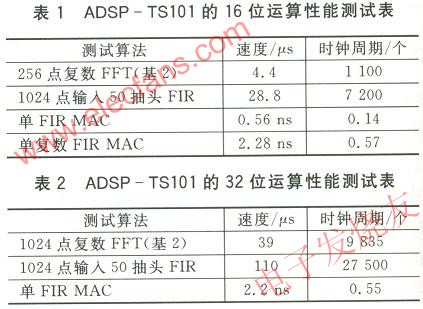

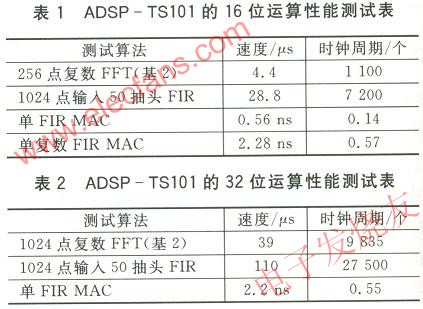

Adsp-TS101性能比ADSP21160有顯著提高,且與之兼容,使得以ADSP21160開發(fā)的產(chǎn)品升級(jí)快速、簡(jiǎn)捷。Adsp-TS101是64位處理器,工作在250 MHz時(shí)鐘下,可進(jìn)行32位定點(diǎn)和32位或40位浮點(diǎn)運(yùn)算,

2010-09-23 09:57:25 1776

1776

《VHDL與數(shù)字電路設(shè)計(jì)》是有盧毅、賴杰主編的,主要介紹涉及數(shù)字系統(tǒng)設(shè)計(jì)的多方面原理、技術(shù)及應(yīng)用,主要內(nèi)容有數(shù)字系統(tǒng)的基本設(shè)計(jì)思想、設(shè)計(jì)方法和設(shè)計(jì)步驟, VHDL 硬件描述語(yǔ)言

2011-07-11 15:54:27 0

0 主要內(nèi)容有:第1 章實(shí)驗(yàn)基本知識(shí)、第2 章 PROTEUS 仿真軟件快速入門、第3 章數(shù)字電路基礎(chǔ)實(shí)驗(yàn)、第4 章數(shù)字電路綜合設(shè)計(jì)實(shí)驗(yàn)、 第5章VHDL 語(yǔ)言基礎(chǔ)、第6 章 數(shù)字電路的CPLD/FPGA 實(shí)現(xiàn)。在教

2011-09-07 16:29:53 0

0 本文介紹了一種通用信號(hào)處理模塊設(shè)計(jì)方法,該模塊選用高性能浮點(diǎn)DSP 芯片ADSP-TS101 實(shí)現(xiàn)各種信號(hào)處理功能,以可靠性高、開放性好、通用性強(qiáng)的VME 總線作為通用信號(hào)處理平臺(tái)的控制總

2011-09-07 18:56:03 36

36 針對(duì)數(shù)字電路工作頻率增加而出現(xiàn)的信號(hào)完整性(si)問(wèn)題,介紹T*tl用SI仿真設(shè)計(jì)來(lái)進(jìn)行高速數(shù)字電路設(shè)計(jì)的方法。并給出了基于SI仿真指導(dǎo)千兆SFP(SmallFormFactorPluggableOpticalTransceiver)光信號(hào)

2011-11-23 16:12:42 84

84 在DSP系統(tǒng)上運(yùn)行的程序,系統(tǒng)上電復(fù)位后需要加載程序到DSP的程序存儲(chǔ)器內(nèi)。這是使用外部加載模式時(shí)的系統(tǒng)開發(fā)不可缺少的環(huán)節(jié)。針對(duì)實(shí)際需求,提出了一種使用USB對(duì)ADSP_TS101S進(jìn)行鏈

2012-06-08 08:51:08 0

0 高速數(shù)字電路中電子隔離比較

2012-07-23 11:07:03 2645

2645

高速數(shù)字電路設(shè)計(jì)及EMC設(shè)計(jì)!資料來(lái)源網(wǎng)絡(luò),如有侵權(quán),敬請(qǐng)見諒

2015-11-19 14:48:57 0

0 圖解實(shí)用電子技術(shù)叢書-高速數(shù)字電路設(shè)計(jì)與安裝技巧

2015-12-21 11:28:21 0

0 高速數(shù)字電路設(shè)計(jì)手冊(cè),專門為電路設(shè)計(jì)工程師寫的,描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用

2016-03-02 15:27:27 0

0 這本書是專門為電路設(shè)計(jì)工程師寫的 它主要描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用 通過(guò)列舉很多的實(shí)例 作者詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴流 串?dāng)_和輻射噪音等問(wèn)題。

2016-03-09 10:19:44 0

0 高速數(shù)字電路設(shè)計(jì)及EMC設(shè)計(jì)(華為),下來(lái)看看。

2016-03-29 15:41:20 52

52 高速數(shù)字電路設(shè)計(jì)大全

2017-01-17 19:54:24 55

55 數(shù)字電路設(shè)計(jì)方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 這本書是專門為電路設(shè)計(jì)工程師寫的。它主要描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用。通過(guò)列舉很多的實(shí)例,作者詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴流、串?dāng)_和輻射噪音等問(wèn)題。

2018-09-10 08:00:00 61

61 《數(shù)字電路設(shè)計(jì)·仿真·測(cè)試》是2010年8月1日華中科技大學(xué)出版社出版的圖書。本書基礎(chǔ)實(shí)驗(yàn)項(xiàng)目均含有基礎(chǔ)性實(shí)驗(yàn)和設(shè)計(jì)性實(shí)驗(yàn);綜合設(shè)計(jì)性實(shí)驗(yàn)以設(shè)計(jì)、仿真、測(cè)試為主線,有利于扎實(shí)基礎(chǔ)鞏固知識(shí)。

2018-11-06 18:56:20 0

0 高速數(shù)字電路設(shè)計(jì)跟低速數(shù)字電路設(shè)計(jì)不同的是 他強(qiáng)調(diào)組成電路的無(wú)源部件對(duì)電路的影響 這些無(wú)源器件包括導(dǎo)線 電路板和組成數(shù)字產(chǎn)品的集成電路 在低速設(shè)計(jì)中 這些部件單純的只是電路的一部分 根本不用多做考慮 可是在高速設(shè)計(jì)中 這些部件對(duì)電路的性能有著直接的影響。

2018-12-04 08:00:00 0

0 電子發(fā)燒友網(wǎng)為你提供ADI(ti)ADSP-TS101S相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有ADSP-TS101S的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,ADSP-TS101S真值表,ADSP-TS101S管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:01:34

高速數(shù)字電路設(shè)計(jì)跟低速數(shù)字電路設(shè)計(jì)不同的是:他強(qiáng)調(diào)組成電路的無(wú)源部件對(duì)電路的影響。這些無(wú)源器件包括導(dǎo)線、電路板和組成數(shù)字產(chǎn)品的集成電路。在低速設(shè)計(jì)中,這些部件單純

的只是電路的一部分,根本不用多做考慮,可是在高速設(shè)計(jì)中,這些部件對(duì)電路的性能有著直接的影響。

2019-04-11 11:38:32 3581

3581

在當(dāng)今電子技術(shù)行業(yè)發(fā)展過(guò)程中,對(duì)高速電路數(shù)字設(shè)計(jì)十分關(guān)注,高速數(shù)字電路是利用多個(gè)電子元件組成的,可以讓計(jì)算機(jī)高速數(shù)字電路技術(shù)進(jìn)一步提高,因此在計(jì)算機(jī)中使用高速數(shù)字電路設(shè)計(jì)技術(shù)也就更加普遍。

2020-08-21 17:41:10 2924

2924 ADSP-TS101S IBIS數(shù)據(jù)文件BGA包

2021-04-12 16:11:10 4

4 ADSP-TS101S EZ-KIT有限公司設(shè)計(jì)數(shù)據(jù)表(1.3版)

2021-04-13 15:14:10 0

0 EE-157:解釋ADSP-TS101上的分支目標(biāo)緩沖區(qū)

2021-04-15 21:33:37 13

13 EE-176:ADSP-TS101S老虎SHARC高級(jí)Processor硬件設(shè)計(jì)檢查表

2021-04-16 08:51:20 0

0 EE-205:將代碼從ADSP-TS101S TigerSHARC?處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項(xiàng)

2021-04-16 13:54:51 9

9 EE-217:更新ADSP-TS101S老虎SHARC-ZEZ-KIT有限公司

2021-04-16 18:18:12 5

5 高速數(shù)字電路設(shè)計(jì)-華為

2021-04-21 15:45:08 0

0 EE-143:了解ADSP-TS101上的DMA

2021-04-24 11:29:52 7

7 EE-174:ADSP-TS101S虎-SHARC高級(jí)ProcessLuter加載內(nèi)核手術(shù)

2021-04-25 10:17:06 9

9 EE-169:ADSP-TS101S的功耗估算

2021-05-10 09:55:06 8

8 ADSP-TS101 TigerSHARC處理器編程參考

2021-05-13 17:11:14 8

8 ADSP-TS101S TigerSHARC版本0.2、0.4異常列表

2021-05-14 15:46:33 0

0 用于ADSP-TS101S TigerSHARC處理器的EZ套件精簡(jiǎn)版產(chǎn)品亮點(diǎn)

2021-05-17 17:33:44 0

0 ADSP-TS101S EZ套件精簡(jiǎn)版?SUP_

2021-05-17 20:10:12 0

0 ADSP-TS101S EZ-KIT Lite評(píng)估系統(tǒng)手冊(cè)(1.1版,2004年3月)

2021-05-18 17:38:05 0

0 ADSP-TS101 TigerSHARC處理器硬件參考

2021-05-22 10:59:30 4

4 EE-178:ADSP-TS101S TigerSHARC?片上SDRAM控制器

2021-05-27 18:03:52 14

14 華為高速數(shù)字電路設(shè)計(jì)教材資源下載

2021-06-04 11:06:00 86

86 ADSP-TS101S IBIS數(shù)據(jù)文件BGA包

2021-06-16 08:36:40 11

11 主要研究了高速數(shù)字電路設(shè)計(jì)中信號(hào)反射的抑制方法。理論上分析了信號(hào)反射產(chǎn)生的原因及其對(duì)電路設(shè)計(jì)指標(biāo)的影響通過(guò)電路仿真比較不同的布局布線和端接策略并針對(duì)具體情況提出了合理的布局布線和接方法。該方法已成功應(yīng)用于多DP并聯(lián)處理系統(tǒng)中實(shí)踐證明該方法可靠、系統(tǒng)工作穩(wěn)定。

2021-08-12 17:14:20 15

15 FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 實(shí)用電子電路設(shè)計(jì)與調(diào)試數(shù)字電路教材資料免費(fèi)下載。

2022-04-07 14:46:38 26

26 黑魔書 351頁(yè)- 高速數(shù)字設(shè)計(jì)PDF版,華為內(nèi)部數(shù)字電路設(shè)計(jì)教材

2022-06-08 14:33:25 0

0 高速數(shù)字電路設(shè)計(jì)教材-華為

2022-06-13 14:55:54 0

0 數(shù)字電路設(shè)計(jì)是數(shù)字電路最為關(guān)鍵及重要的一步,今天我們將從各個(gè)流程為大家介紹完整的數(shù)字電路設(shè)計(jì)!

2022-07-10 17:14:16 6046

6046 ?? ? ? ? 這本書是專門為電路設(shè)計(jì)工程師寫的。它主要描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中 的分析應(yīng)用。通過(guò)列舉很多的實(shí)例,作者詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴流、串 擾和輻射噪音

2023-08-17 16:57:35 0

0 高速數(shù)字電路設(shè)計(jì)

2022-12-30 09:22:18 19

19 高速數(shù)字電路設(shè)計(jì)教材-華為

2022-12-30 09:22:18 41

41 電子發(fā)燒友網(wǎng)站提供《FPGA/CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.pdf》資料免費(fèi)下載

2023-11-21 11:03:12 3

3 數(shù)字電路設(shè)計(jì)的仿真驗(yàn)證流程是確保設(shè)計(jì)能夠正確運(yùn)行的重要步驟之一。在現(xiàn)代電子設(shè)備中,數(shù)字電路被廣泛應(yīng)用于各種應(yīng)用領(lǐng)域,如計(jì)算機(jī)、通信設(shè)備、汽車電子等等。因此,設(shè)計(jì)師必須通過(guò)仿真驗(yàn)證來(lái)確保電路能夠按照

2024-01-02 17:00:43 256

256

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論