ModelSim仿真入門:功能仿真

本實(shí)驗(yàn)的目的就是在ModelSim環(huán)境下學(xué)習(xí)掌握該軟件的一般仿真測(cè)試流程和仿真測(cè)試方法,另外學(xué)習(xí)編寫簡(jiǎn)單的Test Bench程序并在ModelSim下進(jìn)行調(diào)試。

實(shí)驗(yàn)步驟如下:

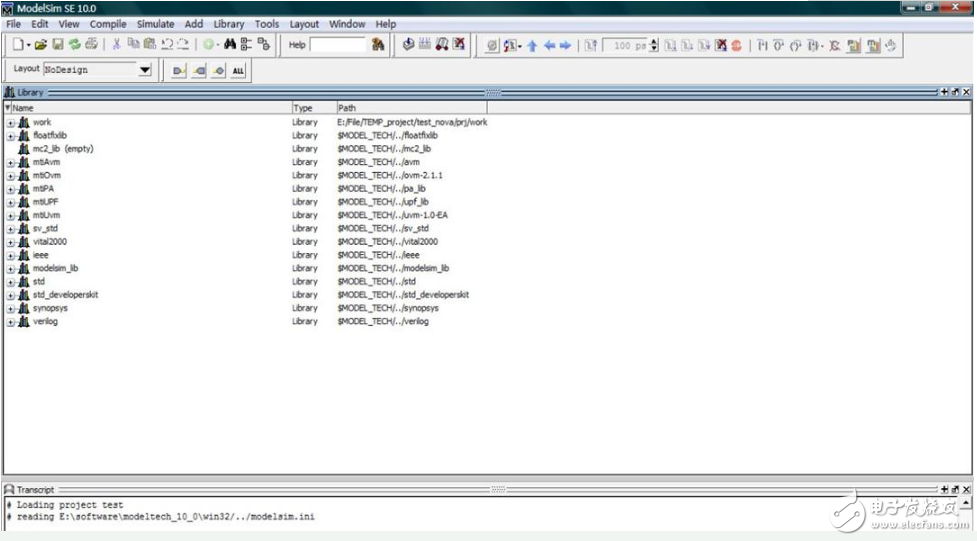

1. 打開(kāi)ModelSim軟件,如圖1所示:

圖1 打開(kāi)軟件

2. 軟件的啟動(dòng)畫面如圖2所示,進(jìn)入界面后如圖3所示:

圖2 軟件的啟動(dòng)畫面

圖3 軟件進(jìn)入后的畫面

注意:如果是第一次使用軟件,進(jìn)入后會(huì)有一些諸如軟件的歡迎畫面等不相關(guān)的對(duì)話框,無(wú)須擔(dān)心,直接關(guān)閉即可,亦可選擇下次登陸時(shí)不顯示。

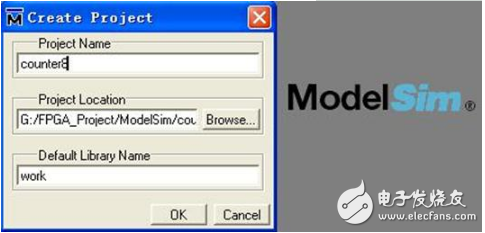

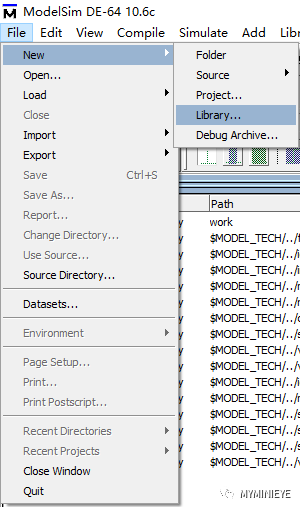

3. 進(jìn)入ModelSim主窗口后,選擇File菜單下的“New→Project”,新建一個(gè)工程,在彈出的對(duì)話框中,給該工程命名并指定一個(gè)存放的路徑,如圖4所示:

圖4 新建工程

在這里,工程名和你的頂層文件名保持一致是推薦的做法。路徑的注意事項(xiàng)已經(jīng)說(shuō)過(guò),這里不再提及。默認(rèn)的庫(kù)名就是“work”,這個(gè)無(wú)需更改,點(diǎn)擊“OK”即可。

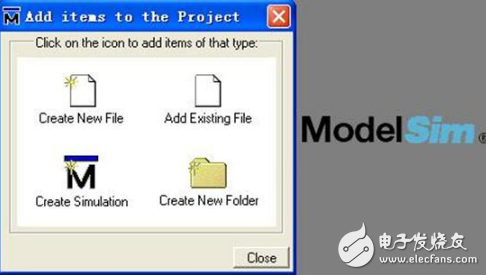

4. 之后會(huì)彈出如圖5的對(duì)話框,選擇是新建一個(gè)文件還是添加已存在的文件,這兩個(gè)都可以選擇,假如事先編好了文件,就選擇添加進(jìn)來(lái),假如沒(méi)有就新建。在這里使用添加已有文件,在軟件開(kāi)始之前就編好所用的程序,這樣比較方便些。軟件自帶的編輯環(huán)境不是很好,使用第三方的編輯工具是推薦的方法。建議使用UltraEdit或Notepad++這些專業(yè)的代碼編輯軟件。

UltraEdit偏重于功能的強(qiáng)大和豐富的用戶可定制化特性,而Notepad++更加注重易用性。兩者在普通功能上差異不是特別大,根據(jù)自己的喜好選擇一款即可。

圖5 給工程中添加文件

在路徑G:FPGA_ProjectModelSimcounter8下新建兩個(gè)文件,一個(gè)是counter8.v,一個(gè)是test_counter8.v,前者是我們的原始的設(shè)計(jì)文件,后者是其相應(yīng)的仿真測(cè)試文件。在這個(gè)路徑的Windows目錄下,在空白處右鍵選擇新建一個(gè)文本文檔.TXT格式,然后在這個(gè)文件上右鍵選擇UltraEdit或Edit with Notepad++就可以啟動(dòng)相應(yīng)的代碼編輯工具進(jìn)行編輯了,保存的時(shí)候注意存成“.v”或“.vhd”格式即可。

以下給出兩個(gè)文件的代碼:

第一個(gè)文件:

//-----------------------------------------------------

// DesignName : counter8

// FileName : counter8.v

//Function : 8 bits counter with asyncclear and sync load

//Coder : Cheng xu

//-----------------------------------------------------

modulecounter8(

clk ,

aclr ,

load ,

load_din ,

dout

);

// Portdeclarations

input clk ;

input aclr ;

input load ;

input [7:0] load_din ;

output [7:0] dout ;

//InternalVariables

wire clk ;

wire aclr ;

wire load ;

wire [7:0] load_din ;

wire [7:0] dout ;

reg [7:0] counter = 0 ;

//CodeStarts Here

always @(posedge clk or negedge aclr)

if(!aclr)

counter 《= 0;

else if(load == 1)

counter 《= load_din;

else

counter 《= counter + 1;

assigndout = counter;

endmodule

第二個(gè)文件:

//test_counter8.v

`timescale1ns/1ns //注意最前面的符號(hào)是數(shù)字鍵“1”左邊的//那個(gè)符號(hào),不是單引號(hào)

moduletest_counter8;

reg clk ;

reg aclr ;

reg load ;

reg [7:0] load_din ;

wire [7:0] dout ;

initial

begin

clk = 0;

aclr = 1;

load = 0;

load_din = 0;

#120 aclr = 0;

#40 aclr = 1;

#20 load = 1;

load_din = 100;

#20 load = 0;

#100 $stop; //可以不添加這個(gè)仿真結(jié)束的系統(tǒng)任務(wù)

end

always#10 clk = ~clk;

counter8U(

.clk(clk),

.aclr(aclr),

.load(load),

.load_din(load_din),

.dout(dout)

);

endmodule

這樣,我們就在該工程路徑下建立好了這兩個(gè)文件。當(dāng)然新建這兩個(gè)文件的的工作可以是放在我們這個(gè)全部的工作開(kāi)始之前進(jìn)行的,無(wú)需等到第4個(gè)步驟開(kāi)始的時(shí)候再進(jìn)行。

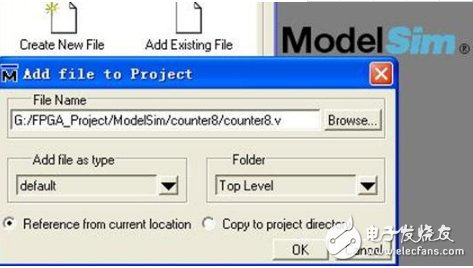

5. 把剛才新建的文件添加到工程中去,點(diǎn)擊“AddExisting Flie”后出現(xiàn)如下畫面,如圖6所示:

圖6 添加原始的待測(cè)試程序文件

點(diǎn)擊“OK”后,繼續(xù)添加另外一個(gè)測(cè)試文件,如圖7所示:

圖7 添加仿真測(cè)試文件

之后點(diǎn)“OK”,再關(guān)閉“Add items to the Project”這個(gè)對(duì)話框。最簡(jiǎn)單的辦法是一次同時(shí)添加兩個(gè)文件,點(diǎn)擊“Browse”之后,鼠標(biāo)直接框選這兩個(gè)文件,這樣可以一次添加多個(gè)文件到ModelSim工程中。

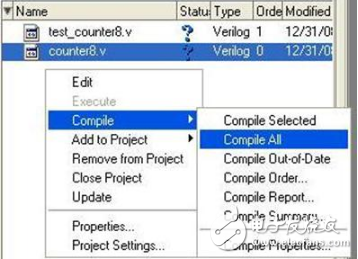

6. 我們?cè)谲浖腜roject區(qū)域已經(jīng)能看到我們添加的這兩個(gè)文件了,如圖8所示:

圖8 Project區(qū)域狀態(tài)

我們下面就可以編譯這兩個(gè)文件了,這時(shí)候因?yàn)檫€沒(méi)有編譯文件,所以Status一欄顯示的是兩個(gè)問(wèn)號(hào)。接著在這個(gè)Project區(qū)域單擊鼠標(biāo)右鍵,選擇“Compile→Compile All”,把HDL源文件編譯到當(dāng)前工程的工作庫(kù)當(dāng)中去。如圖9所示:

圖9 編譯源文件和仿真測(cè)試文件

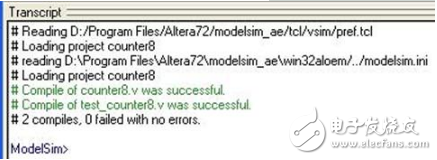

我們?cè)谲浖路降腡ranscript區(qū)域中假如看到如圖10的字樣,就說(shuō)明編譯通過(guò)了:

圖10 編譯成功畫面

注意中間的兩個(gè)successful說(shuō)明成功了。另外,我們?cè)赑roject區(qū)域中的Status一欄中能夠看見(jiàn)兩個(gè)綠色的勾,這也是一種編譯成功的提示。

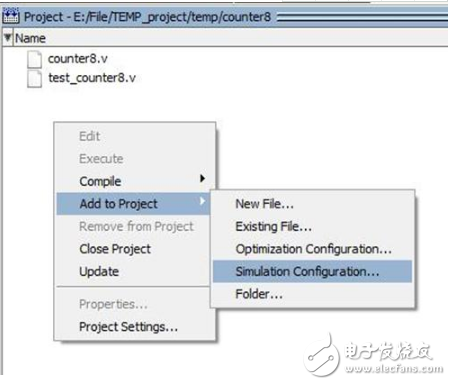

7. 編譯通過(guò)之后,在Project區(qū)域鼠標(biāo)右鍵點(diǎn)擊“Add to Project → Simulation Configuration”,如圖11所示:

圖11 添加Simulation Configuration

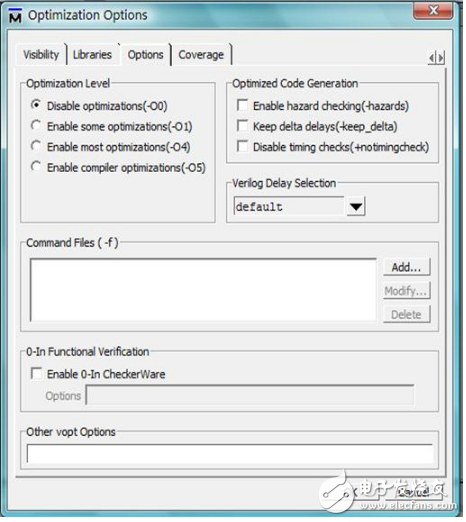

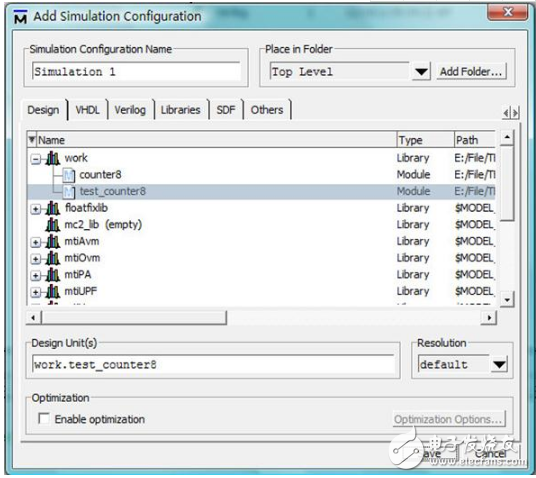

在出現(xiàn)的Add SimulationConfiguration對(duì)話框的右下角打開(kāi)OptimizationOptions,打開(kāi)后切換到Options選項(xiàng)卡頁(yè)面,在Optimization Level中選擇Disable Optimizations,如圖12所示:

圖12 關(guān)閉優(yōu)化選項(xiàng)

點(diǎn)擊OK確定之后返回Add Simulation Configuration對(duì)話框,在Optimization欄中關(guān)閉Enable Optimization,再展開(kāi)work目錄,選中Test Bench文件test_counter8,之后save保存。如圖13所示:

圖13 關(guān)閉優(yōu)化選項(xiàng)

此時(shí)會(huì)在Project區(qū)域出現(xiàn)一個(gè)仿真配置文件:Simulation 1,雙擊它就能進(jìn)入仿真了,在重啟ModelSim之后,還可以雙擊它進(jìn)入仿真,比較方便。

注意:如果不關(guān)閉優(yōu)化選項(xiàng)的話,有時(shí)候ModelSim軟件會(huì)報(bào)錯(cuò)導(dǎo)致不能正常進(jìn)行仿真。

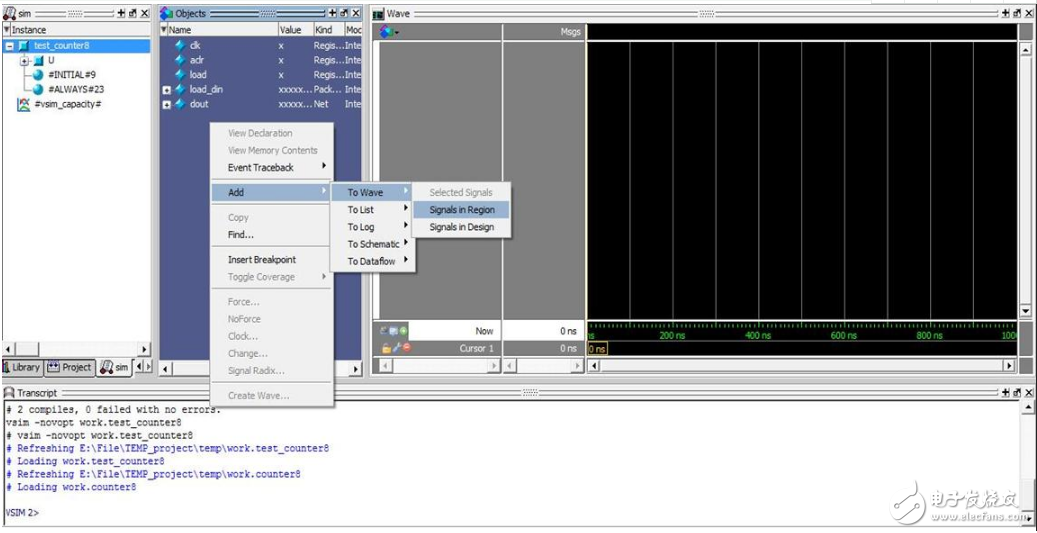

8. 雙擊“Simulation 1”后進(jìn)入仿真波形界面,在Object區(qū)域鼠標(biāo)右鍵選擇“Add → To Wave → Signals inRegion”,把待仿真的信號(hào)添加入Wave窗口。如圖14所示:

圖14 待仿真的信號(hào)添加入Wave窗口

9. 接著我們把wave窗口中的兩個(gè)信號(hào)量改成無(wú)符號(hào)數(shù)顯示,方便我們觀察,在load_din和dout上依次單擊鼠標(biāo)右鍵,按照?qǐng)D15的方法修改即可:

ModelSim仿真入門:時(shí)序仿真

正如前面第二講所述,時(shí)序仿真在實(shí)際應(yīng)用中使用的并不多,但是為了保持仿真系列文檔的完整性,我們還是把仿真的方法寫出來(lái)。

時(shí)序仿真就要比第二講的功能仿真步驟上要多一些,本講以目前的QuartusII的12.0SP2版本和Cyclone IV的EP4CE6F17C8為例,講解下時(shí)序仿真的方法和步驟。

時(shí)序仿真需要的文件總共有以下幾種:

①綜合后生成的網(wǎng)表文件“ * .vo ”(假如在Setting里面設(shè)置里輸出語(yǔ)言為VHDL的話,則生成的網(wǎng)表文件為“ * .vho”)

②綜合后生成的具有工程延時(shí)信息的文件“ * .sdo ”(VHDL語(yǔ)言亦為此)

③ Test Bench程序文件

大致的過(guò)程就是先在Quartus II中生成網(wǎng)表文件和時(shí)延文件,然后調(diào)用ModelSim進(jìn)行仿真,具體的時(shí)序仿真步驟如下:

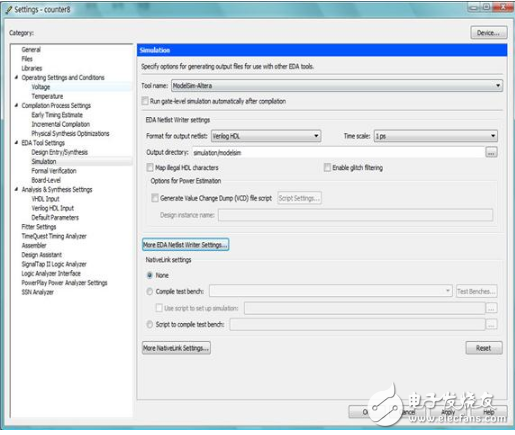

1. 打開(kāi)Quartus II軟件,新建工程,再新建文件counter8.v,把上一講中的counter8.v這個(gè)源文件復(fù)制到Quartus II的工程目錄中,并添加該文件到工程中。接著,選擇“Settings”→“EDA Tool Settings”,選擇左欄的“Simulation”,設(shè)置情況如圖1所示。

第一欄的“Tool name”選擇ModelSim-Altera

第二欄的“Format for output netlist”選擇自己熟悉的語(yǔ)言,VHDL或Verilog都可以,后面的“output directory”是選擇輸出的網(wǎng)表文件和延時(shí)信息文件的存放路徑,一般選擇默認(rèn)即可,這樣的話,將來(lái)編譯成功后,會(huì)在Quartus II的工程文件夾(本例為counter8這個(gè)文件夾)下面生成一個(gè)simulation/modelsim的文件夾,里面存有將來(lái)要用到的.vo和.sdo這兩個(gè)文件。

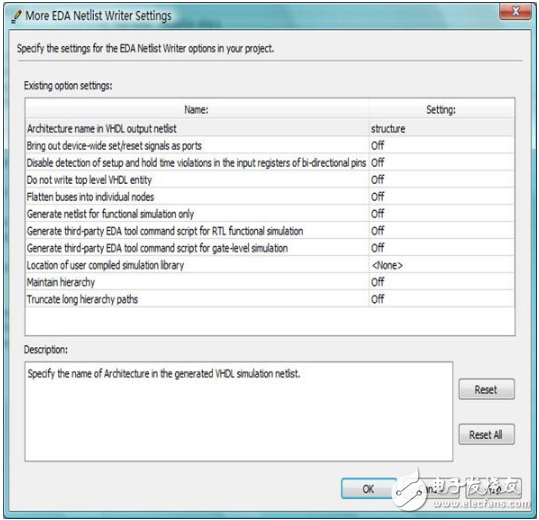

再往下,看到有“More EDA Netlist WritterSettings…”按鈕,點(diǎn)擊后進(jìn)入設(shè)置畫面,設(shè)置情況如圖2所示。注意的地方就是Generatenetlist for functional simulation這一項(xiàng)后面是處于OFF的關(guān)閉狀態(tài),這樣才能生成我們所要的時(shí)序仿真文件。

圖1 simulation的設(shè)置

圖2 More EDA Netlist WritterSettings的設(shè)置

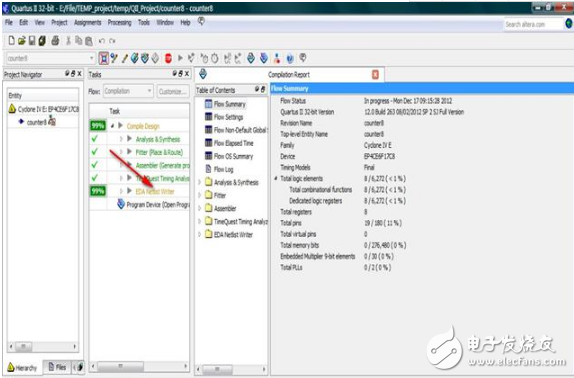

都設(shè)置好了以后,全部點(diǎn)擊“OK”后退出設(shè)置,在QII的編譯環(huán)境下執(zhí)行全編譯。編譯中的情況如圖3所示:

圖3 編譯中的情況

注意:下面比我們平時(shí)進(jìn)行的全編譯時(shí)多了一項(xiàng)“EDANetlist Writer”,圖3的紅色箭頭指向的位置。

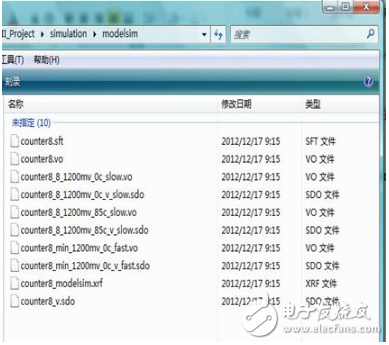

2. 找到新建工程目錄所在的文件夾,在里面找到simulation/modelsim這個(gè)文件夾,會(huì)發(fā)現(xiàn)文件夾內(nèi)有10個(gè)文件,如圖4所示:

圖4 生成的10個(gè)文件

注意:counter8.vo和counter8_v.sdo就是時(shí)序仿真需要的兩個(gè)重要的網(wǎng)表文件,它們與counter8_8_1200mv_85c_slow.vo和counter8_8_1200mv_85c_v_slow.sdo只是命名不同而已,文件的內(nèi)容其實(shí)是一樣的。后兩個(gè)是QuartusII目前新的網(wǎng)表文件的命名方法,文件名標(biāo)示出了速度等級(jí)(-8)、內(nèi)核電壓(1200mv)、溫度條件(85℃)以及時(shí)序模型(slow)。

之所以Altera還沒(méi)有取消舊的命名文件方法并讓QuartusII繼續(xù)生成這兩個(gè)網(wǎng)表文件,是因?yàn)橛蠺clScript文件是按照舊的命名方法寫的,需要兼容它們。

以下時(shí)序仿真以counter8.vo和counter8_v.sdo為例,如果需要用fast時(shí)序模型做仿真,也是按照下面的方法進(jìn)行,只是把vo和sdo文件換為fast。

另外“.xrf”和“.sft”這兩個(gè)文件,是QuartusII編譯生成的一些相關(guān)的信息文件,時(shí)序仿真用不到。

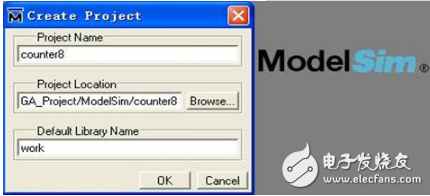

3. 打開(kāi)ModelSim軟件,新建一個(gè)工程,如圖5所示:

圖5 新建工程并指定路徑

①接著把剛才生成的counter8.vo和counter8_v.sdo兩個(gè)文件拷貝到現(xiàn)在個(gè)仿真工程的目錄下面。

②之后還要拷貝一個(gè)很重要的文件,到QuartusII的安裝目錄下: quartusedasim_lib,找到cycloneive_atoms.v這個(gè)文件,這個(gè)是Altera器件庫(kù)的庫(kù)文件,進(jìn)行時(shí)序仿真就是基于這個(gè)庫(kù)文件的,把它也拷貝到仿真工程目錄。

注意:我們是以Cyclone IV的EP4CE6F17C8為例的,所以這里需要復(fù)制的就是cycloneive這個(gè)庫(kù)文件,如果是其它器件的話,需要再對(duì)應(yīng)選擇。

③把test_counter8.v文件拷貝到這個(gè)仿真工程目錄下面。

④在QII安裝目錄的。.altera12.0quartusedafv_libverilog,把這里面的dffeas.v和dffep.v文件拷貝到這個(gè)仿真工程目錄下面。

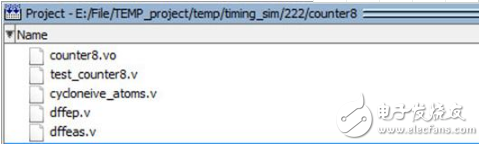

4. 進(jìn)行完上面的步驟后,返回到ModelSim這個(gè)軟件界面,會(huì)發(fā)現(xiàn)軟件還停留在剛才新建工程,需要我們?yōu)槠涔こ烫砑游募膶?duì)話框,那我們就添加文件,把“counter8.vo”、“cycloneive_atoms.v”、“test_counter8.v”、“dffeas.v”和“dffep.v”這5個(gè)文件添加進(jìn)去,如圖6所示:

圖6 添加的5個(gè)文件

注意:此時(shí)不需要添加counter8.v這個(gè)文件了,.vo文件可以替代它。

5. 之后關(guān)閉添加文件對(duì)話框,可以看見(jiàn)Project區(qū)域有了我們添加的5個(gè)文件了,在該區(qū)域點(diǎn)右鍵,“Compile”→“Compile All”執(zhí)行全部編譯。

6. 在Project區(qū)域點(diǎn)右鍵,“Add to Project”→“Simulation Configuration”添加一個(gè)仿真配置的設(shè)置,這時(shí)會(huì)直接彈出添加仿真配置對(duì)話框,這里,我們要進(jìn)行如下的設(shè)置:

①在“Design”選項(xiàng)卡下展開(kāi)work前面的“+”號(hào)后點(diǎn)選test_counter8,這個(gè)就是Test Bench文件。如圖7所示:

圖7 Design選項(xiàng)卡的設(shè)置

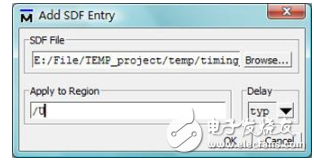

②再切換到“SDF”選項(xiàng)卡,點(diǎn)擊“Add”添加“.sdo”文件,點(diǎn)擊瀏覽后會(huì)直接出現(xiàn)這個(gè)“.sdo”文件的,選擇即可,在下面的“Apply to Region”內(nèi)輸入“U”,這個(gè)就是我們的Test Bench程序中例化頂層文件的例化名字。如圖8所示:

圖8 SDF選項(xiàng)卡的設(shè)置

接著把下面的兩個(gè)SDF選項(xiàng)的復(fù)選框都選中。如圖9所示:

圖9 選中SDF選項(xiàng)的兩個(gè)復(fù)選框

點(diǎn)擊“OK”退出配置設(shè)置界面。配置好了以后的Project區(qū)域的內(nèi)容如圖10所示:

圖10 Project區(qū)域的內(nèi)容

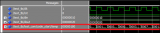

7. 雙擊Simulation執(zhí)行仿真,后面的步驟和功能仿真一樣的了,不再贅述。仿真的波形圖如圖11所示:

圖11 時(shí)序仿真的波形圖

從圖11中可以看到dout相對(duì)于主時(shí)鐘clk有明顯的延時(shí),這個(gè)延時(shí)大小與當(dāng)前使用的器件的時(shí)序模型有關(guān)。

在具體實(shí)踐過(guò)程中,可能還會(huì)遇到各種各樣的問(wèn)題,ModelSim正常運(yùn)行也依賴于仿真庫(kù)文件的齊備,所以碰到某些工程在仿真中遇到報(bào)錯(cuò)的情況時(shí),不妨檢查下ModelSim的提示信息,看看是否有仿真所必需的庫(kù)文件沒(méi)有添加進(jìn)來(lái)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論