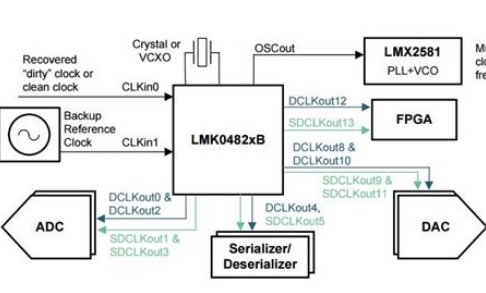

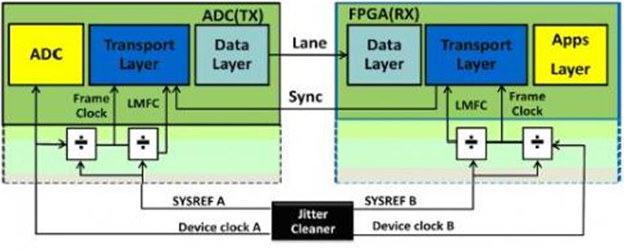

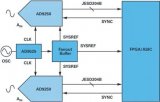

(SYSREF)模式,以及如何用它們來最大限度地提高JESD204B時鐘方案的性能。 LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是

2018-05-14 08:48:18 9732

9732

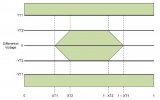

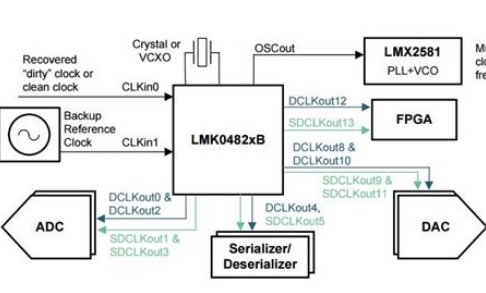

規范,以及利用TI 公司的芯片實現其時序要求。##LMK04820 系列的時鐘芯片是一款專用的JESD204B 時鐘芯片,Device Clock 和SYSREF是成對輸出的,其輸出的時序滿足其時序要求

2015-01-23 10:42:18 21149

21149 和設計優化。最后,此設計還包含原理圖、板布局、硬件測試和測試結果。主要特色高頻 (GSPS) 采樣時鐘生成符合 JESD204B 標準、高通道數、可擴展的時鐘解決方案適用于射頻采樣 ADC/DAC 的低相

2018-10-15 15:09:38

接收器的 3.2Gsps 1.5GHz 多通道高速模擬前端通道間的時鐘偏斜小于 5ps符合 JESD204B 標準的多通道時鐘解決方案可擴展的平臺,適用于具有引腳兼容性的 ADC12DJxx00 系列支持 TI 的高速轉換器和采集卡 (TSW14J56/TSW14J57)

2018-10-11 11:59:37

字前端 (DFE) 處理功能的首個廣泛可用的處理器。通過連接 12J4000 ADC 和 38J84 DAC 可為測試和測量以及國防應用提供高效的解決方案。主要特色信號處理器易于通過 JESD204B 集成到

2018-09-19 09:03:22

的應用的更高帶寬需求。該標準的最新版本JESD204C于2017年底發布,以繼續支持當前和下一代多千兆數據處理系統性能要求的上升趨勢。JESD204C 小組委員會為該標準的新修訂版制定了四個高水平目標:提高通道

2021-01-01 07:44:26

表示JESD204A版本中增加的功能,即支持多通道。 圖2:第一版——JESD204A通過在標準中加入這些功能,便可支持采用更高采樣速率和/或分辨率的轉換器。例如,根據JESD204,采樣時鐘為250

2019-05-29 05:00:03

,轉換器具有各種通道數和位分辨率。在CMOS和LVDS輸出中,數據用作每個通道數據的同步時鐘,使用CML輸出時,JESD204B數據傳輸的最大數據速率為4.0Gbps。從該表中可以發現,使用CML驅動器

2019-06-17 05:00:08

FR-4 材料以全數據速率接收清晰的數據眼圖。特性使用低成本 PCB 材料實現高性能 JESD204B 串行鏈路了解有損通道的局限性并通過均衡技術突破限制使用基于公式的方法來優化 ADC16DX370 的均衡特性此參考設計已經過測試,并包含 EVM、配置軟件和用戶指南`

2015-05-11 10:40:44

什么是8b/10b編碼,為什么JESD204B接口需使用這種編碼?怎么消除影響JESD204B鏈路傳輸的因素?JESD204B中的確定延遲到底是什么? 它是否就是轉換器的總延遲?JESD204B如何使用結束位?結束位存在的意義是什么?如何計算轉換器的通道速率?什么是應用層,它能做什么?

2021-04-13 06:39:06

性能被用戶廣泛接受,同時在某些需要用延時調整去適應DPD 算法的應用中也能很好提供完美時鐘解決方案。如下圖所示,這是通過調整LMK04800 的輸出延時,用示波器采集的JESD204B 的時鐘,其時序能很好的滿足其標準。

2019-06-19 05:00:06

MS-2503: 消除影響JESD204B鏈路傳輸的因素

2019-09-20 08:31:46

使用AD6688時遇到一個JESD204B IP核問題。參考時鐘為156.25MHz,參數L=2,F=2,K=32,線速率為6.25Gbps,使用的為SYSREF always中的每個SYSREF都

2019-04-11 21:12:09

在使用我們的最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。此外,我還在 E2E 上的該

2022-11-21 07:02:17

在使用最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。那么在解決 ADC 至 FPGA

2021-04-06 06:53:56

JESD204B 協議狀態圖1. 代碼組同步 (CGS) — 不需要接口時鐘,因此 RX 必須將其數位及字邊界與 TX 串行輸出對齊。RX 可向 TX 發送 SYNC 請求,讓其通過所有信道發送一個已知的重復

2018-09-13 14:21:49

JESD204B的工作原理JESD204B的控制字符

2021-04-06 06:01:20

JESD204B生存指南

2019-05-28 12:08:12

如果您有接觸使用 FPGA 的高速數據采集設計,沒準聽說過新術語“JESD204B”。我在工作中看到過很多工程師詢問有關 JESD204B 接口的信息以及它如何同 FPGA 協作。他們特別感興趣

2022-11-23 06:35:43

FIFO方案,則無法正常工作。

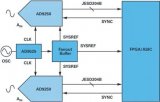

該問題的一種解決方案是讓雙通道轉換器使用多點鏈路JESD204B接口,其中每個轉換器都使用各自獨立的串行鏈路輸出。然后便可針對每個ADC使用非相干時鐘,且每個串行鏈路

2024-01-03 06:35:04

JESD204B產品組合的更多詳情,其中包括 12 位、4GSPS ADC12J4000 模數轉換器 (ADC);16 位、雙通道、250MSPS ADS42JB69 ADC;16 位、4 通道、2.5GSPS DAC38J84 數模轉換器 (DAC) 以及 LMK04828 高性能時鐘抖動清除器。

2018-09-18 11:29:29

所需的時間。該時間通 常以分辨率為幀時鐘周期或以器件時鐘進行測量。JESD204B的確定性延遲規格沒有考慮到ADC模擬前端內核 或DAC后端模擬內核的情況。它只基于輸入和輸出 JESD204B數字幀

2018-10-15 10:40:45

in JESD204B high speed serial interfaces for data converters. This reference design features the ADC16DX370, a

2018-08-09 08:40:10

jesd204B調試經驗有哪些?注意事項是什么?

2021-06-21 06:05:50

我最近嘗試用arria 10 soc實現與ad9680之間的jesd204B協議,看了很多資料,卻依然感覺無從下手,不知道哪位大神設計過此協議,希望可以請教一番,在此先謝過。

2017-12-13 12:47:27

因實際需求,本人想使用JESD204b的ip核接收ADC發送過來的數據,ADC發送的數據鏈路速率是15gbps, 廠家說屬于204b標準。我看到jesd204b的ip核標準最大是12.5gbps,但是支持的支持高達16.375 Gb/s的非標準線速率。請問我可以使用這個IP核接收ADC的數據嗎?

2020-08-12 09:36:39

使用內部PLL,輸入參考頻率為100MHz。在采樣率時鐘設置為1GHz時,DAC的JESD204B鏈路能建立,但是當頻率改為1.5GHz時,SYNC一直為低。其他相關寄存器都已經修改,serdes

2023-12-05 08:17:30

AD9164 JESD204B接口的傳輸層是如何對I/Q數據進行映射的

2023-12-04 07:27:34

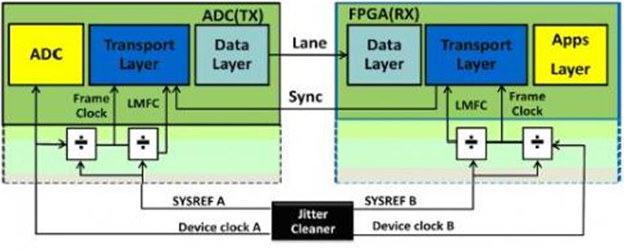

的設計方案。利用JESD204B協議的確定性延遲特性,只要保證通道間下行數據的相互延遲不超過一個多幀時鐘周期,通過關鍵控制信號的設計和處理,通道間可以實現數據的同步,有效控制板內多片ADC之間進行

2019-12-03 17:32:13

該設計是一種軟硬件結合的簡化方案,通過合理設計硬件、設計SYSREF信號的扇出控制邏輯,在一定采樣率范圍內滿足JESD204B協議ADC多片多通道之間采樣點相對時延固定,從而確保各通道采集信號相位一致

2019-12-04 10:11:26

嗨,我必須在Kintex 7上導入為Virtex 6開發的代碼,以便將JESD204B標準中的ADC輸出接口。我修改了代碼和ucf文件,以便在演示板MC705上實現它。Synthesize

2020-05-21 14:22:21

使用AD9680時遇到一個問題,AD9680采樣率為1Gsps,JESD204B IP核的GTX參考時鐘為250MHz,參數L=4,F=2,K=32,線速率為10Gbps,使用的為SYSREF

2023-12-12 08:03:49

使用AD9680時遇到一個問題,AD9680采樣率為1Gsps,JESD204B IP核的GTX參考時鐘為250MHz,參數L=4,F=2,K=32,線速率為10Gbps,使用的為SYSREF

2018-08-08 07:50:35

JESD204B到底是什么呢?是什么導致了JESD204B標準的出現?什么是JESD204B標準?為什么關注JESD204B接口?

2021-05-24 06:36:13

是LVDS的三倍多。當比較諸如多器件同步、確定延遲和諧波時鐘等高級功能時,JESD204B是提供這些功能的唯一接口。所有通路和通道對確定延遲敏感、需要寬帶寬多通道轉換器的系統將無法有效使用LVDS或并行

2019-05-29 05:00:04

為什么JESD204內核不使用GTX通道綁定功能來對齊通道?我試圖從AD接收數據,AD使用JESD204B協議傳輸數據。我的計劃是使用GTX核心并自己編寫JESD部分。我的項目需要兩個車道,我在初始

2020-08-18 10:03:51

時鐘網絡。一,JESD204B時鐘網絡原理概述 本文以JESD204B subclass1來討論時鐘的時序需要以及TI時鐘芯片方案的實現。任何一個串行協議都離不開幀和同步,JESD204B也不例外,也

2019-12-17 11:25:21

我使用的是KC705板卡,調用了里面JESD204B的IP核,使用模式為interpolation值為4,4條鏈路,DAC頻率為2.5GHZ,通道速度為6.25GHZ,出現的問題是:

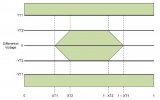

幀同步過程

2023-12-12 07:28:25

我在使用AD9163的時候遇到JESD204B的SYNC信號周期性拉低。通過讀寄存器值如圖,發現REG470和REG471都為0xFF,而REG472始終為0.不知有誰知道是什么原因?該如何解

2023-12-04 07:30:17

關于JESD204B接口你想知道的都在這

2021-09-29 06:56:22

傳播延遲。主要特色通過展示 JESD204B 千兆采樣 ADC 的同步來演示典型的相控陣列雷達子系統詳細介紹了所用的 LMK04828 時鐘解決方案測試結果顯示出 50ps 內的同步,未使用任何特性化電纜,也未校準傳播延遲討論了 Xilinx 固件開發,從而明確要求此子系統經過測試,并包含示例配置文件

2018-08-15 07:16:07

Xilinx FPGA上的JESD204B發送器和接收器框圖。發送器/接收器通道實現加擾和鏈路層;8B/10B編碼器/解碼器和物理層在GTP/GTX/GTHGbit 收發器中實現。圖4. 使用Xilinx

2018-10-16 06:02:44

了確定性延遲,確定包含德州儀器 (TI) LM97937 ADC 和 Xilinx Kintex 7 FPGA 的系統的鏈路延遲。主要特色保證 JESD204B 鏈路中的確定性延遲理解鏈路延遲與鏈路

2018-11-21 16:51:43

JESD204B數模轉換器的時鐘規范是什么?JESD204B數模轉換器有哪些優勢?如何去實現JESD204B時鐘?

2021-05-18 06:06:10

的模數轉換器(ADC)和數模轉換器(DAC)支持最新的JESD204B串行接口標準,出現了FPGA與這些模擬產品的最佳接口方式問題。FPGA一直支持千兆串行/解串(SERDES)收發器。然而在過去,大多數ADC

2021-04-06 09:46:23

JESD204B系統(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。圖1:典型的JEDEC JESD204B應用方框圖 LMK04821憑借來自第二鎖相環(PLL)電壓控制振蕩器的單個SYSREF時鐘分頻器來產生SYSREF信號。信號從分頻器被分配到個別的輸出路徑…

2022-11-18 06:36:26

,JESD204支持的每通道串行鏈路速率是LVDS的三倍以上。當比較諸如多器件同步、確定延遲和諧波時鐘等高級功能時,JESD204B是提供這些功能的唯一接口。所有通路和通道對確定延遲敏感、需要寬帶寬多通道轉換器

2021-11-03 07:00:00

JESD204b接口已經在國內好幾年,但是幾乎沒有一篇文章和其實際應用相關。其實對于一個關于JESD204b接口ADC項目來講一共大致有5個部分:ADC內核,ADC的JESD接口,[color

2017-08-09 20:33:19

DC1974A-C,LTC2122演示板,14位,170Msps雙通道ADC,帶JESD204B輸出。演示電路1974A-C支持具有符合JESD204B標準的CML輸出的LTC2122,14位雙

2019-06-20 08:05:16

是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是典型JESD204B系統(以LMK04821系列器件作為時鐘解決方案)的高級

2018-09-06 15:10:52

在上篇博客《理解JESD204B協議》中,我對 JESD204B 協議中的三個狀態進行了概括性的功能介紹。這三個狀態對于在鏈路的 TX 和 RX 之間構建有效數據鏈路非常重要,它們是:代碼組同步

2022-11-21 07:18:42

的 LMFS 配置和 PLL 設置。要在經過 JESD204B 協議的各個狀態時檢驗信號,可使用 FPGA 廠商提供的信號分析工具。構建JESD204B 鏈路的第一步是RX 發信號通知TX 開始代碼組同步

2018-09-13 09:55:26

AD9680-LF1000EBZ,用于AD9680-LF1000 14位,1000 MSPS JESD204B,雙通道模數轉換器的評估板。該參考設計提供了在各種模式和配置下運行ADC所需的所有支持

2019-03-28 07:21:47

AD9680只有兩個ADC通道(A與B),但是當DDC啟用復數輸出模式后,就會有四個不同的(16位)數據流通向JESD204B接口。對于JESD204B接口來說,這就相當于此時有四個轉換器在發送位流。所以

2018-10-30 15:06:13

探討如何同步多個帶 JESD204B 接口的模數轉換器 (ADC) 以便確保從 ADC 采樣的數據在相位上一致。主要特色同步 2 個采樣頻率為 3.072GHz 的千兆采樣 ADC系統可擴展到超過 2

2018-07-13 06:47:51

探討如何同步多個帶JESD204B 接口的模數轉換器 (ADC) 以便確保從 ADC 采樣的數據在相位上一致。特性同步 2 個采樣頻率為 3.072GHz 的千兆采樣 ADC系統可擴展到超過 2 個

2022-09-19 07:58:07

描述高速多通道應用需要低噪聲、可擴展且可進行精確通道間偏斜調節的時鐘解決方案,以實現最佳系統 SNR、SFDR 和 ENOB。此參考設計支持在菊鏈配置中增加 JESD204B 同步時鐘。此設計可提供

2018-12-28 11:54:19

Up to 15GHz sample clock generationMulti-channel JESD204B compliant clock solutionLow phase noise

2018-10-15 15:13:45

全球領先的高性能信號處理解決方案供應商,最近推出一款高性能時鐘抖動衰減器HMC7044,其支持JESD204B串行接口標準,適用于連接基站設計中的高速數據轉換器和現場可編程門陣列(FPGA)。

2015-09-09 11:20:06 1284

1284

在使用我們的最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。此外,我還在 E2E

2017-04-08 04:48:17 2131

2131

JESD204B是一種高速數據傳輸協議,采用8位/10位編碼和加擾技術,旨在確保足夠的信號完整性。針對JESD204B標準,總吞吐量變為在此設置中,由于AD9250中沒有其他數字處理任務,所以JESD204B鏈路(JESD204B發射器)一目了然。

2017-09-08 11:36:03 39

39 隨著高速ADC跨入GSPS范圍,與FPGA(定制ASIC)進行數據傳輸的首選接口協議是JESD204B。為了捕捉頻率范圍更高的RF頻譜,需要寬帶RF ADC。在其推動下,對于能夠捕捉更寬帶寬并支持

2017-11-16 18:48:16 9537

9537

本設計致力于用SystemC語言建立JESD024B的協議標準模型,描述JESD204B的所有行為,并且能夠保證用戶可以通過該JESD204B的SystemC庫,進行JESD204B行為的仿真

2017-11-17 09:36:56 3002

3002

在本文中,筆者將談論抖動合成器與清除器的不同系統參考信號(SYSREF)模式,以及如何用它們來最大限度地提高JESD204B時鐘方案的性能。 LMK04821系列器件為該話題提供了很好的范例研究素材

2017-11-17 10:31:45 3009

3009

在從事高速數據擷取設計時使用FPGA的人大概都聽過新JEDEC標準「JESD204B」的名號。近期許多工程師均聯絡德州儀器,希望進一步了解 JESD204B 接口,包括與FPGA如何互動、JESD204B如何讓他們的設計更容易執行等。本文介紹 JESD204B標準演進,以及對系統設計工程師有何影響。

2017-11-18 02:57:01 13942

13942 隨著數模轉換器的轉換速率越來越高,JESD204B 串行接口已經越來越多地廣泛用在數模轉換器上,其對器件時鐘和同步時鐘之間的時序關系有著嚴格需求。本文就重點講解了JESD204B 數模轉換器的時鐘

2017-11-18 08:00:01 1831

1831 高速多通道應用需要低噪聲、可擴展且可進行精確通道間偏斜調節的時鐘解決方案,以實現最佳系統 SNR、SFDR 和 ENOB。此參考設計支持在菊鏈配置中增加 JESD204B 同步時鐘。此設計可提供

2019-11-29 08:00:00 0

0 AD9656:四通道、16位、125 MSPS JESD204B 1.8 V模數轉換器(ADC)

2021-03-19 06:14:59 14

14 HMC7044: 帶 JESD204B 接口的高性能、3.2 GHz、14 路輸出抖動衰減器

2021-03-21 11:14:44 11

11 AD9680: 14位、1000 MSPS JESD204B雙通道模數轉換器

2021-03-22 09:22:01 12

12 )和并行輸出ADC的需要,延遲不一致的問題對系統設計人員而言歷來是一個難題。 JESD204B提供了一個方法通過一個或多個差分信號發送高速串行數據,比如發送ADC的輸出。JESD204B規范本身具有實現通道間粗調對齊的功能。數據分割為幀,并持續發送至

2021-03-25 14:49:55 5629

5629

LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持數據表

2021-04-22 15:52:09 9

9 LTC2122:帶JESD204B串行輸出的雙14位170 Msps ADC數據表

2021-05-09 21:06:02 11

11 AD9528:具有14個LVDS/HSTL輸出的JESD204B時鐘發生器數據表

2021-05-13 08:29:21 13

13 帶JESD204B串行接口的14位250 Msps ADC系列

2021-05-18 15:04:50 7

7 LTC6953:超低抖動、4.5 GHz時鐘分配器,帶11個輸出和JESD204B/JESD204C支持數據表

2021-05-19 15:23:53 14

14 LTC2123:帶JESD204B串行輸出的雙14位250 Msps ADC數據表

2021-05-24 08:01:59 8

8 明德揚的JESD204B采集卡項目綜合上板后,可以使用上位機通過千兆網來配置AD9144和AD9516板卡,實現高速ad采集。最終可以在示波器和上位機上采集到設定頻率的正弦波。本文重點介紹JESD204B時鐘網絡。

2022-07-07 08:58:11 1296

1296

如何構建您的JESD204B 鏈路

2022-11-04 09:52:11 3

3 理解JESD204B協議

2022-11-04 09:52:12 3

3 JESD204B:適合您嗎?

2022-11-07 08:07:23 0

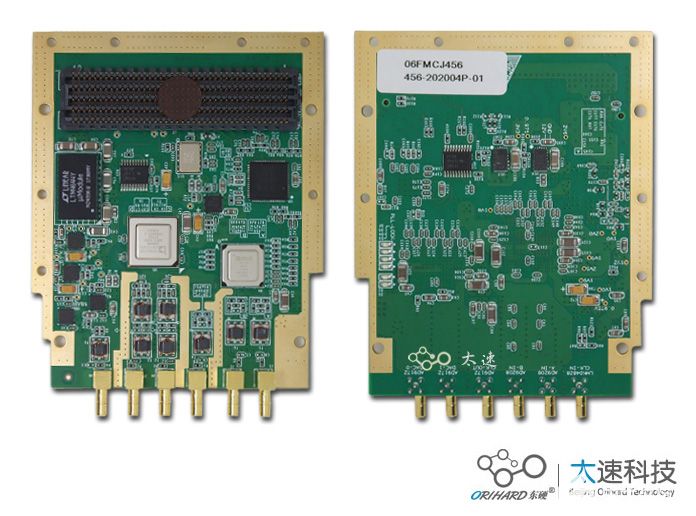

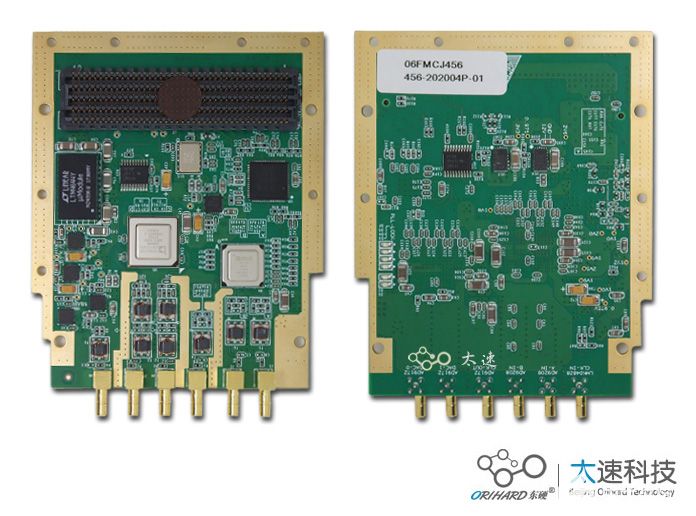

0 MC子卡模塊, 超寬帶接收機, 多通道MIMO通信, JESD204B板卡, JESD204B

2023-01-06 10:06:44 439

439

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是典型JESD204B系統(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。

2023-04-18 09:25:30 919

919

本文旨在提供發生 JESD204B 鏈路中斷情況下的調試技巧簡介

2023-07-10 16:32:03 802

802

電子發燒友網為你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相關產品參數、數據手冊,更有AD9207

2023-10-16 19:02:55

電子發燒友App

電子發燒友App

評論