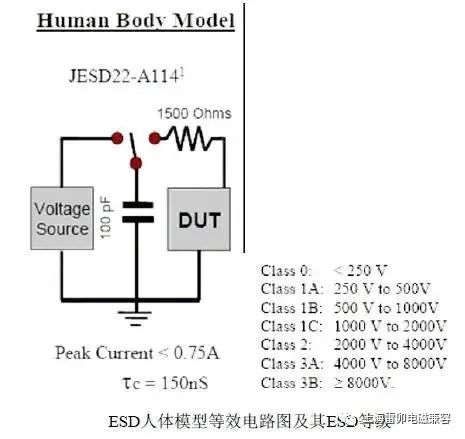

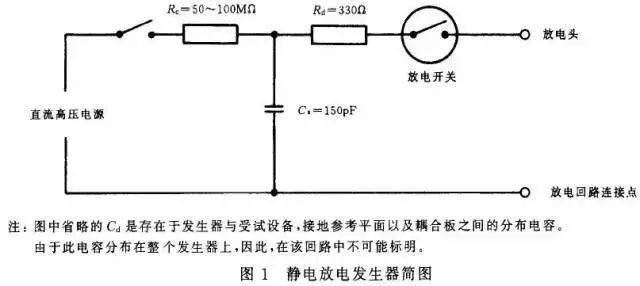

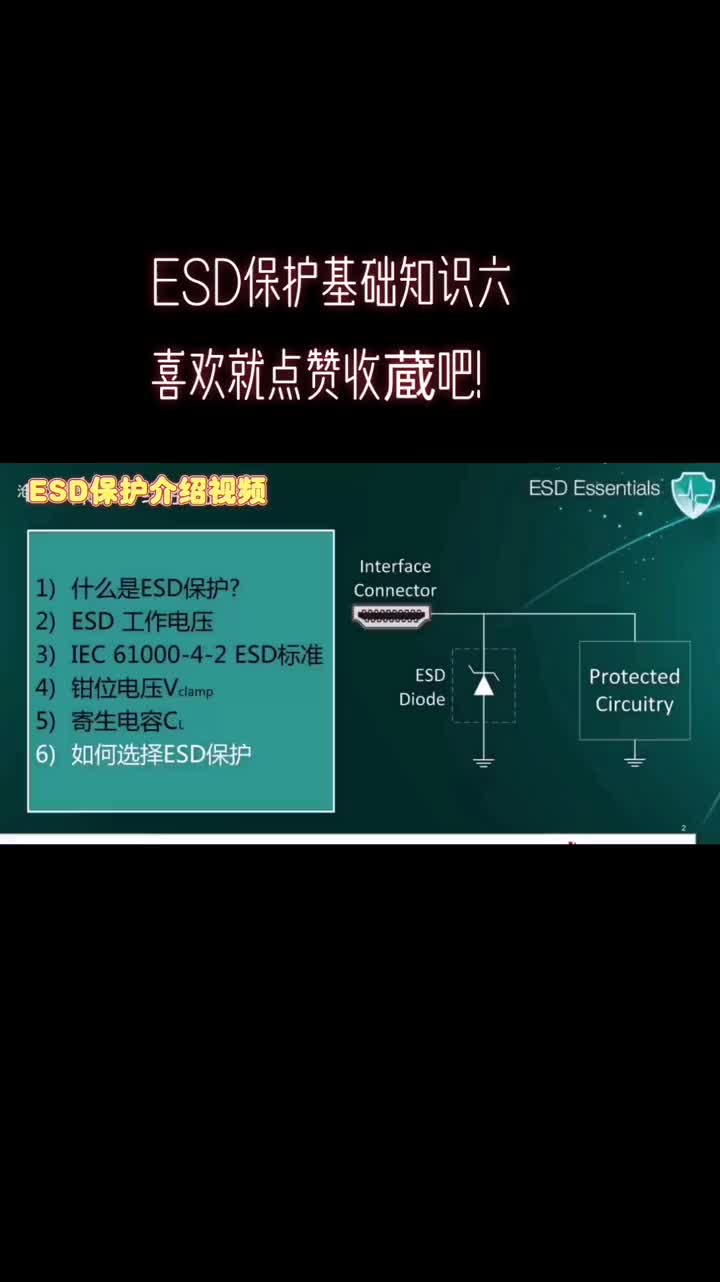

靜電是人們非常熟悉的一種自然現象。靜電的許多功能已經應用到軍工或民用產品中,如靜電除塵、靜電噴涂、靜電分離、靜電復印等。然而,靜電放電ESD卻又成為電子產品和設備的一種危害,造成電子產品和設備的功能混亂甚至部件損壞。現代半導體器件的規模越來越大,工作電壓越來越低,導致了半導體器件對外界電磁騷擾敏感程度也大大提高。ESD對于電路引起的干擾、對元器件、CMOS電路造成的破壞等問題越來越引起人們的重視。電子設備的ESD也開始作為電磁相容性測試的一項重要內容寫入國家標準和國際標準中。

1、靜電成因及其危害

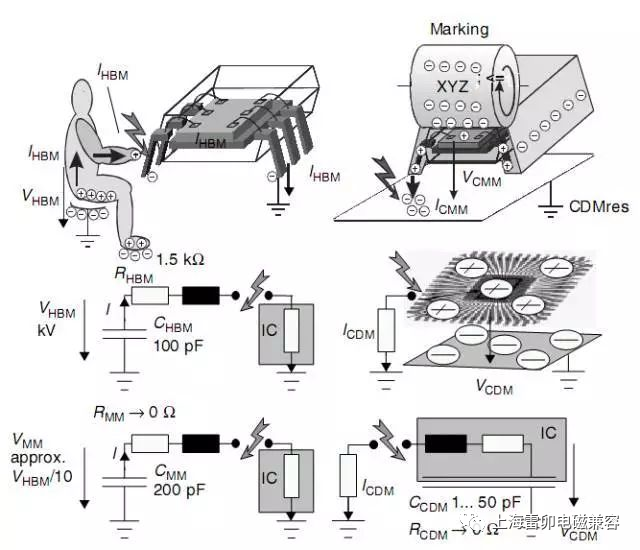

靜電是兩種電系數不同的物質摩擦時,正負極性的電荷分別積累在兩個物體上而形成。當兩個物體接觸時,其中一個趨從于另一個吸引電子,因而兩者會形成不同的充電電位。就人體而言,衣服與皮膚之間的摩擦發生的靜電是人體帶電主要原因之一。

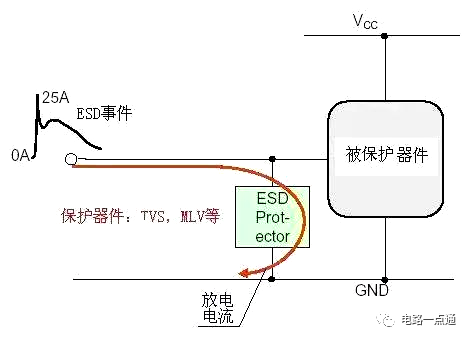

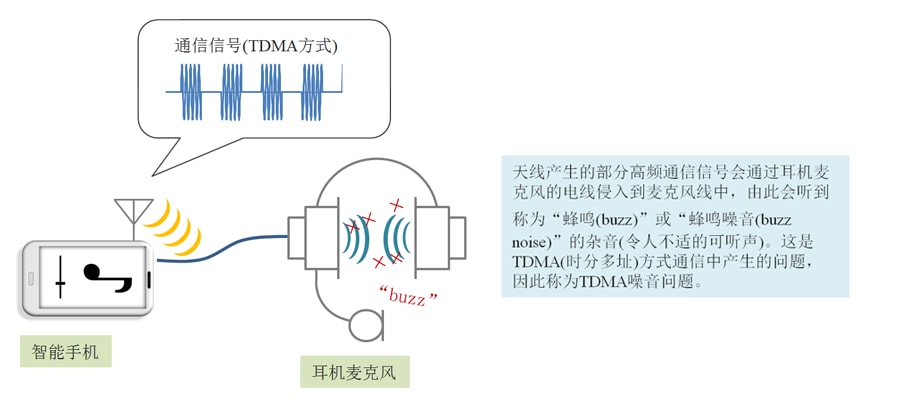

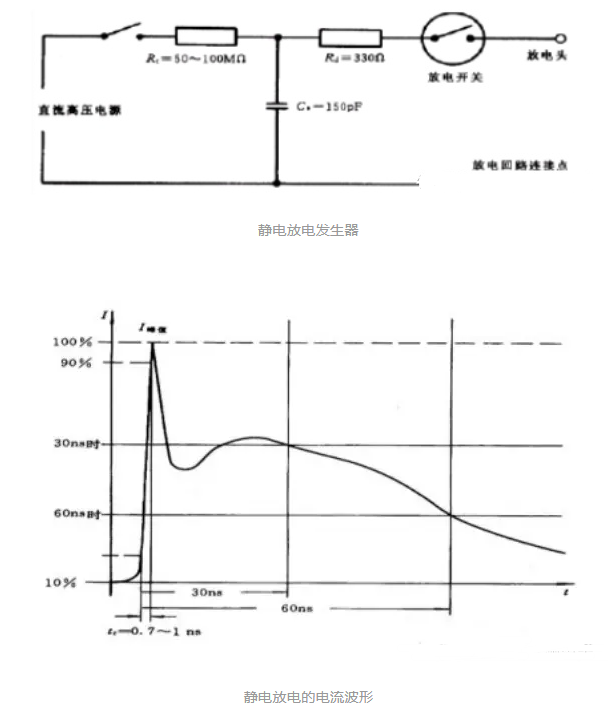

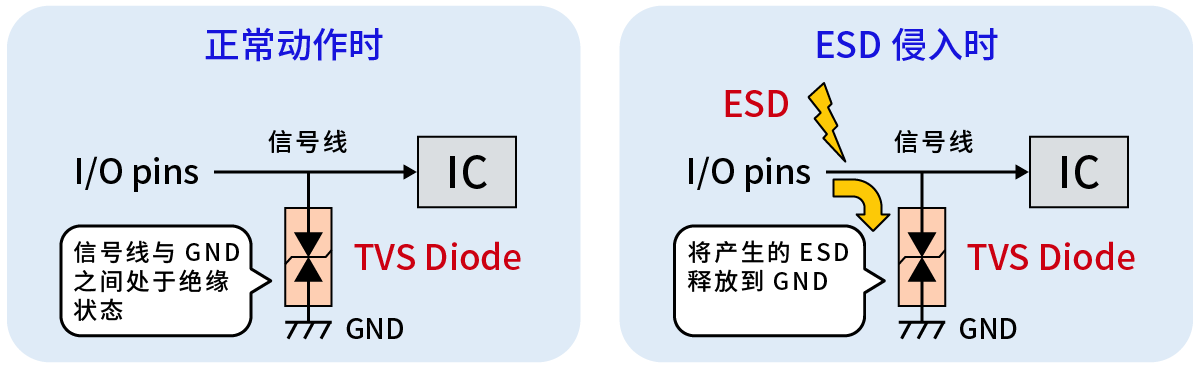

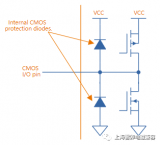

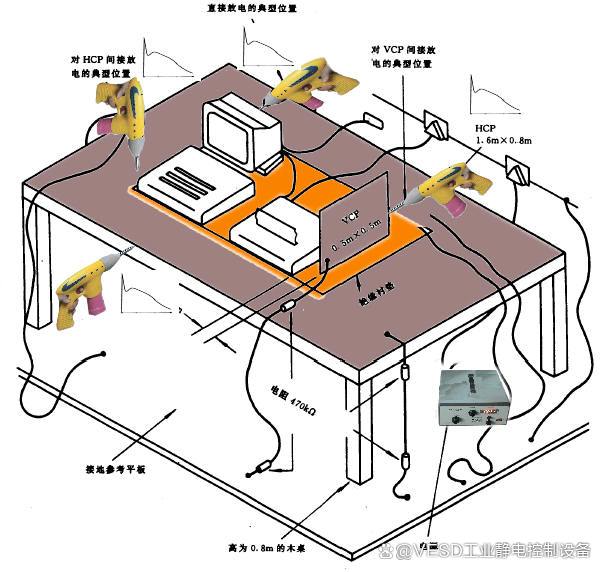

靜電源于其它物體接觸時,依據電荷中和的物理存在著電荷流動,傳送足夠的電量以抵消電壓。在高速電量的傳送過程中,將產生潛在的破壞電壓、電流以及電磁場。嚴重時,將其中物體擊毀,這就是靜電放電。國家標準中定義:靜電放電是具有不同降低電位的物體互相靠近或直接接觸引起的電荷轉移(GB/T4365-1995),一般用ESD表示。ESD會導致電子設備嚴重損壞或操作失常。

靜電對器件造成的損壞有顯性和隱性兩種。隱性損壞在當時看不出來,但器件變得更脆弱,在過壓高、溫等條件下極易損壞。

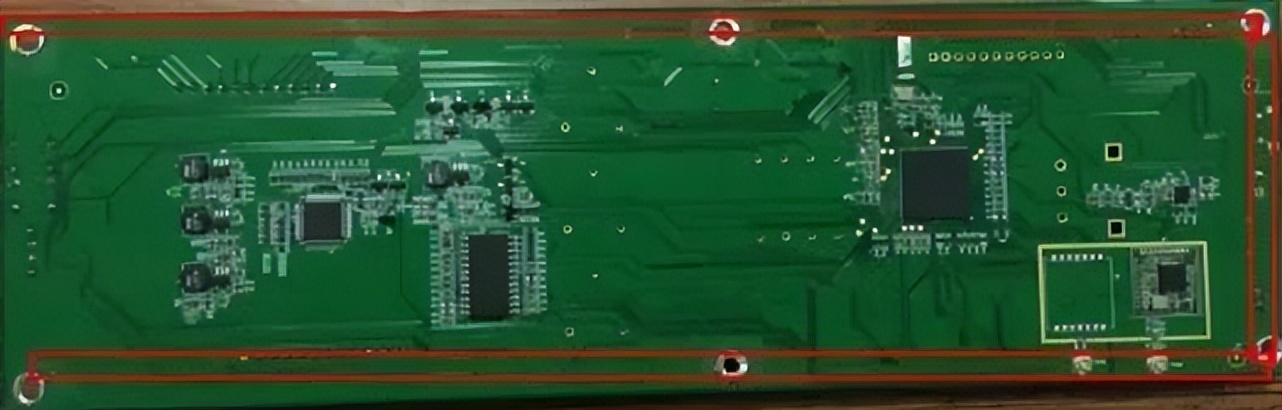

2、產品的PCB設計

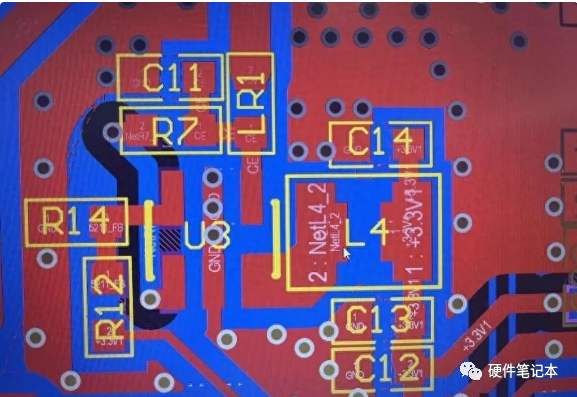

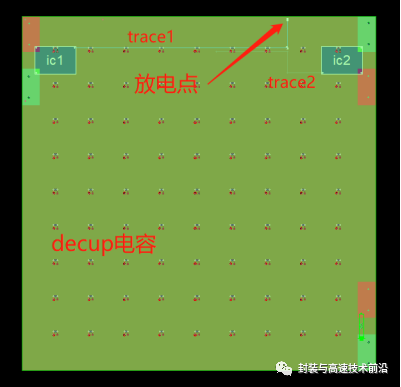

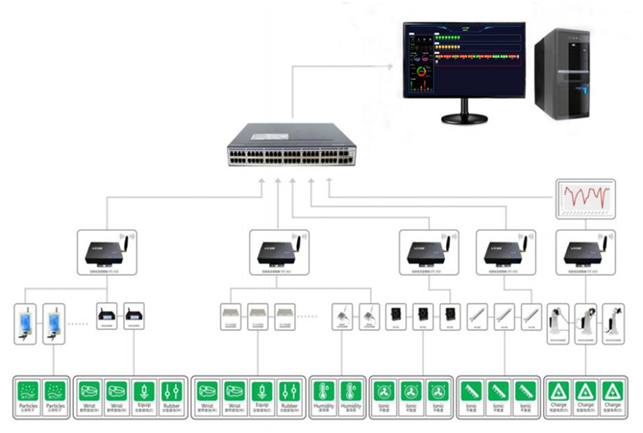

現在產品的PCB都是高密度板,通常為4層板,隨著密度的增加,趨勢是使用6層板,其設計抑制都需要考慮性能的平衡。一方面,越大的空間可以有更多的空間擺放元器件,同時,走線的線寬跟線距寬,對于EMI、音頻、ESD等各方面性能都有好處。另一方面,數碼產品設計的小巧又是趨勢的需要。所以,設計時需要找到平衡點。就ESD問題而言,設計上需要注意的地方很多,尤其是關于GND布線的設計以及線距,很有講究。有些產品中ESD存在很大的問題,一直找不到原因,通過反復研究跟實驗,發現PCB設計中出現的問題。

為此,這里總結了PCB設計中應該注意的要點:

1、PCB板邊(包括通孔Via邊界)跟其它布線之間的距離在大于0.3mm;

2、PCB板邊最好全部用GND走線包圍;

3、GND跟其它布線之間的距離保持在0.2mm~0.3mm;

4、Vbat跟其它布線之間距離保持在0.2mm~0.3mm;

5、重要的線如Reset、Clock等于其它布線之間的距離應大于0.3mm;

6、大功率的線跟其它布線之間的距離保持在0.2mm~0.3mm;

7、不同層的GND之間應有盡可能多的通孔(VIa)相連;

8、在最后的鋪地時應盡量避免尖角,有尖角應盡量使其平滑。

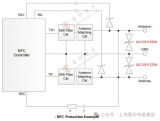

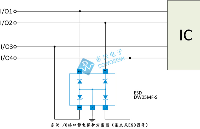

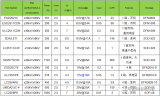

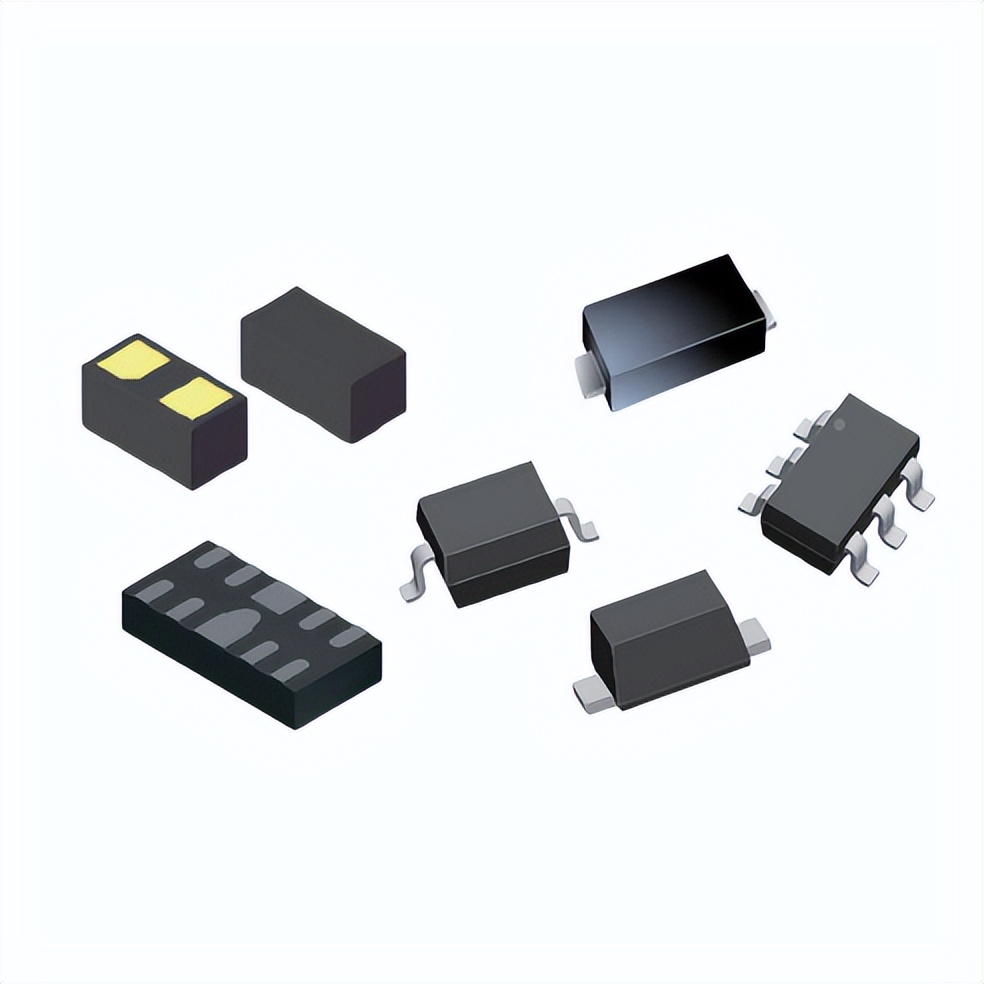

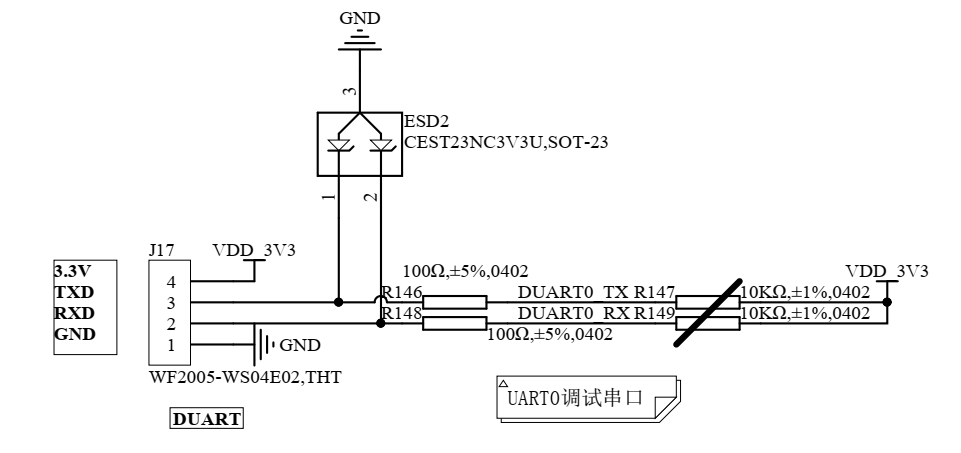

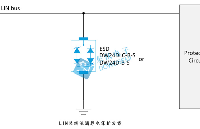

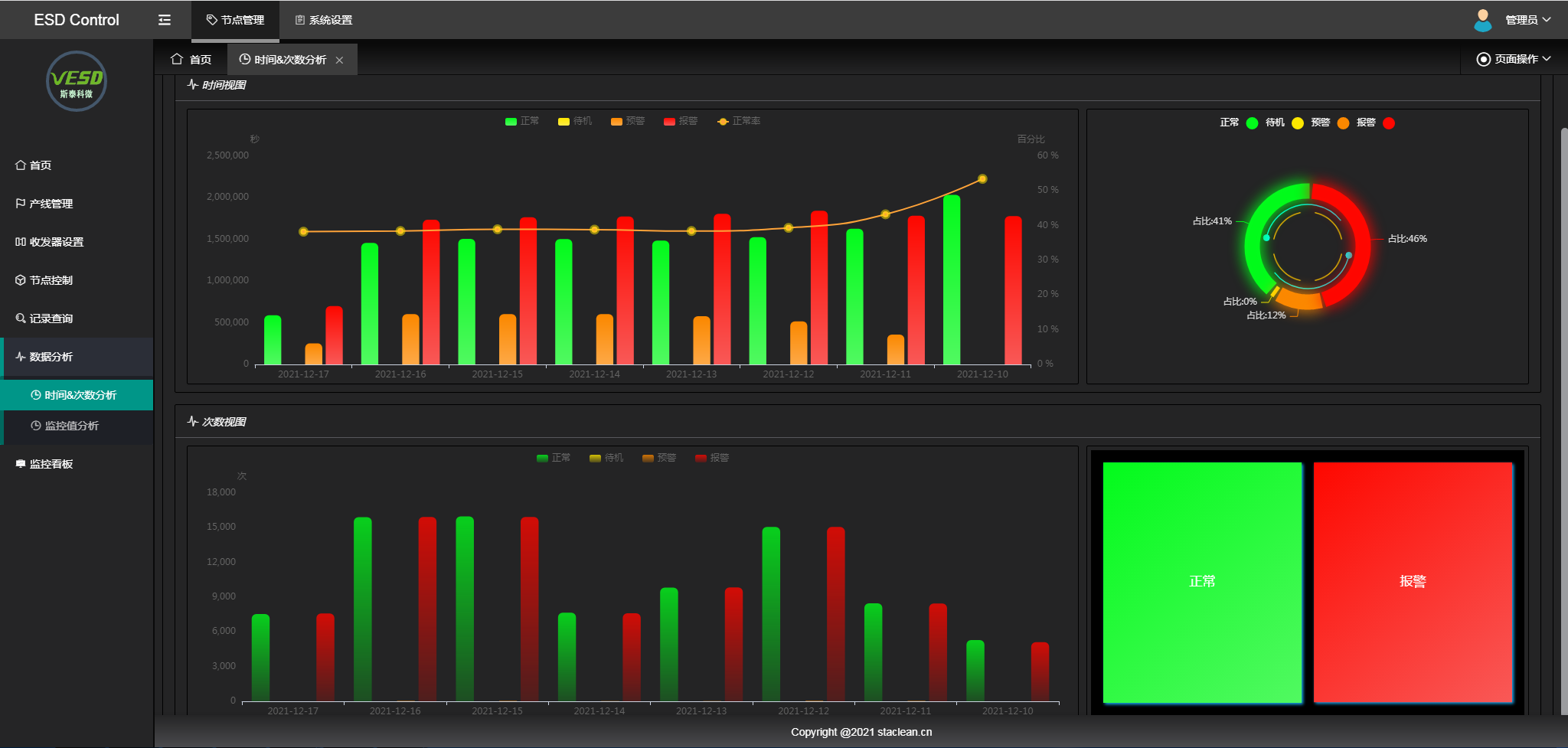

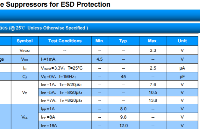

為了使其產品變得更加安全有保證,可以加上Asim ESD保護器件:

本文出自深圳市阿賽姆科技有限公司轉載請說明出處及鏈接(http://www.asim-emc.com/)

電子發燒友App

電子發燒友App

評論