使用STM32H723ZG通過FMC操作外部SDRAM W9825G6KH時, 數據寬度16bit, 總線頻率108M, FMC操作時序如圖

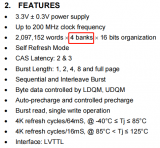

SDRAM CAS值為2,從0XC0000000到

2024-03-11 06:40:14

在mdk里面可以利用attribute關鍵字來將數組存放在外擴的SDRAM里面。但是在cubeide里面這樣做就會報錯,哪位大佬可以解釋一下

2024-03-06 07:25:37

服務器內存條和普通內存條的區別? 服務器內存條和普通內存條是計算機中常見的兩種內存設備。它們在設計、功能和應用方面存在一些顯著的區別。 1.物理特性 普通內存條通常采用DIMM封裝形式,而服務器

2024-02-19 10:19:58 466

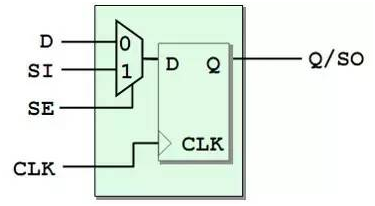

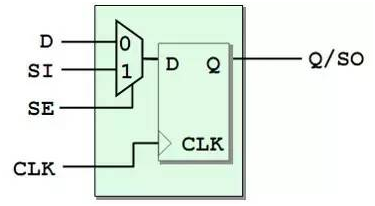

466 ,時序電路可以分為同步時序電路和異步時序電路。接下來,我們將詳細討論時序電路的分類以及其基本單元電路。 一、同步時序電路 同步時序電路是指所有的時鐘信號在整個電路中具有相同的時鐘頻率和相位。它包括鎖存器、觸發器

2024-02-06 11:25:21 394

394 時序電路是由觸發器等時序元件組成的數字電路,用于處理時序信號,實現時序邏輯功能。根據時序元件的類型和組合方式的不同,時序電路可以分為同步時序電路和異步時序電路。本文將從這兩個方面詳細介紹時序

2024-02-06 11:22:30 288

288 產生相應的輸出信號。本文將詳細介紹時序邏輯電路的分類、基本原理、設計方法以及與組合邏輯電路的區別。 一、時序邏輯電路的分類 時序邏輯電路主要分為三類:鎖存器、觸發器和計數器。 鎖存器(Latch): 鎖存器是一種用于存

2024-02-06 11:18:34 496

496 系統內存和運行內存都是計算機中重要的概念,它們在計算機的存儲和運行方面起著不可或缺的作用。雖然它們與計算機存儲和運行息息相關,但是它們具有不同的功能和實現方式。接下來我將詳細介紹系統內存和運行內存

2024-01-15 16:32:25 461

461 STM32H750是STMicroelectronics推出的一款高性能微控制器,其特點之一是可擴展的SDRAM(同步動態隨機存儲器)接口。本文將詳細介紹STM32H750擴展SDRAM的相關知識

2024-01-04 14:09:23 339

339 和DDR5的主要特點。LPDDR5是為移動設備設計的內存標準,它具有低功耗的特點,能夠提供高帶寬和大容量的存儲。而DDR5是桌面和服務器領域的內存標準,它更注重性能和可靠性。 在時序方面,LPDDR5的時序比DDR5慢。這是因為LPDDR5的主要目標是降低功耗,因此它采用

2024-01-04 10:22:06 1156

1156 的引腳介紹

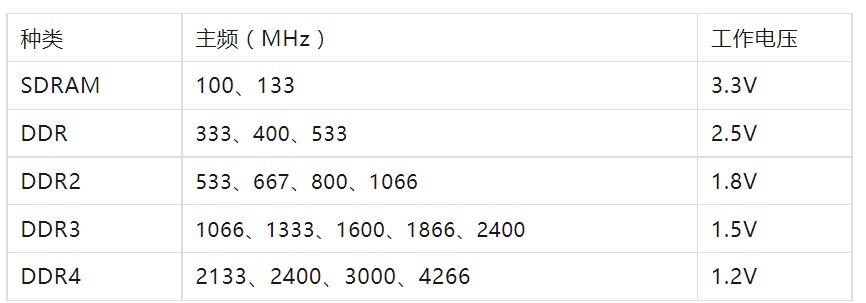

DDR內存條的引腳數,取決于內存條的類型和規格。以下是一些常見的 DDR內存條類型和它們的引腳數 :

DDR1內存條,184引腳(92針對每側)

DDR2內存條,240引腳(120針對每側

2023-12-25 14:02:58

的引腳介紹

DDR內存條的引腳數,取決于內存條的類型和規格。以下是一些常見的 DDR內存條類型和它們的引腳數 :

DDR1內存條,184引腳(92針對每側)

DDR2內存條,240引腳(120針對每側

2023-12-25 13:58:55

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 內存溢出與內存泄漏:定義、區別與解決方案? 內存溢出和內存泄漏是計算機科學中常見的問題,在開發和調試過程中經常會遇到。本文將詳細介紹內存溢出和內存泄漏的定義、區別以及解決方案。 一、內存溢出的定義

2023-12-19 14:10:12 883

883 時,位寬變為64bit,即8個字節,于是SIMM就順勢變為DIMM(Double-Inline Memory Module)。這種形態一直延續至今,也是內存條的基本形態。

2023-12-16 15:00:57 1072

1072

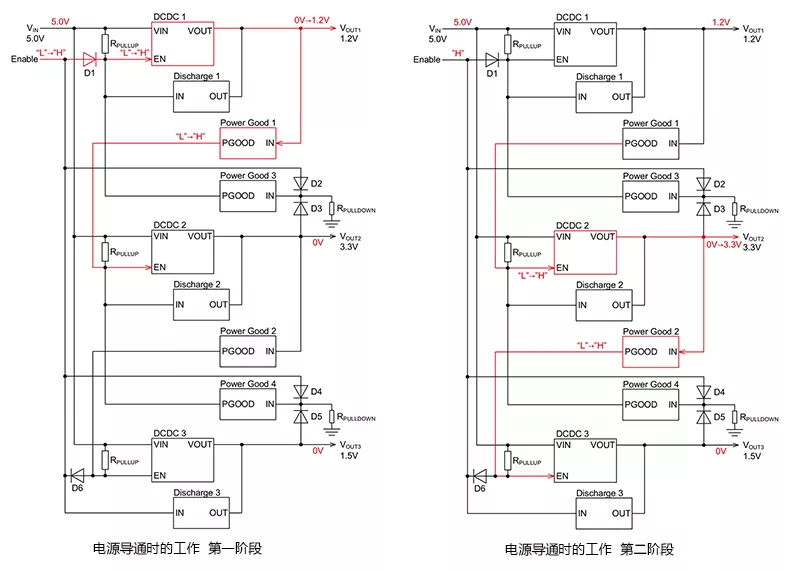

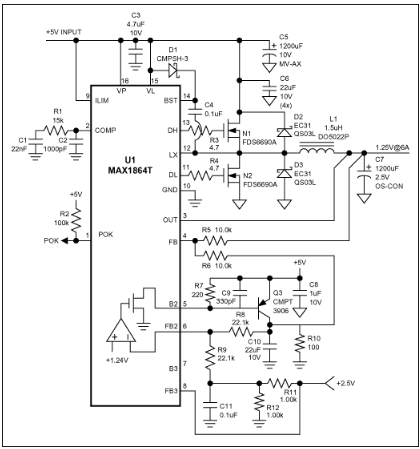

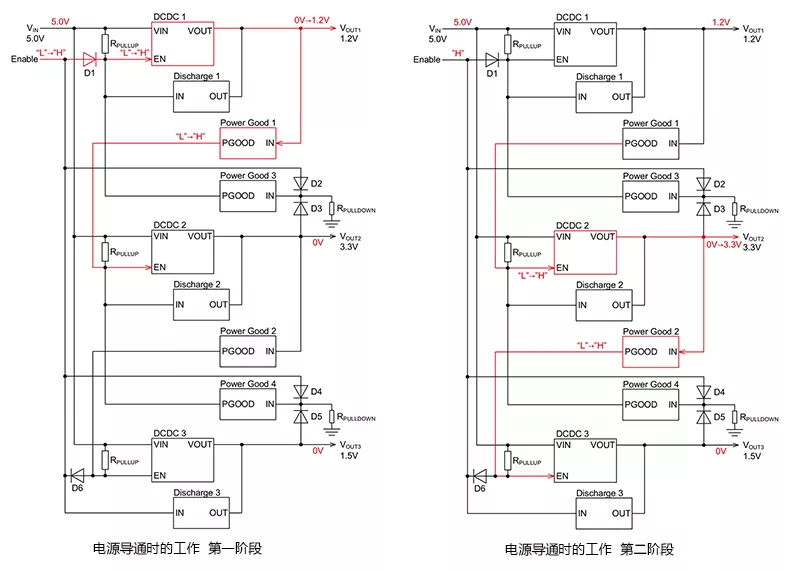

電源時序規格:電源導通時的時序工作

2023-12-08 18:21:43 326

326

什么是內存呢?在計算機的組成結構中,有一個很重要的部分,就是存儲器。存儲器是用來存儲程序和數據的部件,對于計算機來說,有了存儲器,才有記憶功能,才能保證正常工作。存儲器的種類很多,按其用途可分為

2023-12-07 11:02:27 622

622 追風A60采用新一代DDR5內存規格,相較DDR4,性能提升接近1倍。高配6000MHz頻率實現DDR4 3200MHz的1.6倍傳輸速度和1.9倍傳輸帶寬,讓用戶在使用臺電內存條時獲得更快速、更流暢的電腦體驗。

2023-12-05 15:52:49 411

411

將詳細介紹每個運行時數據內存的作用和特點。 堆內存(Heap Memory): 堆內存是JVM管理的最大的一塊內存,用于存儲對象實例。當我們使用new關鍵字創建對象時,對象實例被分配在堆內存中。堆內存是線程共享的,所有的線程都可以訪問堆中的對象。它被劃

2023-12-05 14:09:34 167

167 JVM(Java虛擬機)是Java程序的運行平臺,它負責將Java程序轉換成機器碼并在計算機上執行。在JVM中,內存模型和內存結構是兩個重要的概念,本文將詳細介紹它們。 一、JVM內存模型 JVM

2023-12-05 11:08:39 320

320 通過 SDRAM 的 7 個模式寄存器,可以對 SDRAM 的特性,功能以及設置進行編程。這些寄存器本身通過 MRS 命令編輯。模式寄存器一般在初始化期間進行設定,但也可以在后續正常工作期間進行修改。

2023-12-02 13:44:08 921

921

過程中常見的問題之一,可能導致應用程序崩潰、性能下降甚至系統崩潰。在本文中,將詳細介紹如何排查和解決Java內存溢出問題。 一、什么是Java內存溢出 在開始解決Java內存溢出問題之前,首先需要了解Java內存

2023-11-23 14:46:07 539

539 電子發燒友網站提供《多電源系統監控和時序控制介紹.pdf》資料免費下載

2023-11-22 16:04:24 0

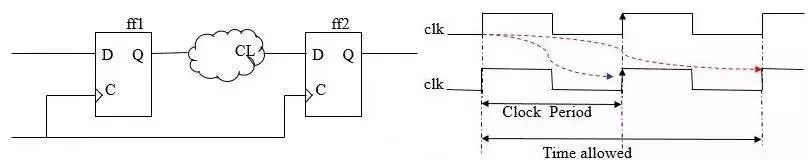

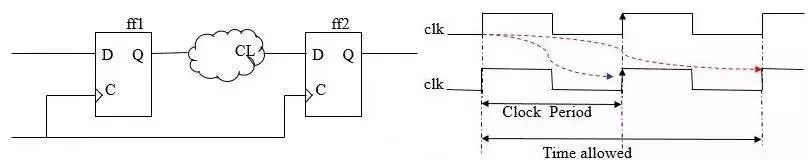

0 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

隨著科技的不斷進步,光纖技術已經成為現代通信網絡的核心組成部分。其中,光纖反射內存產品作為一種新型的存儲方式,在數據存儲、傳輸和處理等方面具有顯著的優勢,逐漸得到了廣泛的應用。本文將詳細介紹光纖反射

2023-11-11 12:26:12 1110

1110 時序數據庫的一哥 InfluxDB,是我們最初選擇的時序數據庫。但隨著時序曲線的規模變大,InfluxDB 的局限性也開始暴露了出來。同時社區中關于 InfluxDB OOM 的討論也日益增多

2023-10-13 16:04:25 257

257

遇到一個比較有意思的問題。一個朋友問我說:他的電腦內存壞了,想換一條新的內存,換DDR5內存條是不是更好?看了他的配置之后,電腦使用的是DDR4的條子。顯然這是不能換的。

2023-10-10 11:18:13 606

606

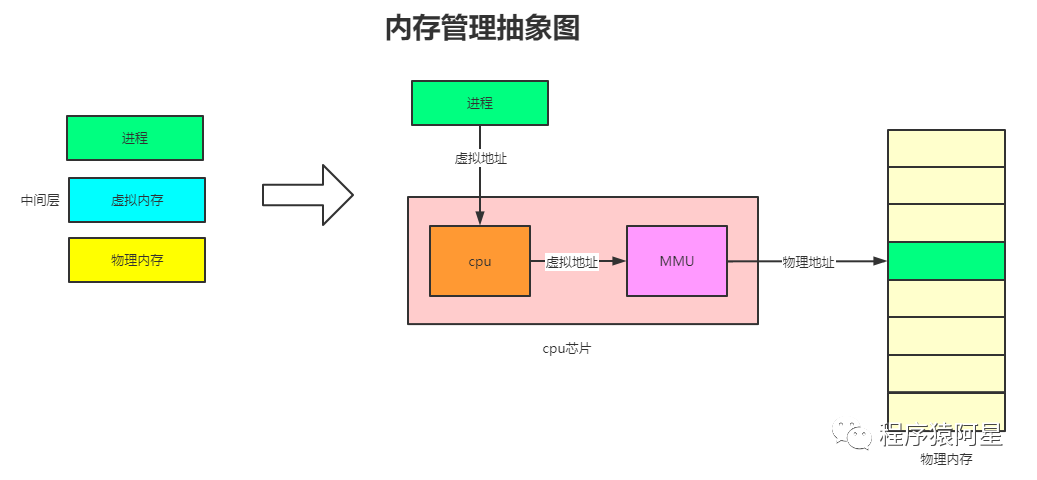

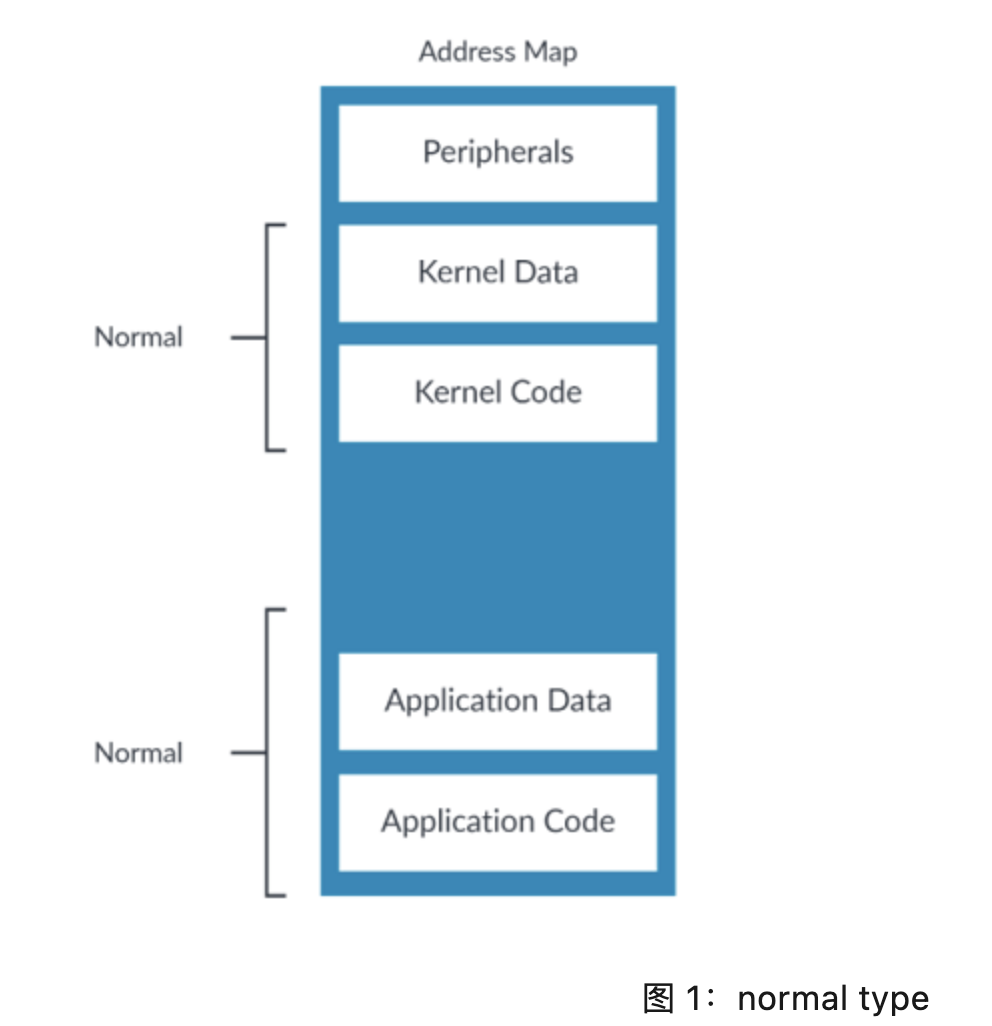

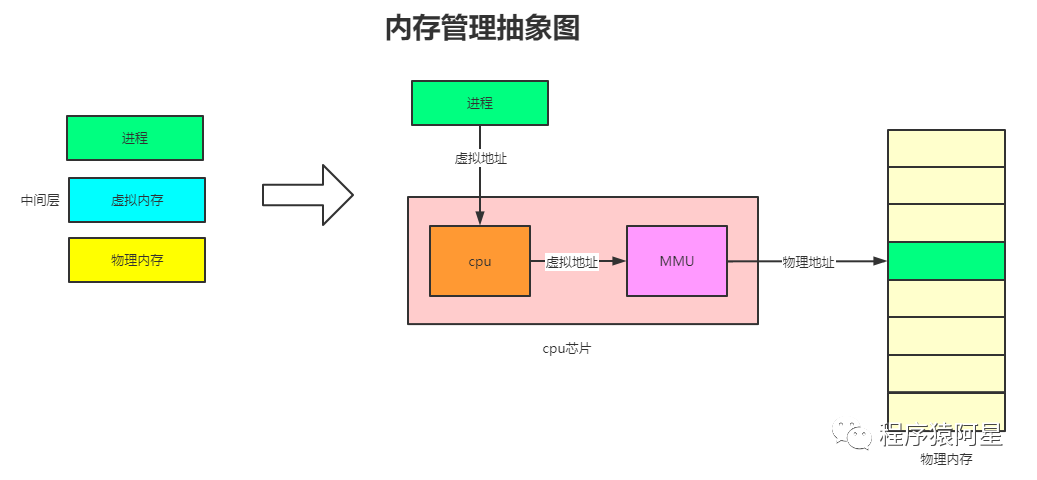

什么是內存 我們想準備運行程序進程需要經過那幾個步驟,這里猜測一下。 首先要去申請內存,操作系統根據現在剩余的地毯空間與你地毯的規模劃分一塊相應大小的內存給你,接著你就可以愉快的運行程序進程

2023-10-09 16:23:42 433

433

在電腦上拆到2條rdram內存條,這個和sdram內存條有什么區別,可以兼容嗎

2023-10-08 09:01:45

事件內存管理定義為在DEM模塊中添加、更新和刪除事件內存條目的過程。DEM模塊確定事件內存條目是新的還是當前存在于事件內存中。 Event retention Event retention定義

2023-10-04 11:45:00 317

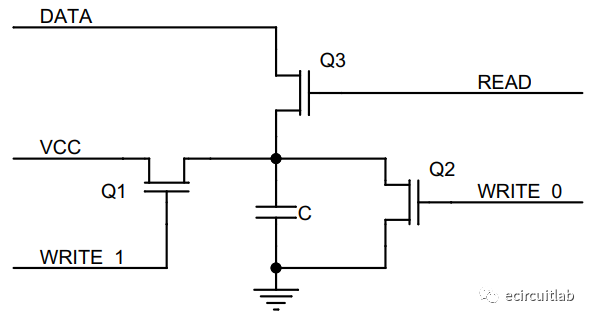

317 SDRAM的內部是一個存儲陣列,將數據“填”進去,你可以它想象成一張表格。和表格的檢索原理一樣,先指定一個行(Row),再指定一個列(Column),我們就可以準確地找到所需要的單元格,這就是內存芯片尋址的基本原理。

2023-09-28 17:26:29 637

637

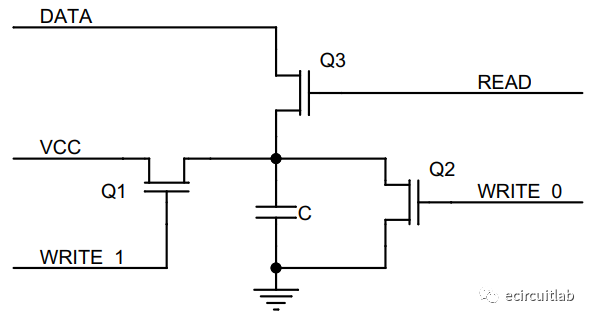

SDRAM(synchronous dynamic random-access memory)即同步動態隨機存取內存。在介紹SDRAM前,我們先了解下DRAM(Dynamic random-access memory),DRAR中文譯為動態隨機存取內存

2023-09-27 15:02:32 1004

1004

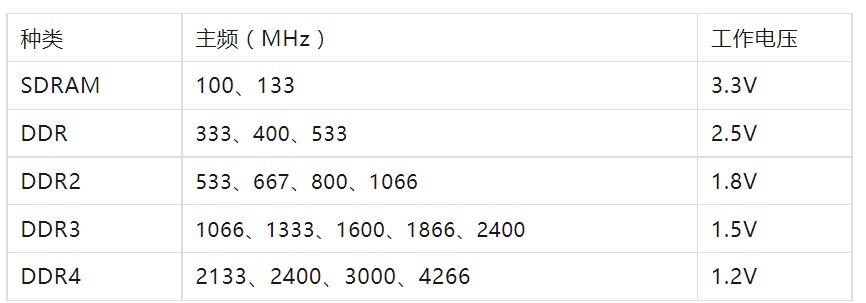

DRAM 由于其結構簡單,設計體積小,在服務器的內存中占主導地位,并得到了長足的發展,從 DRAM 逐漸演進到 SDRAM 再到 DDR SDRAM 系列。SDRAM為同步的動態隨機處理器,同步

2023-09-15 10:13:03 964

964

最新的32Gb DDR5內存芯片,繼續采用12nm級別工藝制造,相比三星1983年推出的4Kb容量的第一款內存產品,容量已經增加了50多萬倍!

2023-09-04 14:28:11 264

264 關于農林氣象站的基本介紹

2023-08-23 16:58:56 220

220 石墨烯電池技術詳細介紹? 石墨烯電池技術是當今電池領域的新寵,它擁有高功率、長壽命、較低的負載,以及高能量密度等特點,正逐漸成為該領域實現突破的重要技術手段之一。本文將為大家詳細介紹石墨烯電池技術

2023-08-22 17:06:07 2468

2468 時序路徑作為時序約束和時序分析的物理連接關系,可分為片間路徑和片內路徑。

2023-08-14 17:50:02 451

451

PL340內存控制器是一款高性能、面積優化的SDRAM或移動SDR內存控制器,兼容高級微控制器總線架構(AMBA)AXI協議。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

本節總結

2023-08-12 06:25:03

PL341內存控制器是一款高性能、面積優化的DDR2 SDRAM內存控制器,兼容高級微控制器總線架構(AMBA)AXI協議。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

本節總結了周期模型的功能與硬件的功能,以及周期模型的性能和準確性。

2023-08-12 06:01:49

我手上有一張DDR200T的開發板,板載了一塊512M的SDRAM內存,板子燒了一個UX600的demosoc,我是要在這個板子跑RT-Thread。

要是想使用這塊SDRAM應該怎么做呢?應該

2023-08-11 08:05:46

SDRAM全稱Synchronous Dynamic RAM,同步動態隨機存儲器。首先,它是RAM,即隨機存儲器的一種。

2023-08-08 15:10:46 896

896

貼片Y電容是一種常見的電子元件,它在電子設備中具有廣泛的應用。貼片Y電容的型號眾多,每個型號都有其獨特的特點和應用場景。今天弗瑞鑫小編將詳細介紹貼片Y電容的各種型號及其特點,以便讀者更好地了解和選擇適合自己應用的型號。

2023-08-04 08:41:38 558

558 關于該產品是DMC-620的高級概述。

DMC-620是Arm AMBA 5芯片SoC外設,由Arm開發、測試和許可。它是一款高性能、區域優化的內存控制器,與AMBA 5 CHI協議兼容。

它支持

2023-08-02 11:55:49

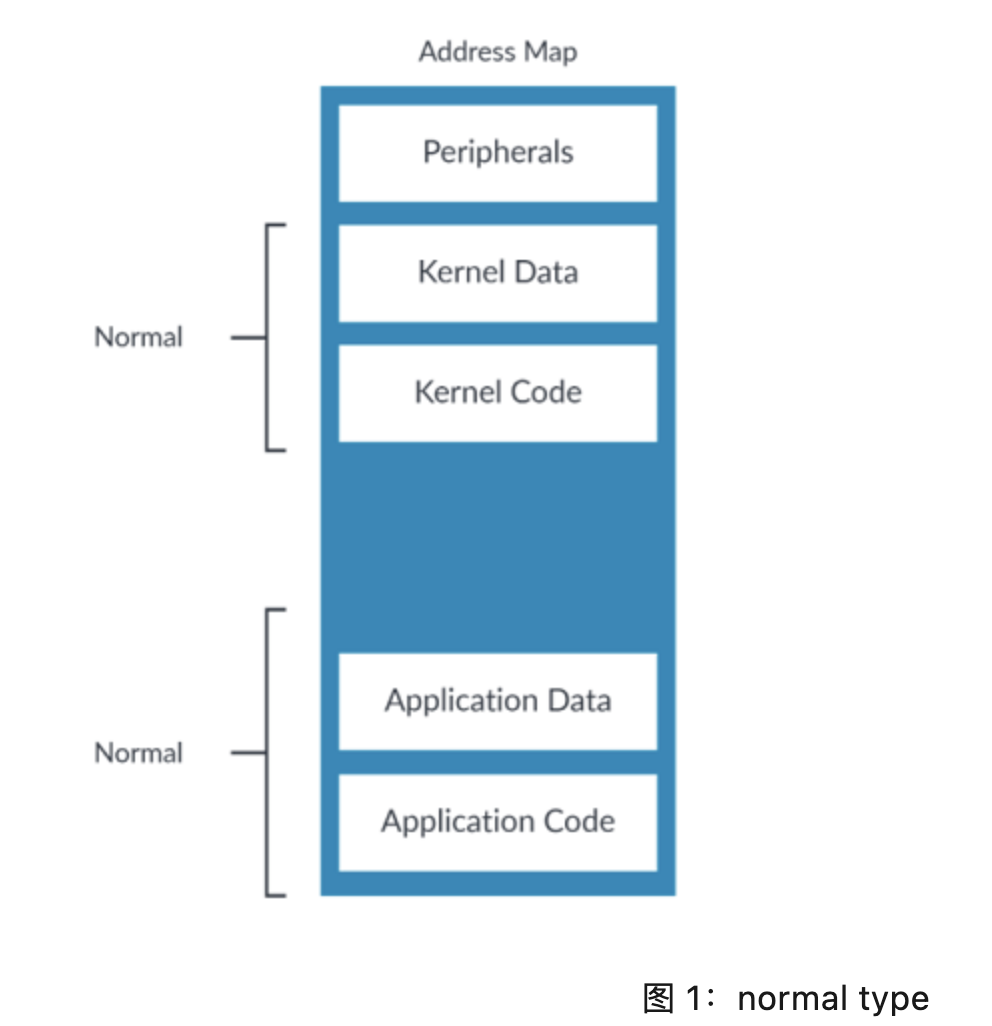

1. 本指南介紹由 Armv8-A 架構定義的內存定序模型,并介紹所提供的不同內存障礙;本指南還確定一些需要明確定序的常見情況,以及如何使用內存障礙以確保實現正確操作;本指南適用于低級別代碼的開發者

2023-08-02 11:03:30

可以作為內存堆,但是 STM32 內部 RAM 比較小,遇到那些需要大容量 RAM 的應用就不行了,如音視頻處理。不過? STM32 可以外接 SRAM 甚至大容量的 SDRAM ,如果

2023-07-30 10:47:42 500

500 的工作原理 DDR芯片內存的工作原理可以分為兩部分, 一部分是時序,一部分是數據傳輸 。 控制DDR內存的時序,是由內存控制器控制的,它負責管理內存的讀寫操作。內存控制器會向DDR內存發送時鐘信號,這個時鐘信號被稱為 系統時鐘 。 DDR內存的數據傳輸,是通過前沿和下降沿來實現的

2023-07-28 13:12:06 1883

1883

時序:字面意思,時序就是時間順序,實際上在通信中時序就是通信線上按照時間順序發生的電平變化,以及這些變化對通信的意義就叫時序。

2023-07-26 10:06:03 1641

1641 今天要介紹的時序基本概念是Mode(模式). 這是Multiple Scenario環境下Sign off的一個重要概念。芯片的設計模式包括最基本的功能function模式,以及各種各樣相關的測試模式。

2023-07-10 17:21:38 1716

1716

今天主要介紹的時序概念是時序庫lib,全稱liberty library format(以? lib結尾),

2023-07-07 17:15:00 1638

1638

今天我們要介紹的時序基本概念是Timing arc,中文名時序弧。這是timing計算最基本的組成元素,在昨天的lib庫介紹中,大部分時序信息都以Timing arc呈現。

2023-07-06 15:00:02 1396

1396

今天我們要介紹的時序分析概念是 **時序路徑** (Timing Path)。STA軟件是基于timing path來分析timing的。

2023-07-05 14:54:43 985

985

今天要介紹的時序分析基本概念是Slew,信號轉換時間,也被稱為transition time。

2023-07-05 14:50:53 1530

1530

今天要介紹的時序分析基本概念是skew,我們稱為偏差。

2023-07-05 10:29:37 2119

2119

今天我們要介紹的時序分析基本概念是MMMC分析(MCMM)。全稱是multi-mode, multi-corner, 多模式多端角分析模式。這是在先進工藝下必須要使用的一種時序分析模式。

2023-07-04 15:40:13 1461

1461

今天要介紹的時序分析基本概念是Latency, 時鐘傳播延遲。主要指從Clock源到時序組件Clock輸入端的延遲時間。

2023-07-04 15:37:08 1305

1305

??本文主要介紹了時序設計和時序約束。

2023-07-04 14:43:52 691

691 ??本文主要介紹了靜態時序分析 STA。

2023-07-04 14:40:06 525

525

今天我們要介紹的時序分析概念是 **AOCV** 。全稱Stage Based Advanced OCV。我們知道,在OCV分析過程中,我們會給data path,clock path上設定單一的timing derate值。

2023-07-03 16:29:05 1155

1155

今天我們要介紹的基本sdc是 **時序特例** ,也就是我們常說的Path exception。針對一些路徑需要的一些特殊設定,常用的有set_false_path, set_multicycle_path, set_max_delay,set_min_delay等

2023-07-03 15:34:52 471

471

今天我們要介紹的時序分析概念是clock gate。 clock gate cell是用data signal控制clock信號的cell,它被頻繁地用在多周期的時鐘path,可以節省功耗。

2023-07-03 15:06:03 1481

1481

今天我們要介紹的時序分析概念是 **min pulse width** ,全稱為最小脈沖寬度檢查。這也是一種非常重要的timing arc check,經常用在時序器件或者memory上面。

2023-07-03 14:54:11 1197

1197

今天要介紹的時序分析基本概念是lookup table。中文全稱時序查找表。

2023-07-03 14:30:34 664

664

向量和動態仿真 。本文將介紹靜態時序分析的基本概念和方法,包括時序約束,時序路徑,時序裕量,setup檢查和hold檢查等。 時序路徑 同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最

2023-06-28 09:38:57 714

714

同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最壞情況下滿足時序要求,我們需要進行靜態時序分析,即不依賴于測試向量和動態仿真,而只根據每個邏輯門的最大延遲來檢查所有可能的時序違規路徑。

2023-06-28 09:35:37 490

490

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向導(Constraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1834

1834

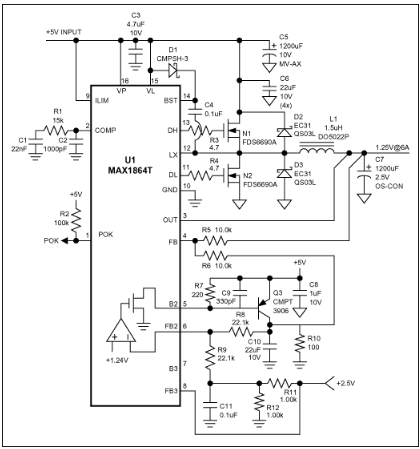

本設計筆記顯示了用于工作站和服務器的高速內存系統的雙倍數據速率 (DDR) 同步 DRAM (SDRAM)。使用MAX1864 xDSL/電纜調制解調器電源,電路產生等于并跟蹤VREF的終止電壓(VTT)。

2023-06-26 10:34:36 549

549

前面幾篇文章已經詳細介紹了FPGA時序約束基礎知識以及常用的時序約束命令,相信大家已經基本掌握了時序約束的方法。

2023-06-23 17:44:00 1260

1260

本文介紹 Armv8-A 架構的內存序模型,并介紹 arm 的各種內存屏障。本文還會指出一些需要明確內存保序的場景,并指明如何使用內存屏障以讓程序運行正確。

2023-06-15 18:19:37 864

864

,頻率更高:采用超短進口雙頭探針設計,相比同類測試產品使IC與PCB之間數據傳輸距離更短;

⑥可自行維修,節省時間:采用帶定位孔內存顆粒測試專用PCB,探針板與PCB 孔定位,保證探針與PCB精確定位;以上就是關于DDR內存條治具六大特點 的介紹 ,希望對您有益~

2023-06-15 15:45:22

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1229

1229 在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 6199

6199

內存管理是計算機系統中負責管理系統內存資源的一種機制,主要包括內存分配、內存釋放、內存映射和虛擬內存管理等方面。它是計算機系統中非常重要的一個組成部分,能夠有效地提高系統的資源利用率和應用程序的性能。

2023-05-29 14:09:37 1356

1356

內存,也就是電腦中的內存條,其用于暫時存放CPU中的運算數據,以及與硬盤等外部存儲器交換的數據。只要計算機開始運行,操作系統就會把需要運算的數據從內存調到CPU中進行運算,當運算完成,CPU將結果傳送出來。內存決定了我們應用的上限,也就是我們能夠同時運行多少應用,從硬盤向CPU調取多少數據。

2023-05-26 11:22:32 15066

15066

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序邏輯電路的核心部分——計數器。

2023-05-22 17:01:29 1879

1879

5G單站驗證詳細介紹

2023-05-22 12:38:38 309

309

本篇介紹了UML時序圖的基礎知識,并通過visio繪制一個物聯網設備WIFI配網的UML時序圖實例,來介紹UML時序圖的畫法與所表達的含義。

2023-05-16 09:09:22 1225

1225

本文介紹接口和協議時序

2023-05-10 15:37:16 2022

2022

我想將 i.MX RT1024 與外部 64MB SDRAM 一起使用。根據數據表,它支持 8/16 位 SDRAM 外部存儲器接口。從性能的角度來看,哪種模式更好?如何?如果有任何鏈接/參考可以通過此詳細信息,請告訴我。謝謝

2023-05-05 11:17:30

本公司目前MCU系列,到目前為止, SWM34x 支持外接8M16M SDRAM,SWD34S系列已經把SDRAM合封入芯片,合封的SDRAM大小根據芯片型號不同,具體見官方手冊。

2023-04-28 09:30:22 1496

1496

想用SDRAM運行SAI,修改內存配置后好像不能正常運行。是什么原因?

我在 SDK 中使用 evkmimxrt1020_sai_edma_record_playback,并調整 RAM 以指向 BOARD_SDRAM。該程序似乎無法正常運行。

2023-04-26 06:42:50

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條單向數據線配置,并進行主機接收從機發送。 1、SPI簡介及相關函數介紹關于SPI單工通信模式下1條時鐘線和1條單向數據線配置介紹,在第46章已經

2023-04-25 16:50:41

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條雙向數據線配置,并進行主機接收從機發送。 1、SPI簡介及相關函數介紹關于SPI單工通信模式下1條時鐘線和1條雙向數據線配置介紹,在第46章已經

2023-04-25 16:48:14

詳細介紹安科瑞產品中關于絕緣監測和絕緣故障定位的相關產品,從含義,解決方法,產品技術參數等 詳細介紹。

2023-04-23 15:29:14 495

495

大佬們,這個free在finsh里面介紹是列出系統使用的內存,我把sdram打開了,在list——memheap里面能找到sdram,為什么在free里面的total不包括sdram的大小

2023-04-14 10:06:25

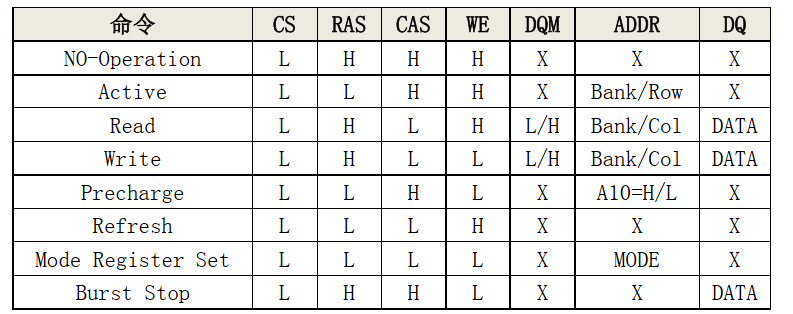

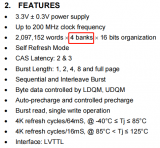

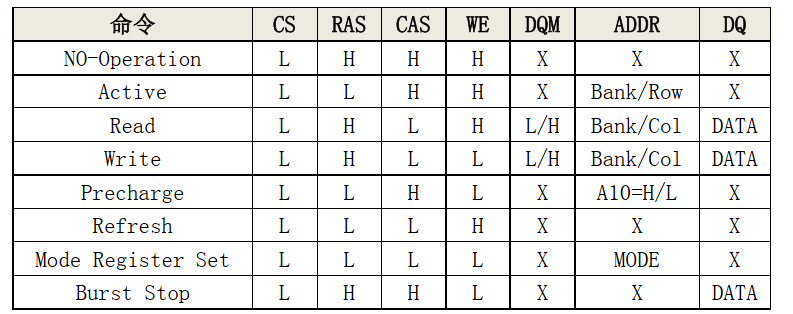

SDRAM的驅動需要用到一些命令,介紹幾個常見的命令。

2023-04-04 17:13:19 1814

1814

DDR內存1代已經淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 2867

2867

本章節主要介紹一些簡單的時序約束的概念。

2023-03-31 16:37:57 928

928

SDRAM SLICE CARD

2023-03-30 12:05:53

我正在嘗試修改 SDK 示例以使用一個 SDRAM 而不是板上可用的兩個。我修改了內存設置和DCD文件。我嘗試了多種配置,但總是以錯誤告終。如何使用一個 SDRAM 運行 lVGL 示例?

2023-03-30 07:27:47

讀寫整個行,我們可以利用突發終止命令將其終止掉。 下面兩個時序就是SDRAM的頁讀頁寫時序,在某個位置使用突發終止命令將其終止掉。 頁寫被終止時序圖:頁讀被終止時序圖: 具體的參考設計請參考圖像顯示系統設計。

2023-03-27 17:09:14

在win10/win11下使用PADS layout時,報錯‘’Out of memory‘’,或者報錯‘’數據庫嚴重錯誤編號 2010‘’已經嘗試過:1.加大內存條內存,無法解決2.加大虛擬內存

2023-03-25 18:58:13

SDRAM支持讀寫的長度為1、2、4、8和一行(整頁)。

具體的SDR SDRAM的介紹可以查看手冊。下面只介紹幾個相對重要的時序圖。

在SDR SDRAM正常使用之前,需要進行初始化。初始化

2023-03-23 17:40:58

電子發燒友App

電子發燒友App

評論