更上一層樓???

改動很小,也就是把光模塊的扇出改成激光孔的設計,客戶就“偷偷瞞著我們”自己修改并投了板。花了大價錢用了激光孔的加工工藝,等板子回來的一刻,心情肯定是激動萬分了,期待測試出來的性能更好。但是

2024-03-19 14:53:25

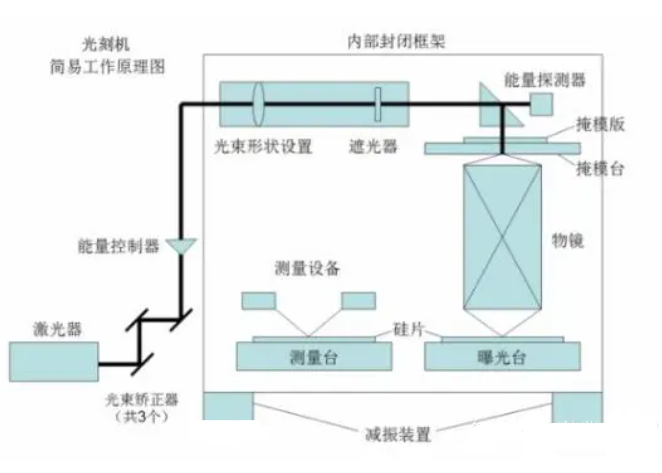

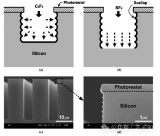

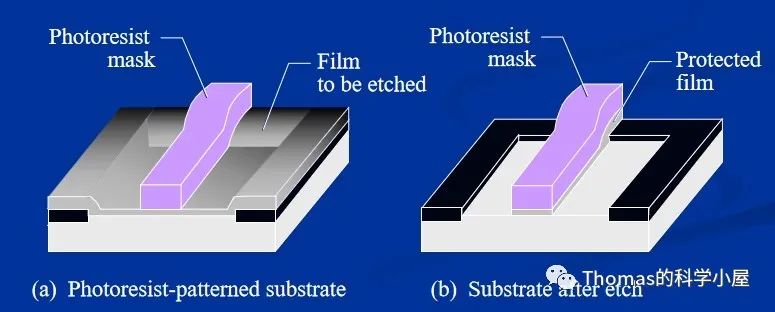

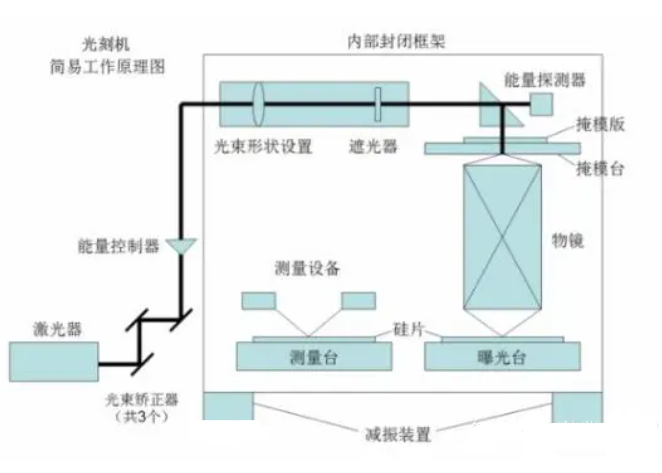

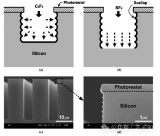

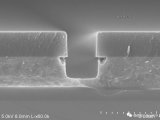

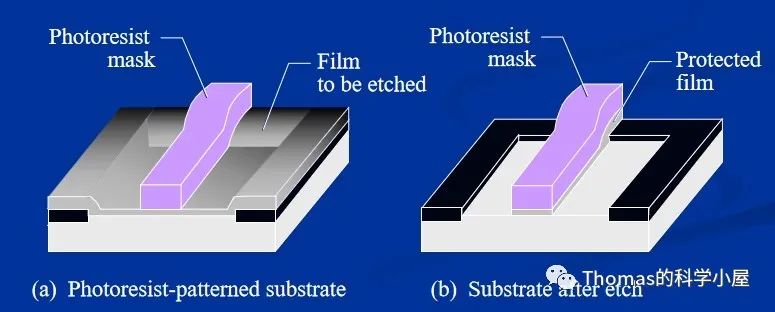

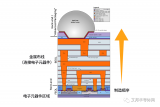

刻蝕機的刻蝕過程和傳統的雕刻類似,先用光刻技術將圖形形狀和尺寸制成掩膜,再將掩膜與待加工物料模組裝好,將樣品置于刻蝕室內,通過化學腐蝕或物理磨蝕等方式將待加工物料表面的非掩膜區域刻蝕掉,以得到所需的凹槽和溝槽。

2024-03-11 15:38:24 459

459

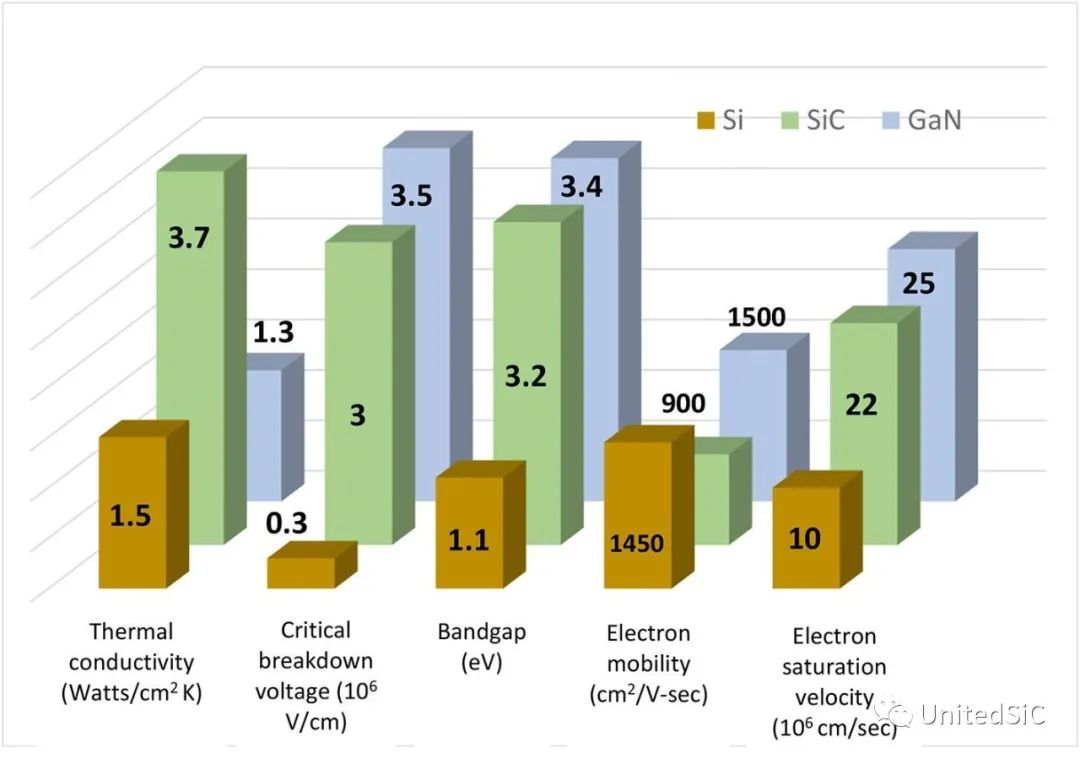

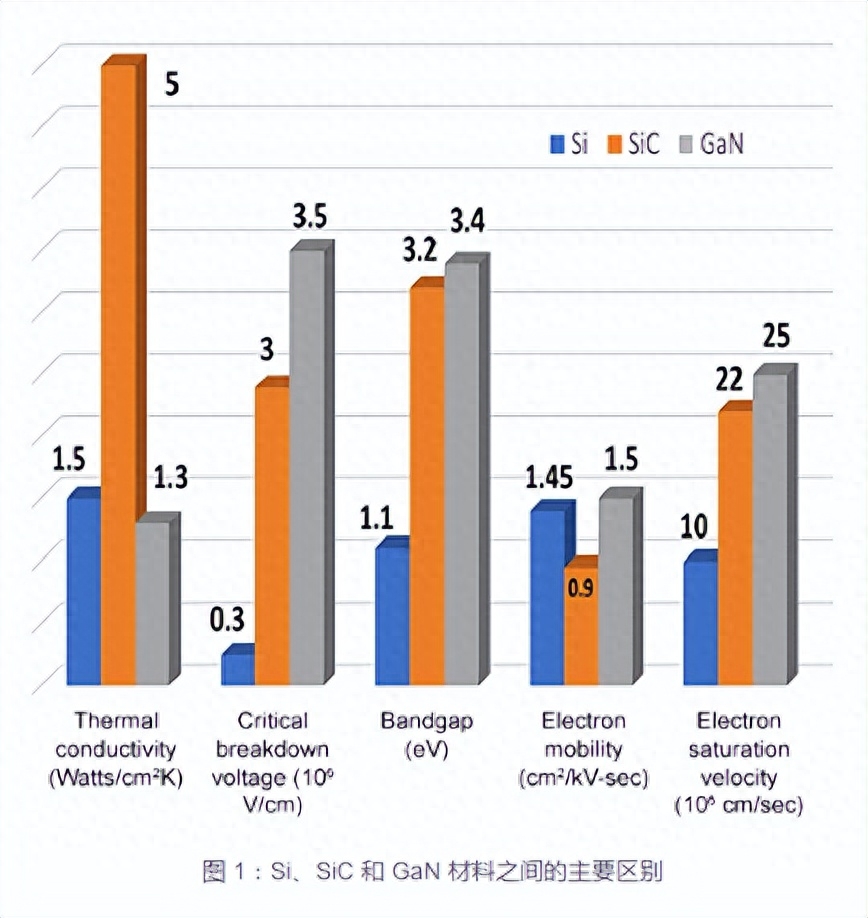

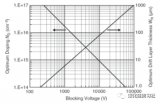

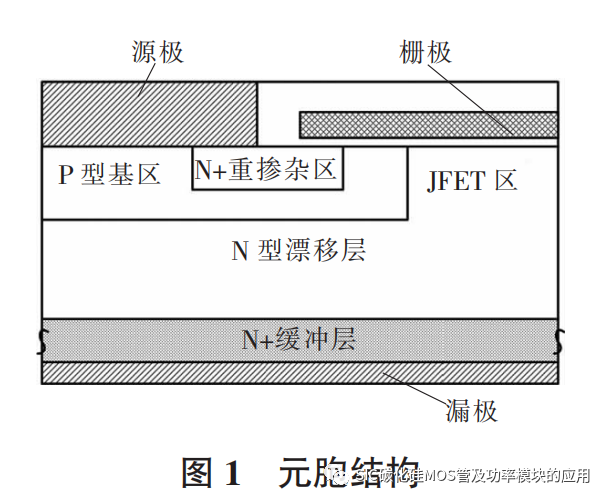

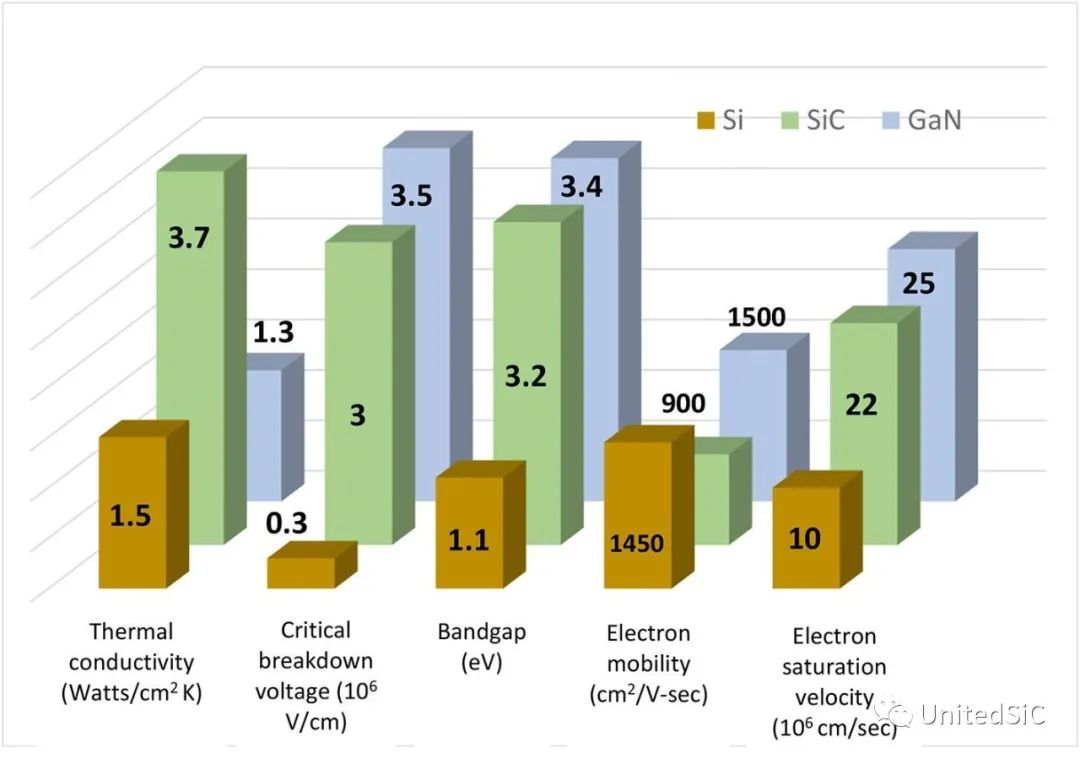

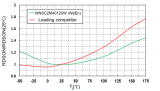

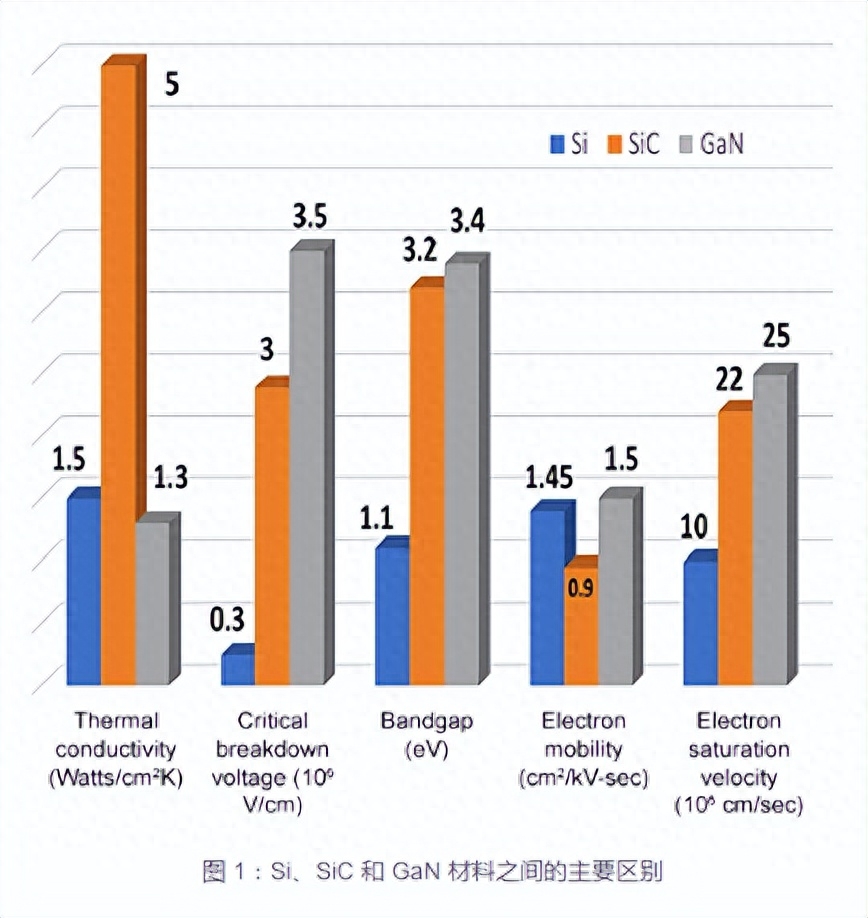

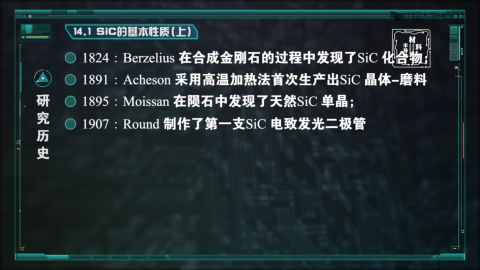

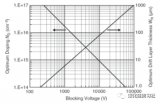

SiC器件的核心優勢在于其寬禁帶、高熱導率、以及高擊穿電壓。具體來說,SiC的禁帶寬度是硅的近3倍,這意味著在高溫下仍可保持良好的電性能;其熱導率是硅的3倍以上,有利于高功率應用中的熱管理。

2024-03-08 10:27:15 42

42

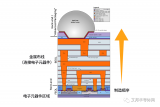

共讀好書 杜隆純 何勇 劉洪偉 劉曉鵬 (湖南國芯半導體科技有限公司 湖南省功率半導體創新中心) 摘要: 針對SiC功率器件封裝的高性能和高可靠性要求,文章研究了芯片雙面銀燒結技術與粗銅線超聲鍵合

2024-03-05 08:41:47 104

104

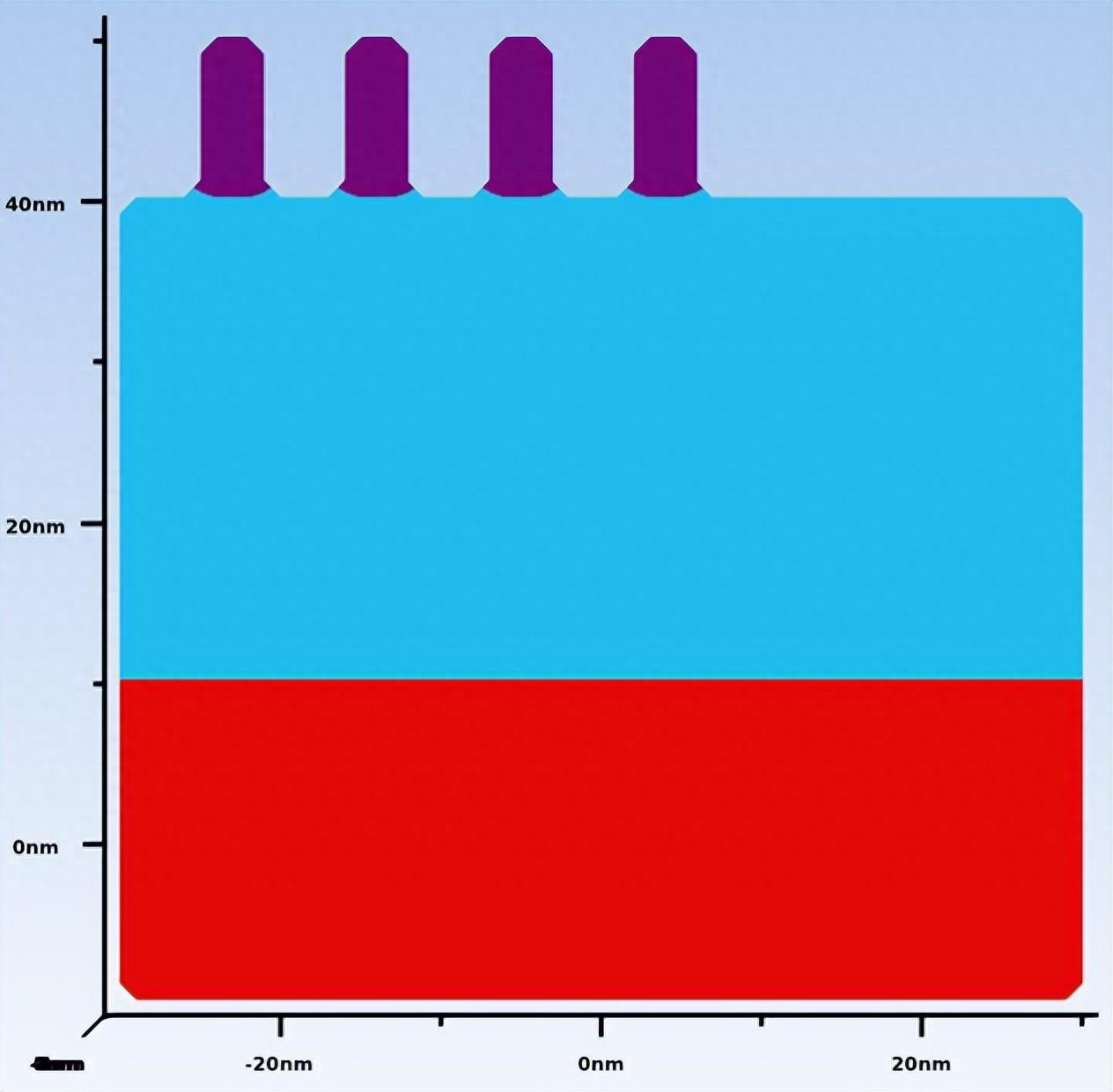

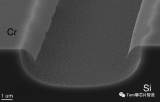

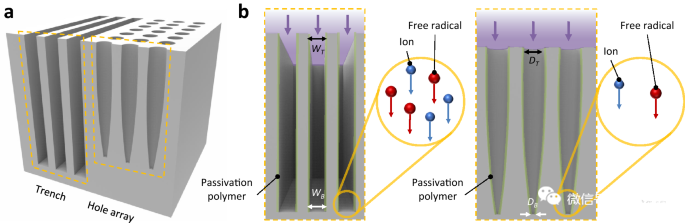

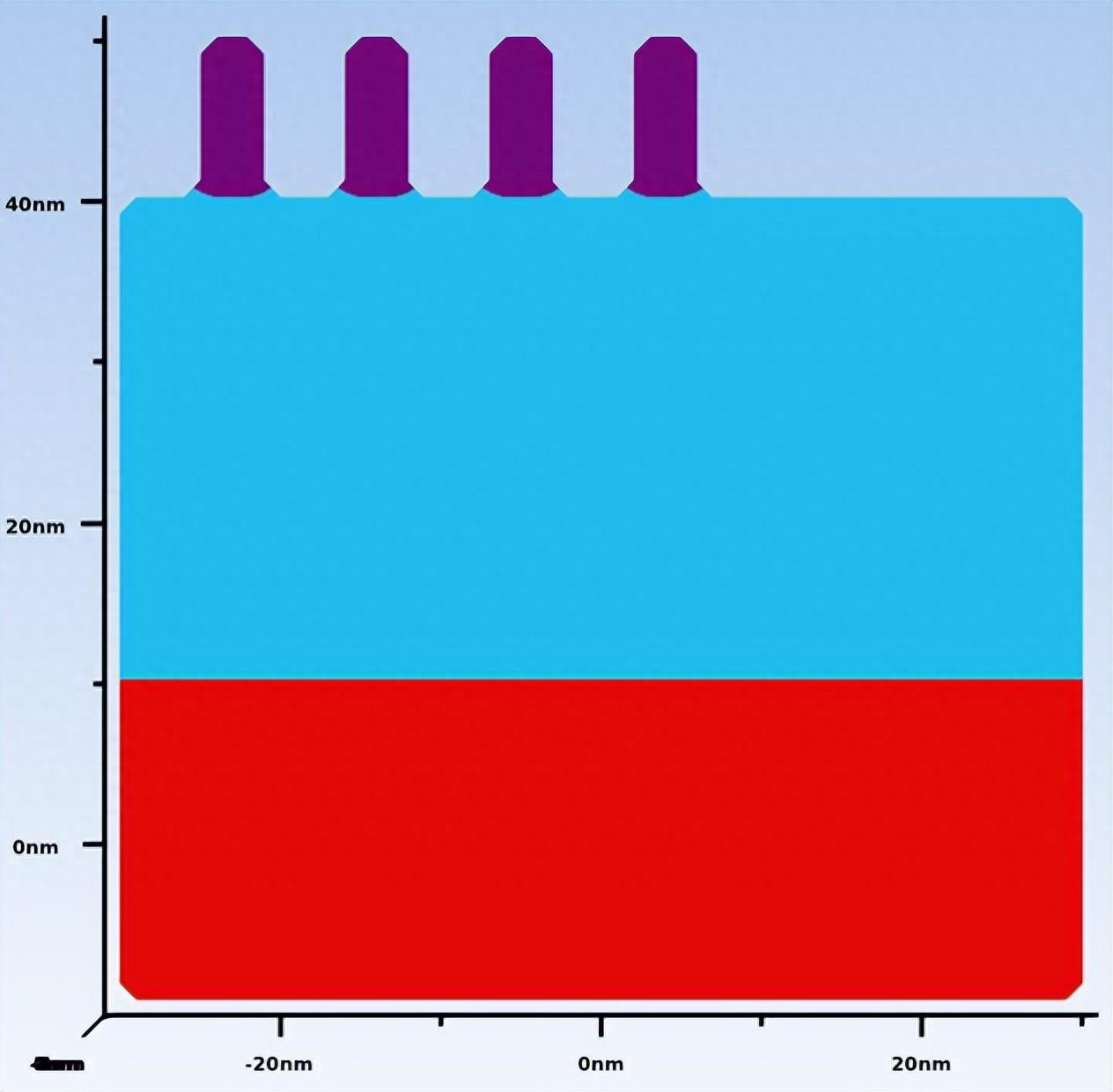

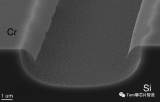

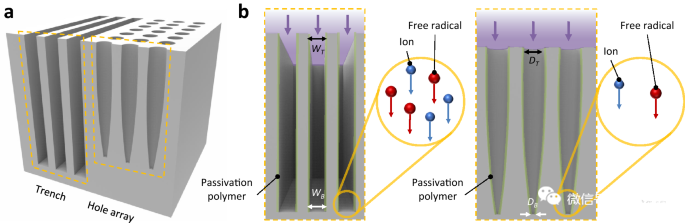

的 2.5D/3D 封裝技術可以實現芯片之間的高速、低功耗和高帶寬的信號傳輸。常見的垂直 TSV 的制造工藝復雜,容易造成填充缺陷。錐形 TSV 的側壁傾斜,開口較大,有利于膜層沉積和銅電鍍填充,可降低工藝難度和提高填充質量。在相對易于實現的刻蝕條件下制備

2024-02-25 17:19:00 119

119

影響深硅刻蝕的關鍵參數有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:44:39 283

283

影響深硅刻蝕的關鍵參數有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:40:16 19

19

在半導體加工工藝中,常聽到的兩個詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現,有著千絲萬縷的聯系,這一節介紹半導體刻蝕工藝。

2024-01-26 10:01:58 547

547

干法刻蝕技術是一種在大氣或真空條件下進行的刻蝕過程,通常使用氣體中的離子或化學物質來去除材料表面的部分,通過掩膜和刻蝕參數的調控,可以實現各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結構

2024-01-20 10:24:56 1106

1106

使用SEMulator3D?工藝步驟進行刻蝕終點探測 作者:泛林集團 Semiverse Solutions 部門軟件應用工程師 Pradeep Nanja 介紹 半導體行業一直專注于使用先進的刻蝕

2024-01-19 16:02:42 128

128

對DRIE刻蝕,是基于氟基氣體的高深寬比硅刻蝕技術。與RIE刻蝕原理相同,利用硅的各向異性,通過化學作用和物理作用進行刻蝕。不同之處在于,兩個射頻源:將等離子的產生和自偏壓的產生分離

2024-01-14 14:11:59 510

510

在紅外探測器的制造技術中,臺面刻蝕是完成器件電學隔離的必要環節。

2024-01-08 10:11:01 206

206

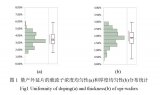

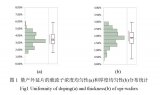

探索SiC外延層的摻雜濃度控制與缺陷控制,揭示其在高性能半導體器件中的關鍵作用。

2024-01-08 09:35:41 623

623

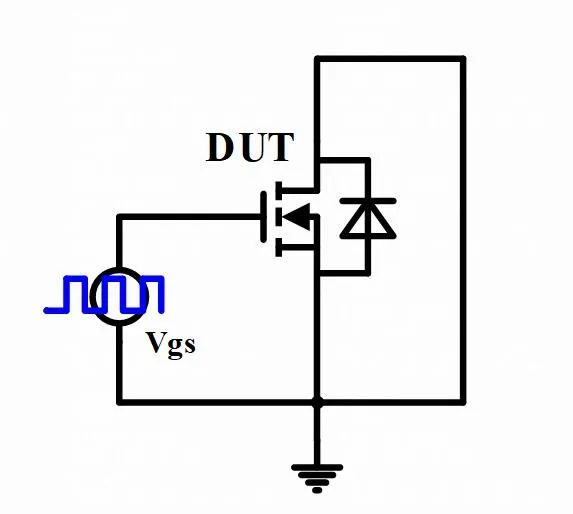

等大功率領域,能顯著提高效率,降低裝置體積。在這些應用領域中,對功率器件的可靠性要求很高,為此,針對自主研制的3300V SiC MOSFET 開展柵氧可靠性研究。首先,按照常規的評估技術對其進行了高溫

2024-01-04 09:41:54 594

594

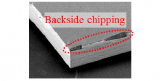

摘要:論述了傳統的集成電路裝片工藝面臨的挑戰以及現有用DAF膜(DieAttachmentFilm,裝片膠膜)技術進行裝片的局限性;介紹了一種先進的、通過噴霧結合旋轉的涂膠模式制備晶圓背面

2023-12-30 08:09:58 337

337

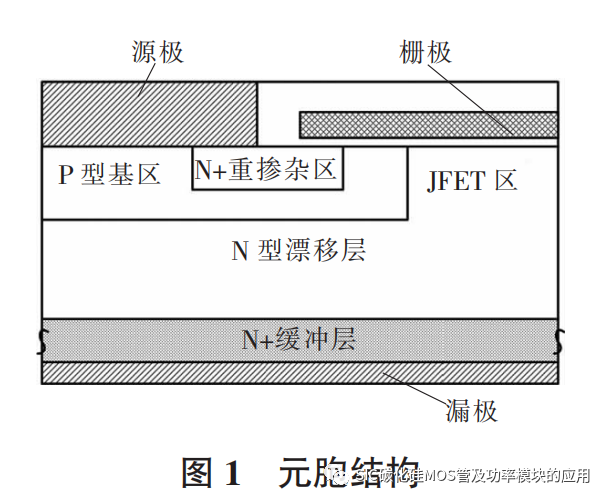

SiC具有高效節能、穩定性好、工作頻率高、能量密度高等優勢,SiC溝槽MOSFET(UMOSFET)具有高溫工作能力、低開關損耗、低導通損耗、快速開關速度等特點

2023-12-27 09:34:56 473

473

TOPCon 電池的制備工序包括清洗制絨、正面硼擴散、BSG 去除和背面刻蝕、氧化層鈍化接觸制備、正面氧化鋁沉積、正背面氮化硅沉積、絲網印刷、燒結和測試分選,約 12 步左右。從技術路徑角度:LPCVD 方式為目前量產的主流工藝,預計 PECVD 路線有望成為未來新方向。

2023-12-26 14:59:11 2707

2707

SiC材料具有優異的高溫穩定性、耐腐蝕性、熱導性能和機械強度等優勢,因此受到廣泛關注和應用。

2023-12-26 10:13:44 462

462

合的生產工藝就直接影響了HDI板成品的可靠性,壓合的方法也尤為重要,本文主要介紹HDI(盲、埋孔)板的壓合工藝問題。

機械盲孔板壓合

壓合是利用高溫高壓使半固化片受熱融化,并使其流動,再轉變為固化片

2023-12-25 14:09:38

在新能源產業強勁需求下,全球SiC產業步入高速成長期,推升了對SiC襯底產能的需求。

2023-12-19 10:09:18 294

294

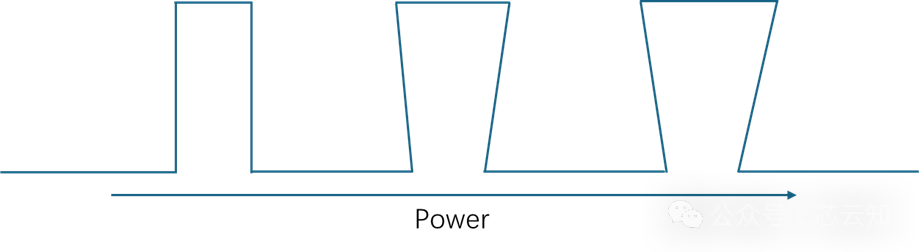

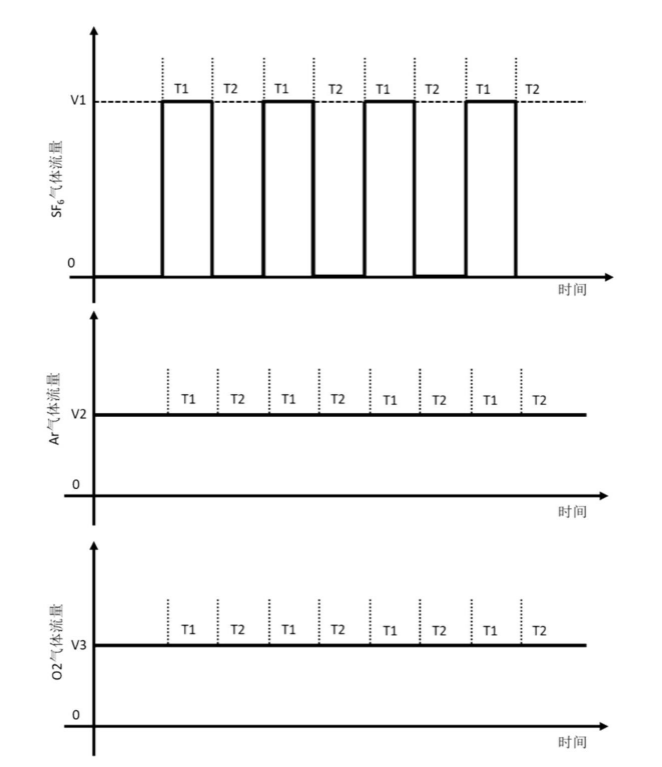

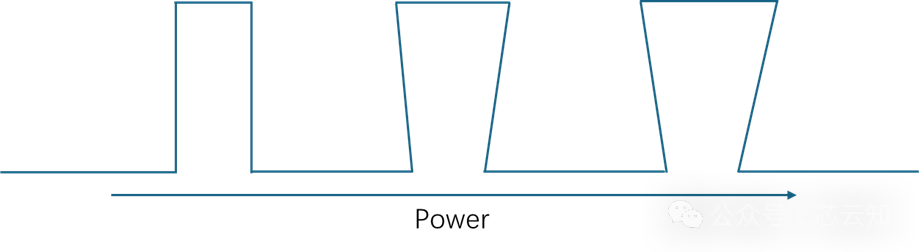

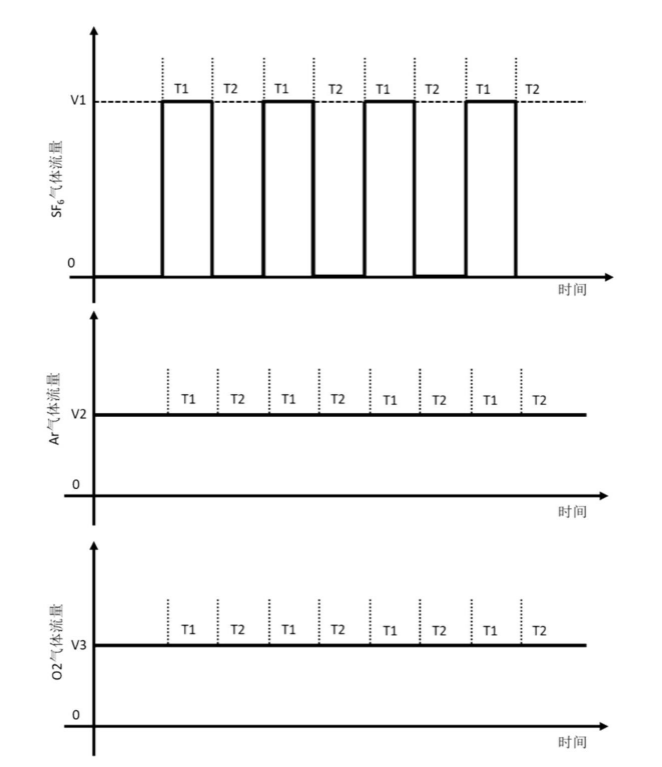

該專利詳細闡述了一種針對含硅有機介電層的高效刻蝕方法及相應的半導體工藝設備。它主要涉及到通過交替運用至少兩個刻蝕步驟來刻蝕含硅有機介電層。這兩個步驟分別為第一刻蝕步驟和第二刻蝕步驟。

2023-12-06 11:58:16 370

370

W刻蝕工藝中使用SF6作為主刻步氣體,并通過加入N2以增加對光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負載效應,避免產生凹坑,并使用對TiN有高選擇比的化學氣體進行刻蝕。

2023-12-06 09:38:53 1536

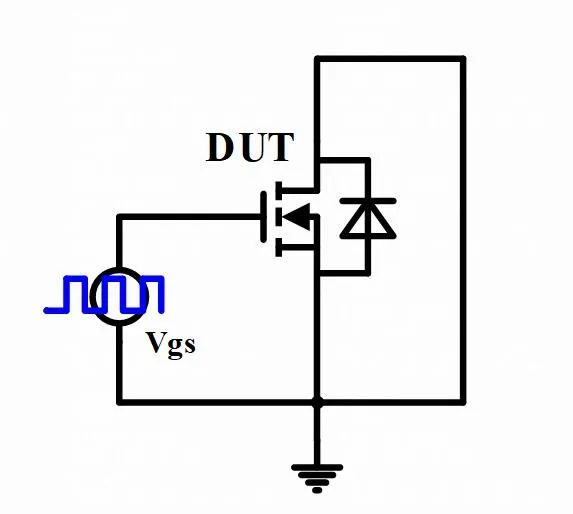

1536 SiC MOSFET AC BTI 可靠性研究

2023-11-30 15:56:02 345

345

還沒使用SiC FET?快來看看本文,秒懂SiC FET性能和優勢!

2023-11-29 16:49:23 273

273

在晶圓生產工藝的結尾,有些晶圓需要被減薄(晶圓減薄)才能裝進特定的封裝體重,以及去除背面損傷或結;對于有將芯片用金-硅共晶封裝中的芯片背面要求鍍一層金(背面金屬化,簡稱背金);

2023-11-29 12:31:26 203

203

半導體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創建所需圖形

2023-11-27 16:54:26 256

256

濕法刻蝕由于成本低、操作簡單和一些特殊應用,所以它依舊普遍。

2023-11-27 10:20:17 452

452

合封芯片工藝是一種先進的芯片封裝技術,將多個芯片或不同的功能的電子模塊封裝在一起,從而形成一個系統或子系統。合封芯片更容易實現更復雜、更高效的任務。本文將從合封芯片工藝的工作原理、應用場景、技術要點等方面進行深入解讀。

2023-11-24 17:36:32 332

332 近日,一家日本廠商發布了一種全新的SiC晶圓劃片工藝,與傳統工藝相比,這項技術可將劃片速度提升100倍,而且可以幫助SiC廠商增加13%的芯片數量。

2023-11-21 18:15:09 901

901

在芯片制程中,很多金屬都能用等離子的方法進行刻蝕,例如金屬Al,W等。但是唯獨沒有聽說過干法刻銅工藝,聽的最多的銅互連工藝要數雙大馬士革工藝,為什么?

2023-11-14 18:25:33 2618

2618

但是里面也有幾個關鍵的工藝參數需要控制的。同樣Etch GaAs也可以用ICP干法刻蝕的工藝,比濕法工藝效果要好些,側壁也垂直很多。

2023-11-14 09:31:29 406

406 晶圓承載系統是指針對晶圓背面減薄進行進一步加工的系統,該工藝一般在背面研磨前使用。晶圓承載系統工序涉及兩個步驟:首先是載片鍵合,需將被用于硅通孔封裝的晶圓貼附于載片上;其次是載片脫粘,即在如晶圓背面凸點制作等流程完工后,將載片分離。

2023-11-13 14:02:49 1410

1410

點擊藍字?關注我們 對于高壓開關電源應用,碳化硅或 SiC MOSFET 與傳統硅 MOSFET 和 IGBT 相比具有顯著優勢。SiC MOSFET 很好地兼顧了高壓、高頻和開關性能優勢。它是電壓

2023-11-02 19:10:01 361

361

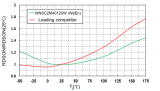

下面將對于SiC MOSFET和SiC SBD兩個系列,進行詳細介紹

2023-11-01 14:46:19 736

736

為什么TPS54331DR這個DCDC芯片這么多人用的,有什么優勢?

2023-10-27 06:13:48

碳化硅(SiC)技術已達到臨界點,即不可否認的優勢推動技術快速采用的狀態。 如今,出于多種原因,希望保持競爭力并降低長期系統成本的設計人員正在轉向基于SiC的技術,其中包括: 降低總擁有

2023-10-13 09:24:17 824

824 刻蝕(或蝕刻)是從晶圓表面去除特定區域的材料以形成相應微結構。但是,在目標材料被刻蝕時,通常伴隨著其他層或掩膜的刻蝕。

2023-10-07 14:19:25 2067

2067

有過深硅刻蝕的朋友經常會遇到這種情況:在一片晶圓上不同尺寸的孔或槽刻蝕速率是不同的。

2023-10-07 11:29:17 1446

1446

,華潤微電子在寬禁帶半導體領域匠心深耕,利用全產業鏈優勢,從產品設計、制造工藝、封裝技術和系統應用等方面大力推進SiC器件產品產業化。華潤微SiC SBD系列產品具有可媲美國際先進水平的卓越產品性能,均已

2023-10-07 10:12:26

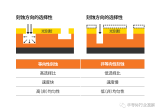

在半導體制造中,刻蝕工序是必不可少的環節。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術各有優勢,也各有一定的局限性,理解它們之間的差異是至關重要的。

2023-09-26 18:21:00 3305

3305

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-09-24 17:42:03 995

995

硅碳化物(SiC)技術已經達到了臨界點,即無可否認的優勢推動一項技術快速被采用的狀態。

2023-09-07 16:13:00 659

659

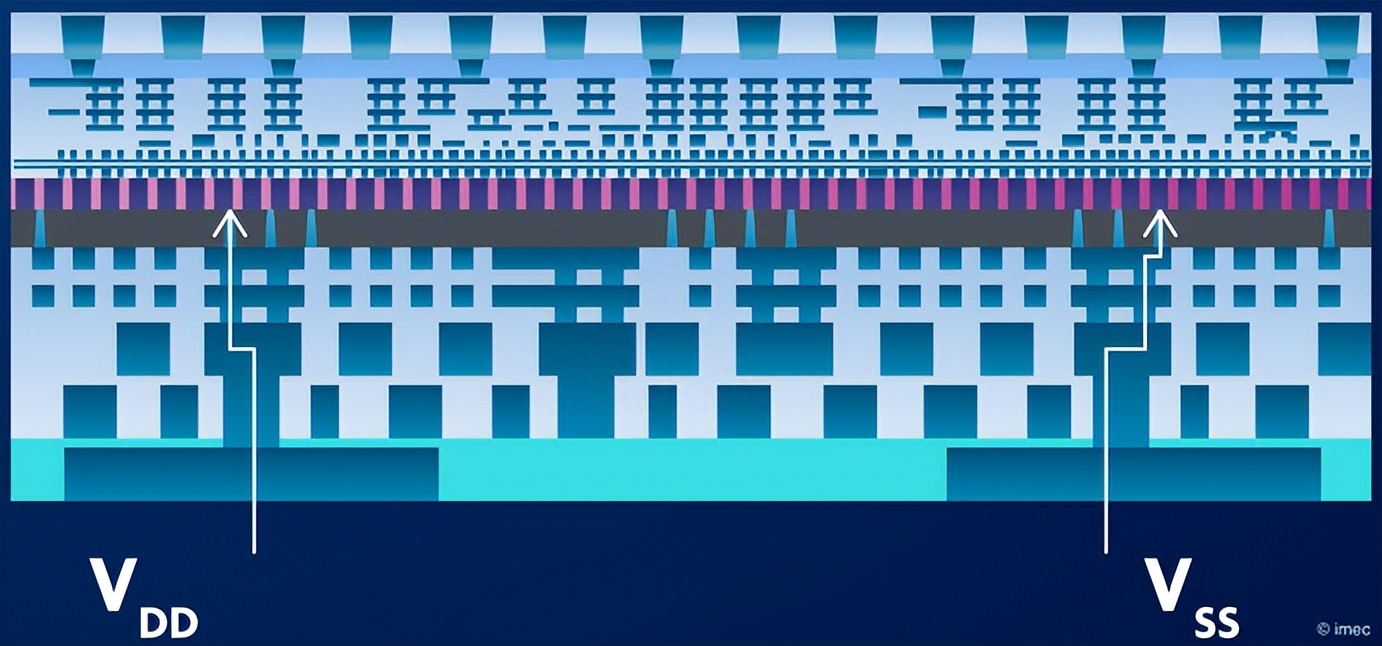

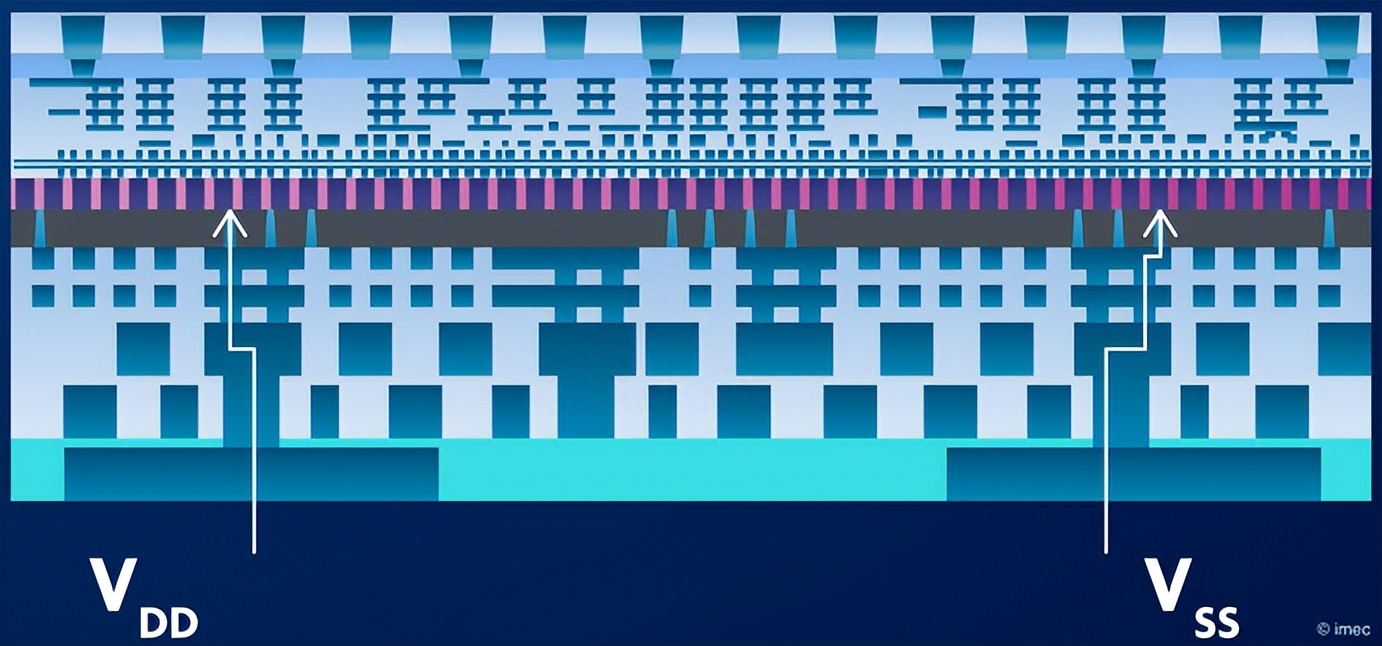

,整個配電網絡被移至晶圓的背面。硅通孔(TSV)將電源直接從背面傳送到正面,而無需電子穿過芯片正面上日益復雜的后道工序(BEOL)堆棧。 圖1. 背面供電網絡的示意圖,該網絡允許將電力傳輸與信號網絡解耦。 背面供電網絡(BSPDN)的目標是緩解

2023-09-05 16:39:38 464

464

背面電力傳輸打破了在硅晶圓正面處理信號和電力傳輸網絡的長期傳統。通過背面供電,整個配電網絡被移至晶圓的背面。硅通孔 (TSV) 將電源直接從背面傳送到正面,而無需電子穿過芯片正面日益復雜的后道工序 (BEOL) 堆棧。

2023-08-30 10:34:20 547

547

電子發燒友網站提供《SiC應用優勢及趨勢.pdf》資料免費下載

2023-08-29 16:24:51 1

1 濕法刻蝕由于精度較差,只適用于很粗糙的制程,但它還是有優點的,比如價格便宜,適合批量處理,酸槽里可以一次浸泡25張硅片,所以有些高校和實驗室,還在用濕法做器件,芯片廠里也會用濕法刻蝕來顯露表面缺陷(defect),腐蝕背面多晶硅。

2023-08-28 09:47:44 890

890

識別,從而顯著提高系統性能。碲鎘汞材料、量子阱材料和銻化物Ⅱ類超晶格材料均可用于制備雙色紅外探測器。其中,InAs/GaSb Ⅱ類超晶格材料因其帶隙靈活可調、電子有效質量更大、大面積均勻性高等特點以及成本優勢,成為制備雙色

2023-08-25 09:16:42 886

886

光刻蝕(Photolithography)是一種在微電子和光電子制造中常用的加工技術,用于制造微細結構和芯片元件。它的基本原理是利用光的化學和物理作用,通過光罩的設計和控制,將光影投射到光敏材料上,形成所需的圖案。

2023-08-24 15:57:42 2265

2265 前言新能源汽車依舊火熱,今年上半年國內銷量突破370萬輛,比亞迪、特斯拉、豐田、現代、吉利、上海大眾、日產等車企都已經在引入SIC器件。為何車企都采用SiC器件?SiC器件具備哪些優勢?碳化硅

2023-08-17 16:41:23 816

816

PVP可以在刻蝕過程中形成一層保護性的膜,降低刻蝕劑對所需刻蝕材料的腐蝕作用。它可以填充材料表面的裂縫、孔洞和微小空隙,并防止刻蝕劑侵入。這樣可以減少不需要的蝕刻或損傷,提高刻蝕的選擇性。

2023-08-17 15:39:39 2855

2855 在半導體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來講講如何采用這個“餅干模具”印出我們想要的“餅干”。這一步驟的重點,在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

2023-08-10 15:06:10 505

505 刻蝕(Etching)的目的是在材料表面上刻出所需的圖案和結構。刻蝕的原理是利用化學反應或物理過程,通過移除材料表面的原子或分子,使材料發生形貌變化。

2023-08-01 16:33:38 3904

3904 電子發燒友網報道(文/周凱揚)在半導體制造的各路工序中,尤其是前道工序中,技術難度最大的主要三大流程當屬光刻、刻蝕和薄膜沉積了。這三大工藝的先進程度直接決定了晶圓廠所能實現的最高工藝節點,所用產品

2023-07-30 03:24:48 1556

1556

刻蝕和蝕刻實質上是同一過程的不同稱呼,常常用來描述在材料表面上進行化學或物理腐蝕以去除或改變材料的特定部分的過程。在半導體制造中,這個過程常常用于雕刻芯片上的細微結構。

2023-07-28 15:16:59 4138

4138 最近有許多正在全球范圍內研究和開發的技術,例如晶體管GAA(Gate All around)、背面供電以及3D IC。

2023-07-26 18:21:58 1843

1843

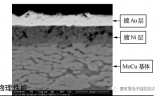

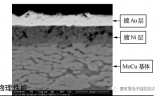

及能譜儀分析接頭的顯微組織、元素分布,通過X射線檢測儀測定接頭的孔洞率,研究GaAs芯片背面和MoCu基板表面的鍍層與焊料之間的相互作用以及焊縫的凝固過程。GaAs芯片背面的Au層部分溶解在AuSn焊料

2023-07-15 14:01:42 1276

1276

第一種是間歇式刻蝕方法(BOSCH),即多次交替循環刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 3213

3213

背面實施流程已通過成功的 SF2 測試芯片流片得到驗證。這是 2nm 設計的一項關鍵功能,但可能會受到三星、英特爾和臺積電缺乏布線的限制,而是在晶圓背面布線并使用過孔連接電源線。

2023-07-05 09:51:37 460

460 在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設計好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 843

843

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。其中,刻蝕工藝是光刻(Photo)工藝的下一步,用于去除光刻膠(Photo Resist

2023-06-26 09:20:10 816

816

英特爾表示,它是業內第一個在類似產品的測試芯片上實現背面供電的公司,實現了推動世界進入下一個計算時代所需的性能。PowerVia 將于 2024 年上半年在英特爾 20A 工藝節點上推出,正是英特爾業界領先的背面供電解決方案。它通過將電源路由移動到晶圓的背面,解決了面積縮放中日益嚴重的互連瓶頸問題。

2023-06-20 15:39:06 326

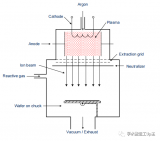

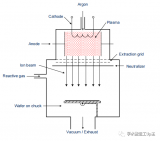

326 離子束蝕刻 (Ion beam etch) 是一種物理干法蝕刻工藝。由此,氬離子以約1至3keV的離子束輻射到表面上。由于離子的能量,它們會撞擊表面的材料。晶圓垂直或傾斜入離子束,蝕刻過程是絕對

2023-06-20 09:48:56 3989

3989

基于SiC器件的電力電子變流器研究

2023-06-20 09:36:23 410

410

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-06-15 17:51:57 1176

1176

時,,另一次是其它非盤中孔的電鍍。按照IPC-A-6012里面的規定,最小的過孔孔銅二級是18um,平均孔銅是20um,三級是最小20um,平均孔銅是25um。如果按照IPC二級標準,使用1/3OZ基銅

2023-06-14 16:33:40

光刻工藝后,在硅片或晶圓上形成了光刻膠的圖形,下一步就是刻蝕。

2023-06-08 10:52:35 3314

3314

英特爾率先在產品級芯片上實現背面供電技術,使單元利用率超過90%,同時也在其它維度展現了業界領先的性能。 英特爾宣布在業內率先在產品級測試芯片上實現背面供電(backside power

2023-06-06 16:22:00 314

314 外延層是在晶圓的基礎上,經過外延工藝生長出特定單晶薄膜,襯底晶圓和外延薄膜合稱外延片。其中在導電型碳化硅襯底上生長碳化硅外延層制得碳化硅同質外延片,可進一步制成肖特基二極管、MOSFET、 IGBT 等功率器件,其中應用最多的是4H-SiC 型襯底。

2023-05-31 09:27:09 2823

2823

經過前端工藝處理并通過晶圓測試的晶圓將從背面研磨(Back Grinding)開始后端處理。背面研磨是將晶圓背面磨薄的工序,其目的不僅是為了減少晶圓厚度,還在于聯結前端和后端工藝以解決前后兩個工藝

2023-05-22 12:44:23 691

691

經過前端工藝處理并通過晶圓測試的晶圓將從背面研磨(Back Grinding)開始后端處理。背面研磨是將晶圓背面磨薄的工序,其目的不僅是為了減少晶圓厚度,還在于聯結前端和后端工藝以解決前后兩個工藝

2023-05-12 12:39:18 759

759

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。

2023-04-28 11:24:27 1073

1073

主要講述 PCB Layout 中焊盤和過孔的設計標準及工藝要求,包括 BGA 焊盤。

一、 過孔的設置(適用于二層板,四層板和多層板)孔的設計

過線孔:制成板的最小孔徑定義取決于板厚度

2023-04-25 18:13:15

利。

工藝性設計要考慮:

a)自動化生產所需的傳送邊、定位孔、光學定位符號;

b)與生產效率有關的拼板;

c)與焊接合格率有關的元件封裝選型、基板材質選擇、組裝方式、元件布局、焊盤設計、阻焊

2023-04-25 16:52:12

本篇要講的金屬布線工藝,與前面提到的光刻、刻蝕、沉積等獨立的工藝不同。在半導體制程中,光刻、刻蝕等工藝,其實是為了金屬布線才進行的。在金屬布線過程中,會采用很多與之前的電子元器件層性質不同的配線材料(金屬)。

2023-04-25 10:38:49 986

986

技術中的個工藝環節。通孔回流焊大的好處就是可以在發揮表面貼裝制造工藝的優點的同時使用通孔插件來得到較好的機械連接強度。 通孔回流焊接工藝與波峰焊接工藝相比的優勢 1、通孔回流焊接工藝首先是減少

2023-04-21 14:48:44

等離子體均勻性和等離子體位置的控制在未來更加重要。對于成熟的技術節點,高的產量、低的成本是與現有生產系統競爭的關鍵因素。如果可以制造低成本的可靠的刻蝕系統,從長遠來看,可以為客戶節省大量費用,有可能

2023-04-21 09:20:22 1347

1347 壓力主要控制刻蝕均勻性和刻蝕輪廓,同時也能影響刻蝕速率和選擇性。改變壓力會改變電子和離子的平均自由程(MFP),進而影響等離子體和刻蝕速率的均勻性。

2023-04-17 10:36:43 1922

1922 的電氣參量;然后研究分析了功率器件結溫測量的各類方法, 并重點闡述了溫敏電參數 (TSEP) 法在 SiC MOSFET 結溫評估領域的應用前景, 從線性度、 靈敏度等 6 個方面對比分析了 各方

2023-04-15 10:03:06 1452

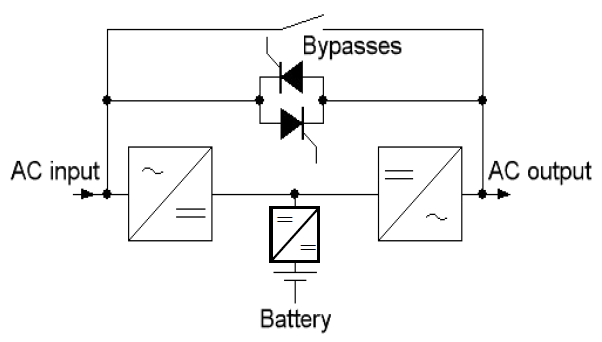

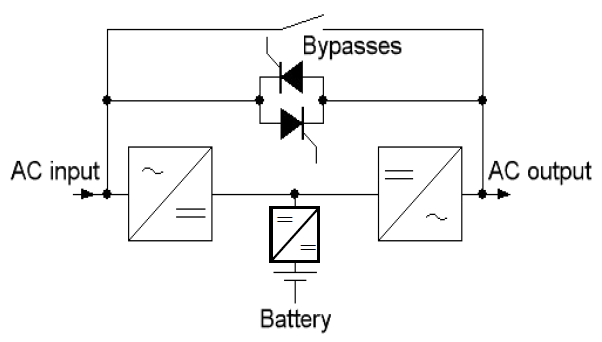

1452 我們聊了關于UPS的概念和分類,以及在線式UPS的三個工作模式。第三代寬禁帶半導體WBG的誕生和發展,讓很多使用Si基半導體器件的行業得到提升,今天我們就簡單地聊聊SiC在UPS中的應用優勢。

2023-04-14 14:35:10 788

788

金屬刻蝕具有良好的輪廓控制、殘余物控制,防止金屬腐蝕很重要。金屬刻蝕時鋁中如果 有少量銅就會引起殘余物問題,因為Cu Cl2的揮發性極低且會停留在晶圓表面。

2023-04-10 09:40:54 2330

2330 DRAM柵工藝中,在多晶硅上使用鈣金屬硅化物以減少局部連線的電阻。這種金屬硅化物和多晶硅的堆疊薄膜刻蝕需要增加一道工藝刻蝕W或WSi2,一般先使用氟元素刻蝕鈞金屬硅化合物層,然后再使用氯元素刻蝕多晶硅。

2023-04-07 09:48:16 2198

2198 SIC438BEVB-B

2023-04-06 23:31:02

PCB生產商的通孔插裝工藝模板的印刷方法有幾種?

2023-04-06 16:12:14

的藍牙模組/NBlot模組,這些不可或缺的通信模組可以像芯片一樣焊接到PCB板上。這些小載板特點為:尺寸較小、單元邊有整排金屬化半孔,通過這些金屬化半孔與母板以及元器件的引腳焊接到一起,行業內對于這種

2023-03-31 15:03:16

介紹了SIC碳化硅材料的特性,包括材料結構,晶體制備,晶體生長,器件制造工藝細節等等。。。歡迎大家一起學習

2023-03-31 15:01:48 17

17 陜西光電子先導院先進光子器件工程創新平臺3月30日在西安全面啟用。該平臺具備光子芯片制程中的光刻、刻蝕、蒸鍍等多項核心工藝,將為光子產業項目提供產品研發、中試、檢測等全流程技術服務,為光子產業各類

2023-03-30 19:09:10 410

410

FinFET三維器件也可以用體硅襯底制作,這需要更好地控制單晶硅刻蝕工藝,如CD、深度和輪廓。

2023-03-30 09:39:18 2458

2458 V SiC MOSFET“S4101”和650V SiC SBD“S6203”是以裸芯片的形式提供的,采用ROHM的這些產品將有助于應用的小型化并提高模塊的性能和可靠性。另外

2023-03-29 15:06:13

,大概是12um(基銅)+20um(盤中孔孔銅)+20um(非盤中孔孔銅),總的銅厚度在52um左右。從上面POFV的工藝流程中,我們可以看出第5工序有減銅的流程,但是通常銅厚不能減太多,大概在

2023-03-27 14:33:01

作為半導體制造的后工序,封裝工藝包含背面研磨(Back Grinding)、劃片(Dicing)、芯片鍵合(Die Bonding)、引線鍵合(Wire Bonding)及成型(Molding)等步驟。

2023-03-27 09:33:37 7222

7222

電子發燒友App

電子發燒友App

評論