: EVAL_PASCO2_SENSOR 供應商給出的確切值 -> 我相信我無法更改

數據通道:攝像機有 4 個數據通道連接到其序列化器。 我匹配的 Deserializer 子 COOLDIM_PRG_BOARD

2024-02-26 08:41:06

眾所周知,序列發送模塊可以不需要腳本代碼實現測試中特定控制報文序列的發送,該模塊多用于循環順序控制的測試案例中。序列發送模塊的常用場景,主要是針對一些新開發的產品需要通過該模塊來驗證產品功能等等

2024-02-19 14:00:11 111

111

脈沖信號和單位采樣序列有何區別? 脈沖信號和單位采樣序列是數字信號處理中兩個重要的概念。在本文中,我們將詳細介紹這兩個概念的定義、特點以及它們之間的區別。 一、脈沖信號的定義和特點 脈沖信號是一種

2024-02-06 09:25:24 277

277 Aurix系列單片機時鐘系統有哪些特點

2024-02-04 06:48:15

ADAS3022設置為基本序列器模式,CFG設置為0xE0FF,最后數據讀出一直為IN6/IN7的電壓值,沒有其它通道的值,序列器沒有啟動,連續讀數,在IN6/IN7的數值后為CFG的設置值0x60FF,由讀出的CFG的值可以確認CFG已經設置成功,但是不知道為什么序列器沒有啟動,請大家幫忙解決一下

2023-12-18 06:07:15

我理解這個D觸發正常運轉要滿足四個約束,第一個是建立時間,第二個是保持時間,第三個是對于最后一個傳輸門的關斷時間的控制,第四個是[時鐘周期]() 約束。

2023-12-04 15:44:02 352

352

的答案:

(1)總的建立時間就等于兩級運放的建立時間之和,即90 ns + 90 ns =180 ns

(2)總的建立時間還是90 ns

(3)認為兩級運放相互獨立,總的建立時間等于兩級運放建立時

2023-11-27 06:54:56

在為ad7610選擇一個單電源的驅動放大器,手冊中推薦的ad8021是雙電源,建立時間參數為:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2023-11-17 06:22:37

Evilparcel漏洞可以導致Bundle在多次序列化和反序列化過程中內容發生改變。結合LAW跳板,可以實現權限提升,嚴重影響系統安全

2023-11-16 14:43:35 132

132

各位前輩好,

最近碰到一個棘手問題,研究了好幾天了,一直沒有搞好:

一個變頻器同時帶動3個熱繼電器,每個熱繼電器下方都有一個電機。電機、熱繼電器的型號都一樣。其中一個提升電機用的熱繼電器,運行時

2023-11-13 07:54:34

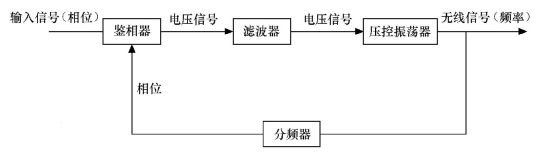

程序開發中,序列化是經常需要用到的。像一些相對高級語言,比如JAVA, C#都已經很好的支持了序列化,那么C++呢?當然一個比較好的選擇就是用Boost,這個號稱C++準標準庫的東西。 什么時候需要

2023-11-10 10:14:30 180

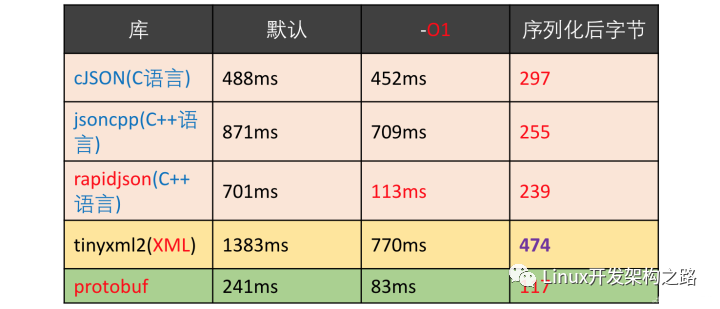

180 一、protobuf簡介: 1.1 protobuf的定義: protobuf是用來干嘛的? protobuf是一種用于 對結構數據進行序列化的工具,從而實現 數據存儲和交換。 (主要用于網絡通信

2023-11-09 09:27:42 378

378

m序列簡介

m序列是一種常用的偽隨機序列,由具有反饋函數的移位寄存器電路產生,具有周期性,一旦反饋表達式及移位寄存器的初值(又稱為種子)給定,就可以重復實現某組確定的序列值。該特點使得m序列在數

2023-11-06 17:03:26

晶振在電路中起到提供穩定的時鐘信號的作用。時鐘信號是電子設備中非常重要的信號之一,它用于同步各個電路模塊的工作,確保它們按照正確的時間序列進行操作。

2023-11-01 18:14:41 378

378 Pydantic 是一個使用Python類型注解進行數據驗證和管理的模塊。安裝方法非常簡單,打開終端輸入: pip install pydantic 它類似于 Django DRF 序列化器的數據

2023-10-30 11:40:04 259

259 如何用VHDL設計同步序列發生器與檢測器

2023-10-18 08:07:04

STM32的獨立看門狗用的時鐘是內部時鐘還是外部時鐘呢

2023-10-15 11:58:05

STM8的獨立看門狗可以直接用內部低速時鐘嗎

2023-10-11 06:04:40

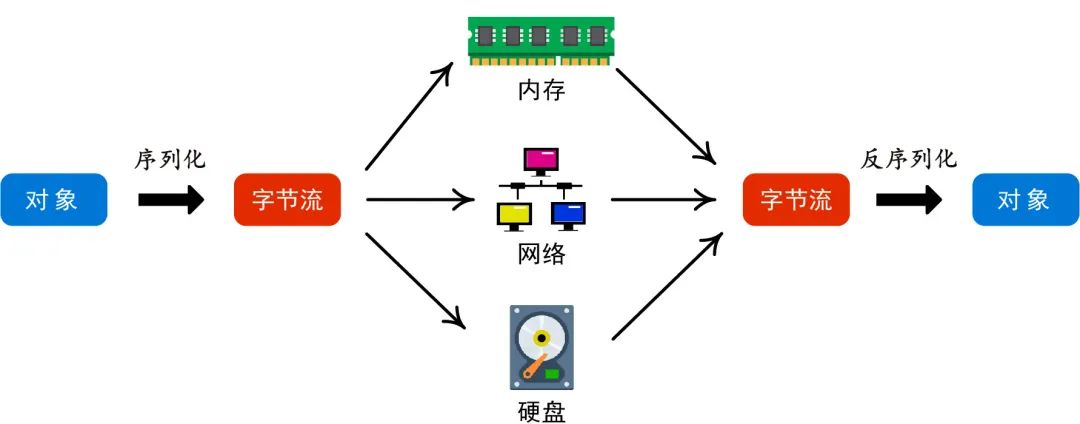

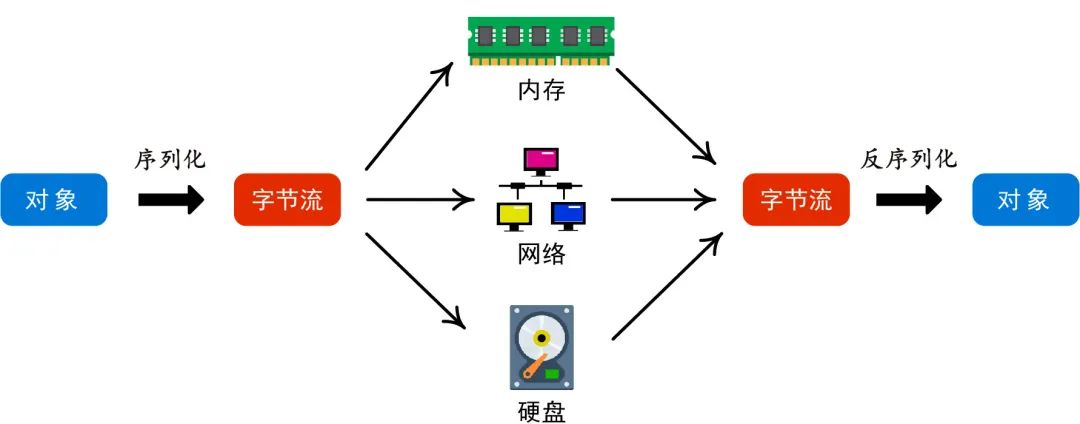

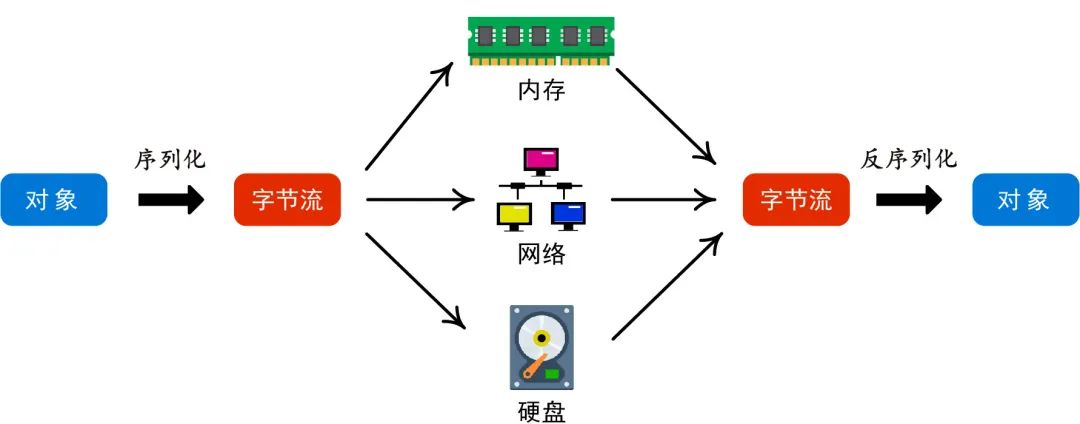

轉換方式就叫做序列化。將文件或者網絡傳輸中得到的 byte[] 數組轉換為 java 對象就叫做反序列化。 怎么使用 如果一個 Java 對象要能被序列化,必須實現一個特殊

2023-10-10 14:19:25 217

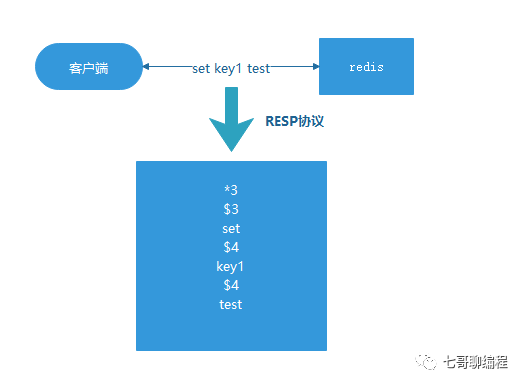

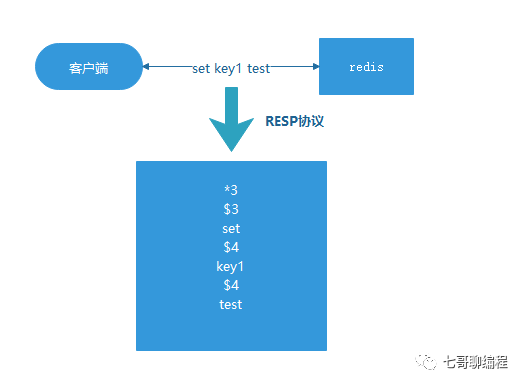

217 原理 在學習AOF原理前,我們首先要了解 RESP (Redis的序列化協議) 從圖中可以看到客戶端在調用redis服務端時,傳入的命令和 key、value 都會通過 RESP 協議序列化為文本

2023-10-09 15:02:38 169

169

在Spring Boot Web 項目中,當使用JSON格式接收數據和返回數據的時候,Spring Boot 默認使用一個ObjectMapper實例來序列化響應和反序列化請求。 在本文中,我們

2023-10-09 10:26:57 1136

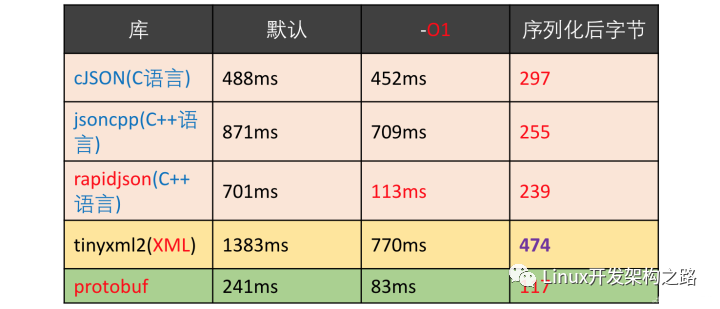

1136 json是目前最為流行的文本數據傳輸格式,特別是在網絡通信上廣泛應用,隨著物聯網的興起,在嵌入式設備上,也需要開始使用json進行數據傳輸,那么,如何快速簡潔地用C語言進行json的序列化和反序列化

2023-10-07 11:05:34 738

738 在順序功能圖中除了前面使用過的單序列和循環序列外,還有并行序列、選擇序列、跳轉序列和混合序列,本期主要介紹并行序列和選擇序列。

2023-10-01 10:53:00 917

917

Serde 是一個用于序列化和反序列化 Rust 數據結構的庫。它支持 JSON、BSON、YAML 等多種格式,并且可以自定義序列化和反序列化方式。Serde 的特點是代碼簡潔、易于使用、性能高效

2023-09-30 17:09:00 730

730 。Worker子線程和宿主線程之間的通信是基于消息傳遞的,Worker通過序列化機制與宿主線程之間相互通信,完成命令及數據交互。

5.TaskPool注意事項

● 實現任務的函數需要使用裝飾器

2023-09-25 15:23:54

buffers. 它是由 Google 研發的,一種可跨語言、可跨平臺、可擴展的序列化數據的機制。類似于 XML ,但是它更小、更快、更簡單。你只需要定義一次你希望的數據如何被結構化,然后你可以使用它的生成工具,生成包含一些序列化和反序列化等操作的源代碼。可以輕松地從各種數據流和使用各種編

2023-09-25 11:26:22 239

239 Prost是一個用于序列化和反序列化協議緩沖區數據的Rust語言庫。它使用Google Protocol Buffers語言來定義協議,并生成Rust代碼以便使用該協議。 Prost具有高性能的特點

2023-09-20 11:09:16 661

661 景,幫助您更好地了解這些材料的熱縮性能。 熱縮測試儀的工作原理是基于材料的熱脹冷縮特性。當材料受熱時,其分子鏈會運動并產生膨脹,導致尺寸增大。當材料冷卻時,

2023-09-18 11:17:54

、PCB設計、到PCB制造、BOM配單、電子裝聯(PCBA)和測試驗證等多個環節,不同的環節的特點和需求不同,對電子供應鏈企業有不同的要求。整體來說,電子供應鏈呈上游集中、下游分散、品類繁雜之態勢。

機會

2023-09-15 11:37:37

很多應用場合需要檢測系統時鐘是否在正常范圍內,以保證MCU能正常工作,CLASS B功能安全實現系統時鐘自檢的方法是采用兩個獨立時鐘源交叉檢查來進行測量

2023-09-14 17:30:49 945

945

理解了序列化,再回到ROS。我們發現,ROS沒有采用第三方的序列化工具,而是選擇自己實現,代碼在roscpp_core項目下的roscpp_serialization中,見下圖。這個功能涉及的代碼

2023-09-14 17:26:28 557

557 什么是序列化? “序列化”(Serialization )的意思是將一個對象轉化為字節流。 這里說的對象可以理解為“面向對象”里的那個對象,具體的就是存儲在內存中的對象數據。 與之相反的過程是“反序列化

2023-09-14 17:22:29 1239

1239

電子發燒友網站提供《基于反序列化過采樣數據的時鐘和數據恢復單元.pdf》資料免費下載

2023-09-13 10:41:34 0

0 可通過option byte來選擇是否使能硬件IWDG功能 更先進的安全功能 IWDG使用獨立的低速時鐘LSI作為時鐘源并在主時鐘無效時仍然保持運行 一旦使能了IWDG該功能就不能被禁止(LSI也

2023-09-13 07:46:59

耗電與頻率成正比最低為1.5μA。如果有32.768kHz的振蕩器連接到LSE精度可達0.5% 復位和從停止/待機模式退出后MSI將作為默認的系統時鐘其建立時間的最大值為2us。 低速內部振蕩器

2023-09-12 08:25:02

信號經過傳輸線到達接收端之后,就牽涉到建立時間和保持時間這兩個時序參數,它們表征了時鐘邊沿觸發前后數據需要在鎖存器的輸入持續時間,是接收器本身的特性。簡而言之,時鐘邊沿觸發前,要求數據必須存在一段時間,這就是器件需要的建立時間;

2023-09-04 15:16:19 391

391

業界高端FPGA的卓越性能和高口碑聲譽都有哪些因素了?其中很重要的一個因素就是FPGA內部豐富的時鐘資源使得FPGA在處理復雜時鐘結構和時序要求的設計中具有很大優勢。設計師可以更好地控制和管理時鐘信號,提高時序性能、減少時鐘相關問題,并滿足設計的高性能和穩定性要求。

2023-08-31 10:44:01 530

530 點擊上方 藍字 關注我們 一、前言 在數字電路中,序列檢測器(Sequence Detector)是指一種特殊類型的電路,用于尋找輸入信號中一定模式的子序列。該模式可以是任意模式,包括重復模式、連續

2023-08-29 10:20:02 514

514

Fury 是一個基于 JIT 動態編譯和零拷貝的多語言序列化框架,支持 Java/Python/Golang/JavaScript/C++ 等語言,提供全自動的對象多語言 / 跨語言序列化能力,和相比 JDK 最高 170 倍的性能。

2023-08-25 17:05:00 701

701

打印機的工作原理是打印頭上安裝有半導體加熱組件,熱打印機有選擇地在熱敏紙的確定位置上加熱,由此就產生了相應的圖形。加熱是由與熱敏材料相接觸的打印頭上的一個小電子加熱器提供的。加熱器排成方點或條的形式由

2023-08-25 08:02:25

,在很多應用場景中都可以用來構建序列發生器。本文將介紹使用D觸發器設計序列發生器的方法和步驟。 首先,我們需要了解D觸發器的基本原理和性質。D觸發器是一種時序電路,它可以存儲和延遲一個輸入信號,并在時鐘信號到來時輸出

2023-08-24 15:50:17 2729

2729 建立時間和保持時間是SOC設計中的兩個重要概念。它們都與時序分析有關,是確保芯片正常工作的關鍵因素。

2023-08-23 09:44:55 388

388 那個有M0518系統時鐘寄存器版本的初始化程序,庫函數的太大了,

系統時鐘實現的功能是使用外部晶振而不是內部

2023-08-22 07:00:34

50 MHz或100 MHz輸入時鐘

8K或64K字糾錯碼(ECC)RAM,具有內置自檢(BIST)功能

所有終端的獨立時間標簽計數器,監視器終端有48位選項

簡單監控終端(SMT)分別記錄命令和數

2023-08-17 17:45:41

的配置篡改。

主要特性:

自由運行的12位向下計數器

如果看門狗定時器被使能,那么當向下計數器的值達到0時產生系統復位;

獨立時鐘源,獨立看門狗定時器在主時鐘故障時仍能工作;

獨立看門狗

2023-08-16 08:13:59

新的體系結構功能:

·可擴展的矢量長度。

·每個車道的預測。

·集中加載和分散存儲。

·容錯推測性向量化。

·水平和序列化向量運算。

此版本的ARM編譯器工具鏈允許您:

·匯編包含SVE指令的源代碼

2023-08-16 06:51:27

時鐘電路是一種用于產生穩定、可靠的時間基準信號的電路。它在電子系統中起著非常重要的作用,用于同步和定時系統的各種操作。時鐘信號主要用于控制數據傳輸、指令執行、操作序列和各種時序事件。

2023-08-14 16:02:58 2004

2004 今天有個小伙伴遇到一個問題,就是在vivado里面綜合后看到的建立時間和保持時間裕量都是inf,我們來看看怎么解決這個問題。

2023-07-30 10:26:02 648

648

QSpan II User 手冊

2023-07-14 09:42:44 0

0 初版的代碼在序列化時沒有考慮到MCU小容量內存設備,需要一次性完成序列化,內存開銷較大等等其他問題。

2023-07-03 09:25:40 175

175 在時序電路設計中,建立時間/保持時間可以說是出現頻率最高的幾個詞之一了,人們對其定義已經耳熟能詳,對涉及其的計算(比如檢查時序是否正確,計算最大頻率等)網上也有很多。

2023-06-27 15:43:55 4582

4582

如果大家看過或者實現過序列化反序列化的代碼,這個問題就不難回答了,今天碰到的這個問題其實是發生在大家可能最常用的`fastjson`庫里的,所以如果大家在使用這個庫,請務必檢查下你的代碼,以免踩到此坑

2023-06-27 15:22:32 305

305 NUC100、NUC200、Nano100與NUC442/NUC472系列芯片支持的實時時鐘控制器,其他系列芯片則無。

多數NuMicro? 家族芯片的實時時鐘控制器是不需要獨立的電源,而是與芯片

2023-06-27 06:08:18

??本文主要介紹了建立時間和保持時間。

2023-06-21 14:38:26 1079

1079

建立時間(setup time)和保持時間(hold time)是時序分析中最重要的概念之一,深入理解建立時間和保持時間是進行時序分析的基礎。

2023-06-21 10:44:01 881

881

運算放大器建立時間是保證數據采集系統性能的關鍵參數。為了實現精確的數據采集,運算放大器輸出必須在A/D轉換器能夠準確數字化數據之前建立。然而,建立時間通常不是一個容易測量的參數。

2023-06-17 10:37:54 366

366

NUC100、NUC200、Nano100與NUC442/NUC472系列芯片支持的實時時鐘控制器,其他系列芯片則無。

多數NuMicro? 家族芯片的實時時鐘控制器是不需要獨立的電源,而是與芯片

2023-06-15 12:41:05

上述類型的內存馬在tomcat7(支持Servlet API 3.0)以后可以通過動態注冊方式向中間件注入,也因其可以動態注冊的特點所以可以在反序列化等可任意執行代碼的漏洞點進行利用。

2023-06-05 17:29:35 534

534

有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口。雖然這樣可以簡化時序分析以及

2023-06-02 14:26:23

首先,我們需要理解什么是時鐘抖動。簡而言之,時鐘抖動(Jitter)反映的是時鐘源在時鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

參考時鐘獨立,參考時鐘不需要穿越背板和連接器,從而使PCB設計變得更為簡單,使得架構更加的靈活。

2023-05-29 12:49:49 5089

5089

眾所周知,序列由幾個數據項組成,它們共同構成了一個有趣的場景。序列可以是分層的,從而創建更復雜的方案。在最簡單的形式中,序列應該是 uvm_sequence 基類的派生,方法是指定請求和響應項類型參數,并使用要執行的特定方案實現 body 任務。

2023-05-29 09:50:40 376

376 測試將使用此序列器來處理序列(如上一篇博客文章中所述)。在這里,我們可能不需要虛擬序列(或虛擬序列器)。

2023-05-29 09:46:18 444

444 本文介紹ROS機器人操作系統(Robot Operating System)的實現原理,從最底層分析ROS代碼是如何實現的。

**1、序列化**

把通信的內容(也就是消息message)序列化是通信的基礎,所以我們先研究序列化。

2023-05-19 17:42:01 803

803 本文介紹ROS機器人操作系統(Robot Operating System)的實現原理,從最底層分析ROS代碼是如何實現的。

**1、序列化**

把通信的內容(也就是消息message)序列化是通信的基礎,所以我們先研究序列化。

2023-05-19 17:41:47 730

730

基站的內部,都有自己獨立的時鐘模塊:晶振(晶體振蕩器),在沒有外部時鐘源時,就處于自由震蕩狀態。

可想而知,在自由震蕩狀態的各個基站間的時鐘沒有同步,每個基站都只是一個孤島,只能獨立運行無法協同

2023-05-10 17:09:50

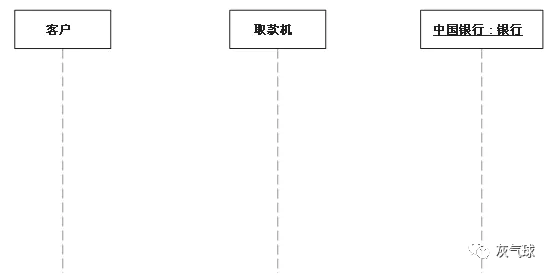

序列圖將交互關系表示為一個二維圖。縱向是時間軸,時間沿豎線向下延伸。橫向軸代表了在協作中各獨立對象的類元角色。類元角色用生命線表示。當對象存在時,角色用一條虛線表示,當對象的過程處于激活狀態時,生命線是一個雙道

2023-05-05 10:28:01 355

355

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用戶手冊

2023-04-27 20:25:40 6

6 ,給企業的利潤帶來了較大的壓力。為應對上述問題,企業不斷加強自身管理能力。

工程項目管理具備計劃性、臨時性、系統性、復雜性以及約束性的特點。項目物資的供應鏈管理貫穿工程項目始終,從項目計劃伊始直至最終

2023-04-25 11:28:10

PowerSpan II User 手冊

2023-04-20 18:51:26 0

0 我讀到 SMP 特性:“對稱內存(有一些小例外)。如果多個內核訪問相同的內存地址,它們的訪問將在內存總線級別序列化。通過原子比較實現對相同內存地址的真正原子訪問-ISA 提供的交換指令。”那么這是否意味著我可以創建全局變量而不用擔心多線程訪問?

2023-04-14 08:40:57

、傳感器等。 總之,配電自動化系統是一種綜合的技術體系,其實現離不開監測、保護、控制、智能化集成和各種配電設備的有機組合。 配電自動化系統的特點 配電自動化系統是一種利用新興科技獨立開發并應用于

2023-04-10 17:04:59

最終啟動序列錯誤,芯片初始化失敗 Ef(34) 初始化閃存超時這些是我被卡住的錯誤,任何人都可以建議我解決請盡快回復我

2023-04-10 08:29:06

序列化對象:將對象轉換為可以存儲或傳輸的形式。

(1) 用于存儲:將對象的字節序列存儲到文件中,程序退出后不會消失,便于后續使用。

(2) 用于傳輸:發送方把對象轉換為字節序列,接收方字節序列恢復為對象。

2023-04-06 15:08:44 465

465 會退出總線繁忙狀態和失敗。 出于好奇,我嘗試將時鐘頻率配置為 400MHz 并使用分頻器 2 來獲得 200M 的值。 我想知道 RFDR 中的這個值表示什么以及誰負責更新? 如果我使用分頻器值 3,則操作成功,RFDR[0] 值為 0x80,依此類推各種循環序列的變化。

2023-04-03 09:01:11

QSpan II User 手冊

2023-03-31 19:31:54 0

0 幾乎稍微復雜的數字設計都離不開時鐘。時鐘也是所有時序邏輯建立的基礎。前面介紹建立時間和保持時間時也涉及過時鐘偏移的概念。下面將總結下時鐘的相關知識,以便更好的進行數字設計。

2023-03-28 13:56:41 978

978

“序列號為“AH06IOXS”的 TED-Kit 2 初始化失敗。此 TED-Kit 2box 無法使用且未顯示在硬件視圖中。”

2023-03-24 06:24:00

分辨率嗎?最大值是多少?我們的案例支持的決議?其中一個顯示器將靠近電路板,另一個將相距幾米。所以我們打算使用TI的序列化程序。您建議使用哪一種 i2c(用于觸摸屏功能)?或者您對我們的案例有任何其他解決方案嗎?

2023-03-23 07:22:41

電子發燒友App

電子發燒友App

評論