DDR應用的一般注意要點

上周的文章我們介紹了應用 DDR 時需要先從電源、時鐘兩個方面必須遵循的固定法則,以保證存儲的正常使用。本次文章,我們主要圍繞DDR的PCB設計保證DDR的正常使用來展開描述。首先從DDR的相對擺放位置做介紹,即根據使用的DDR個數和類型以及實際布板格局做拓撲選擇。拓撲結構的選擇主要還是看其芯片的時序要求。目前常見的有以下幾種拓撲:一對一拓撲、菊花鏈拓撲(改進類型為Fly-by拓撲結構)、星型拓撲(部分改動后也叫T型拓撲)。

我們首先來一個一個看看這些拓撲的應用特點。一對一拓撲是比較簡單的Driver to Rceiver,結構簡單,整個網絡的阻抗特性容易控制,時序關系也容易控制,常見于高速雙向傳輸信號線,常在源端加串行匹配電阻來防止源端的二次反射。接下來所有的拓撲都是一對多的拓撲結構,需要分門別類進行介紹。

星型拓撲

星型拓撲是多負載時常用的拓撲結構,驅動器位于星形的中央,呈輻射狀與多個負載相連,星型拓撲可以有效避免信號在多個負載上的不同步問題,可以讓負載上收到的信號完全同步。

但這種拓撲的問題在于需要對每個支路分別端接,使用器件多,而且驅動器的負載大,必須驅動器有相應的驅動能力才能使用星形拓撲,如果驅動能力不夠,需要加緩沖器。 相對來說,星型拓撲只能用在相對低速信號上,而且是在各接收芯片需要同步接收的情況,只有在非常嚴格的時序要求下會采用星形拓撲,其中重要的原因是布局布線實現起來比較困難。

T型拓撲

T型拓撲結構是樹型拓撲,又叫對稱型的遠端簇型拓撲結構、等臂分支拓撲。實際上是星型拓撲的一個改進,它將星型拓撲中位于Driver端的分支節點移動到與Receivers最近的遠端,既滿足了各個接收器上接收信號的同步問題,又解決了阻抗匹配復雜和驅動器負載重的問題,因為遠端簇形拓撲只需要在分支節點處終端匹配就可以了。

遠端簇型拓撲要求各個接收器到分支點的距離要盡量近,分支線長了會嚴重影響信號的質量,如果各個接收器芯片在空間上不能擺放在一起,那么就不能采用遠端簇型拓撲即T型拓撲。

T型拓撲結構各個分支的端接負載和走線長度要盡量保持一直,如此才能更好的保證每個分支的接收端負載接收到的信號盡量同步,并且,每個分支電路中都需要有端接電阻,通過端接電阻與走線的特性阻抗更好的匹配來減小信號反射干擾的問題;T型拓撲結構可以讓時鐘、地址、控制等信號得到更好的同步效果。

布線布局時,T型拓撲結構要求從驅動端Driver到交叉T點的PCB布線長度要遠遠大于交叉T點到各個接收端Receiver的PCB布線長度,同時交叉T點到各個接收端Receiver的距離要盡量等長,信號匹配設計可以做在交叉T點處。如果是一拖二的,可以把兩片芯片貼在PCB的正反兩面,對貼減小分叉的長度。

菊花鏈拓撲

菊花鏈是把所有的負載串起來,沒有等長要求,菊花鏈一般適用較低速的信號,它比星型在布局布線上更容易實現,所以是最常見的一種拓撲結構。

但隨著芯片制造技術的更替,就是低速驅動器的上升沿也隨著變陡,這使得低速不低頻,更多的高頻分量使反射也變成低速信號要考慮的問題了,尤其是多負載菊花鏈的多重反射,所以菊花鏈的信號完整性問題比星形拓撲負載復雜多了。菊花鏈最差波型總是出現在第一個接收器,因為后面每個阻抗不連續點的反射都會影響這里。

fly-by拓撲

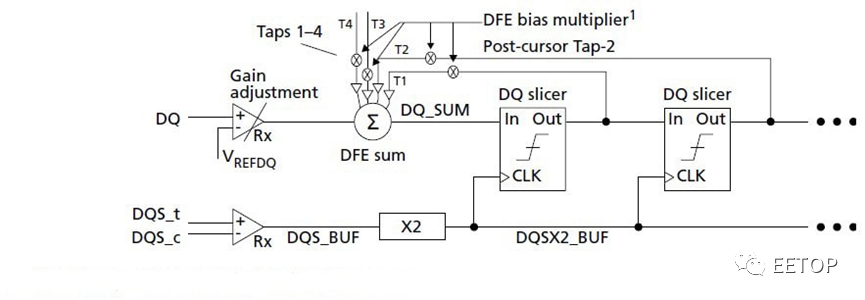

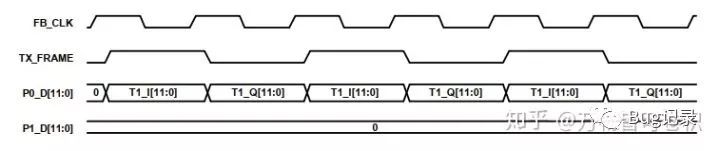

相比T拓撲,fly-by拓撲在傳輸較高速率信號時更占優勢一些,但是使用fly-by拓撲,負載之間有延時差,導致信號不能同時到達接收端。為解決這個問題,DDR3引入了read and write leveling。也就是,只有在主控芯片有讀寫平衡功能,也就是有Write Leveling,Read Leveling功能,才能采用這個拓撲結構。

此外,fly-by由于分支結構的存在,通道本身就存在一些缺點。例如:通道阻抗不連續;容性突變對時序的影響等等。信號通道中只要有分叉就會存在阻抗的不連續,fly-by結構處處是分叉,阻抗不連續問題就很突出。至于為什么要在最后一級增加端接電阻,是因為從Driver到最后一顆DDR的電流是這一串所有DDR當中最大的;根據△I=△Q/△T的原理,電流加大了, △T減小了,故在一定程度上補償了因線長導致的延時問題。

以上就是本次介紹的所有拓撲結構。那么,根據所使用的DDR,如何選擇拓撲呢?

我們先看一個結論:(1)當信號速率比較高時,使用T型拓撲結構信號明顯比使用FLY-BY拓撲結構的信號質量差。(2)當顆粒較多時,不論是采用T型拓撲結構還是FLY-BY的拓撲結構,容性負載補償對信號有明顯的改善。又根據DDR、DDR1、DDR2、DDR3、DDR4的特性以及對應的Driver的特點、板層的規劃,有以下結論:

一般而言,DDR1/2采用星型結構,DDR3采用菊花鏈結構【不是所有的DDR3都可以用Fly by結構,如果主控芯片不支持讀寫平衡(Read and WriteLeveling)功能,則不能使用Fly by拓撲結構】。Fly by結構的DQS和CK不等長,沒有write leveling就沒法調整DQS和CK之間的偏斜。拓撲結構只影響地址線的走線方式,不影響數據線。星型拓撲就是地址線走到兩片DDR中間再向兩片DDR分別走線,菊花鏈就是用地址線把兩片DDR“串起來”。

DDR2是采用T形拓撲結構,是因為時序要求信號要同時到達。那DDR3采用的Fly by結構,其實就是stub較短的菊花鏈,之所以采用此種結構是因為DDR3多了讀寫平衡的新技能,即使你們不同時到達,也能把它調過來。所以采用何種拓撲結構首先要看時序要求。選定了拓撲結構,在布局時元器件的擺放,有以下幾個原則需要遵守:

一,考慮拓撲結構,查看Driver地址線的位置,使得地址線有利于相應的拓撲結構;

二,地址線上的匹配電阻靠近Driver(發送端);

三,數據線上的匹配電阻靠近DDR;

四,將DDR芯片擺放并旋轉,使得DDR數據線盡量短,DDR芯片的數據引腳靠近Driver;

五,如果有VTT端接電阻,將其擺放在地址線可以走到的最遠的位置。一般來說,DDR2不需要VTT端接電阻,只有少數Driver需要;DDR3都需要VTT端接電阻。

六,DDR芯片的去耦電容放在靠近DDR芯片相應的引腳。

然后是處理端接問題,DDR常用的端接技術有兩種,分別如下:

串行端接,主要應用在負載DDR顆粒不大于4個的情況下。對于雙向I/O信號來說,例如DQ,串行端接電阻Rs放置在走線的中間,用來抑制振鈴,過沖和下沖。對于單向的信號來說,例如地址線,控制線,串行端接電阻放置在走線中間或者是信號的發送端,推薦放置在信號的發送端。

并行端接,主要應用在負載SDRAM器件大于4個,走線長度》2inch,或者通過仿真驗證需要并行端接的情況下。并行端接電阻Rt取值大約為2Rs,Rs的取值范圍是10~33ohm,故Rt的取值范圍為22~66ohm。并行端接電壓為VTT。

對于沒有ODT功能的DDR,所有的數據線,地址,命令,控制線都需要使用single-ended Parallel Termination端接。

?

以上就是應用DDR時布局和端接的一些介紹總結。除了技術人員的處理之外,選擇合適的或者有過批量生產的DDR型號也不錯。在工業級應用當中, Alliance 公司的 DRAM 產品具有工業級的品質,抗干擾性強,則需要很強的穩定性,具有從16M、64M、128M、256M、512M到1G的完整的DRAM生產線。這些存儲器被使用于主流的數字信號處理器(DSP)和微控制器,主要發現在數字消費電子、網絡、移動通信、工業、醫療和汽車電子市場。

fqj

電子發燒友App

電子發燒友App

評論