Bypass電容的大小和計算方法 Bypass電容是一種常見的電子元件,用于繞過或降低電路中的噪聲、干擾或漏磁磁通。它能夠有效地將高頻噪聲或漏磁磁通通過一個低阻抗路徑繞過,從而保持電路的穩定性和信號

2024-02-14 17:56:00 2974

2974 有人說用這個公式U=4.44f*kN*phi,其中U是相電壓額定值,f是額定頻率,kN是定子繞組每相有效匝數,phi就是磁鏈。這里的問題是定子繞組每相有效匝數我不知道呀,是不是有個大概的范圍呢?向各位請教了。

另外,還有沒有其他的方法來計算磁鏈給定值呢?

2024-01-10 07:38:54

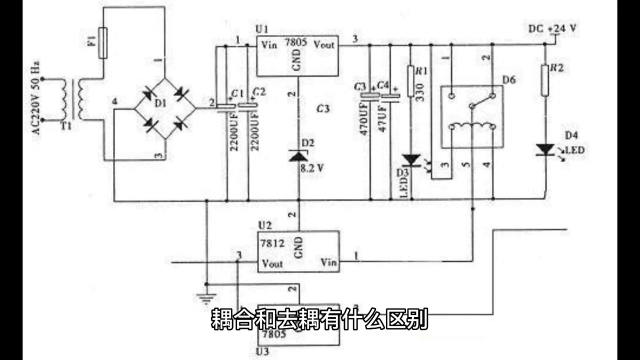

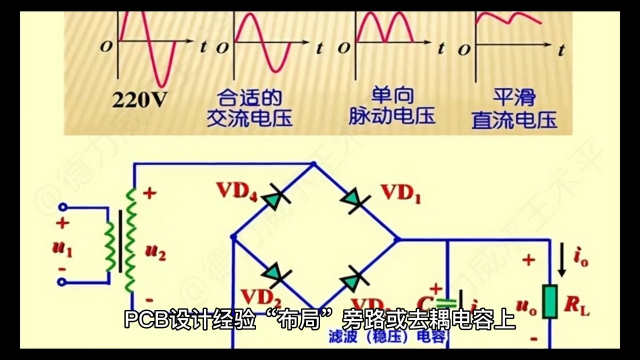

我們在電源濾波電路上可以看到各種各樣的電容,100uF,10uF,100nF,10nF不同的容值,那么這些參數是如何確定的?

數字電路要運行穩定可靠,電源一定要”干凈“,并且能量補充一定要及時

2024-01-09 08:25:59

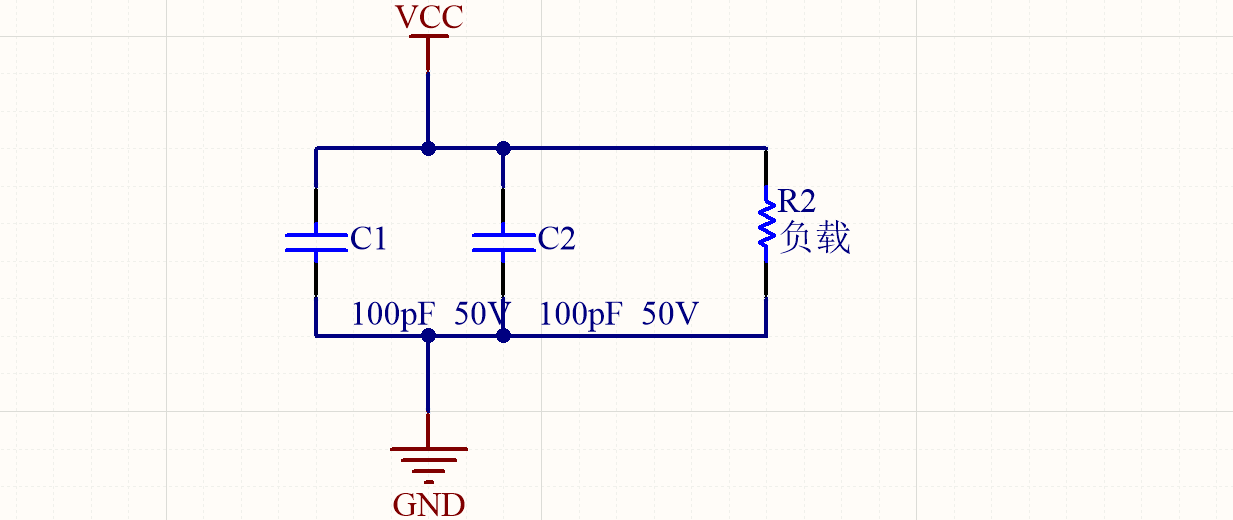

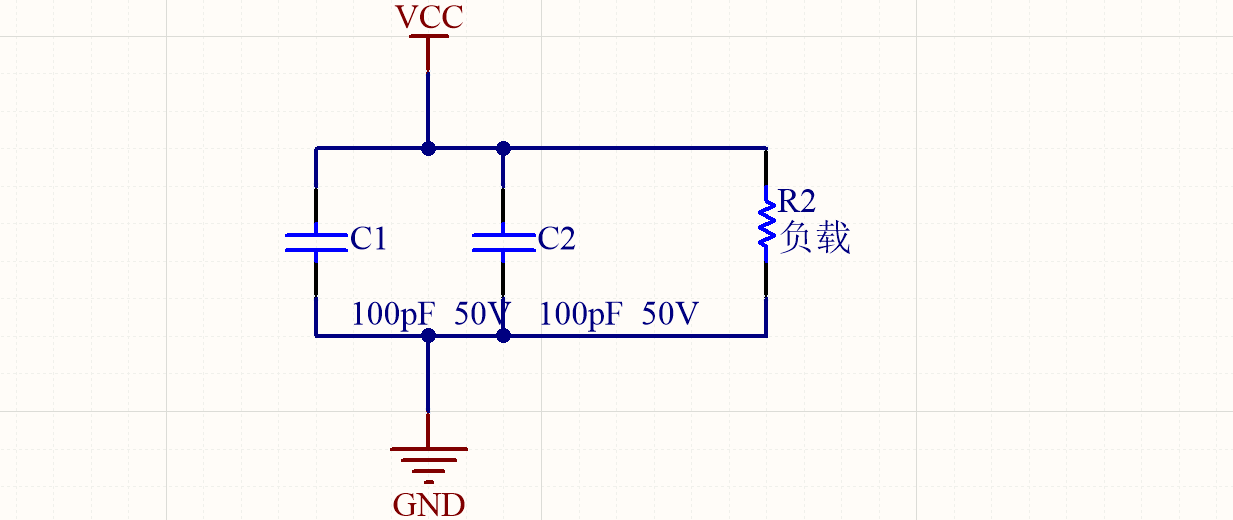

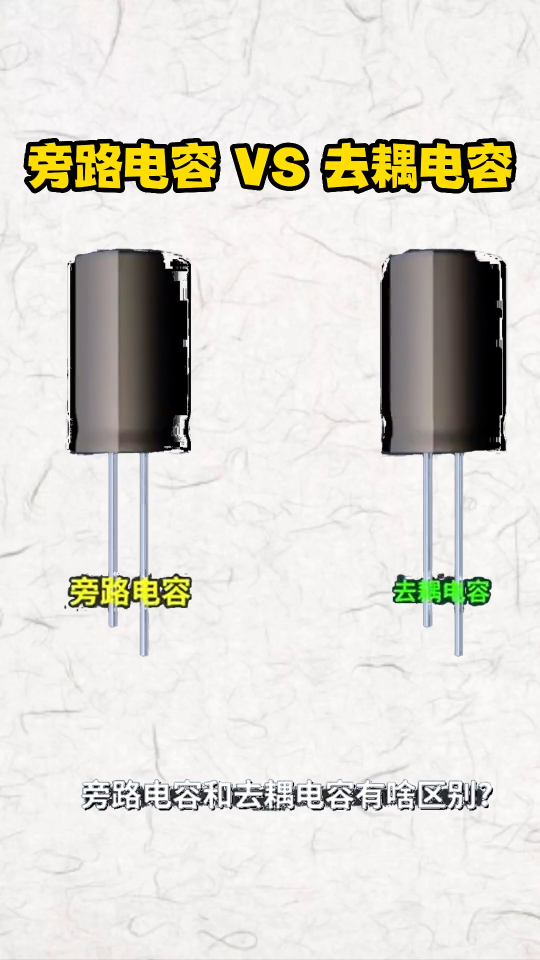

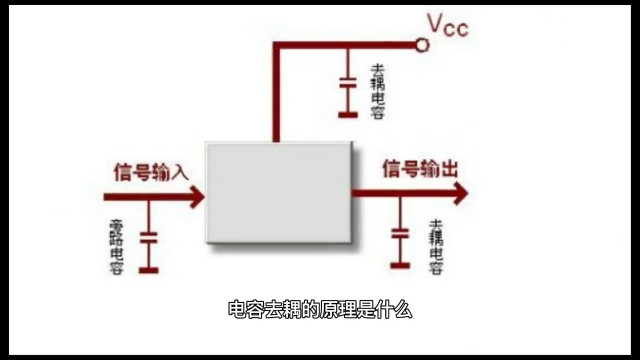

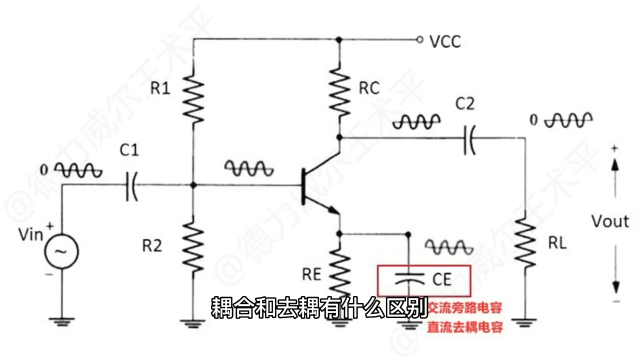

我知道在電源設計中,電源輸入與輸出都要濾波和去耦合,請問下怎么叫去耦電容?什么叫旁路電容啊??我知道概念,它們兩者區別在于:旁路電容是把輸入信號中的干擾信號去掉,而去耦電容是把輸出信號中的干擾信號去掉;但是我不知道具體怎么區分?難道左邊的是旁路電容,右邊的是去耦電容嗎?

2024-01-08 11:30:57

請較一下LDO(比如LT3045)和普通三端穩壓(比如LT1083)輸入電容與輸出電容正確的計算方法,用書上的方法計算都感覺不對,我感覺用去耦的方式計算應該比較對一下,請教一下具體怎么配置嗎

比如

2024-01-04 08:04:43

LTC4364規格書里的典型應用,低壓輸入VCC都是直接接VIN;36~72輸入是通過電阻接VIN, 但是圖上沒有顯示有接VCC的去耦電容,請問這種情況下VCC是否不需要去耦電容?謝謝

2024-01-04 07:55:12

電容充電時間計算是計算一個電容器從初始電壓充電到目標電壓所需的時間。這個時間可以由一個簡單的公式來計算。在本文中,我將詳細解釋電容充電時間的計算公式,并提供一個詳實和細致的說明,以確保你理解電容充電

2023-12-28 16:49:44 2317

2317

如上述截圖(UG-1098 51頁),有以下幾點不明白:

1)IcalibrationFSP 0.0002這個值是怎么計算出來的,最好說明下推導過程,這個值和ADE9000的動態范圍及互感器的比值

2023-12-25 08:14:39

如何計算安規電容漏電流?

2023-12-15 16:54:55 524

524

AD7173-8的評估板上的ADC輸入端電容均未給出容值,還有其它部分電路的電容也未給出容值,有沒有對應的參考值呢?謝謝!

截圖如下:

2023-12-15 07:01:47

怎樣設計和驗證TRL 校準件以及TRL 校準的具體過程

2023-12-14 09:40:37 0

0 在使用AD5546做精密衰減的參考電路中,有一個反饋電容C6。這個電容值的大小應該如何隨頻率變化呢?

在參考輸入是正弦波頻率是150KHZ~1750KHZ頻段的時候適合用多大容值的電容呢?

2023-12-14 06:07:39

請問AD7192噪聲 和精度是怎樣計算的?例如4.7HZ128倍時12NV有效值噪聲怎么算出的精度22.5(20)

2023-12-06 08:03:41

為什么要計算電容器壽命?

2023-12-04 14:06:00 185

185

LTC7545按照下面的電路連接,這個是非官方標準的接法,想問下具體的增益計算公式是什么,VOUT和VIN以及數字code值之間的關系。

2023-12-04 07:27:12

請問怎樣才能將SharcAudioToolbox導入SigmaStudio?具體如何操作?

2023-11-30 07:47:12

。

其實,這是容值不同的電容并聯諧振的結果,也是本文要說的第二“振”。

分析起來也很簡單,當一個電容的感性區遇上另一個電容的容性區,諧振峰就出現了。

綜合考慮VRM和芯片內去耦,如果說第一“振”決定

2023-11-28 15:12:01

來至網友的提問:為什么IC需要自己的去耦電容?

2023-11-24 07:50:02

。

其實,這是容值不同的電容并聯諧振的結果,也是本文要說的第二“振”。

分析起來也很簡單,當一個電容的感性區遇上另一個電容的容性區,諧振峰就出現了。

綜合考慮VRM和芯片內去耦,如果說第一“振”決定

2023-11-21 09:38:08

ADA4807-2的數據手冊有關于容性負載的描述,其中圖69可以看到,對于較大的電容,無需串聯電阻來維持穩定性。

同時,圖68可見,電容越小,需要的串聯電阻越大

但是,按照之前學習的理論,運放

2023-11-17 12:14:36

去藕電容的容值該怎么去計算呢?

2023-11-01 07:29:30

貼片電容測試以后發現貼片電容的容值就有偏低的現象,是什么原因,是不是老化了,有什么解決的方法??

2023-10-30 08:12:15

什么時候會選擇1uf的電容作為去耦電容

2023-10-30 06:45:40

CMRR(Common Mode Rejection Ratio)的絕對值越大對共模電壓的抑制能力越強,本文主要討論在實際應用中OPA關于CMRR的計算具體案例。

2023-10-25 10:36:00 1067

1067

去耦電容的容值是否有固定的標準,自己選擇其他的容量會有影響嗎

2023-10-23 07:21:33

高速先生成員--黃剛

當然這篇文章也還是針對高速信號的交流耦合電容,并不是用于電源的去耦電容,同時文章的靈感也來源于上一篇文章講不同容值電容對高速信號原理上的效果差異。為什么我們在做高速設計的時候

2023-10-17 16:39:41

電容有移相作用,那移相具體是什么作用? 關于電容的移相作用,其實可以從三個方面來進行詳細解析: 1. 從物理學角度來說,電容儲存電荷,當電壓變化時,電容器中的電荷會發生變化,這種變化會導致電容器產生

2023-10-17 16:15:46 1615

1615 會有隔直電容,做過類似硬件原理的朋友都知道,電容的容值一般就是100到幾百nf級別的,有的用100nf,有的用220nf,差不多就是這個量級了。

大家用著也很習慣,只要鏈路的阻抗損耗等PCB參數優化

2023-10-13 16:28:01

首先大概說一下結論,兩個相同容值和耐壓值的電容,并聯之后:耐壓值不變,容值增加。C=C1+C2.串聯之后:耐壓值為兩電容之和,容值減小1/C=1/C1+1/C2.

2023-09-26 10:14:45 1673

1673

在EMC設計中,電容是應用最廣泛的元件之一,主要用于構成各種低通濾波器或用作去耦電容和旁路電容。大量實踐表明∶在EMC設計中,恰當選擇與使用電容﹐不僅可解決許多EMI問題﹐而且能充分體現效果良好

2023-09-20 08:22:28

相互光電隔離的數字地和模擬地之間要考慮到地點位平衡,采用電容連接,容值為1-10nf,對于這個結論,相信大部分情況是正確的。但是,有例外如下:產品是大概是把極其微弱模擬信號放大后讓單片機ADC可以

2023-09-20 06:48:36

怎樣選擇合適的電容 電容是電子元件中的一種重要元器件,用于儲存電荷和調節電壓。電容的原理是根據介質電容比空氣電容大的特性進行設計的,當電容器兩端之間存在電勢差時,電荷便會在兩端之間積聚,形成電場

2023-09-08 11:28:50 1401

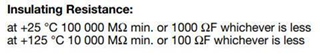

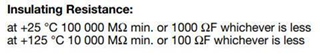

1401 在電源管腳上加電解電容可能會引發一些情況,具體影響取決于電容的性質、電源的特點以及電路的設計。

2023-09-05 09:36:56 223

223 y電容與漏電流的計算? 電容是電學中的一種重要的元件,它可以在電路中儲存電荷,并在需要時將其釋放。在許多應用中,電容被用來濾波、穩壓,以及作為時序電路的元件。然而,電容也會引起漏電流的問題,影響電路

2023-08-27 16:43:33 2961

2961 電容的電量如何計算? 電容的電量是電學中的一項重要指標,指的是電容器內存儲的電荷量。電子學的發展也促進了電容的廣泛應用,電容器在直流還是交流電路中都有著重要的作用。在這篇文章中,我們將詳細討論電容

2023-08-27 16:43:31 6474

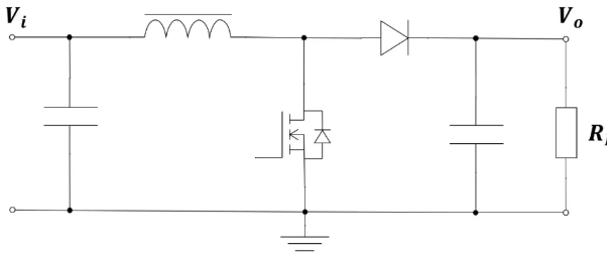

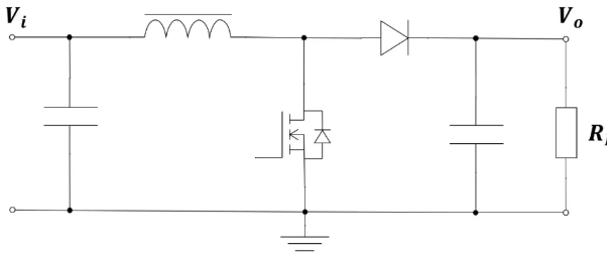

6474 我們之前了解過電容的作用,不外乎儲能、濾波等作用。那么在Boost電源中又該怎樣去選擇電容的型號和電容容量呢?

2023-08-14 15:44:43 1052

1052

llc諧振中,的感性區域和容性區域是根據什么區分的呢,大多數論文中只是說不能工作工作于容性區域,這是為啥呢?

感性區域是諧振電感電流滯后于諧振電容的電壓,為何就能實現zvs?

2023-08-01 10:48:44

DAB的輸出濾波電容怎么計算?

2023-07-31 14:45:19

信號,輸入到此引腳。用于控制輸出電流。如何選型電流采樣電阻?

4.RT/CT引腳(4腳):通過外部RT、CT兩個電阻器連接到地線,用于設置內部振蕩器的頻率。如何計算4腳電阻和電容的值?

5.電感如何計算?

以上,假如從11.1V升壓到56V

2023-06-08 13:57:41

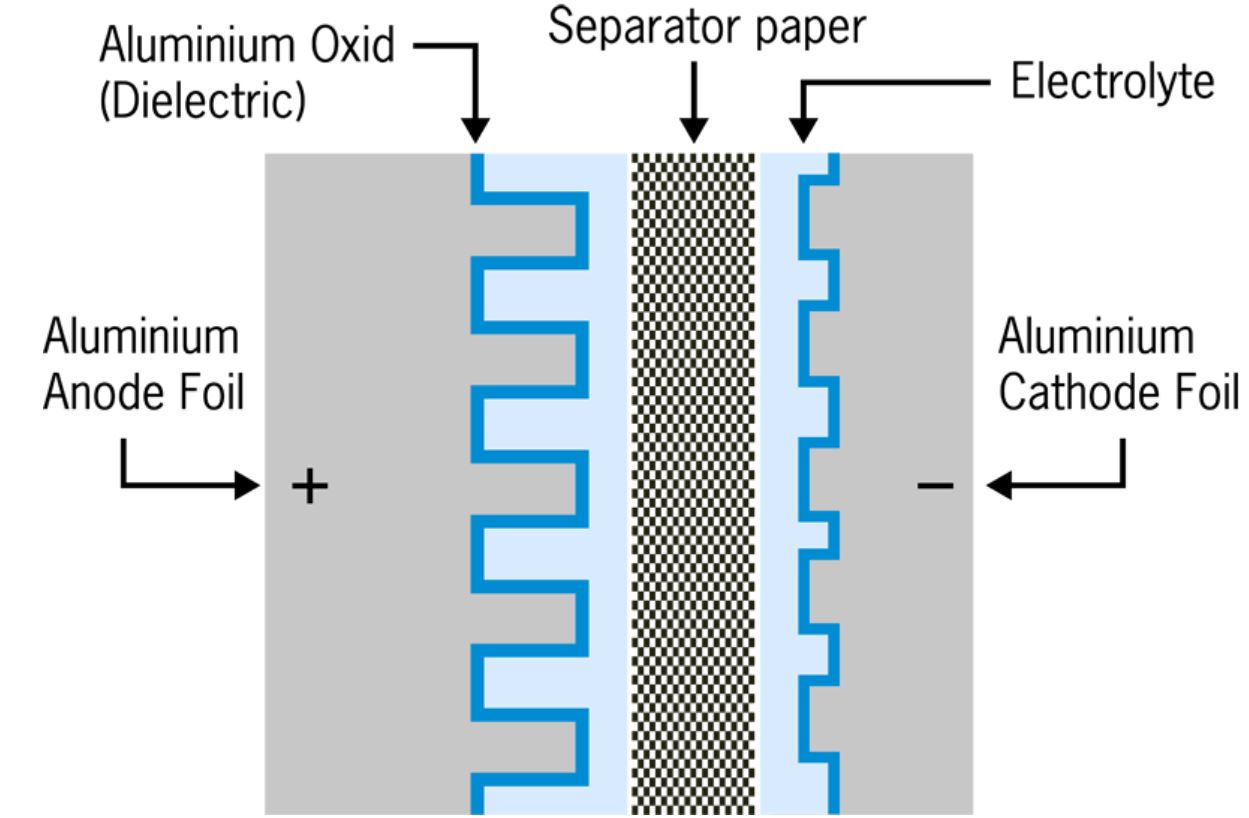

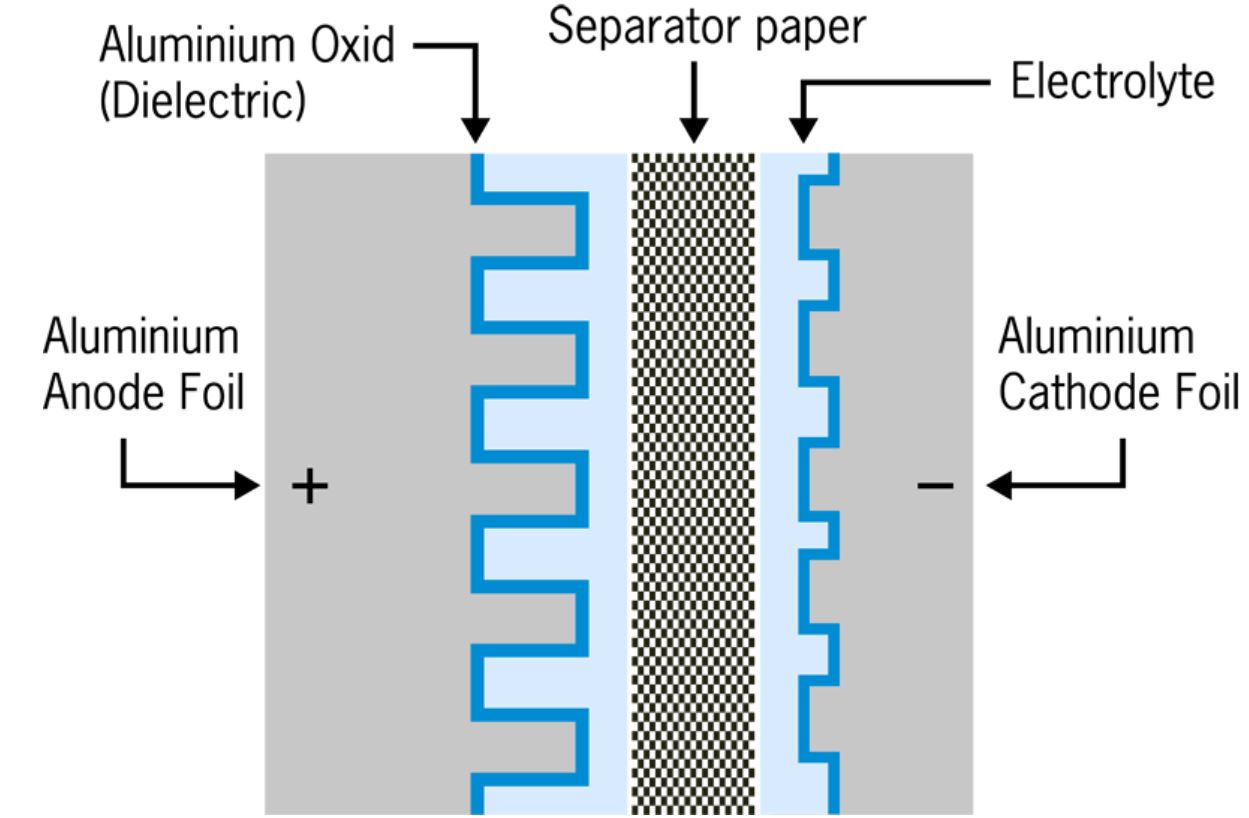

的結構

電容的結構組成可以簡單分為三部分:電極+介質+電極,以下是片狀多層陶瓷電容和鋁電解電容的基本結構示意圖:

電容的容值計算公式為:

C為電容值,單位法拉F,ε為介質介電常數,S為電極的面積,d

2023-06-07 09:02:22

高速先生成員--孫小兵

我們先來了解一下容性負載和感性負載對鏈路阻抗的影響。仿真鏈路模型如下圖所示。鏈路中有三段50Ω的理想傳輸線,第一段和第二段之間增加一個電容模擬容性負載,第二段和第三段之間增加

2023-05-16 17:57:26

電容為什么能過濾波?多大的電容濾掉怎樣的波呢?

2023-05-15 14:32:56

如輸入為5V的電源,并聯10個0.1u的電容后接地。為什么不是直接接一個1u的電容而是接10個0.1u電容。論容值 1u=0.1u*10 。求解!!

2023-04-21 18:09:28

去耦陶瓷電容在電源和地引腳的作用是什么?

2023-04-21 18:07:13

請問電源去耦和電源濾波是一回事嗎?

2023-04-21 17:42:23

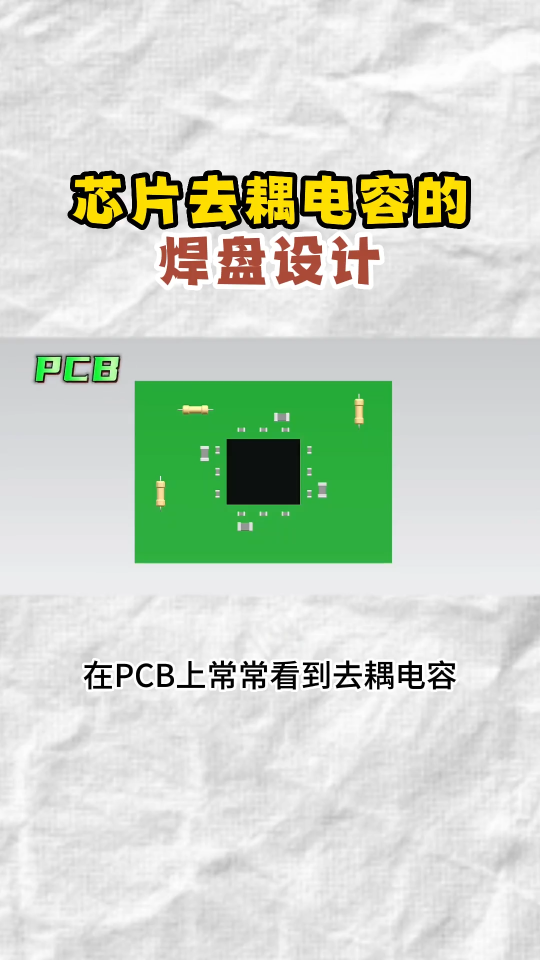

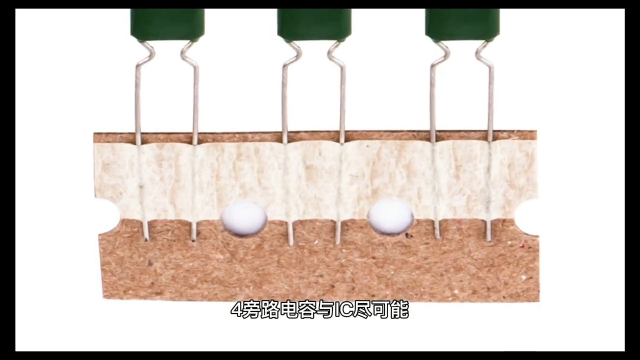

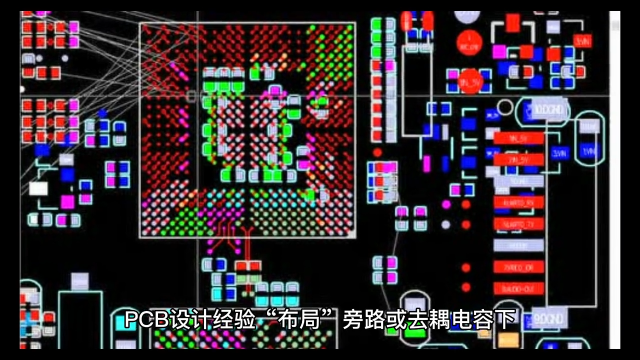

電源去耦電容為何要接近IC電源引腳?是什么原因呢?

2023-04-21 17:36:30

封閉環路可能造成干擾問題。 選擇正確類型的去耦電容低頻噪聲去耦通常需要用電解電容(典型值為1F至100F),以此作為低頻瞬態電流的電荷庫。將低電感表面貼裝陶瓷電容(典型值為0.01F至0.1F)直接

2023-04-21 17:27:59

通過遵循一些在PCB布局中放置去耦電容器的準則,了解如何減少二次諧波失真。 在上一篇文章中,我們討論了需要對稱的PCB布局以減少二次諧波失真。 在本文中,我們將看到,如果沒有適當的去耦,我們

2023-04-21 15:24:03

電容為什么能過濾波?多大的電容濾掉怎樣的波呢?

2023-04-20 17:28:44

刪減。 IC 電源引腳的去耦電容的容值通常會比較小,如 0.1μF、0.01μF 等;對應的封裝也比較小,如 0402封裝、0603封裝等。在擺放去耦電容時,應注意以下幾點。 (1)盡可能靠近電源

2023-04-20 10:32:14

距離。 現在計算出的電感僅為0.12 nH,我們可以看到一對通孔可以提供遠遠優于走線的性能。 結論 我們已經討論了在去耦電容器和位于同一PCB層上的高速數字IC之間建立高性能連接的一項重要技術。原作者:booksoser 汽車電子工程知識體系

2023-04-14 16:51:15

常用到的電感就是“貼片功率電感”,那大家如何保證選擇的“貼片功率電感”是可靠的? 假設通過計算也好還是參考原廠設計也好,我們已經知道了電感值。那我們怎么去選型呢?下面是村田的“貼片功率電感”關鍵參數

2023-04-14 14:56:28

MHZ的區域造成阻抗。適合用于中頻范圍內(KHZ到MHZ)。也常用于去耦電路和高頻率波。 特殊的低損耗陶質電容和云母電容適合與甚高頻應用和微波電路。 為了得到最好的EMC特性,電容有更低的ESR(等效

2023-04-12 16:42:43

的交流干擾,但并不是使用的電容容量越大越好,因為實際的電容并不是理想電容,不具備理想電容的所有特性。 去耦電容的選取可按C=1/F計算,其中F為電路頻率,即10MHz取0.1uF,100MHz取

2023-04-11 16:26:00

我現在正在制作一個新的原理圖并放置旁路電容器。我正在查看設計指南文檔 AN5426,它對 S32K144 的 100 針版本提出了以下建議:而具有相同微控制器的開發板具有用于去耦電容的功能:S32K148EVB 更進一步: 這 3 個中的最佳實踐是什么?

2023-04-11 06:33:39

在RTT的ADC驅動框架里,adc只讀回原始值,上層在根據adc的最大量程電壓去換算成實際電壓。這會帶來一個問題:應用需要知道所使用的ADC通道的量程信息才能做具體換算。我的疑惑是,既然這個量程

2023-04-07 16:15:05

旁路電容,一般也被叫做去耦電容,在我們的布局中往往是緊靠著IC的電源和地腳,而且往往他的容值為0.1uF,今天我們就來說說為什么要這樣做和這樣選型。 一、為什么旁路電容緊盯著IC不放 電線

2023-04-03 14:42:53

BGA放置在PCB頂層,退耦電容放置在BGA下面的底層,如何移動退耦電容?

2023-03-29 17:24:49

電源端為什么要加那么多去耦電容,而不是用一個等效的大電容代替!如輸入為5V的電源,并聯10個0.1u的電容后接地。為什么不是直接接一個1u的電容而是接10個0.1u電容。論容值 1u=0.1u*10 。求解!!

2023-03-28 16:12:56

設計中最常用到的電感就是“貼片功率電感”,那大家如何保證選擇的“貼片功率電感”是可靠的? 假設通過計算也好還是參考原廠設計也好,我們已經知道了電感值。那我們怎么去選型呢?下面是村田的“貼片功率電感”關鍵

2023-03-27 16:22:01

數字電路的直流供電,正負極之間為什么并聯若干個不同電容值的解耦電容呢?

2023-03-24 17:23:57

電子發燒友App

電子發燒友App

評論