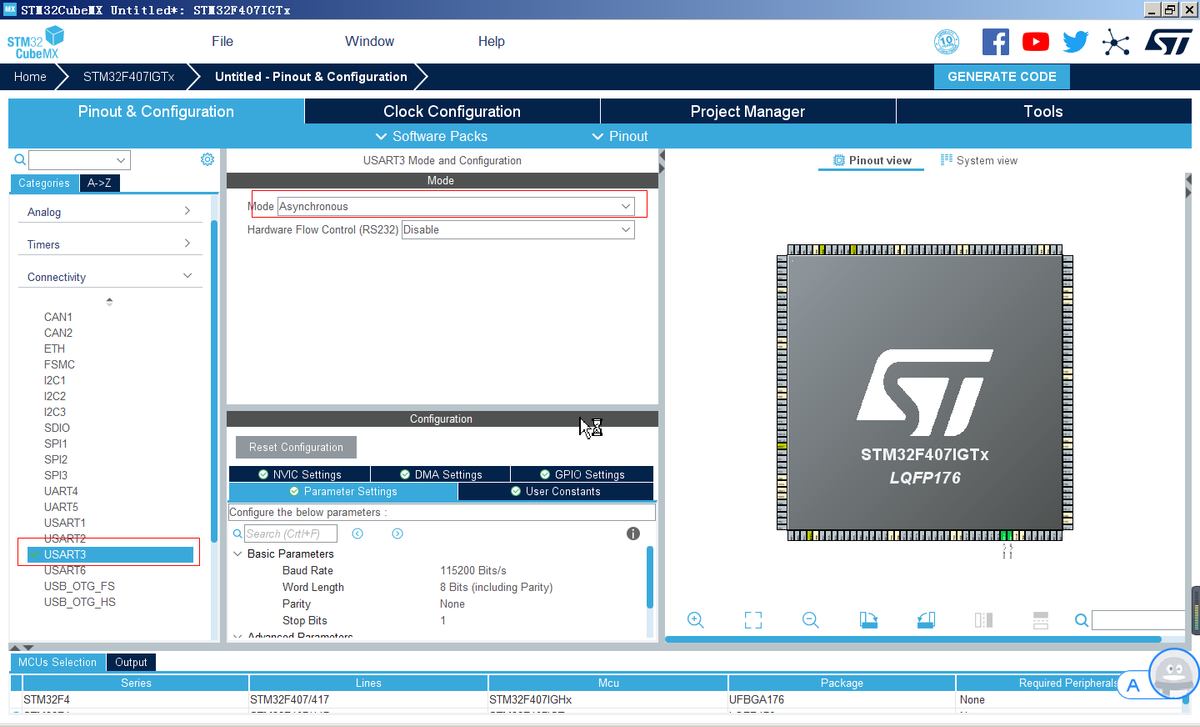

HSI為24M,用HSI配置PLL 48M時(shí)鐘作為HCLK時(shí),無(wú)法用SW口進(jìn)行仿真,只要HCLK不使用PLL,就可以正常進(jìn)行仿真,請(qǐng)教一下PLL的參數(shù)該如何配置啊?多謝!!!!!!

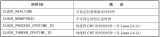

現(xiàn)PLL配置參數(shù)

2024-03-13 09:50:57

NuMaker-IoT-M487開(kāi)發(fā)板使用RT-Thread Studio創(chuàng)建工程。連上WIFI后一切正常,當(dāng)開(kāi)啟NTP獲取網(wǎng)絡(luò)時(shí)間時(shí)提示錯(cuò)誤,偶爾能打印出來(lái)NTP時(shí)間。

2024-03-05 08:26:16

Proteus是一款功能強(qiáng)大的電子電路設(shè)計(jì)與仿真軟件,其中包括了波形發(fā)生器的功能。使用Proteus的波形發(fā)生器,您可以快速創(chuàng)建各種波形,并對(duì)其進(jìn)行可視化分析。以下是關(guān)于如何在Proteus中調(diào)出

2024-02-23 16:53:57 458

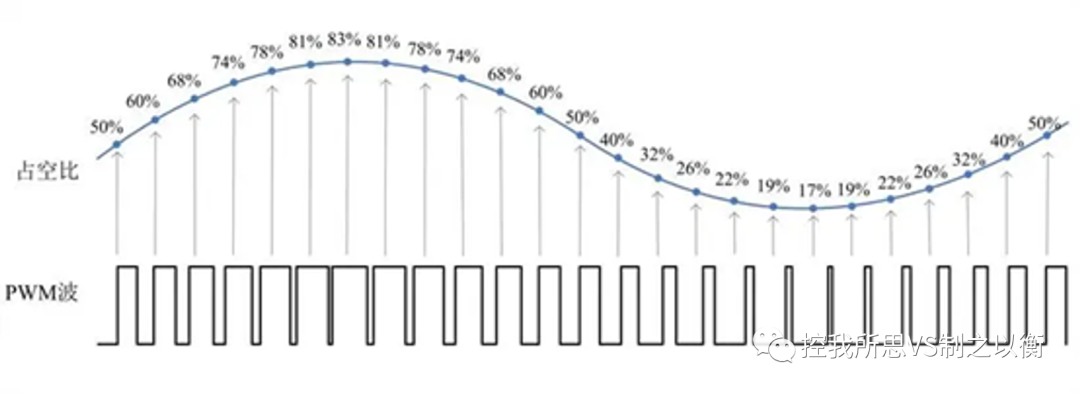

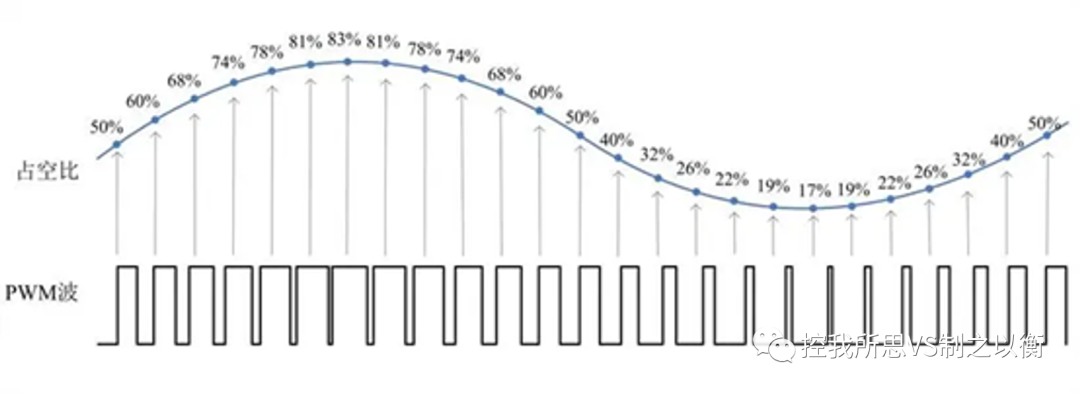

458 SPWM是一種常見(jiàn)的脈寬調(diào)制技術(shù),主要用于變頻器中控制交流電機(jī)的輸出頻率和幅值。SPWM脈沖調(diào)制變頻器的輸出波形實(shí)質(zhì)上是一串脈沖信號(hào),其特征是具有可變的脈沖寬度和固定的脈沖頻率。

2024-02-20 16:31:00 110

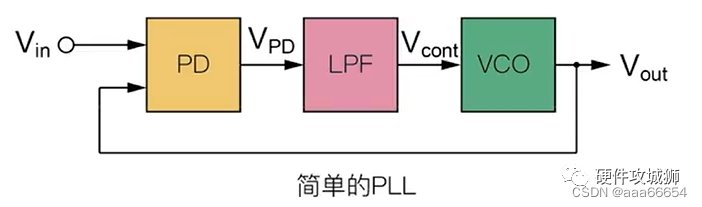

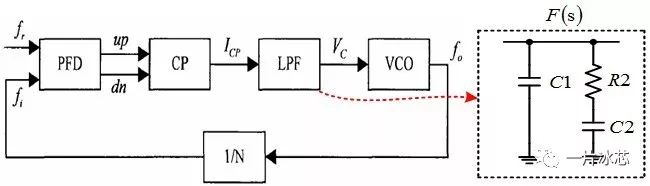

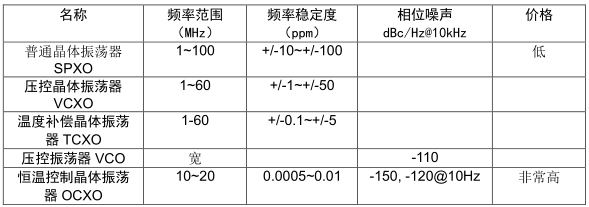

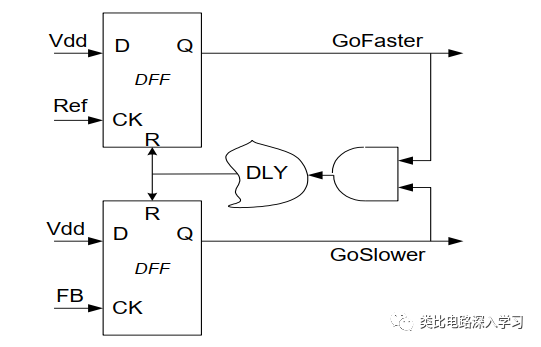

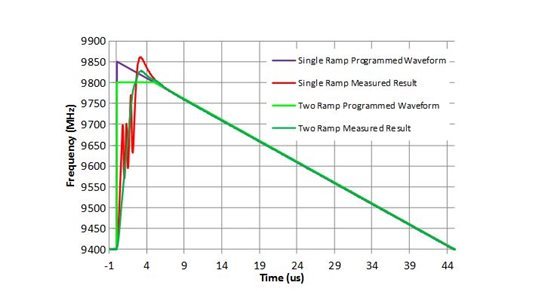

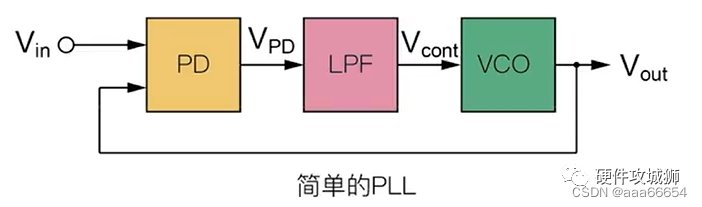

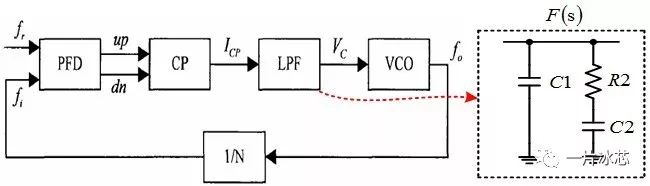

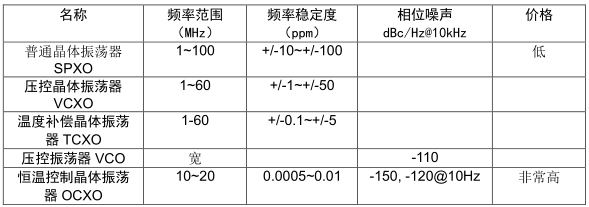

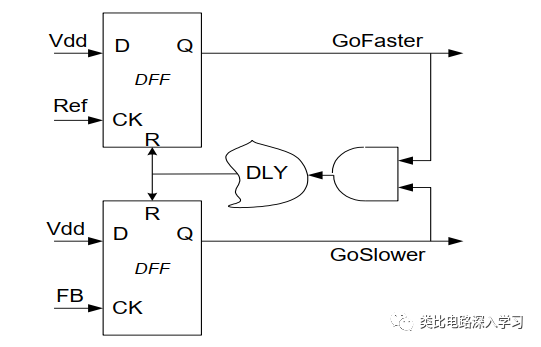

110 鎖相環(huán) (PLL) 是電子系統(tǒng)中最通用、最靈活和最有價(jià)值的電路配置之一,因此在許多應(yīng)用中都有使用。它用于時(shí)鐘重定時(shí)和恢復(fù),作為頻率合成器和可調(diào)諧振蕩器,僅舉幾個(gè)例子。

2024-02-17 14:07:00 161

161

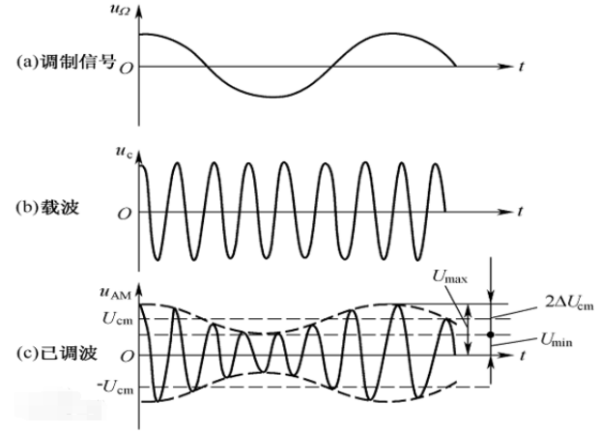

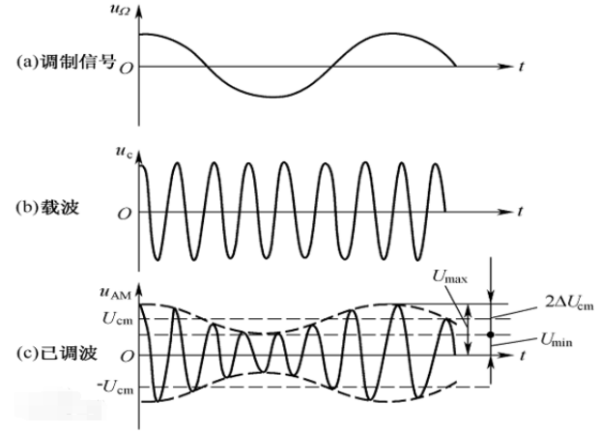

FM波形和AM波形它們有什么共同點(diǎn)和不同點(diǎn)呢? FM波形和AM波形是調(diào)制技術(shù)中常見(jiàn)的兩種模式。雖然它們?cè)?b class="flag-6" style="color: red">調(diào)制波形的方式和應(yīng)用方面有著一些共同點(diǎn),但也存在著一些顯著的差異。下面將詳細(xì)探討FM波形和AM

2024-02-06 14:50:10 263

263 。 一、單極性PWM調(diào)制: 單極性PWM調(diào)制指的是在電路中,只使用一種極性的脈沖信號(hào)來(lái)調(diào)制模擬信號(hào)。根據(jù)信號(hào)值的大小,決定脈沖的寬度。通常,當(dāng)模擬信號(hào)的值高于設(shè)定的閾值時(shí),輸出脈沖為高電平,反之為低電平。單極性PWM調(diào)制的一種常見(jiàn)應(yīng)用是直

2024-02-06 14:13:13 820

820 SPWM的輸出電壓波形和電流波形有什么不同? SPWM(正弦脈寬調(diào)制)是一種常用的交流變頻控制技術(shù),主要用于控制電機(jī)等電力設(shè)備。在SPWM技術(shù)中,輸出電壓波形和電流波形有一些不同之處,下面將詳細(xì)介紹

2024-02-06 13:59:49 329

329 由一個(gè)參考正弦波的振幅和頻率決定。這些脈沖信號(hào)的寬度按照正弦波形的周期進(jìn)行調(diào)整,以便產(chǎn)生一個(gè)與參考正弦波頻率相同的輸出信號(hào)。 生成SPWM波形的方法有多種,下面將介紹其中幾種常見(jiàn)的方法: 1. 基于查表法的SPWM波形生成: 這種方法適用于頻率相對(duì)較

2024-02-06 13:52:16 338

338 SPWM脈寬調(diào)制變頻器出來(lái)的是什么波形,是脈沖吧? SPWM是一種常見(jiàn)的脈寬調(diào)制技術(shù),主要用于變頻器中控制交流電機(jī)的輸出頻率和幅值。SPWM脈沖調(diào)制變頻器的輸出波形實(shí)質(zhì)上是一串脈沖信號(hào),其特征是具有

2024-02-06 11:33:14 1207

1207 SPWM調(diào)制方式是怎樣實(shí)現(xiàn)變壓功能的?又是怎樣實(shí)現(xiàn)變頻功能的? SPWM是一種常見(jiàn)的調(diào)制方式,它通過(guò)調(diào)節(jié)脈沖的寬度來(lái)控制輸出波形的幅度和頻率,因此可以實(shí)現(xiàn)變壓和變頻功能。下面將詳細(xì)介紹SPWM調(diào)制

2024-02-06 11:09:00 281

281 SPWM調(diào)制波形是由哪兩種波形進(jìn)行調(diào)制獲得的? SPWM調(diào)制波形是由三角波和參考波形進(jìn)行調(diào)制獲得的。 SPWM調(diào)制是一種常用的電力電子調(diào)制方法,廣泛應(yīng)用于交流電壓調(diào)制器、逆變器和變頻器等電力電子設(shè)備

2024-02-06 09:25:56 237

237 在SPWM調(diào)制中,調(diào)制波和載波的信號(hào)波形一般各是什么? SPWM調(diào)制(正弦波脈寬調(diào)制)是一種常用于交流電驅(qū)動(dòng)和逆變器的調(diào)制技術(shù),它通過(guò)調(diào)節(jié)一個(gè)正弦波形的寬度(脈寬)來(lái)控制輸出的交流信號(hào)波形

2024-02-05 16:48:49 384

384 什么是PWM和SPWM波形??jī)烧叩膮^(qū)別在哪? PWM(脈寬調(diào)制)和SPWM(正弦脈寬調(diào)制)都是常用于控制和調(diào)節(jié)電力設(shè)備的波形方法。它們的主要區(qū)別在于波形的形狀和應(yīng)用領(lǐng)域。下面我們將詳細(xì)介紹PWM

2024-02-05 16:36:39 306

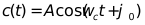

306 調(diào)幅波和調(diào)頻波是兩種常見(jiàn)的無(wú)線電波調(diào)制方式,它們的波形有著顯著的區(qū)別。首先,讓我們了解一下這兩種調(diào)制方式的原理。

2024-02-05 15:12:19 705

705

低壓差調(diào)節(jié)器(LDO)如何影響PLL相位噪聲?? 低壓差調(diào)節(jié)器 (LDO) 在集成電路設(shè)計(jì)中扮演著非常重要的角色。它們的主要功能是將高電壓降至可接受的低電壓水平,以供給PLL電路中需要的各個(gè)部分

2024-01-31 16:43:11 170

170 任意波發(fā)生器,如何輸出波形、帶調(diào)制的信號(hào)? 任意波發(fā)生器是一種用于產(chǎn)生各種波形的信號(hào)發(fā)生器。它可以生成特定頻率、幅度、相位和形狀的波形,并在需要時(shí)進(jìn)行調(diào)制。在本文中,我們將探討如何使用任意波發(fā)生器

2024-01-19 15:54:52 168

168 屏中,可以給每個(gè)控件(包括窗口)創(chuàng)建一個(gè)定時(shí)器,定時(shí)器到點(diǎn)后觸發(fā)v-on:timer事件。在AWTK串口屏中,提供了6個(gè)定時(shí)器相關(guān)函數(shù):start_timer啟動(dòng)定

2024-01-13 08:24:26 127

127

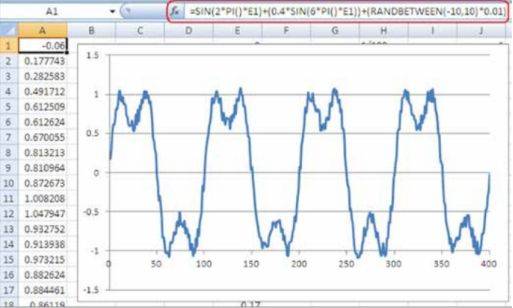

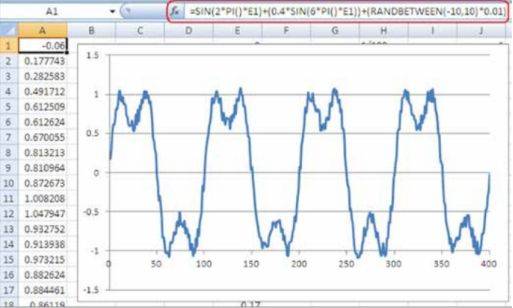

在從零開(kāi)始創(chuàng)建任意波形時(shí),大多數(shù)工程師要么采用工程編程環(huán)境,比如Matlab、LabVIEW或VEE,要么采用免費(fèi)或收費(fèi)的定制任意波形軟件套件。這些是很好的工具,但如果你不常用的話,它們的價(jià)格就顯得比較昂貴,并且學(xué)會(huì)使用也比較耗時(shí)。多數(shù)工程師未曾想到的另一個(gè)方案是Excel。

2023-12-26 15:02:52 270

270

對(duì)AD9779A中的調(diào)制器進(jìn)行相關(guān)的配置以后,正常輸出波形為正弦波,可是有時(shí)候又會(huì)出現(xiàn)包絡(luò)波形,這是怎么回事?正常的經(jīng)過(guò)調(diào)制以后應(yīng)該出現(xiàn)正弦波還是包絡(luò)波形?AD9779A中有解調(diào)器嗎?如果沒(méi)有的話,那么正常經(jīng)過(guò)調(diào)制以后不是應(yīng)該出現(xiàn)包絡(luò)波么?請(qǐng)幫我解答一下吧!謝謝了~

2023-12-25 08:07:59

和sinLO接到AD2S1200輸入端,再用示波器看波形,波形下端被截止一部分

這是為什么?一直沒(méi)有找到解決方法,輸入AD2S1200的波形符合3.6Vp-p,10HZ

2023-12-21 06:48:46

信息處理等領(lǐng)域有重要的應(yīng)用。 空間光調(diào)制器的工作原理基于光的幅度、相位的空域分布特性。當(dāng)光通過(guò)空間光調(diào)制器時(shí),其幅度和相位會(huì)由光在空間上的分布結(jié)構(gòu)所決定,通過(guò)調(diào)節(jié)空間光調(diào)制器的控制參數(shù),可以控制光的幅度、相位的

2023-12-20 13:45:01 734

734 大家好,

我最近在調(diào)試一塊發(fā)射通道時(shí)遇到的問(wèn)題

使用AD9746配合ADRF6755做正交調(diào)制,輸出頻譜中存在大量DAC時(shí)鐘的偶次諧波,切能量很大,

請(qǐng)教大家造成這種現(xiàn)象的原因是什么,感謝!!!

2023-12-19 06:43:59

我使用的是ti的dsp2812的spi連接AD7988-5,一切都工作的很好,但是波形總是出現(xiàn)一點(diǎn)相位失真,例如測(cè)試3000Hz正弦波會(huì)出現(xiàn)幾個(gè)Hz的頻率錯(cuò)誤,AD7988-5的輸入端是測(cè)試的信號(hào)

2023-12-15 07:00:15

中,常見(jiàn)的信號(hào)調(diào)制方式有以下幾種: 1. 幅度調(diào)制(AM) 幅度調(diào)制是一種將原始信號(hào)的幅度變化嵌入到載波信號(hào)中的調(diào)制方式。在幅度調(diào)制中,調(diào)制信號(hào)的幅度決定了載波的幅度大小,從而改變了信號(hào)的能量分布。幅度調(diào)制常用于調(diào)制

2023-12-08 16:06:14 697

697 11月30日消息,據(jù)來(lái)自韓國(guó)的未經(jīng)證實(shí)的消息稱,蘋(píng)果公司在多次嘗試完善自研 5G 調(diào)制解調(diào)器芯片失敗后,決定停止開(kāi)發(fā)該芯片。

2023-11-30 09:29:05 402

402 我們知道所有的一切調(diào)制都是對(duì)波形的改變,那么實(shí)現(xiàn)這些改變的元器件有哪些呢

2023-11-27 10:02:11 394

394

示波器采集模式決定由示波器從模擬-數(shù)字轉(zhuǎn)換器(簡(jiǎn)稱ADC)所獲取的采樣點(diǎn)如何與波形點(diǎn)相結(jié)合及顯示。那么示波器采集模式有哪幾種?示波器在進(jìn)?信號(hào)采集中沒(méi)有出現(xiàn)波形,該如何處理?接下來(lái)一起看看

2023-11-20 16:31:37 356

356

,deadline_timer會(huì)被逐漸淘汰。 僅僅固定時(shí)間后去執(zhí)行某任務(wù),可以使用boost中的asio庫(kù)提供了steady_timer定時(shí)器,定時(shí)器的用法也是比較簡(jiǎn)單的,基本上分三步。創(chuàng)建 io_service , 創(chuàng)建timer 并設(shè)置等待時(shí)間, 調(diào)用wait 或async_wait 等待.

2023-11-09 17:20:31 304

304 由于目前C++標(biāo)準(zhǔn)中沒(méi)有現(xiàn)成的定時(shí)器,本設(shè)計(jì)使用C++11相關(guān)語(yǔ)法并進(jìn)行封裝。 本定時(shí)器包含一個(gè)TimerManager類用于創(chuàng)建定時(shí)器和進(jìn)行定時(shí)任務(wù)管理,TimerManager會(huì)創(chuàng)建兩個(gè)線程

2023-11-08 16:50:55 239

239 盡管基本PLL自其出現(xiàn)之日起幾乎保持原樣,但是使用不同技術(shù)制作及滿足不同應(yīng)用要求的PLL的實(shí)現(xiàn)一直給設(shè)計(jì)者提出挑戰(zhàn)。

2023-10-30 16:11:12 1938

1938

到芯片邏輯的正確運(yùn)行。在測(cè)試PLL IP時(shí),通常會(huì)有多個(gè)測(cè)試項(xiàng)目,如頻率測(cè)試、相位噪聲、鎖定時(shí)間、穩(wěn)定性、誤差和漂移等。 但在SoC的ATE測(cè)試中,CP階段通常只進(jìn)行PLL頻率和鎖定測(cè)試。 那么DFT

2023-10-30 11:44:17 662

662

鎖相環(huán)鎖定時(shí)間取決于哪些因素?如何加速鎖定? 鎖相環(huán)(PLL)是一種常見(jiàn)的電路,用于穩(wěn)定頻率。PLL中的關(guān)鍵是相鎖。相鎖發(fā)揮著將輸入頻率與參考頻率調(diào)整到相等的重要作用。在鎖相環(huán)設(shè)計(jì)中,鎖定時(shí)

2023-10-30 10:51:18 899

899 PLL芯片對(duì)電源的要求有哪些? PLL芯片是廣泛應(yīng)用于電子電路中的一種重要的芯片,它主要用于頻率合成、時(shí)鐘信號(hào)的處理和數(shù)據(jù)傳輸?shù)确矫妗T趹?yīng)用中,PLL芯片對(duì)電源的要求非常高,以確保系統(tǒng)的穩(wěn)定、精度

2023-10-30 10:46:54 510

510 PLL對(duì)射頻輸入信號(hào)有什么要求? PLL(Phase Locked Loop)是一種電路,可將輸入信號(hào)和參考信號(hào)的相位和頻率保持一致,用于頻率合成、時(shí)鐘生成、調(diào)制解調(diào)、數(shù)字信號(hào)處理、無(wú)線通信等一些

2023-10-30 10:46:50 410

410 頻率的比例決定了鎖定的頻率倍數(shù),因此對(duì)于VCO的頻率穩(wěn)定性要求比較高。 2. 延遲:VCO的輸出延遲對(duì)于PLL系統(tǒng)的工作非常重要。如果VCO的輸出延遲太大,則可能會(huì)導(dǎo)致鎖定時(shí)間變長(zhǎng)或者無(wú)法鎖定。 3. 噪聲:VCO的輸出噪聲會(huì)影響PLL系統(tǒng)的性能和穩(wěn)定性。因此,要求VCO的輸出噪聲較

2023-10-30 10:46:44 358

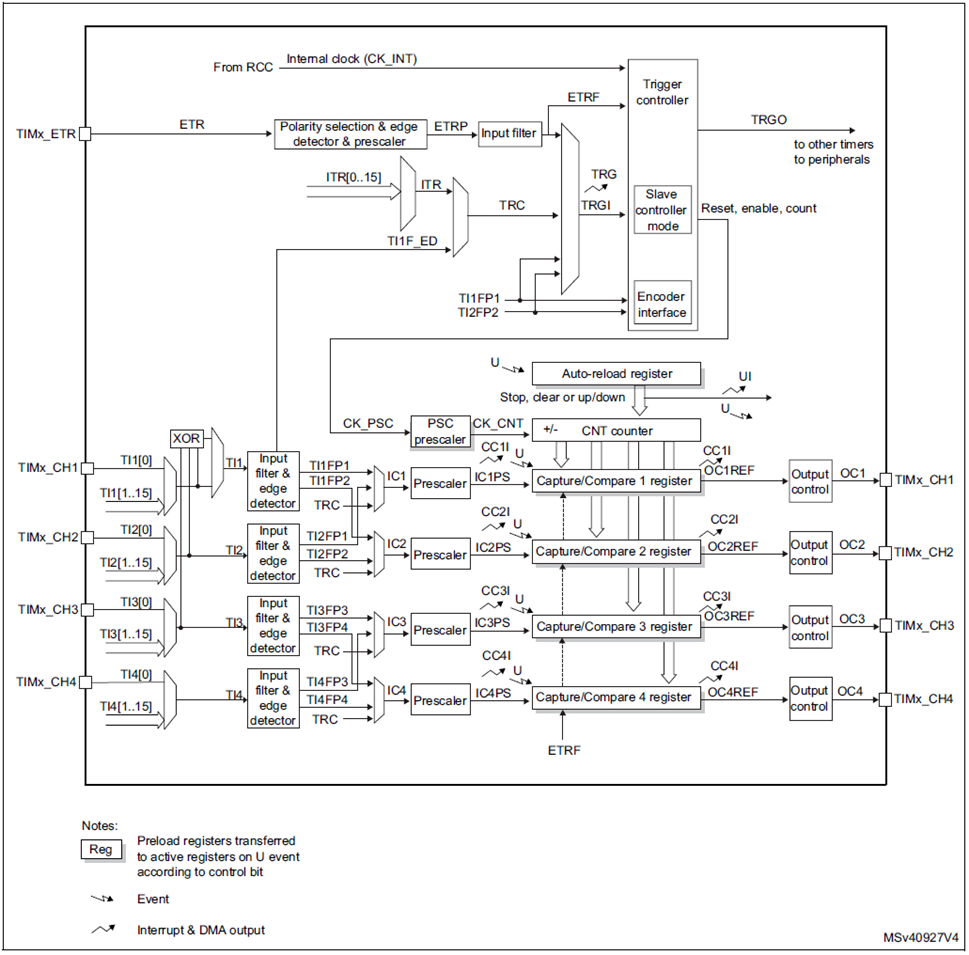

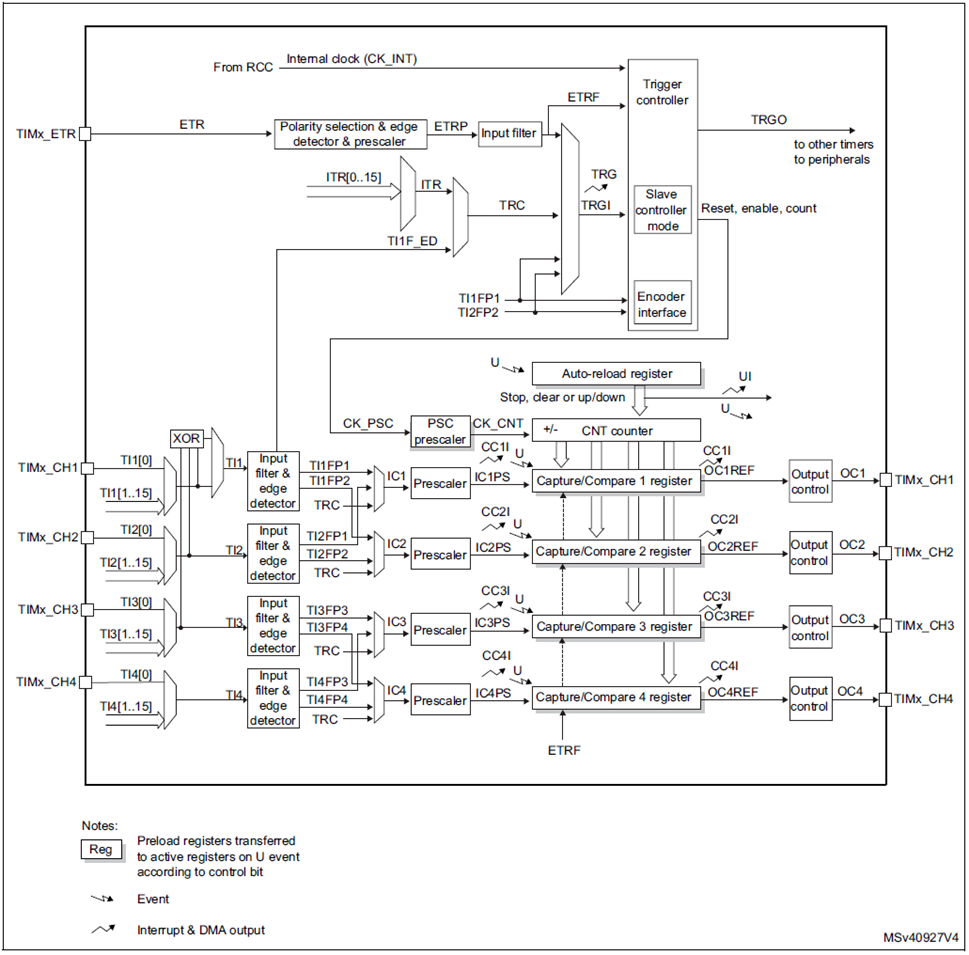

358 本文主要研究了STM32H7芯片系列中定時(shí)器同步啟動(dòng)并輸出PWM波形的實(shí)現(xiàn)方法。

2023-10-24 14:56:29 529

529

了解鎖相環(huán)(PLL)瞬態(tài)響應(yīng) 如何優(yōu)化鎖相環(huán)(PLL)的瞬態(tài)響應(yīng)? 鎖相環(huán)(PLL)是一種廣泛應(yīng)用于數(shù)字通信、計(jì)算機(jī)網(wǎng)絡(luò)、無(wú)線傳輸?shù)阮I(lǐng)域的重要電路。PLL主要用于時(shí)鐘恢復(fù)、頻率合成、時(shí)鐘同步等領(lǐng)域

2023-10-23 10:10:20 869

869 鎖相環(huán)(PLL)基本原理 當(dāng)鎖相環(huán)無(wú)法鎖定時(shí)該怎么處理的呢? 鎖相環(huán)(Phase Locked Loop, PLL)是一種電路系統(tǒng),它可以將輸入信號(hào)的相位鎖定到參考信號(hào)的相位。在鎖相環(huán)中,反饋回路

2023-10-23 10:10:15 1352

1352 鎖相環(huán)(PLL)是一種反饋系統(tǒng),其中電壓控制振蕩器(VCO)和相位比較器相互連接,使得振蕩器可以相對(duì)于參考信號(hào)維持恒定的相位角度。在使用PLL的過(guò)程中您都遇到過(guò)哪些問(wèn)題呢?咱們工程師整理了PLL芯片

2023-10-14 15:55:02 362

362

時(shí)鐘發(fā)生器由哪些部分組成?鎖相環(huán)pll的特點(diǎn)是什么?如何用硬件配置pll? 時(shí)鐘發(fā)生器是指通過(guò)特定的電路設(shè)計(jì)產(chǎn)生適合各種電子設(shè)備使用的時(shí)鐘信號(hào)的器件。時(shí)鐘發(fā)生器由多個(gè)部分組成,其中最核心的是鎖相環(huán)

2023-10-13 17:39:50 443

443 pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式? PLL鎖相環(huán)是現(xiàn)代電子技術(shù)中廣泛應(yīng)用的一種電路,它的作用是將一個(gè)特定頻率的輸入信號(hào)轉(zhuǎn)換為固定頻率的輸出信號(hào)。PLL鎖相環(huán)的三種配置模式分別為

2023-10-13 17:39:48 1099

1099 設(shè)計(jì)一個(gè)振幅調(diào)制器,使其能實(shí)現(xiàn)AM和DSB信號(hào)調(diào)制,輸出波形無(wú)明顯失真。

2023-10-12 09:59:36 2512

2512

目的是想通過(guò)串口觸摸屏控制單片機(jī),實(shí)現(xiàn)輸出PWM的脈寬和頻率的單獨(dú)調(diào)制。。。。stc89c52單片機(jī)一共兩個(gè)定時(shí)器,因?yàn)槊}寬和頻率的單獨(dú)調(diào)制功能就占用了T0和T1了,現(xiàn)在可以通過(guò)獨(dú)立按鍵實(shí)現(xiàn)脈寬和

2023-10-08 07:36:55

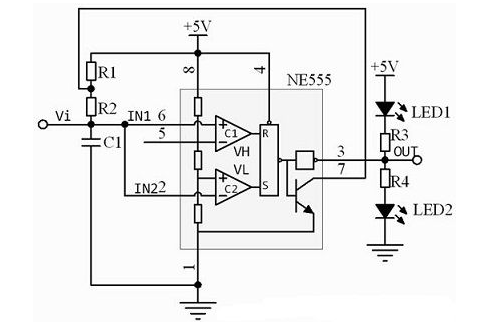

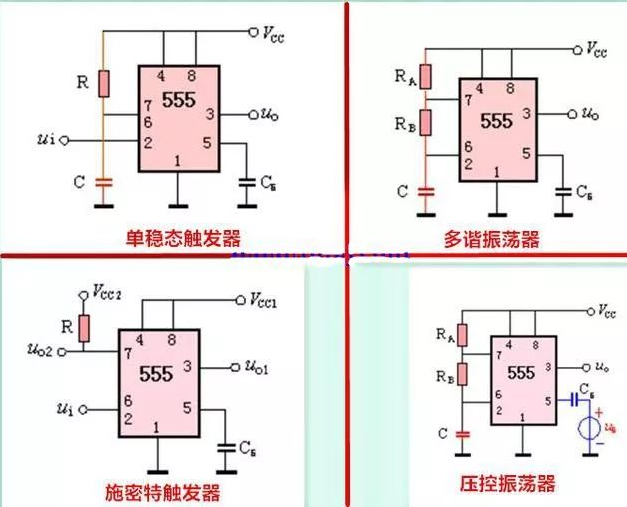

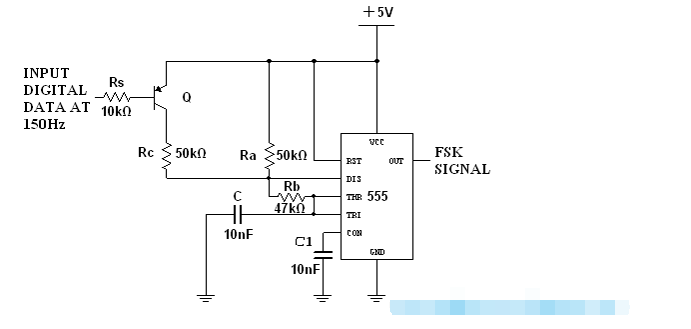

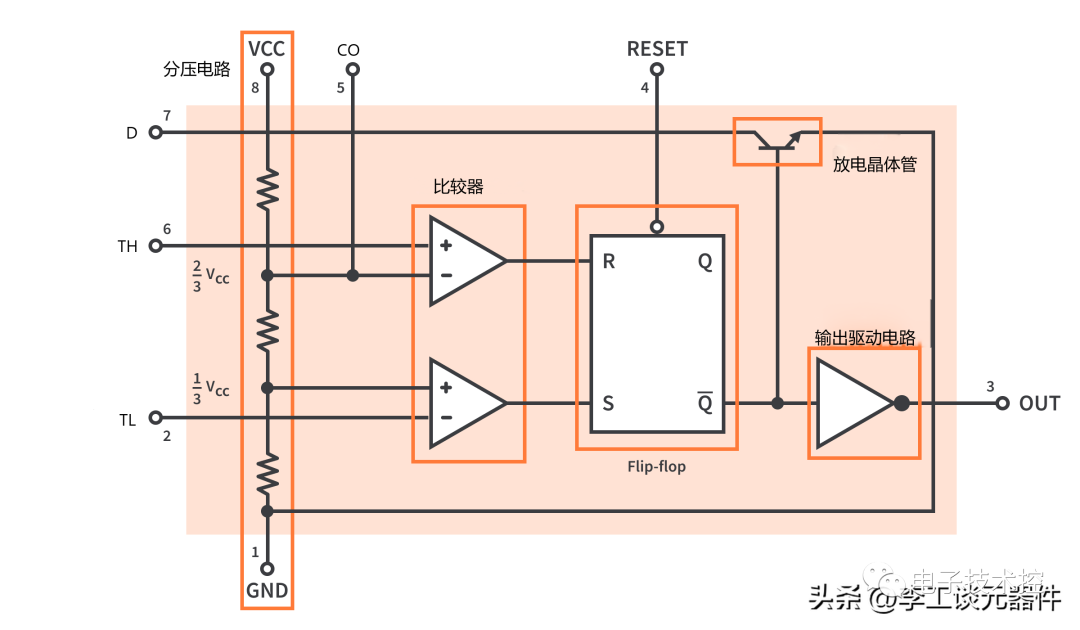

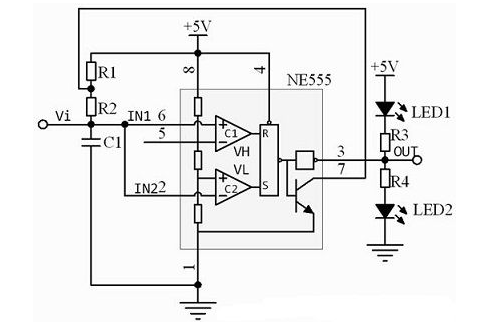

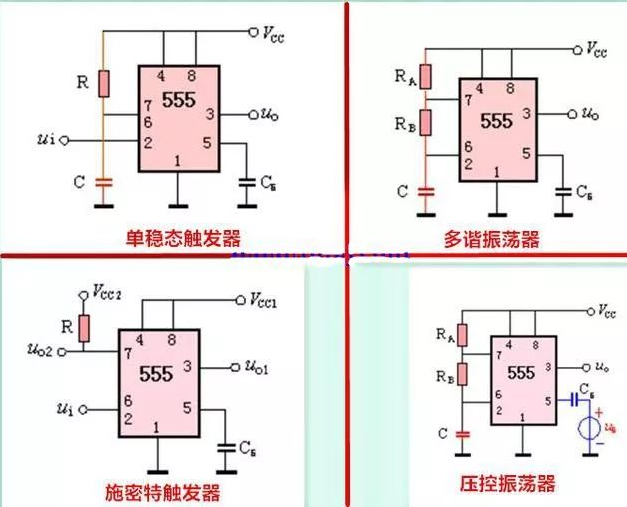

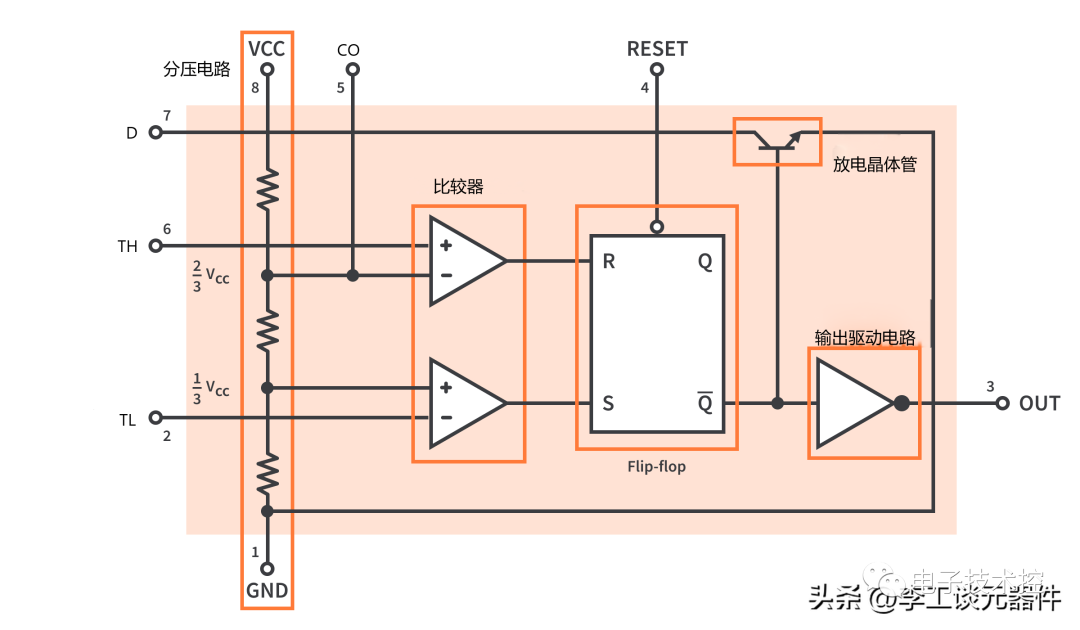

在此模式下,555 作為振蕩器工作。這種工作狀態(tài)的555芯片常用于頻閃燈、脈沖發(fā)生器、邏輯電路時(shí)鐘、音調(diào)發(fā)生器、脈沖位置調(diào)制(PPM)等電路中。如果用熱敏電阻作為定時(shí)電阻,555 IC可組成溫度傳感器,其輸出信號(hào)的頻率由溫度決定。

2023-10-04 17:39:00 1766

1766

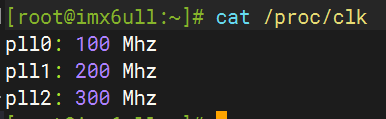

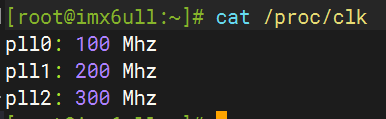

procfs接口創(chuàng)建 實(shí)現(xiàn)效果: 例如, 在 /proc 下創(chuàng)建一個(gè)clk節(jié)點(diǎn),通過(guò) cat /proc/clk 可查看內(nèi)容: 在驅(qū)動(dòng)中添加以下代碼: # include # include

2023-09-27 11:24:06 183

183

數(shù)字調(diào)制是數(shù)字信號(hào)轉(zhuǎn)換為與信道特性相匹配的波形的過(guò)程。 調(diào)制波是二進(jìn)制(或 M進(jìn)制)的已編碼的數(shù)字基帶碼流。 調(diào)制的過(guò)程就是輸入數(shù)據(jù)控制 (鍵控)載波的幅度、 頻率和相位。 MSK 是在數(shù)字調(diào)制技術(shù)上發(fā)展起來(lái)的。 它是二進(jìn)制連續(xù)相位頻移鍵控( CPFSK)的一種特殊情況。

2023-09-21 07:37:27

通常情況下,標(biāo)準(zhǔn)的信號(hào)發(fā)生器并不會(huì)進(jìn)行信號(hào)調(diào)制,功能僅僅只有產(chǎn)生特定頻率、波形、幅度和相位的基本信號(hào),如正弦波、方波、脈沖等。然而,一些專用信號(hào)發(fā)生器具備調(diào)幅(AM)、調(diào)頻(FM)或者QAM等調(diào)制方式的能力。這些信號(hào)發(fā)生器可以在生成基帶信號(hào)的基礎(chǔ)上,將基帶信

2023-09-09 08:07:20 1239

1239

pll鎖定時(shí)間按照頻率精度多少來(lái)計(jì)算? PLL鎖定時(shí)間是指當(dāng)PLL嘗試將輸出頻率與輸入頻率相匹配時(shí)所需的時(shí)間。這個(gè)時(shí)間可以用來(lái)衡量PLL的性能,因?yàn)樗?b class="flag-6" style="color: red">決定了PLL能否快速、準(zhǔn)確地鎖定頻率,并且

2023-09-02 15:12:23 811

811 pll倍頻最大倍數(shù)? PLL倍頻是一種常見(jiàn)的電路設(shè)計(jì)技術(shù),通常用于將信號(hào)的頻率提高到需要的倍數(shù)。PLL倍頻的實(shí)現(xiàn)原理比較復(fù)雜,通常需要使用精密的電路元件、時(shí)鐘信號(hào)以及數(shù)字信號(hào)處理器。本文將詳細(xì)介紹

2023-09-02 14:59:30 811

811 別問(wèn)什么高級(jí)不高級(jí)了,輸出個(gè)波形而已,沒(méi)有啥難的。只是給出了一些細(xì)節(jié),比如你想輸出自己定制的一些波形,該怎么辦?

2023-08-29 09:46:04 592

592

和應(yīng)用。 一、555定時(shí)器的工作原理 555定時(shí)器是一種集成電路,由三個(gè)主要部分組成:比較器、SR鎖存器和輸出驅(qū)動(dòng)器。555定時(shí)器最廣泛應(yīng)用的是單穩(wěn)態(tài)兩種基本工作方式,可根據(jù)外接器件的不同實(shí)現(xiàn)不同的定時(shí)、頻率測(cè)量、波形生成和開(kāi)關(guān)控制功能。 555定時(shí)電路的基本

2023-08-24 15:49:56 5644

5644 。M480可生成來(lái)自BPWM和EPWM的PWM波形波形。

這兩個(gè)示例代碼列出了PLL和BPWM/EPWM設(shè)置,可以從指定的輸入時(shí)鐘頻率生成目標(biāo)輸出頻率。

您可以在下列時(shí)間下載樣本代碼http://www.nuvoton.com/resources-downlo.0108110124。

nuvoton 核

2023-08-23 06:46:42

PWM(脈沖寬度調(diào)制)可用于電機(jī)的調(diào)速、LED的亮度調(diào)節(jié)、無(wú)源蜂鳴器輸出音調(diào)等,是嵌入式系統(tǒng)開(kāi)發(fā)中經(jīng)常采用的方法。本期內(nèi)容以一個(gè)用無(wú)源蜂鳴器播放音樂(lè)的例子,帶領(lǐng)大家了解使用定時(shí)器PWM輸出功能的方法

2023-08-16 06:13:17

555定時(shí)器能夠?qū)崿F(xiàn)多種功能,如振蕩器、定時(shí)器、觸發(fā)器等。外部的電阻、電容和配置方式決定了具體的工作模式和特性。因此,在使用555定時(shí)器時(shí),需要根據(jù)具體的應(yīng)用需求進(jìn)行正確的接線和配置。

2023-08-15 14:35:40 6578

6578

寫(xiě)了一個(gè)vi,單獨(dú)運(yùn)行一切正常,一旦加到項(xiàng)目中就報(bào)錯(cuò)

2023-08-14 17:14:39

HongKe控制電光調(diào)制器的虹科AWGArbitraryWaveformGenerator如今,電光調(diào)制器被廣泛應(yīng)用在光學(xué)、光子學(xué)和脈沖激光的應(yīng)用中,新一代科學(xué)家正在為其實(shí)際應(yīng)用開(kāi)辟新的領(lǐng)域,例如

2023-08-09 08:07:37 536

536

目前是想先利用定時(shí)器觸發(fā)ADC+DMA采集數(shù)據(jù)將信號(hào)發(fā)生器給的正玄波通過(guò)串口打印出來(lái),但是波形有一部分為0,是為啥呢,代碼如下:

MX_GPIO_Init();MX_DMA_Init

2023-08-07 14:16:55

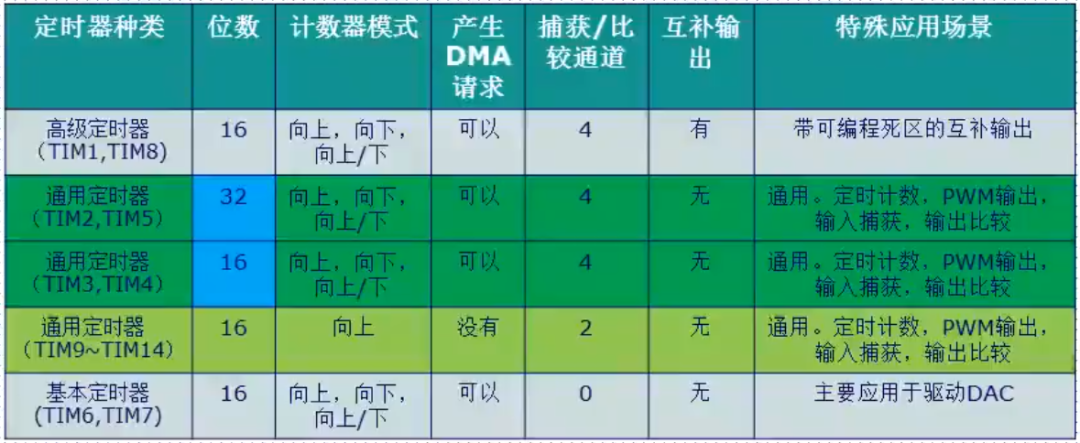

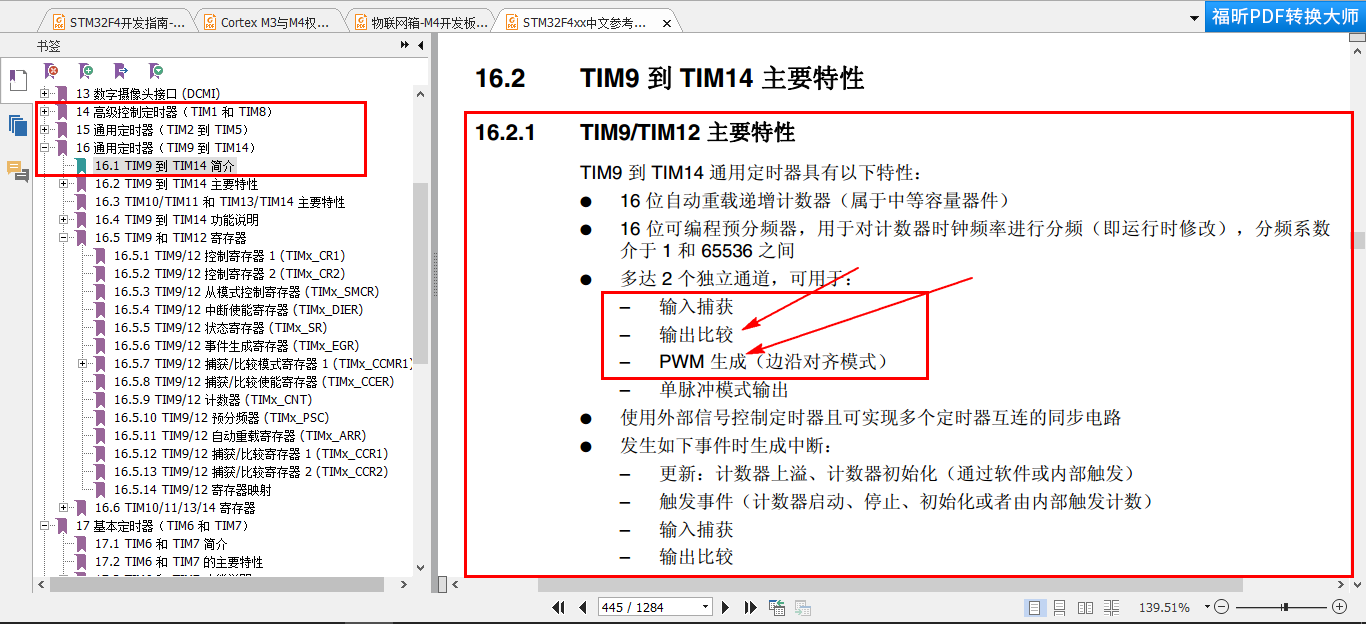

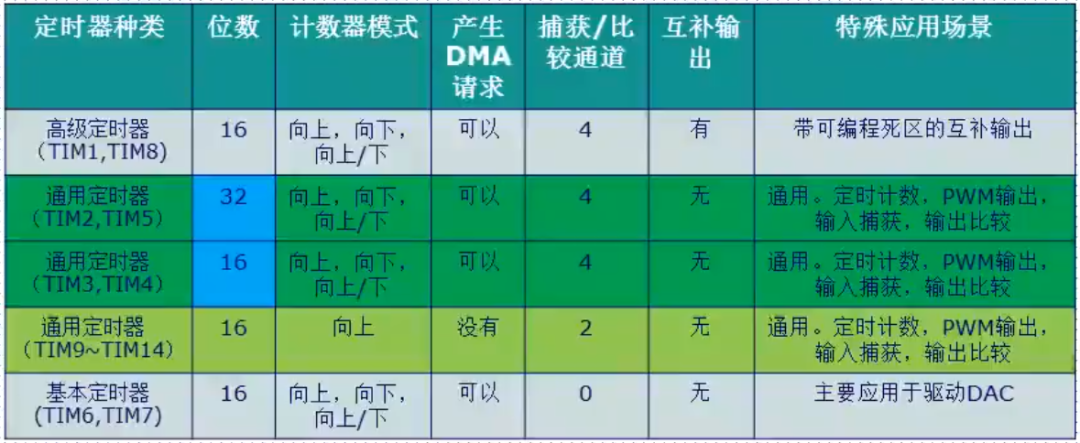

STM32定時(shí)器分類眾多,按照內(nèi)核、外核標(biāo)準(zhǔn)分為兩部分:核內(nèi)定時(shí)器+核外定時(shí)器

2023-07-21 14:51:12 2486

2486

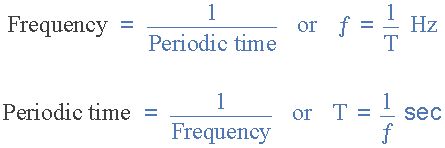

在電子電路中,我們經(jīng)常需要產(chǎn)生一些不同類型、不同形狀或不同頻率的波形做為信號(hào)波形,如正弦波、方波、矩形波、三角波、鋸齒波等等。這些波形通常會(huì)被用于時(shí)鐘信號(hào)、觸發(fā)脈沖、定時(shí)信號(hào)等等。

2023-07-20 15:06:30 14809

14809

定時(shí)分辨率的波形。 大20 Vp-p振輸幅出,至50 Ω負(fù)載(AFG3011) 通過(guò)創(chuàng)建高振幅信號(hào)節(jié)省成本和設(shè)置時(shí)間,無(wú)需使用外

2023-07-12 11:13:27 208

208

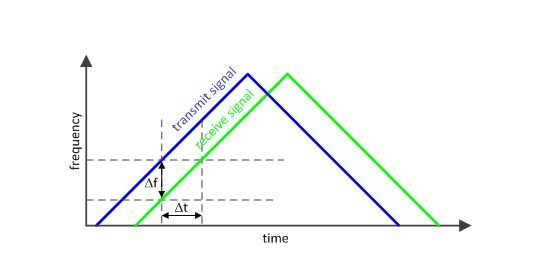

本實(shí)驗(yàn)活動(dòng)介紹鎖相環(huán)(PLL)。PLL電路有一些重要的應(yīng)用,例如信號(hào)調(diào)制/解調(diào)(主要是頻率和相位調(diào)制)、同步、時(shí)鐘和數(shù)據(jù)恢復(fù),以及倍頻和頻率合成。在這項(xiàng)實(shí)驗(yàn)中,您將建立一個(gè)簡(jiǎn)單的PLL電路,讓您對(duì)PLL操作有基本的了解。

2023-07-10 10:22:24 794

794

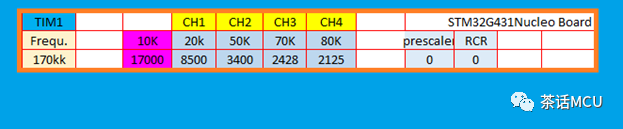

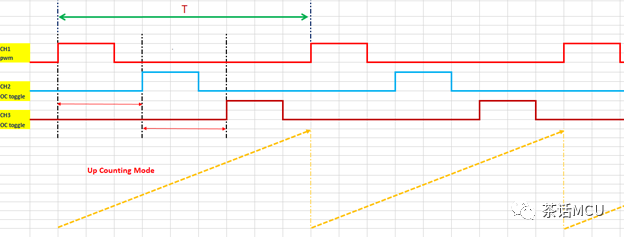

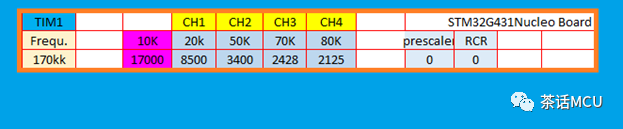

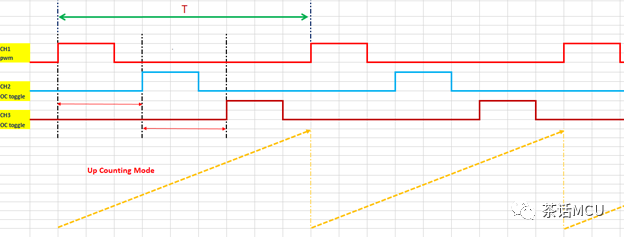

一般來(lái)講,一個(gè)STM32定時(shí)器輸出基于同一頻率的各路信號(hào)比較方便。但經(jīng)常也會(huì)有人問(wèn)使用STM32一個(gè)定時(shí)器是否可以實(shí)現(xiàn)多路不同頻率的輸出。

2023-07-06 15:57:42 1101

1101

有人想實(shí)現(xiàn)下面的PWM輸出波形,三路頻率相同,占空比同步可調(diào),且三路輸出波形時(shí)差固定為T(mén)/3。

2023-07-06 15:22:41 1022

1022

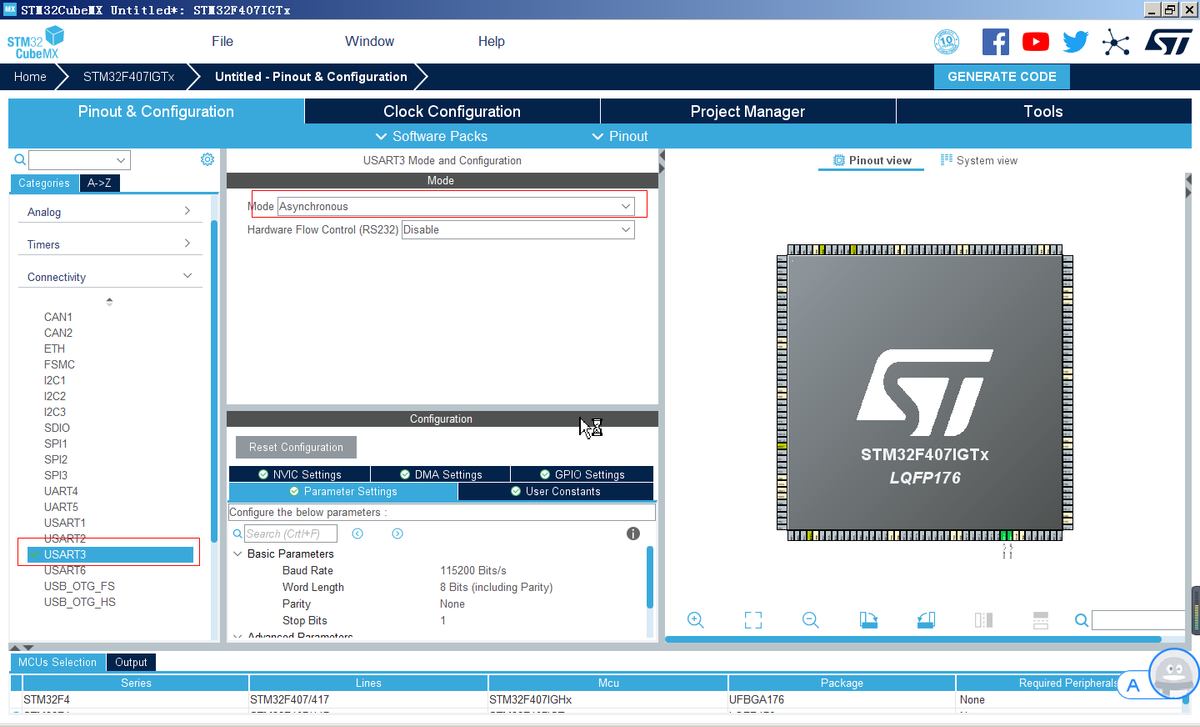

介紹STM32F407定時(shí)器PWM波形輸出配置方式。 通過(guò)邏輯分析采集波形數(shù)據(jù)進(jìn)行可視化顯示對(duì)比。

2023-07-06 14:33:48 2959

2959

PLL(AT16LPLL0000MP4P1G18V1A) 數(shù)據(jù)表模擬 PLL 倍頻

2023-07-05 19:47:36 0

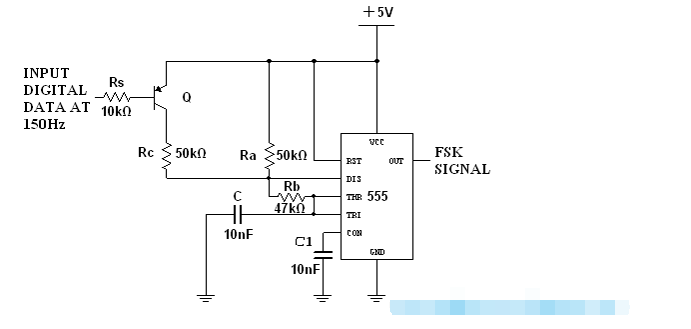

0 之間偏移,因此它被命名為頻移Keying.Today我們將看到使用FSK信令技術(shù)的ICNE555和PLL565的無(wú)線調(diào)制解調(diào)器的簡(jiǎn)單設(shè)計(jì)設(shè)計(jì)。對(duì)于電子專業(yè)的學(xué)生來(lái)說(shuō),這確實(shí)是一個(gè)值得做的迷你項(xiàng)目,甚至在

2023-07-03 10:41:44 487

487

頻率的產(chǎn)生有兩種方法:DDS和PLL,但是為什么射頻工程師一般用PLL多,很少用DDS呢?

2023-06-28 09:38:48 1823

1823

使用的官方代碼,發(fā)現(xiàn)串口0用定時(shí)器3時(shí)能進(jìn)入中斷一切都正常,用定時(shí)器1時(shí)一直沒(méi)進(jìn)入中斷,而且發(fā)現(xiàn)在發(fā)送數(shù)據(jù)時(shí)會(huì)進(jìn)入死循環(huán)等待,代碼已給出,中斷服務(wù)程序都一樣不列出來(lái)了唯一不同就是串口初始化看圖片

2023-06-15 08:25:25

MAXQ微控制器中的定時(shí)器B可以提供不同的PWM波形,這取決于TBC和TBR寄存器的相對(duì)值以及DCEN位的狀態(tài)。定時(shí)器 B 將在有或沒(méi)有比較寄存器待定的情況下工作。表1和表2分別總結(jié)了不帶TBC比較

2023-06-13 16:30:40 440

440

本文以SoC中的PLL為例,對(duì)PLL電路進(jìn)行設(shè)計(jì)和仿真。

2023-06-02 15:25:44 4438

4438

我目前正在嘗試按照這些說(shuō)明進(jìn)行操作:目標(biāo)是使用 D1 卡創(chuàng)建計(jì)數(shù)燈。在插入電路板并看到端口出現(xiàn)之前,一切都與結(jié)構(gòu)順利進(jìn)行。我可以插入卡,藍(lán)燈閃爍,然后……什么都沒(méi)有。沒(méi)有端口出現(xiàn)。我沒(méi)有安裝驅(qū)動(dòng)程序

2023-06-01 10:57:44

(PLM) 的電路板原理圖,一切正常,但在線工具提供了有源負(fù)載調(diào)制 (ALM) 設(shè)計(jì)的計(jì)算,因此我們要仔細(xì)檢查是否一切正常。

附件是兩個(gè)設(shè)計(jì),名為“Card”和“Ring”。兩者都有自己的定制天線

2023-06-01 06:17:45

模式以產(chǎn)生的脈寬調(diào)制波**,能夠使輸出電流波形盡可能接近于理想的正弦波形。SVPWM與傳統(tǒng)的正弦PWM不同,它是從三相輸出電壓的整體效果出發(fā),著眼于如何使電機(jī)獲得理想圓形磁鏈軌跡。

2023-05-29 17:09:52 3985

3985

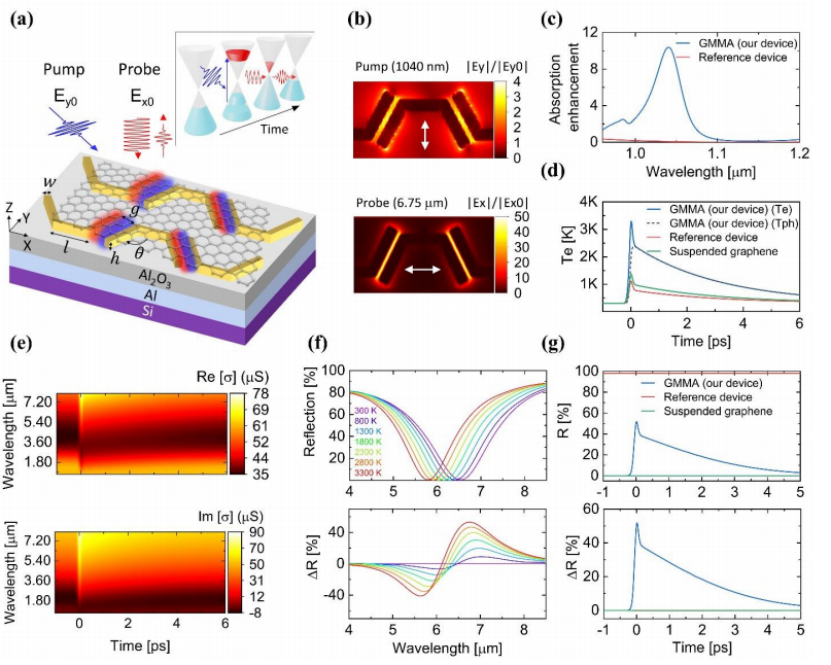

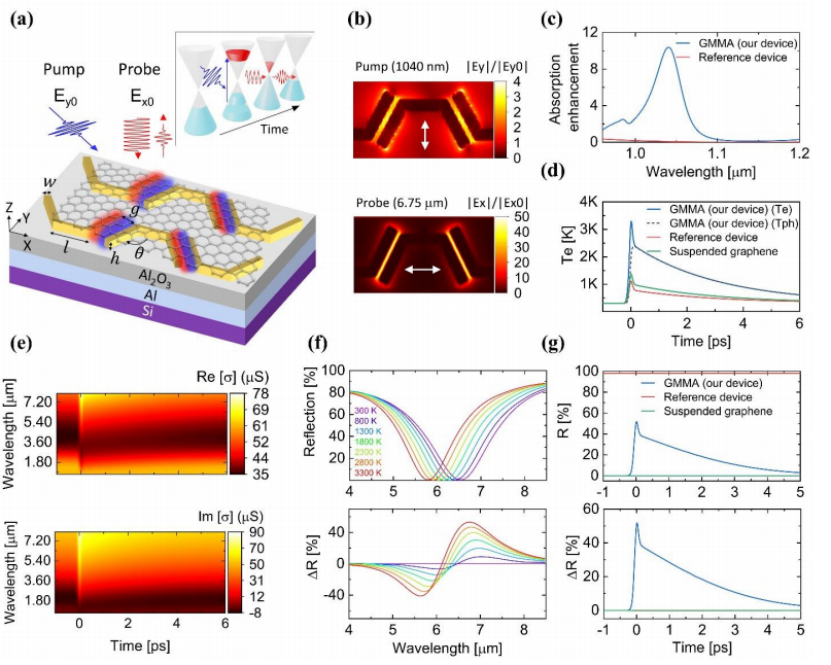

高速光調(diào)制是許多應(yīng)用的重要組成部分,在光互連、超快分子光譜、材料處理、光學(xué)信息處理和計(jì)算等領(lǐng)域中有著廣泛的應(yīng)用。與基于熱、磁、聲、機(jī)械和電效應(yīng)的其他技術(shù)相比,全光調(diào)制能夠?qū)崿F(xiàn)最高可達(dá)太赫茲的調(diào)制帶寬。

2023-05-29 14:39:47 330

330

特征:雙通道,60 MHz 正弦波,30 MHz 方波14 位,300 MS/s 任意波形,1 M 點(diǎn)記錄長(zhǎng)度幅度 1 mVp-p 至 10 Vp-p 至 50 Ω 負(fù)載連續(xù)、掃描、突發(fā)和調(diào)制模式

2023-05-25 17:49:03

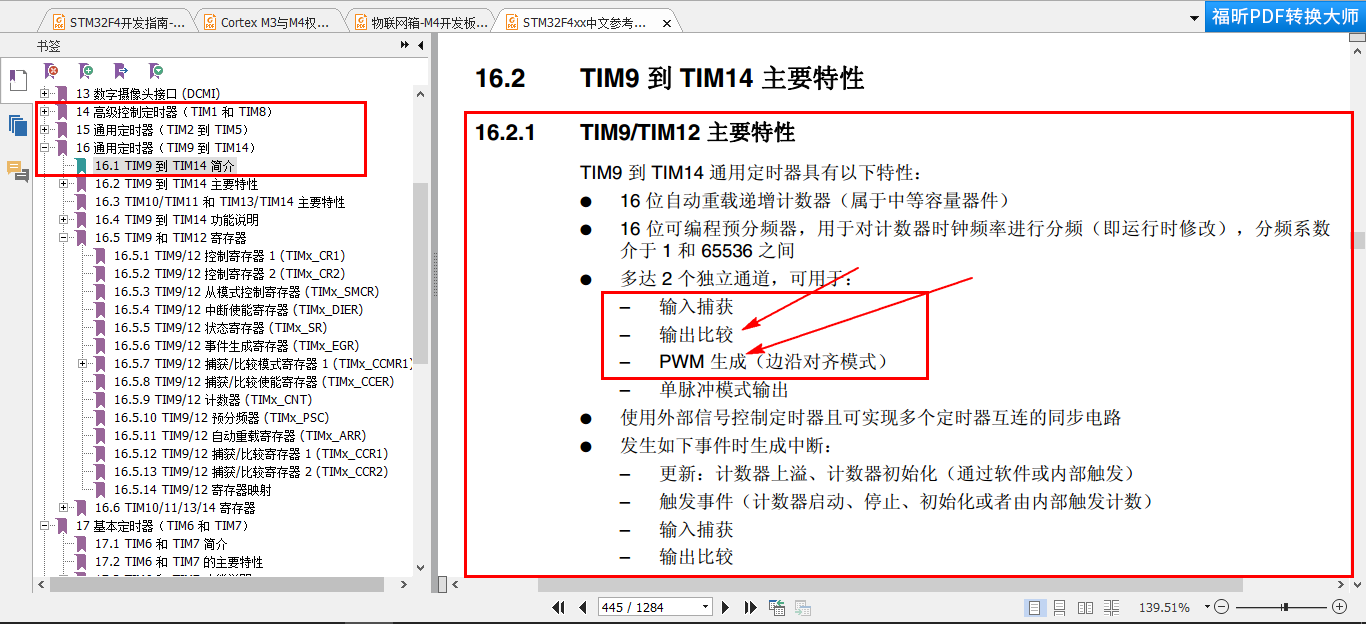

這一課我們將介紹CKS32F4XX系列產(chǎn)品的定時(shí)器使用,CKS32F4XX的定時(shí)器功能十分強(qiáng)大,包含2個(gè)高級(jí)控制定時(shí)器,8個(gè)普通定時(shí)器,2個(gè)基礎(chǔ)定時(shí)器,以及兩個(gè)看門(mén)狗定時(shí)器和一個(gè)系統(tǒng)定時(shí)器,總共15個(gè)定時(shí)器之多。關(guān)于定時(shí)器部分內(nèi)容的講解我們將分3個(gè)部分展開(kāi),本節(jié)將介紹定時(shí)器的基本特征和定時(shí)操作。

2023-05-19 09:18:50 506

506

測(cè)量和補(bǔ)償大氣壓力。我還包括一個(gè)分壓器來(lái)測(cè)量電池電壓。一切都通過(guò)使用 2 x 9,900 mah 18650 電池的 ESP07 進(jìn)行控制。ESP07 進(jìn)入深度睡眠 30 分鐘,然后醒來(lái)讀取讀數(shù),然后

2023-05-11 08:27:49

(spatial modulation)是空間域中的代表性IM技術(shù),如圖2所示,空間調(diào)制的索引資源是天線索引,其中X代表的是調(diào)制符號(hào),藍(lán)色部分代表的是當(dāng)前激活的天線。SM由于每個(gè)傳輸時(shí)隙只有一根天線被激活

2023-05-10 16:44:58

本帖最后由 jf_94210865 于 2023-5-9 12:11 編輯

一個(gè)很簡(jiǎn)單的問(wèn)題,如何創(chuàng)建波形圖X軸的局部變量?

我正在編寫(xiě)一個(gè)列車(chē)模擬運(yùn)行程序,用到了波形圖,現(xiàn)在需要導(dǎo)入一段線路

2023-05-09 12:06:21

555定時(shí)振蕩器也就是通常所說(shuō)的 555定時(shí)器 。 555定時(shí)器的用途非常廣泛,可以 生成各種類型的脈沖 、 創(chuàng)建時(shí)間延遲 ,也可以用于 脈沖寬度調(diào)制(PWM) ,555定時(shí)器最常見(jiàn)的用途是為電路產(chǎn)生時(shí)鐘信號(hào)。

2023-05-09 09:18:38 3664

3664

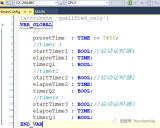

定時(shí)器指令存放在函數(shù)庫(kù):Tc2_Standard,在新項(xiàng)目創(chuàng)建時(shí)會(huì)自動(dòng)加載。我在之前的文章中多次介紹過(guò)IEC定時(shí)器,比如【西門(mén)子SCL編程入門(mén)教程連載(7)-定時(shí)器指令】,今天這篇文章,我們?cè)诒陡C3編程環(huán)境下再次學(xué)習(xí)IEC定時(shí)器的使用。

2023-05-04 16:00:38 1839

1839

本文將介紹通過(guò)定時(shí)器的輸出比較功能實(shí)現(xiàn)脈寬可調(diào)的輸出波形來(lái)控制LED等,實(shí)現(xiàn)呼吸燈的效果。

2023-05-01 09:03:00 638

638

本設(shè)計(jì)理念描述了一種從基于555的自由運(yùn)行振蕩器產(chǎn)生可變占空比波形的新方法。該電路的寬調(diào)制范圍、對(duì)寬占空比值范圍內(nèi)的高度線性控制以及出色的線性度使其成為基于 PWM(脈寬調(diào)制)的控制應(yīng)用的理想選擇。

2023-04-29 16:40:00 301

301

setitimer() 創(chuàng)建一個(gè)間隔式定時(shí)器,這種定時(shí)器會(huì)在未來(lái)某個(gè)時(shí)間點(diǎn)到期,并于此后(可選擇地)每間隔一段時(shí)間到期一次

2023-04-27 15:29:33 1294

1294

一切從用戶需求出發(fā),一切為了用戶的智慧家庭生活體驗(yàn)。

2023-04-25 13:35:45 342

342 ?

疑問(wèn)2:PLL是不是可以生成指定的某一點(diǎn)頻率呢? 生成的范圍由什么決定啊?

疑問(wèn)3::大家平時(shí)說(shuō)的PLL失鎖了,失鎖的是指頻率還是相位啊?平時(shí)調(diào)試電路的時(shí)候怎么判斷是否失鎖了?平時(shí)調(diào)試電路的時(shí)候怎么確定是否已經(jīng)鎖定了?

2023-04-24 09:46:09

,PCIe4 支持 Gen3,PCIe1、2 和 3 也都映射到 PLL1。 根據(jù) 19.4.2 SerDesxPLLnCR0 部分,DLYDIV_SEL 必須設(shè)置為 01 以啟用 FRATE_SEL/16

2023-04-18 08:25:33

PCB設(shè)計(jì)和PCB制造的一切。 LED PCB有哪些類型? 有不同類型的LED pcb。LED PCB板的類型根據(jù)制造規(guī)格、材料類型和用途而有所不同。以下是最流行的LED pcb類型包括

2023-04-17 15:07:14

我注意到 Freemaster 和處理器通信存在問(wèn)題。如果處理器無(wú)法響應(yīng) Freemaster 查詢,一切都會(huì)凍結(jié)。這個(gè)問(wèn)題不是每次都會(huì)發(fā)生。我想當(dāng)我們?cè)谔幚砥鬓D(zhuǎn)到 CAN_TX 時(shí)斷開(kāi)電纜時(shí)會(huì)

2023-04-17 06:36:01

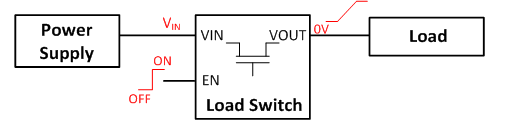

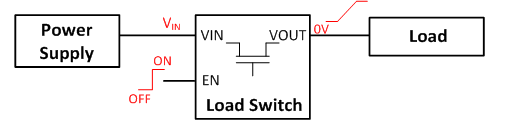

對(duì)于一個(gè)終端用戶來(lái)說(shuō),打開(kāi)一個(gè)電子設(shè)備很簡(jiǎn)單;只需按下按鈕就可以了。然而,需要花費(fèi)大量的精力來(lái)創(chuàng)建一個(gè)平滑順暢的加電體驗(yàn)。系統(tǒng)接通的過(guò)快將會(huì)導(dǎo)致由不可控的涌入電流大尖峰所引起的電源故障。對(duì)于那些

2023-04-15 10:27:33 616

616

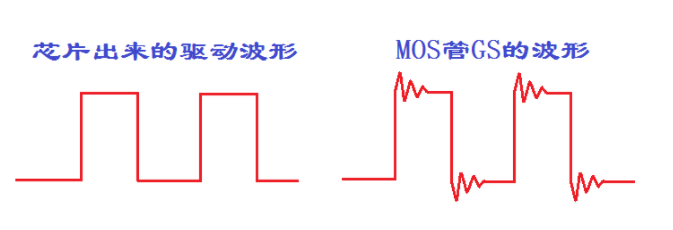

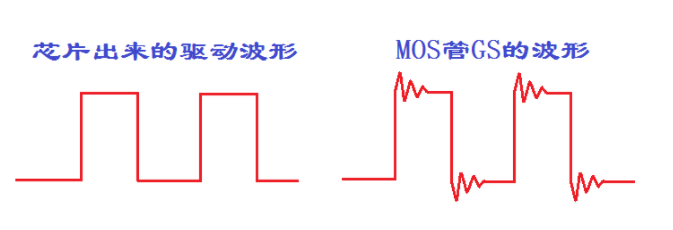

對(duì)于咱們電源工程師來(lái)講,我們很多時(shí)候都在看波形,看輸入波形,MOS開(kāi)關(guān)波形,電流波形,輸出二極管波形,芯片波形,MOS管的GS波形,我們拿開(kāi)關(guān)GS波形為例來(lái)聊一下GS的波形。

2023-04-10 09:42:00 1673

1673

PLL1708 3.3 V DUAL PLL MULTI-CLO

2023-04-06 17:07:21

鎖相環(huán) IP 核是由鎖相環(huán)(PLL)電路實(shí)現(xiàn)。鎖相環(huán)是一種反饋控制系統(tǒng),它可以自動(dòng)調(diào)整本地產(chǎn)生的信號(hào)的相位,以匹配輸入信號(hào)的相位。鎖相環(huán)通過(guò)振蕩器產(chǎn)生的波形的相位匹配輸入信號(hào)的相位來(lái)工作。輸入信號(hào)的微小

2023-04-06 16:04:21

頻變占空比PWM調(diào)制的情況。 穩(wěn)態(tài)下的PWM,電感電流,和輸出電容(包含ESR和ESL)各部分電壓的細(xì)節(jié)波形如下。 通過(guò)觀察得到兩個(gè)結(jié)論: PWM從低變高恰對(duì)應(yīng)電感電流iL上升時(shí)刻,從高變低恰

2023-03-23 14:41:06

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論