中微公司的電感耦合等離子體(ICP)刻蝕設備Primo nanova系列第500臺反應腔順利付運國內一家先進的半導體芯片制造商。

2024-03-21 15:12:43 99

99 本文目錄晶體管和晶振什么區別有源晶振引腳怎么定義的有源晶振有分極性嗎什么是有源晶振,有何作用51單片機的晶振是有源還是無源有源晶體和無源晶體怎么區分晶體管和晶振什么區別晶體管和晶振的區別是晶體管可以

2024-03-12 14:23:48 68

68

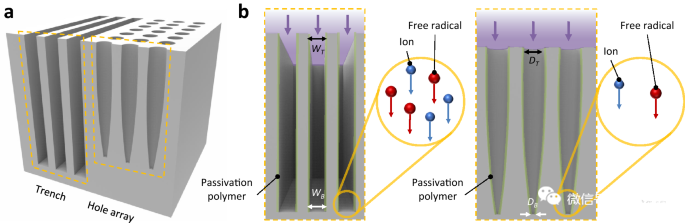

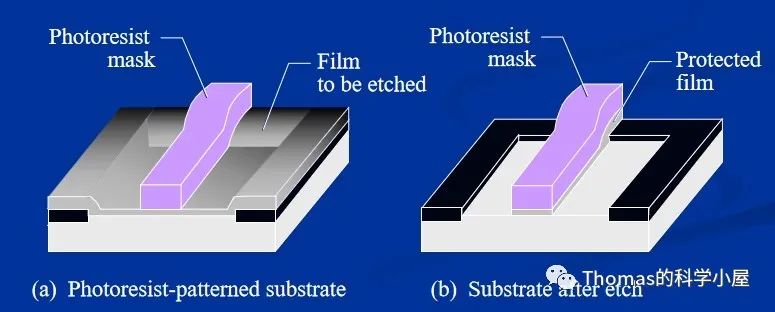

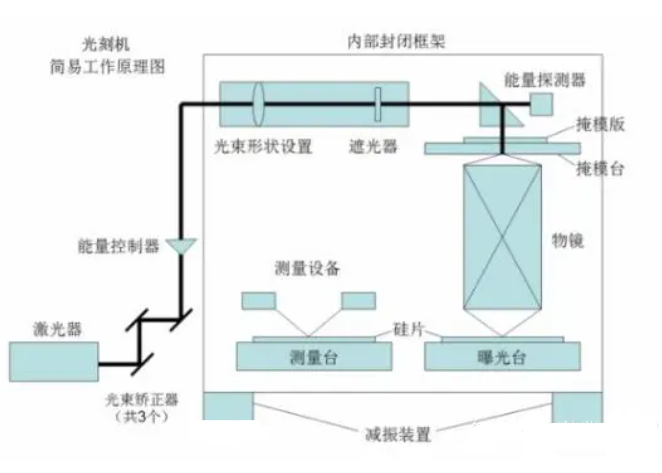

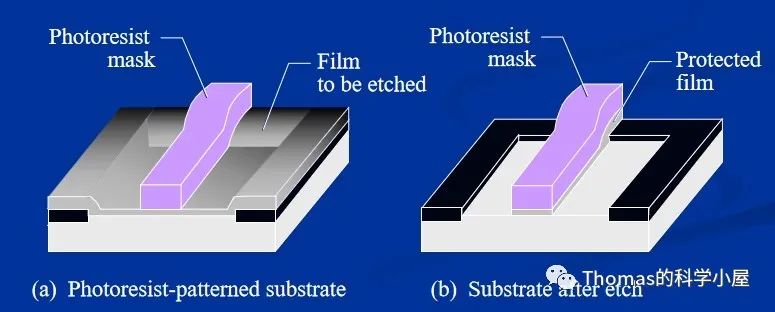

刻蝕機的刻蝕過程和傳統的雕刻類似,先用光刻技術將圖形形狀和尺寸制成掩膜,再將掩膜與待加工物料模組裝好,將樣品置于刻蝕室內,通過化學腐蝕或物理磨蝕等方式將待加工物料表面的非掩膜區域刻蝕掉,以得到所需的凹槽和溝槽。

2024-03-11 15:38:24 461

461

集成電路是通過一系列特定的平面制造工藝,將晶體管、二極管等有源器件和電阻、電容等無源器件,按照一定的電路互連關系,“集成”在一塊半導體單晶片上,并封裝在一個保護外殼內,能執行特定的功能復雜電子系統。

2024-02-29 15:01:19 182

182

請問官方是否測試過CX3的實際傳輸速率?最高可以到多少啊?

2024-02-29 07:48:58

MIPI CS2 input timing和CX3 mipi interface configuration 的關系是什么?

CX3 mipi interface configuration中的值設置成什么是合理的?

2024-02-29 07:25:02

Cx3開發板(s)I2C最大速率可以設置到1MHz嗎?當前接口CyU3PMipicsiInitializeI2c 最大只能400K,有沒有其他接口實現提速的?

2024-02-28 06:10:09

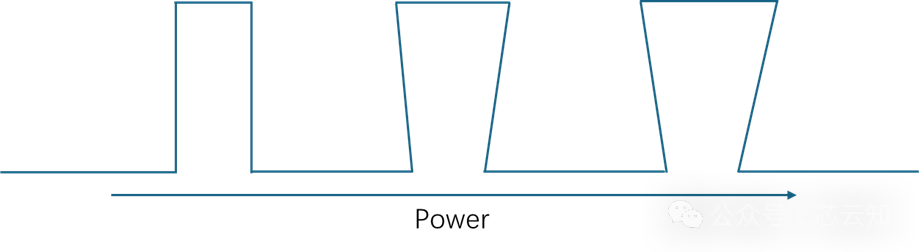

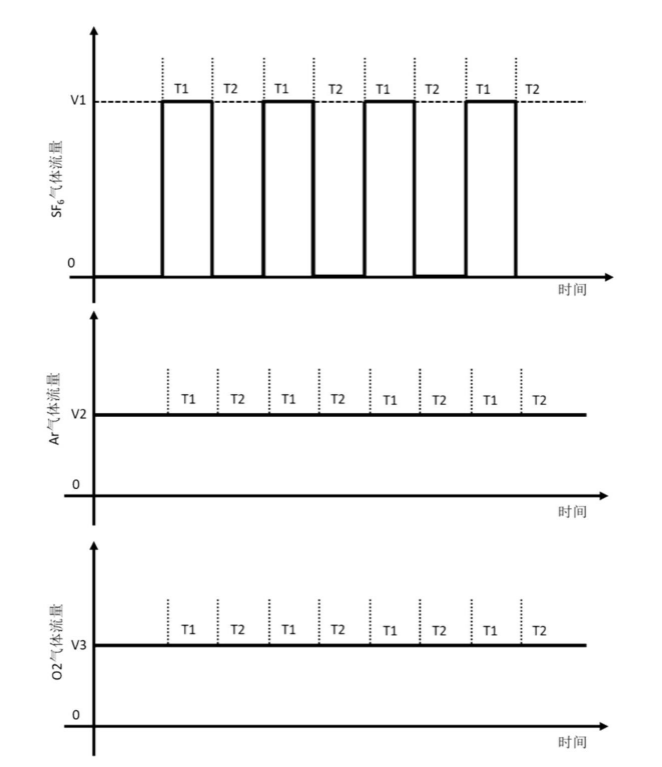

影響深硅刻蝕的關鍵參數有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:44:39 283

283

影響深硅刻蝕的關鍵參數有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:40:16 19

19

IGBT的柵極電壓與管子允許的短路時間是什么關系? IGBT是一種集成了晶體管和MOSFET技術的功率電子器件。它的主要功能是將低電平信號轉換為高電壓、高電流能力的輸出信號。在工業控制和電源

2024-02-20 11:00:57 205

205 檢查晶體管的靜態工作點偏置是否處于放大區域。通過測量和計算晶體管的集電極電壓(或源極電壓)和基極電壓之間的關系,可以確定其所處的工作區域。

2024-02-05 15:26:20 545

545 在半導體加工工藝中,常聽到的兩個詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現,有著千絲萬縷的聯系,這一節介紹半導體刻蝕工藝。

2024-01-26 10:01:58 548

548

晶振電路中為什么并上電阻?你知道晶振和電阻的關系嗎?電路中為什么常常要再晶振的旁邊多加一個電阻呢?能起到什么作用? 晶振電路中為什么要并聯電阻?晶振和電阻的關系是什么?為什么常常要在晶振旁邊

2024-01-24 15:26:00 404

404 ,則分析時則按照單獨的晶體管電路分析,與一般晶體管電路無差。

如果多發射極或多集電極的電路在非多極的一側全部短起來當作一個晶體管,那么此時的關系可以看作一個或門的關系,只要有一路導通,則晶體管就實現

2024-01-21 13:47:56

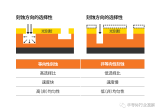

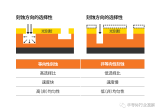

干法刻蝕技術是一種在大氣或真空條件下進行的刻蝕過程,通常使用氣體中的離子或化學物質來去除材料表面的部分,通過掩膜和刻蝕參數的調控,可以實現各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結構

2024-01-20 10:24:56 1106

1106

設備和技術來實現圖形的微縮與先進技術的開發。隨著半導體器件尺寸縮減、工藝復雜程度提升,制造工藝中刻蝕工藝波動的影響將變得明顯。刻蝕終點探測用于確定刻蝕工藝是否完成、且沒有剩余材料可供刻蝕。這類終點探測有助于最大限度地減少刻蝕速率波動的影響。 刻蝕終點探測需要在刻蝕工藝中進

2024-01-19 16:02:42 128

128

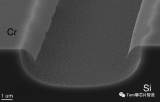

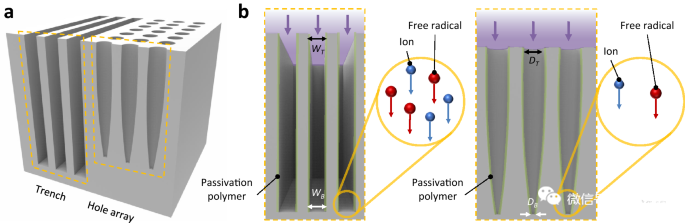

對DRIE刻蝕,是基于氟基氣體的高深寬比硅刻蝕技術。與RIE刻蝕原理相同,利用硅的各向異性,通過化學作用和物理作用進行刻蝕。不同之處在于,兩個射頻源:將等離子的產生和自偏壓的產生分離

2024-01-14 14:11:59 511

511

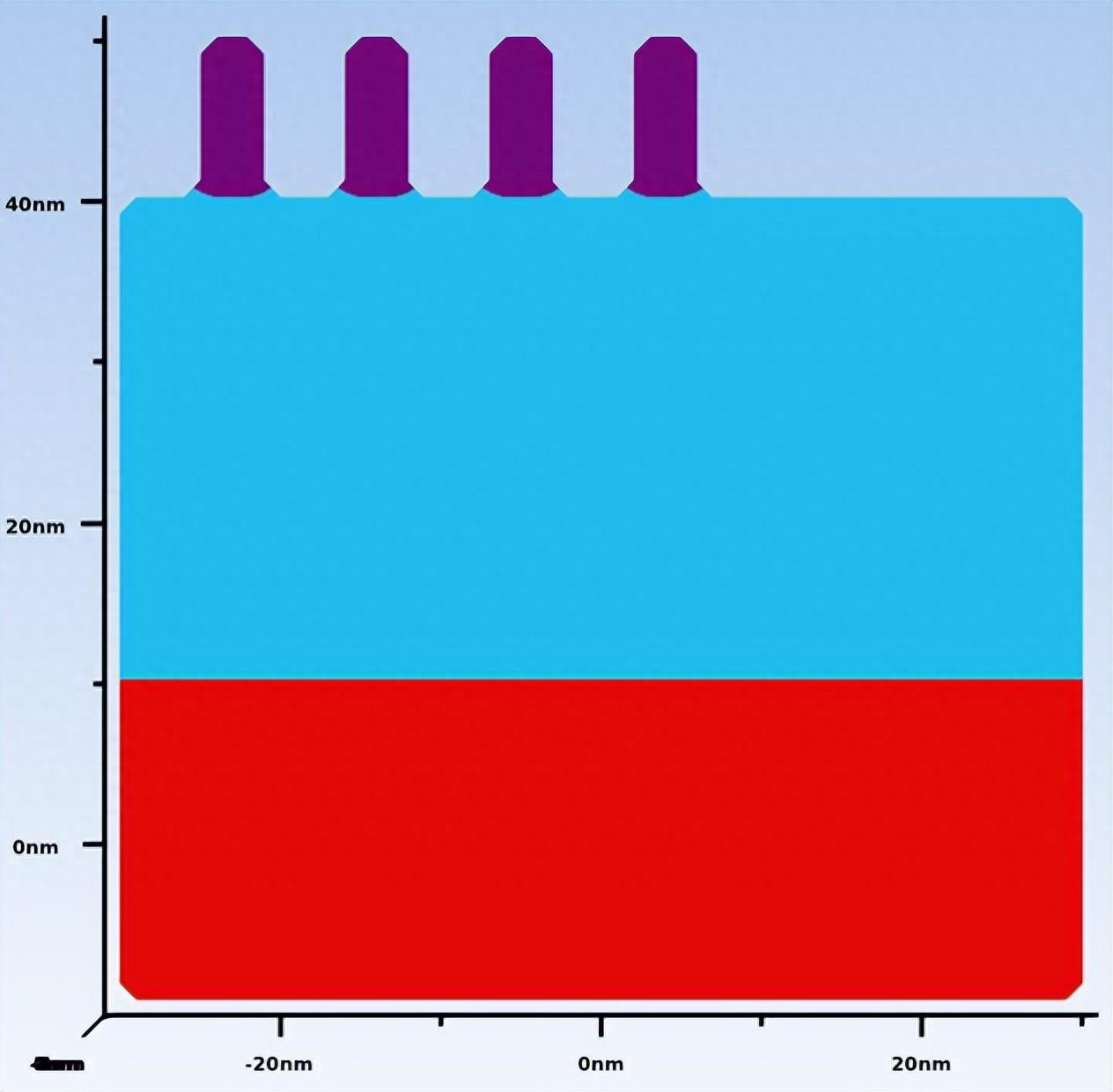

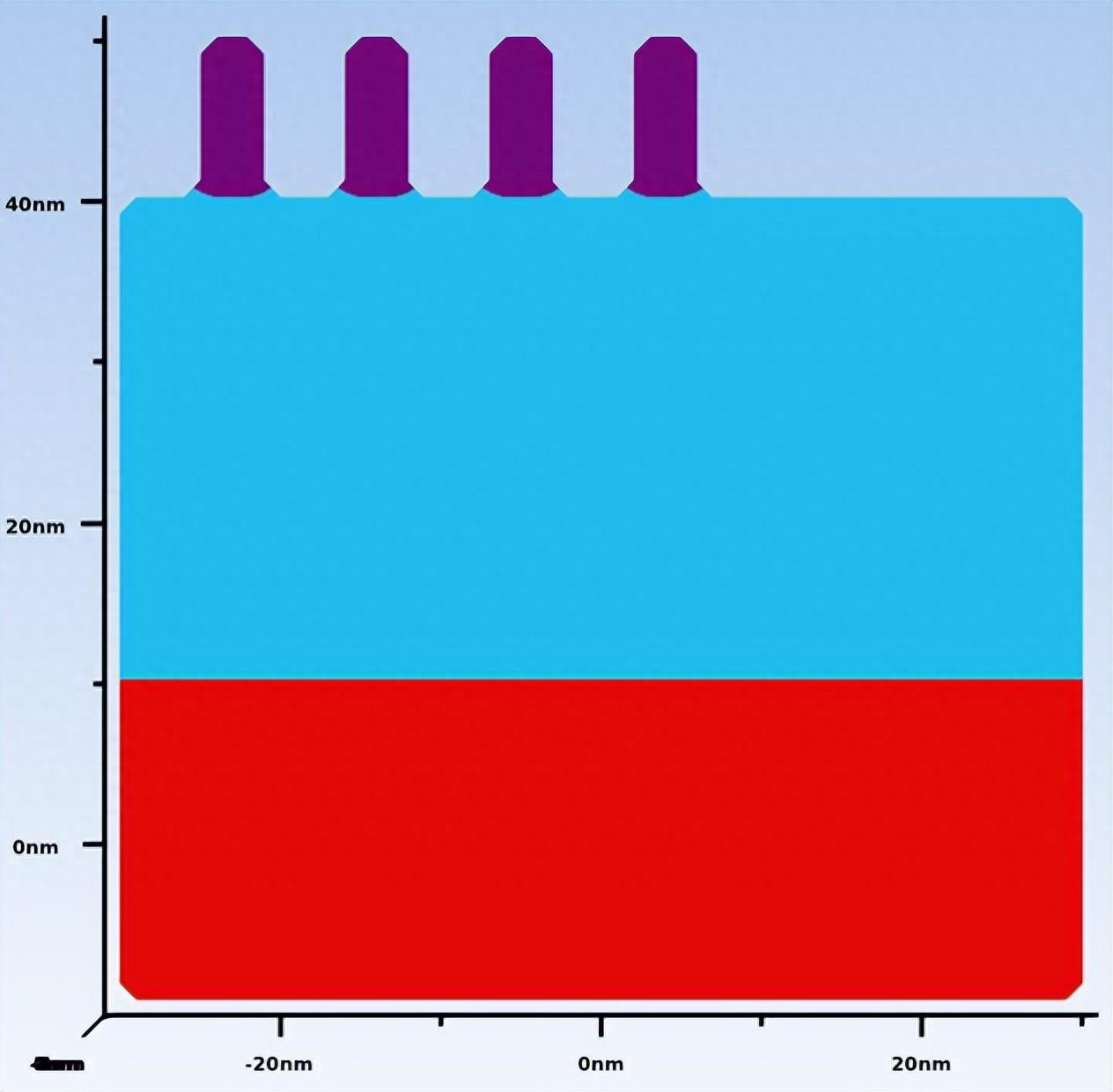

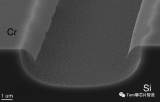

在紅外探測器的制造技術中,臺面刻蝕是完成器件電學隔離的必要環節。

2024-01-08 10:11:01 206

206

)設計原理圖ADI參與評審 ;2)芯片滿串使用 ; 3)批次指向性很明顯,2142周號基本上做試驗必然燒蝕板子;原理圖設計如下:

板子燒蝕嚴重;使用這種內部MOS進行被動均衡,此問題會一直存在,沒有妥善的解決方案,

2024-01-03 06:39:42

高速率光模塊可以用在低速率端口交換機上嗎? 隨著網絡技術的迅猛發展,高速率光模塊作為現代網絡中重要的組成部分之一,為數據傳輸提供了高速、高效、穩定的解決方案。但是,是否可以將高速率光模塊應用于低速率

2023-12-27 11:28:03 192

192 光模塊速率有哪些?怎么看?如何選擇? 光模塊速率是指光纖通信系統中使用的光學模塊傳輸數據的速率。光模塊的速率通常用Gbps(每秒十億個比特)或bps(每秒比特)來表示。不同的應用場景和需求決定

2023-12-27 11:13:48 734

734 晶體管是一種半導體器件,用于放大電信號、開關電路和邏輯運算等。它是現代電子技術和計算機科學的核心之一。在晶體管中,有三個電極:基極、發射極和集電極。這三個電極的電壓之間的關系對于理解晶體管的工作原理

2023-12-20 14:50:49 1201

1201 如題

AD9527 時鐘頻率范圍和轉換速率之間的明確關系?

時鐘輸入頻率和功耗是否有關系?

2023-12-20 08:11:59

采樣速率和輸出速率有什么關系,在ad9625的datasheet中沒有標明輸出速率,怎么樣確定它的輸出速率

2023-12-20 07:16:30

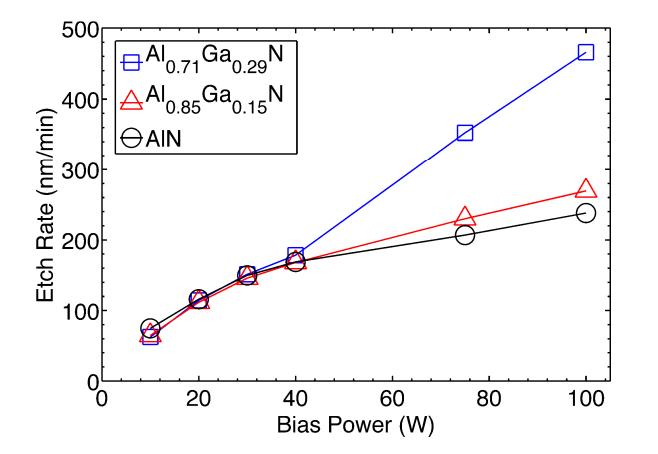

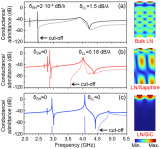

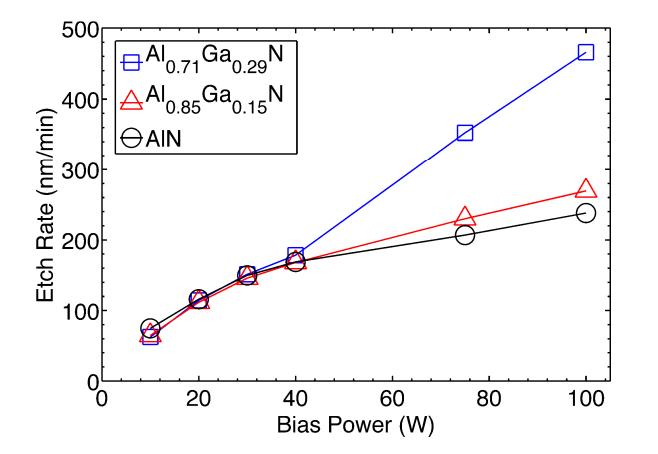

眾所周知,化合物半導體中不同的原子比對材料的蝕刻特性有很大的影響。為了對蝕刻速率和表面形態的精確控制,通過使用低至25nm的薄器件阻擋層的,從而增加了制造的復雜性。本研究對比了三氯化硼與氯氣的偏置功率,以及氣體比對等離子體腐蝕高鋁含量AlGaN與AlN在蝕刻速率、選擇性和表面形貌方面的影響。

2023-12-15 14:28:30 227

227

AD9163的時鐘輸入范圍多大,輸入時鐘大小與輸入數據速率是什么關系?

2023-12-08 08:20:20

晶體和非晶體的區別? 晶體和非晶體是固體材料的兩種基本結構形態。晶體由具有規則排列的原子、離子或分子組成,而非晶體則是由無規則排列的原子、離子或分子組成。晶體和非晶體之間存在著許多顯著的差異,包括

2023-12-07 17:03:39 1705

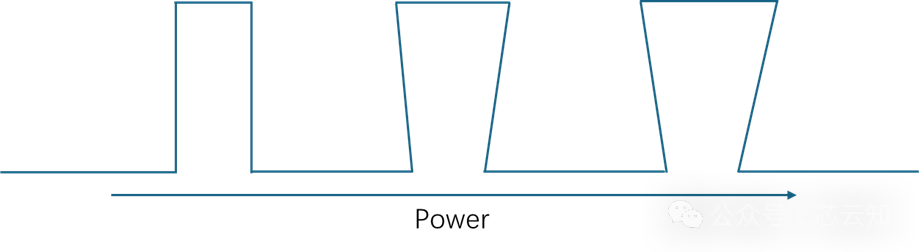

1705 該專利詳細闡述了一種針對含硅有機介電層的高效刻蝕方法及相應的半導體工藝設備。它主要涉及到通過交替運用至少兩個刻蝕步驟來刻蝕含硅有機介電層。這兩個步驟分別為第一刻蝕步驟和第二刻蝕步驟。

2023-12-06 11:58:16 370

370

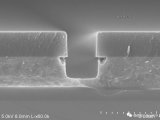

W刻蝕工藝中使用SF6作為主刻步氣體,并通過加入N2以增加對光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負載效應,避免產生凹坑,并使用對TiN有高選擇比的化學氣體進行刻蝕。

2023-12-06 09:38:53 1536

1536 在網上看見說轉換速率應該是帶寬的兩倍,但沒有看到轉換速率與輸出頻率的關系啊,而這個帶寬是指的從零頻率開始的帶寬嗎?轉換的位數是不是只與信號的大小有關啊,位數低的對于小信號的量化會出現問題是嗎。求各位大佬指導指導。

2023-12-01 07:08:08

半導體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創建所需圖形

2023-11-27 16:54:26 256

256

濕法刻蝕由于成本低、操作簡單和一些特殊應用,所以它依舊普遍。

2023-11-27 10:20:17 452

452

來至網友的提問:如何選擇分立晶體管?

2023-11-24 08:16:54

電子發燒友網站提供《晶體管混合π型參數與Y參數的關系.rar》資料免費下載

2023-11-20 09:57:21 0

0 鉛酸電池的放電速率和使用有何關系? 鉛酸電池是一種常見的蓄電池,廣泛用于汽車、UPS電源等領域。它的放電速率與使用有密切關系,下面我將詳細介紹。 一、鉛酸電池的工作原理 鉛酸電池是一種化學電池

2023-11-17 11:41:33 519

519 人工智能(AI)是預計到2030年將成為價值數萬億美元產業的關鍵驅動力,它對半導體性能提出了新的要求。在交付下一代AI能力方面,一些最復雜的問題來自于需要通過新的刻蝕技術來解決的器件制造挑戰。

2023-11-16 16:03:02 164

164 ~250.0uSF: 輸入 12V 直流 G: 退壓式電光調 QH: 適用低重頻率調 Q 晶體 I: 自帶高穩定高壓電源二 應用范圍A:KD*P B:LiNbO3 C:其它三

2023-10-24 15:35:18

什么是數字濾波器的采樣速率?和輸入信號的頻率有什么關系? 數字濾波器的采樣速率是指數字濾波器輸入信號的采樣頻率,也稱為采樣率,通常用赫茲(Hz)表示。在數字信號處理中,為了實現對模擬信號的數字化

2023-10-20 15:02:30 1383

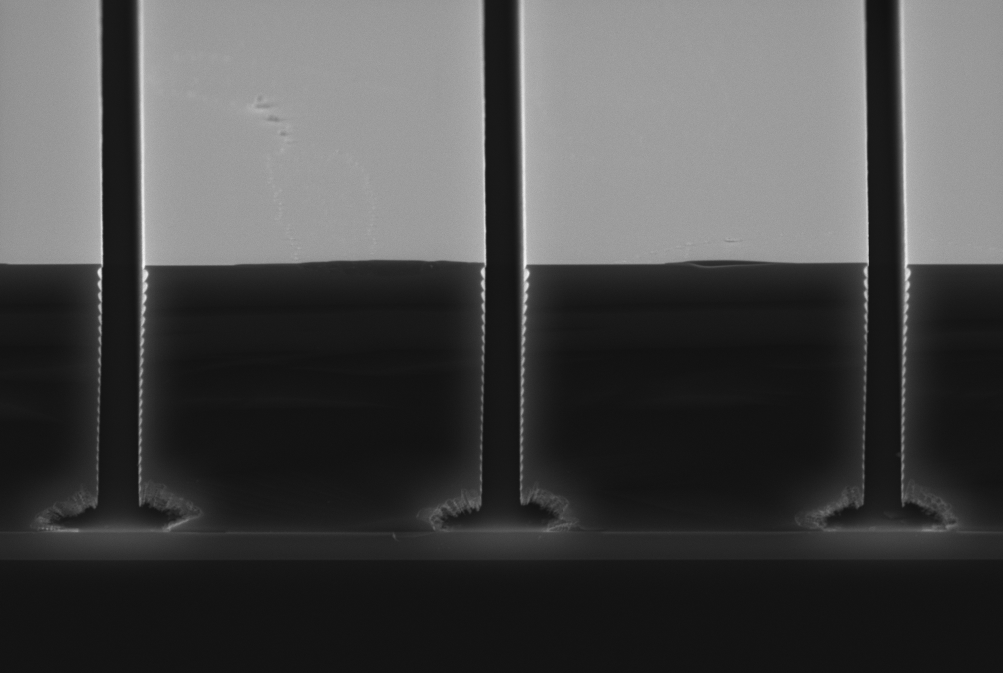

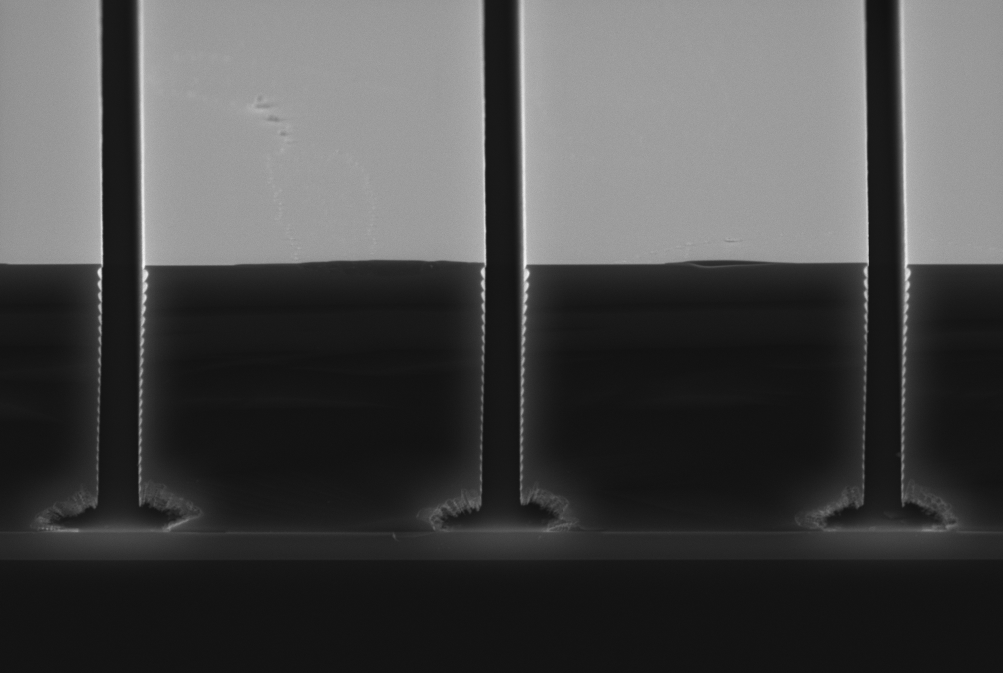

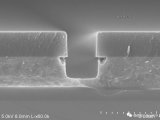

1383 但是,在刻蝕SOI襯底時,通常會發生一種凹槽效應,導致刻蝕的形貌與預想的有很大出入。那么什么是凹槽效應?什么原因引起的?怎么抑制這種異常效應呢?

2023-10-20 11:04:21 454

454

實際樣品中,并不能直接觀察到不同的晶體學方向或晶面,只能看到晶粒的形貌。

2023-10-08 10:40:17 3039

3039

刻蝕(或蝕刻)是從晶圓表面去除特定區域的材料以形成相應微結構。但是,在目標材料被刻蝕時,通常伴隨著其他層或掩膜的刻蝕。

2023-10-07 14:19:25 2073

2073

有過深硅刻蝕的朋友經常會遇到這種情況:在一片晶圓上不同尺寸的孔或槽刻蝕速率是不同的。

2023-10-07 11:29:17 1447

1447

在半導體制造中,刻蝕工序是必不可少的環節。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術各有優勢,也各有一定的局限性,理解它們之間的差異是至關重要的。

2023-09-26 18:21:00 3305

3305

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-09-24 17:42:03 996

996

晶體振蕩器是一種電子振蕩器,使用石英晶體作為振蕩元件。石英晶體具有穩定的機械性質,當施加電場時,會以高精度的頻率振蕩。晶體振蕩器通過正確選擇和驅動石英晶體,可以產生非常精確且穩定的振蕩頻率。

2023-09-21 15:15:20 731

731 半導體工程裝備、北方華創的主要品種是刻蝕、薄膜、清洗、熱處理、晶體生長等核心技術裝備,廣泛應用邏輯部件,存儲半導體零部件、先進封裝、第三代半導體照明、微機電系統、新型顯示、新能源,襯底材料制造等工藝過程。

2023-09-18 09:47:19 578

578 孿晶是指兩個晶體(或一個晶體的兩部分)沿一個公共晶面(即特定取向關系)構成鏡面對稱的位向關系,這兩個晶體就稱為"孿晶",此公共晶面就稱孿晶面。

2023-09-15 10:31:43 3823

3823

取向(crystal orientation)、晶界取向差(grain boundary misorientations)、鑒別物相、以及局部晶體完整性等大量信息,并進一步推導出材料的力學性能和物理特性。

2023-09-15 10:29:04 1158

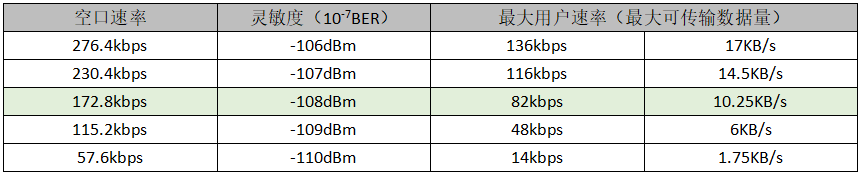

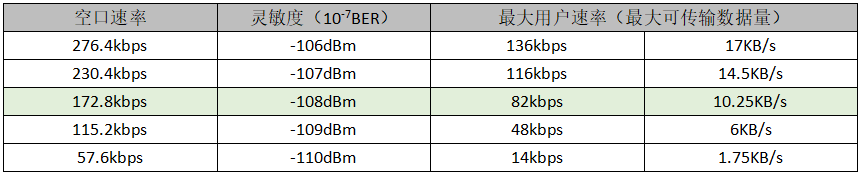

1158 在使用T900數傳模塊的過程中,會遇到空中速率和串口速率如何配置的問題。下面就談談自己的一些體會。

2023-09-11 10:35:45 600

600

濕法刻蝕由于精度較差,只適用于很粗糙的制程,但它還是有優點的,比如價格便宜,適合批量處理,酸槽里可以一次浸泡25張硅片,所以有些高校和實驗室,還在用濕法做器件,芯片廠里也會用濕法刻蝕來顯露表面缺陷(defect),腐蝕背面多晶硅。

2023-08-28 09:47:44 890

890

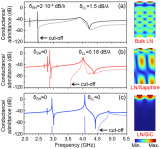

工作簡介 ????上海微系統所異質集成XOI課題組基于自主研制的高單晶質量6英寸LiNbO3/SiC壓電異質晶圓,開發了國際上首款基于單晶壓電薄膜異質集成襯底的5G N79頻段的高性能聲表面波

2023-08-28 09:22:43 960

960

晶體管的三個極的電壓關系 晶體管作為一種電子器件,是當今電子技術和通信領域中不可或缺的重要元件。晶體管的基本結構包括一個基極、一個發射極和一個集電極。它實現了一種對電流的控制,從而能夠實現電子設備

2023-08-25 15:35:20 5248

5248 晶體管和芯片的關系介紹 晶體管和芯片是現代電子技術中最重要的兩個概念,二者有密不可分的關系。晶體管是一種半導體材料制造的電子器件,而芯片則是晶體管等電子器件及相關電路的集成體。 一、晶體管 晶體

2023-08-25 15:29:37 2444

2444 晶體管和芯片的關系是什么? 晶體管和芯片是相互關聯的兩個概念,晶體管是芯片的核心組成部分之一。 晶體管是一種能夠控制電流的電子器件,由美國貝爾實驗室的William Shockley、John

2023-08-25 15:21:05 1513

1513 下圖(a)中的沉積塊狀層是必需的,這是為了SEG可以生長在設計的區域。下圖(c)顯示了KOH硅刻蝕,這種刻蝕對<111>晶體硅具有高的選擇性。

2023-08-25 09:50:40 1717

1717

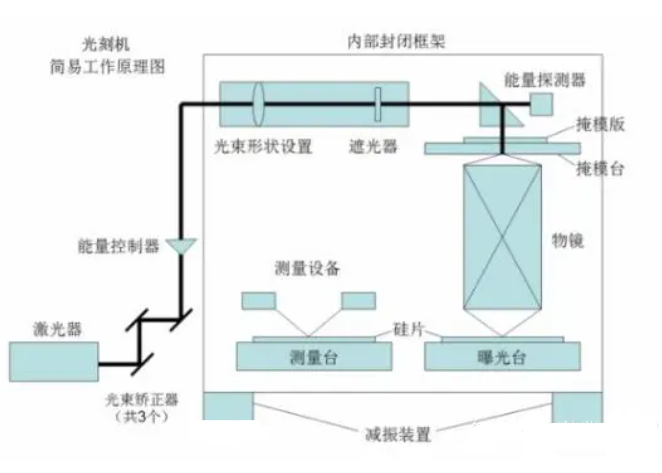

光刻蝕(Photolithography)是一種在微電子和光電子制造中常用的加工技術,用于制造微細結構和芯片元件。它的基本原理是利用光的化學和物理作用,通過光罩的設計和控制,將光影投射到光敏材料上,形成所需的圖案。

2023-08-24 15:57:42 2270

2270 對于數字數據傳輸,傳輸速率表示每秒鐘傳輸的比特數或字節數。例如,一個傳輸速率為1 Mbps的網絡連接,表示每秒鐘可以傳輸100萬個比特(或125,000個字節)的數據。傳輸速率越高,數據傳輸越快。

2023-08-24 15:21:34 5284

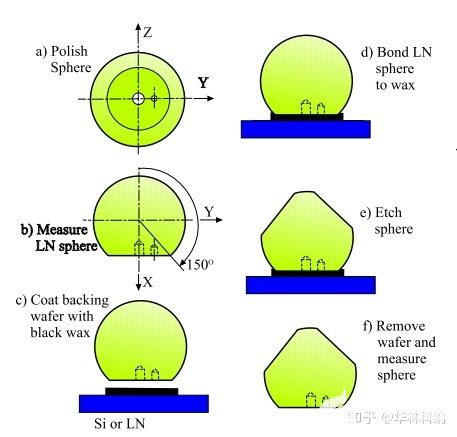

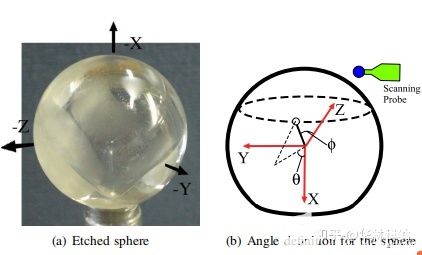

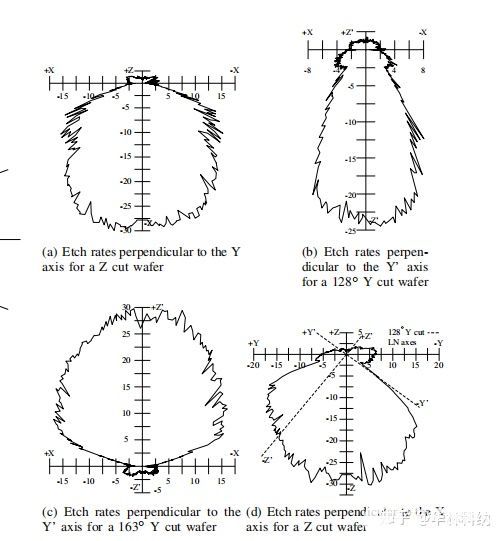

5284 各向異性刻蝕是一種減材微加工技術,旨在優先去除特定方向的材料以獲得復雜且通常平坦的形狀。濕法技術利用結構的晶體特性在由晶體取向控制的方向上進行蝕刻。 然而,概述了一些定性方面用于解釋各向異性的性質

2023-08-22 16:32:01 407

407 恒溫恒濕試驗箱變溫速率的選擇

2023-08-20 09:14:31 621

621

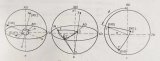

晶體內的幾何關系都是三維的,表示起來很不方便,是不同晶面晶向間的關系以及它們運動的軌跡很難用三維圖表達清楚。所以,往往把它們轉化為一種平面關系。最普遍使用的方法是極射赤面投影。

2023-08-18 11:28:43 2027

2027

PVP可以在刻蝕過程中形成一層保護性的膜,降低刻蝕劑對所需刻蝕材料的腐蝕作用。它可以填充材料表面的裂縫、孔洞和微小空隙,并防止刻蝕劑侵入。這樣可以減少不需要的蝕刻或損傷,提高刻蝕的選擇性。

2023-08-17 15:39:39 2855

2855 實際使用的材料多由多晶體組成,多晶體材料是由許多取向不同的小單晶體,即晶粒組成的。晶粒和晶粒之間的過渡區域就稱為晶界

2023-08-11 10:20:38 1077

1077

在半導體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來講講如何采用這個“餅干模具”印出我們想要的“餅干”。這一步驟的重點,在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

2023-08-10 15:06:10 506

506 晶體管是現代電子設備中至關重要的組件,而芯片則是晶體管的集成。晶體管是一種用于控制電流的電子器件,它是由半導體材料制成的。晶體管的發明和發展對現代科技的進步起到了重要的推動作用。

2023-08-04 09:45:30 1076

1076 TP-PM-1光合速率測定儀是植物學研究中常用的儀器,主要用于測量流經葉片前后CO2和H2O的濃度變化,分析葉片與環境發生的氣體交換,從而計算植物葉片光合速率、葉片蒸騰速率、細胞間CO2濃度、氣孔導度、水分利用率等參數指標。光合速率測定儀主要應用于農林業、園藝、微生物、昆蟲等專業行業及科學試驗中。

2023-08-03 14:37:05 377

377 類型。

雙極結型晶體管(BJT)

雙極結型晶體管是由基極、集電極和發射極 3 個區域組成的晶體管。雙極結型晶體管(與 FET 晶體管不同)是電流控制器件。進入晶體管基極區的小電流會導致從發射極流向集電極

2023-08-02 12:26:53

在微電子制造中,刻蝕技術是制作集成電路和其他微型電子器件的關鍵步驟之一。通過刻蝕技術,微電子行業能夠在硅晶片上創建復雜的微觀結構。本文旨在探討刻蝕設備的市場規模以及行業內的競爭格局。

2023-08-02 10:01:08 623

623

刻蝕(Etching)的目的是在材料表面上刻出所需的圖案和結構。刻蝕的原理是利用化學反應或物理過程,通過移除材料表面的原子或分子,使材料發生形貌變化。

2023-08-01 16:33:38 3908

3908 帶寬(Bandwidth)單位用bps(bit/s),表示每秒鐘傳輸的二進制位數。下載速率單位用Bps(Byte/s)表示,表示每秒鐘傳輸的字節數。1Byte(字節)=8bit(位),即下載速率

2023-07-31 17:38:15 518

518

電子發燒友網報道(文/周凱揚)在半導體制造的各路工序中,尤其是前道工序中,技術難度最大的主要三大流程當屬光刻、刻蝕和薄膜沉積了。這三大工藝的先進程度直接決定了晶圓廠所能實現的最高工藝節點,所用產品

2023-07-30 03:24:48 1556

1556

Accura BE作為國產首臺12英寸晶邊刻蝕設備,其技術性能已達到業界主流水平。” Accura BE通過軟件系統調度優化和特有傳輸平臺的結合,可以提升客戶的產能。

2023-07-19 16:50:01 1140

1140 據介紹,在器件制造過程中,由于薄膜沉積、光刻、刻蝕和化學機械拋光等工藝步驟的大幅增長,在晶圓的邊緣造成了不可避免的副產物及殘留物堆積,這些晶邊沉積的副產物及殘留物驟增導致的缺陷風險成為產品良率的嚴重威脅。

2023-07-19 15:02:26 607

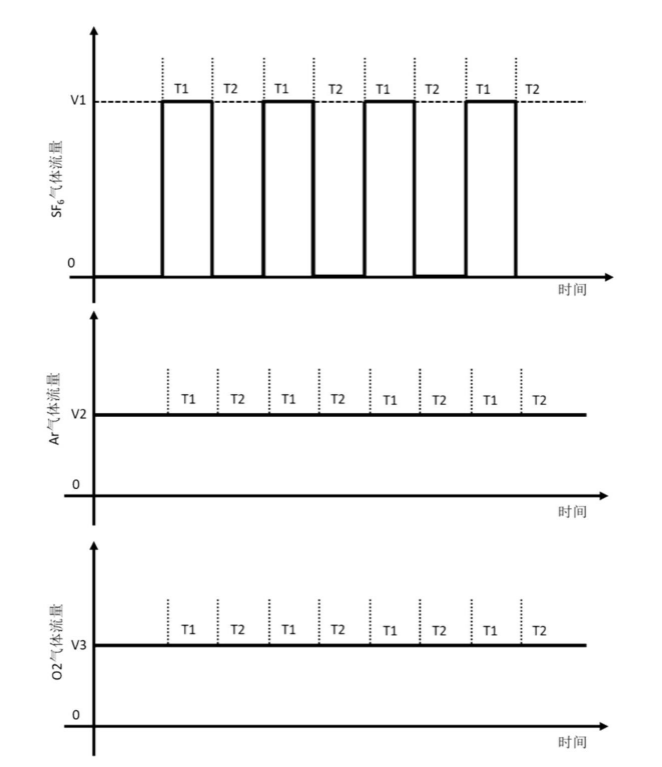

607 第一種是間歇式刻蝕方法(BOSCH),即多次交替循環刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 3213

3213

在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設計好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 843

843

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。其中,刻蝕工藝是光刻(Photo)工藝的下一步,用于去除光刻膠(Photo Resist

2023-06-26 09:20:10 816

816

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-06-15 17:51:57 1177

1177

我們在使用工業路由器的時候,往往最關注的是它到底快不快。那么工業路由器的速度到底如何?它的功率一般多大?5G下的工業路由器速率與舊版路由器區別在哪,本文將為您一一解答。▍工業路由器速率多少合適適合

2023-06-14 15:44:23 437

437

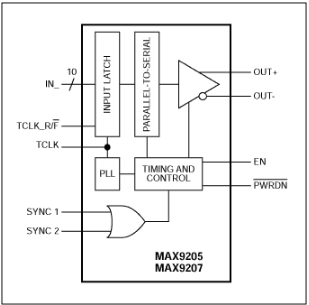

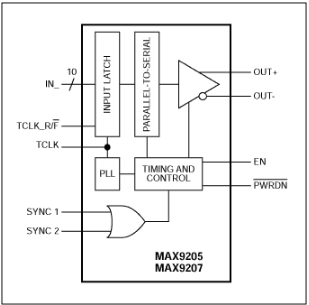

MAX9205/9207串行器和MAX9206/9208解串器設計用于通過點對點互連傳輸高速數據。MAX400-MAX600的串行“有效載荷”數據速率為9207Mbps至9208Mbps

2023-06-10 14:43:49 1762

1762

光刻工藝后,在硅片或晶圓上形成了光刻膠的圖形,下一步就是刻蝕。

2023-06-08 10:52:35 3318

3318

硅的堿性刻蝕液:氫氧化鉀、氫氧化氨或四甲基羥胺(TMAH)溶液,晶片加工中,會用到強堿作表面腐蝕或減薄,器件生產中,則傾向于弱堿,如SC1清洗晶片或多晶硅表面顆粒,一部分機理是SC1中的NH4OH

2023-06-05 15:10:01 1597

1597 但是,HCl為基體的刻蝕溶液,會嚴重地侵蝕Ni(Pt)Si或Ni(Pt)SiGe,使金屬硅化物阻值升高。這就要求有一種刻蝕劑是無氯基體,而且對Ni(Pt)Si或Ni(Pt)SiGe無傷害、對金屬選擇性又高。這就是目前常用的高溫硫酸和雙氧水混合液

2023-05-29 10:48:27 1461

1461

一定速率的pn序列直接擴頻與擴頻信號帶寬的關系是什么?

以及如果知道信息速率,怎么樣求它的系統擴頻增益?

那具體的換算怎么進行呢?

2023-05-16 17:34:28

看到一個公式,數據傳輸率:13.56MHZ/128 = 106Kbit/s;其中13.56MHZ是載波頻率,為什么要除以128,數據傳輸速率和載波頻率有什么關系?

2023-05-10 17:13:18

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。

2023-04-28 11:24:27 1073

1073

關于S32K3:當人為短路晶體導向S32K3產品復原位進入sBAF,是不是看門狗還能起作用?

2023-04-24 07:55:16

壓力主要控制刻蝕均勻性和刻蝕輪廓,同時也能影響刻蝕速率和選擇性。改變壓力會改變電子和離子的平均自由程(MFP),進而影響等離子體和刻蝕速率的均勻性。

2023-04-17 10:36:43 1922

1922 在 OTN 協議中,出現了各種各樣的速率定義。隱含在這些速率定義的數值之下的,是 OTN 協議的潛在規律和及一些關鍵性的原理。

2023-04-13 09:37:36 2595

2595 的圓臺硅通孔,采用的是在頂部不斷橫向刻蝕的方式實現的,不利于封裝 密度的提高,且對于光刻設備的分辨率有一定的要求。針對現有技術中的問題,一種嚴格控制橫向 刻蝕尺寸 (僅占原始特征尺寸的 3%~12

2023-04-12 14:35:41 1569

1569 金屬刻蝕具有良好的輪廓控制、殘余物控制,防止金屬腐蝕很重要。金屬刻蝕時鋁中如果 有少量銅就會引起殘余物問題,因為Cu Cl2的揮發性極低且會停留在晶圓表面。

2023-04-10 09:40:54 2330

2330 DRAM柵工藝中,在多晶硅上使用鈣金屬硅化物以減少局部連線的電阻。這種金屬硅化物和多晶硅的堆疊薄膜刻蝕需要增加一道工藝刻蝕W或WSi2,一般先使用氟元素刻蝕鈞金屬硅化合物層,然后再使用氯元素刻蝕多晶硅。

2023-04-07 09:48:16 2198

2198 FinFET三維器件也可以用體硅襯底制作,這需要更好地控制單晶硅刻蝕工藝,如CD、深度和輪廓。

2023-03-30 09:39:18 2459

2459 我在設計 PCB 時犯了一個錯誤,我的一些晶體管在原理圖上將集電極和發射極調換了。“正常”方式是有 1:基極,2:發射極,3:集電極,但我需要一個晶體管,1:基極,2:集電極,3:發射極。引腳號與此圖像相關:你知道有這種封裝的晶體管嗎?我知道我可以將它倒置并旋轉,但我想知道我是否可以正確使用一個。

2023-03-28 06:37:56

電子發燒友App

電子發燒友App

評論