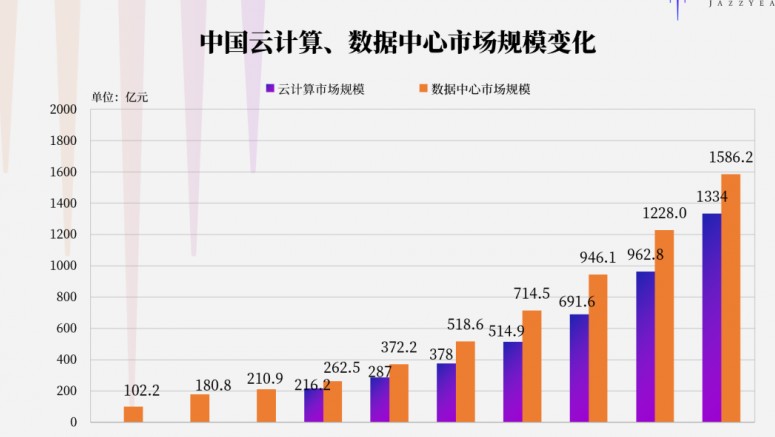

基于云的互聯網服務、人工智能和加密貨幣的出現引發了全球數據中心處理能力的強勁增長。再加上不斷上漲的電力和房地產價格,這一趨勢對高效緊湊的服務器電源產生了明顯的需求。

為了達到所需的更高功率密度,必須考慮以下三個主要因素:

提高效率以在給定體積內保持可接受的總功率損耗。這推動了向新拓撲和技術的過渡。一個很好的例子是從傳統的硅經典升壓 PFC 過渡到氮化鎵/碳化硅圖騰柱 PFC。

改進的封裝和散熱解決方案,可以將功率從器件結消散到散熱器和環境中。這在作為高密度轉換器主要推動力的小型表面貼裝器件 (SMD) 封裝中變得更具挑戰性。

優化的系統設計和開關頻率可在不違反效率要求或溫升限制的情況下實現最大密度。這導致開關頻率增加,推動了從傳統封裝和散熱解決方案向新封裝和散熱解決方案的轉變。

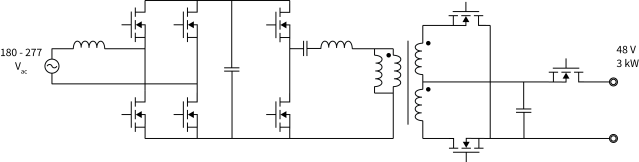

通常,最先進的高效電源由無橋 PFC 級(如圖騰柱級)和諧振 DC/DC 級(如 LLC 轉換器)組成(見圖 1)。服務器電源的示例規格是V in = 180–277 V,V out = 48 V,P out = 3 kW。

圖 1:包含圖騰柱 PFC 和 LLC DC/DC 轉換器的服務器電源

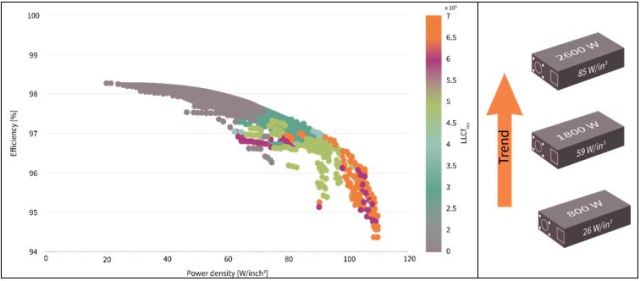

為了量化效率和功率密度之間可實現的性能折衷,應用了帕累托優化方法。該方法系統地考慮了不同轉換器系統設計中的所有可用自由度。通過采用詳細的系統和組件模型,它可以確定位于帕累托前沿的最佳設計。效率是針對額定輸出功率的 50% 計算的,包括 PFC 和 LLC 級損耗。

計算了整個服務器供電系統的帕累托前沿,優化結果如圖 2 所示。該圖表明,對于中等功率密度(~40 W/ in.3 ) ,效率可以達到接近 98.2% ,而設計超過 80 瓦/英寸。3的效率低于 97.5%。該圖中的另一個重要觀察結果是更高密度設計所需的 LLC 級的更高開關頻率。這些觀察結果證實了封裝以更高的頻率和更高的效率運行的必要性。

圖 2:顯示效率與密度的整個服務器電源的優化結果,以及最佳 LLC 級頻率

SMPS 拓撲中使用的 SMD 封裝

英飛凌提供更廣泛的底部冷卻 (BSC) 和頂部冷卻 (TSC) 封裝產品組合,可滿足服務器開關電源 (SMPS) 應用中更高功率和更高密度的趨勢。本節討論并比較了與組裝、熱性能和電氣寄生等主題相關的不同封裝。

BSC 和 TSC 包的組裝實現

底部冷卻

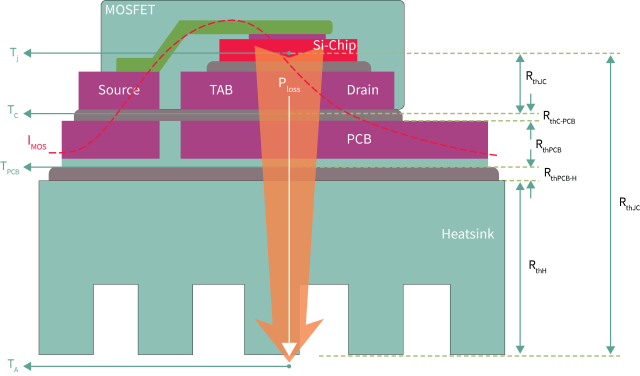

圖 3 和圖 4 顯示了 BSC 和 TSC 的主要冷卻概念。在這兩種情況下,SMD 封裝通常通過回流焊接工藝安裝在 PCB 上。對于 BSC,主要熱通量從封裝底部的器件散熱器(外露焊盤)通過 PCB 引導到安裝在 PCB 另一側的外部散熱器。因此,在使用基于 FR4 的 PCB 時,需要在封裝下方和穿過 PCB 的熱通孔進行熱傳遞。在 PCB 的背面,外部散熱器安裝在帶有散熱孔的區域。散熱器和 PCB 通過熱界面材料 (TIM) 進行電氣隔離。很多時候,厚度在 100–500 μm 范圍內的箔用作 TIM,在最好的情況下,它具有良好的熱導納 (λ)。理想情況下,這會導致低熱阻抗(Zthja ) 用于整個系統。

圖 3:使用底部冷卻的示例解決方案

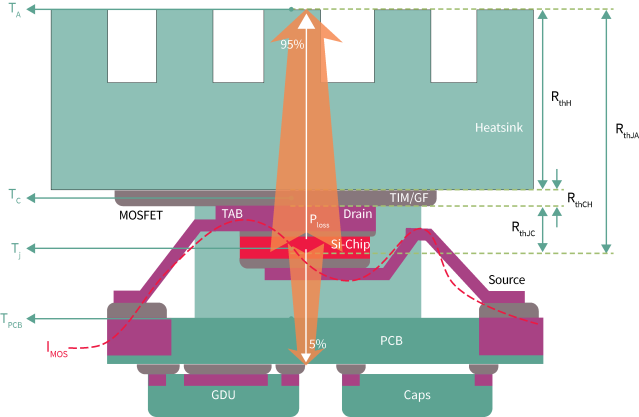

圖 4:使用頂部冷卻的示例解決方案

PCB 具有一定的厚度,受電路設計所需的銅層數量和熱通孔密度限制的影響。因此,與器件散熱器提供的熱傳遞面積相比,通過 PCB 進行熱傳遞的有效橫截面積減小了。這是第一個瓶頸。第二個瓶頸是 TIM,其 λ 比器件散熱器和外部散熱器低得多。

在某些情況下,用絕緣金屬基板 (IMS) 替換基于 FR4 的基板可以在不超過最大器件或 PCB 溫度的情況下獲得更高的熱通量。特別是對于單層 PCB 設計,既不需要熱通孔也不需要額外的 TIM。由于電路板的鋁芯用作散熱器,因此可以節省外部散熱器。然而,雖然 Z thja降低了,但板上溫度循環次數 (TCoB) 也減少了,特別是對于無鉛 SMD 封裝,如TO-leadless (TOLL)或 ThinPAK,由剛性基于 IMS 的 PCB 與更靈活的 PCB 相比引起基于 FR4 的 PCB。

頂部冷卻

在 TSC 封裝中,封裝頂部的器件散熱器通過 TIM 直接連接到外部散熱器(圖 4)。在這種情況下,沒有熱量通過 PCB 和熱過孔,因此從總熱阻抗中消除了它們的熱阻抗。這導致增強的導熱性和更高的封裝最大功耗。

此外,TSC 封裝的另一個優點是相對 PCB 側的空閑區域可用于放置其他器件,例如柵極驅動器和無源元件,以及封裝體正下方的信號路由空間。

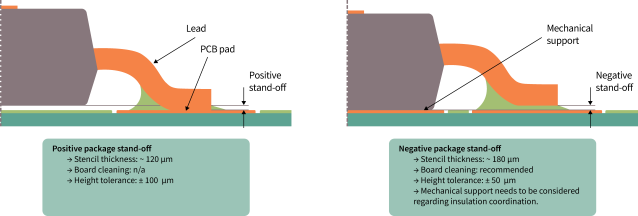

為獲得良好的熱界面,建議在 TSC 器件上用一定的力按壓散熱片。對于具有正封裝支座的引線 SMD 封裝(圖 5,左),該力和其他溫度循環引起的力被封裝引線吸收,從而在 QDPAK 的情況下產生 2,000 次循環的非常好的TCoB。6

如果出現負封裝間距(圖 5,右圖),PCB 設計需要考慮其他因素,以避免系統可靠性問題,這可能會導致系統設計和制造的額外工作量和復雜性。負封裝支架具有降低 Z thja的優勢,因為它降低了封裝高度公差,從而導致更薄的 TIM 厚度。然而,當考慮 PCB 翹曲等其他容差時,特別是對于較大的 PCB 尺寸和使用公共散熱器的多個功率器件,負封裝支架的熱優勢變得不那么重要了。

圖 5:標準正封裝支架(左)和負封裝支架(右)。封裝體下方的銅焊盤有利于作為明確高度的機械支撐和在負支架情況下的高板級可靠性。2

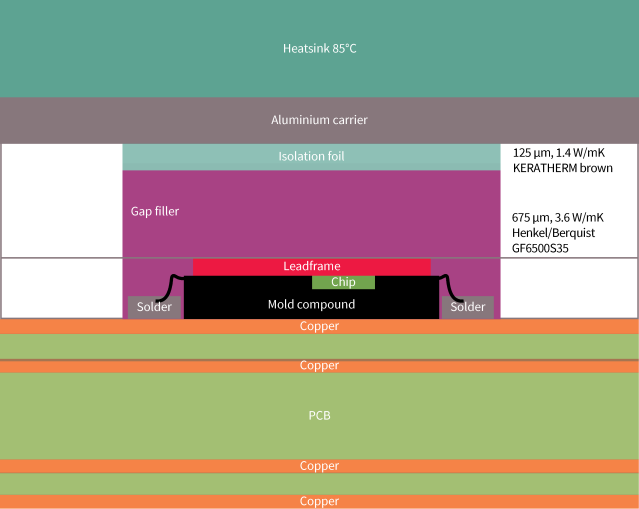

對于常見的散熱器方法,圖 6 示意性地顯示了器件和散熱器之間的 TIM 堆棧,在本示例中由絕緣箔和間隙填充物組成。間隙填充物用于補償設備、散熱器和 PCB 相關的制造公差。僅使用間隙填充物進行傳熱,必須確保設備和外部散熱器之間的可靠絕緣。此外,間隙填充材料必須滿足必要的擊穿等級,并且需要防止在 PCB 組裝過程中間隙填充內的封閉顆粒或氣孔。一般來說,PCB 組裝的清潔制造環境可以降低系統制造過程中因污染而導致系統故障的風險。

圖 6:外部散熱片和器件之間的電氣隔離箔和填縫劑

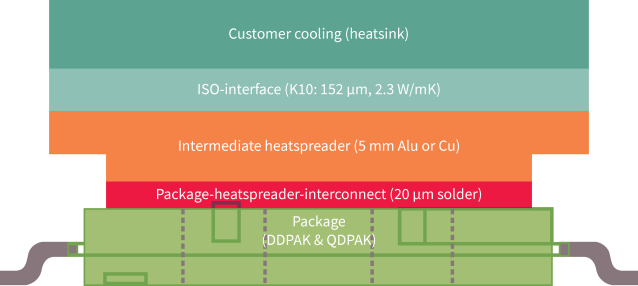

為了進一步提高 TSC 的 Z thja和動態功耗,中間散熱器的實施是一個不錯的選擇,如圖 7 所示。這個額外的散熱器的熱容量可以將額外的熱量存儲一段時間(幾秒鐘)并將其進一步轉移到公共散熱器和環境中。根據系統設計,為了改進系統 Z thja ,也可以移除公共散熱器和 TIM ,其中散熱器是主散熱器并由風扇氣流直接冷卻。

圖 7:單器件散熱器安裝6

熱性能

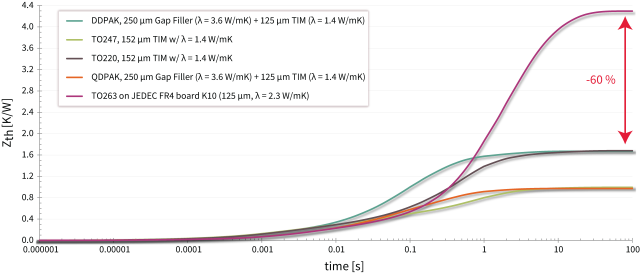

圖 8 顯示了考慮采用強制風冷的基于 FR4 的 PCB 設計的選定通孔器件 (THD)、BSC SMD 和 TSC SMD 封裝的Z thja時間相關圖。假設所有顯示封裝內的相同器件具有相同的功率損耗。將基于 FR4 的 PCB 上的 DDPAK(TSC 封裝)與 TO263(BSC 封裝)進行比較,DDPAK的 Z thja降低了 60% ,盡管這兩種封裝的有效冷卻面積非常相似。DDPAK 繞過了瓶頸“熱通孔”,如前一節所述。該圖還表明,頂部封裝可以實現與 THD 相當的 Z thja值。

圖 8:強制對流下多個封裝的典型瞬態熱阻抗結環境 (Z thja )

圖例表明,使用具有相當高 λ 的薄層隔離材料是實現良好 Z thja結果的關鍵。除此之外,使用具有更高 λ 的間隙填充物和隔離箔將導致所示的 TSC 封裝提供比 THD 更低的Z thja的情況。

高頻操作中的低電感寄生優勢

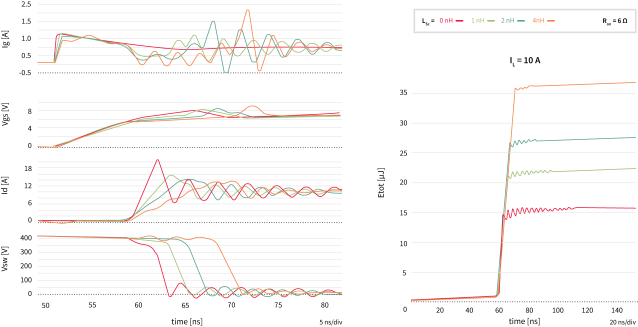

圖 9 展示了封裝源極電感 (L Sc ) 對開啟瞬態的影響。L Sc從 0 增加到 4 nH。漏極電流 (di/dt) 的上升會導致 L Sc上的感應電壓降,這會從柵極驅動電壓中減去,從而降低柵極電流。因此電壓瞬變需要更長的時間,并且損耗會增加。相同的機制但以相反的方式適用于關斷瞬態。

圖 9:封裝源電感對開啟的影響示例:波形細節(左)和損耗(右)

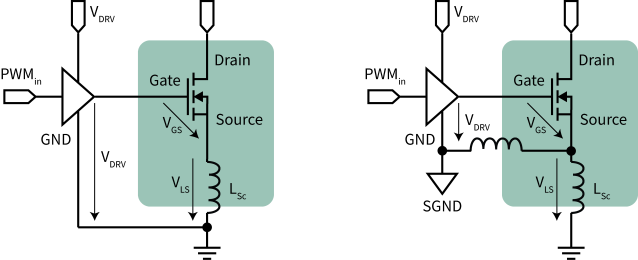

上面討論的 L Sc的負面影響可以通過使用單獨的源極檢測引腳(Kelvin 源)來控制柵極(圖 10,右)來消除,從而有效地降低開關損耗。通過使用源極檢測連接來驅動柵極,L Sc位于柵極驅動環路之外。因此,它的感應電壓峰值不會像標準配置(圖 10,左)那樣只有一個源極連接到MOSFET時會反饋到驅動電路中。

圖 10:標準三端子封裝(左)和采用開爾文源的四端子封裝(右)的柵極驅動環路比較

值得一提的是,Kelvin 源封裝解決了 L Sc對柵極驅動和開關速度的負面影響。然而,L Sc仍會增加總環路電感,這是導致快速開關應用(例如具有寬帶隙 (WBG) 開關的服務器 SMPS)中振鈴的關鍵參數。因此,即使使用開爾文源,封裝 L Sc也最好是最低的。參考應用筆記中提供了更多詳細信息。7

概括

本文討論了功率半導體封裝在滿足服務器電源(特別是硅和 WBG 開關)的功率和密度要求方面的重要性。

簡要介紹了服務器 SMPS 應用和趨勢,然后討論了 SMD 封裝,涉及裝配實施、熱性能和高頻操作中的低電感寄生優勢。

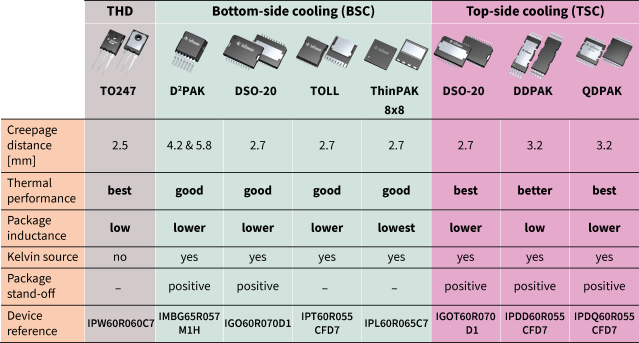

表 1 總結了英飛凌在服務器 SMPS 中使用的 SMD 封裝產品組合,并比較了它們的主要參數。

表 1:用于服務器應用的 SMD BSC 和 TSC 封裝概述。為了評估封裝電感,假設封裝內具有類似 RDS(on) 的器件。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論