本文分析了高性能肖特基勢壘二極管和 D 型 HEMT 在基于 p-GaN HEMT 的 200-V GaN-on-SOI 智能功率 IC 平臺上的成功協同集成。這些組件的添加使芯片設計具有擴展的功能和更高的性能,使單片集成 GaN 功率 IC 更進一步。這一成就為更小、更高效的DC/DC 轉換器和 PoL 轉換器?鋪平了道路。

GaN:電力電子領域的硅解決方案

幾十年來,基于硅的功率晶體管(如 MOSFET)構成了功率轉換系統的主干,可將交流電 (AC) 轉換為直流電 (DC),反之亦然,或者將直流電從低壓轉換為高壓,反之亦然。在尋求可以提高開關速度的替代品時,氮化鎵迅速成為領先的候選材料之一。GaN/AlGaN 材料體系表現出更高的電子遷移率和更高的擊穿臨界電場。結合高電子遷移率晶體管 (HEMT) 架構,與同類硅解決方案相比,它使器件和 IC 具有更高的擊穿強度、更快的開關速度、更低的電導損耗和更小的占位面積。?

?

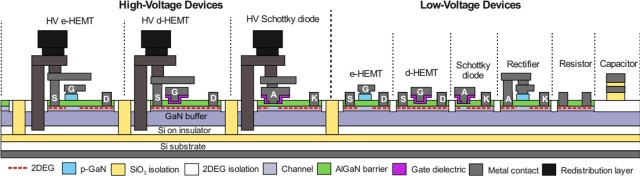

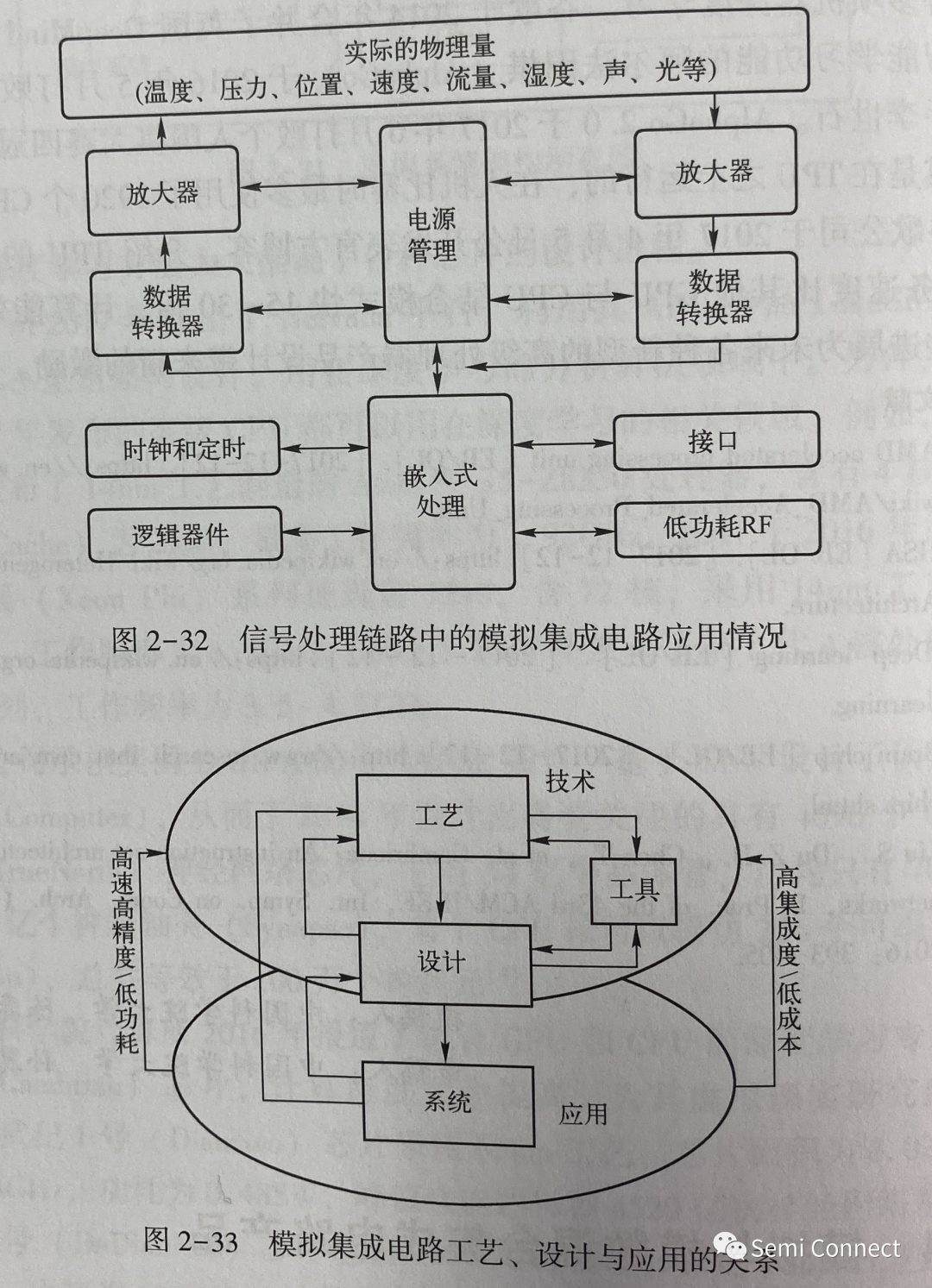

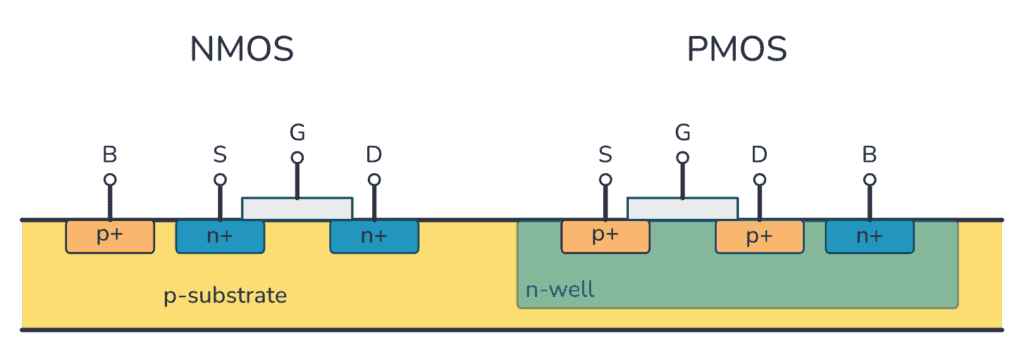

imec 的 200-V GaN-on-SOI 功率 IC 技術和組件的橫截面示意圖。該工藝采用 E-/D-mode HEMT、肖特基二極管、電阻器和電容器的單片共集成,并包括先進的工藝模塊(深溝隔離、襯底接觸、再分布層等)。?

今天,大多數 GaN 電源系統由多個芯片組成。基于 GaN 的器件在組裝到印刷電路板上之前作為分立元件組裝。這種方法的缺點是存在影響器件性能的寄生電感。?

Take a driver, for example. Discrete transistors with drivers on a separate chip suffer a lot from parasitic inductances between the output stages of the driver and the input of the transistor and in the switching node of half-bridges. GaN HEMTs have very high switching speed, which leads to ringing — an unwanted oscillation of the signal — when the parasitic inductance is not suppressed. The best way to reduce the parasitics and exploit the superior switching speed of GaN is to integrate both driver and HEMT on the same chip.?

At the same time, it reduces the dead-time control between two transistors in a half-bridge, wherein one transistor has to switch off just as the other one switches on. During the time in between, there is a short-circuit between the power source and the ground, or dead time. Integrating all components on-chip will address the ringing, reduce dead time, and ultimately improve the power efficiency of your converter.?

Co-integration of D-Mode HEMTs

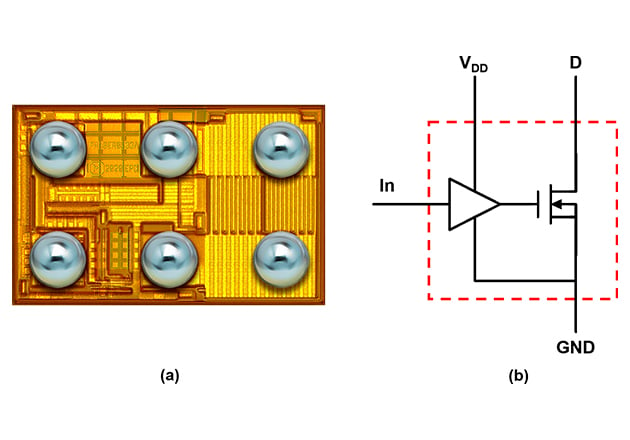

Imec has already made tremendous progress monolithically integrating building blocks on a silicon-on-insulator (SOI) substrate such as drivers, half-bridges, and control/protection circuits. Now, researchers have succeeded in adding two sought-after components to the portfolio: depletion-mode (D-mode) HEMTs and Schottky diodes.?

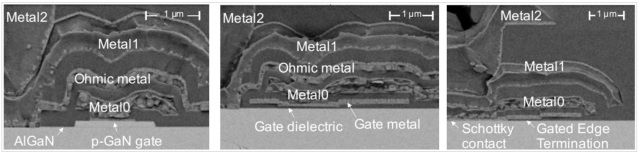

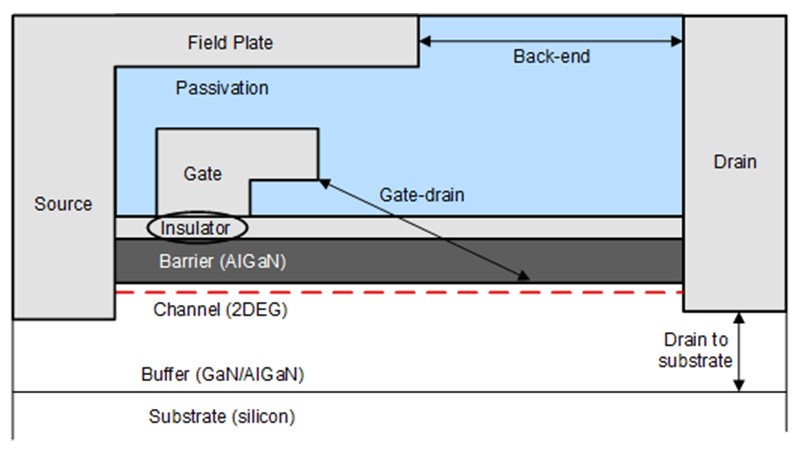

Process cross-sections of the high-voltage components fabricated on 200-mm GaN-on-SOI substrates:

(a) E-mode p-GaN HEMT; (b) D-mode MIS HEMT; (c) Schottky barrier diode. All devices include metal field plates based

on front-end and interconnect metal layers and separated by dielectric layers.

提高 GaN 功率 IC 的全部性能的主要障礙之一是找到合適的解決方案,以解決 GaN 中缺乏具有可接受性能的 p 溝道器件的問題。CMOS 技術使用互補且更對稱的 p 型和 n 型 FET 對,基于兩種 FET 的空穴和電子遷移率。然而,在 GaN 中,空穴的遷移率比電子的遷移率差大約 60 倍;在硅中,這只有 2 倍。這意味著以空穴為主要載流子的 p 溝道器件將比 n 溝道對應器件大 60 倍,而且效率極低。一種廣泛使用的替代方法是用電阻器代替 P-MOS。電阻晶體管邏輯 (RTL) 已用于 GaN IC,但在開關時間和功耗之間表現出權衡。?

Imec 通過在其 SOI 上的功能增強模式 (E-mode) HEMT 平臺上共同集成 D 模式 HEMTS,提高了 GaN IC 的性能。增強和耗盡模式是指在零源電壓下的開啟(D 模式)或關閉(E 模式)狀態,導致晶體管中有電流流動(或不流動)。Imec 預計從 RTL 到直接耦合 FET 邏輯的步驟將提高速度并降低電路的功耗。?

具有低泄漏電流的肖特基二極管

肖特基勢壘二極管的集成進一步提高了 GaN 功率 IC 的功率效率。與硅二極管相比,它們可以在相同的導通電阻下承受更高的電壓或在相同的擊穿電壓下承受更低的導通電阻。?

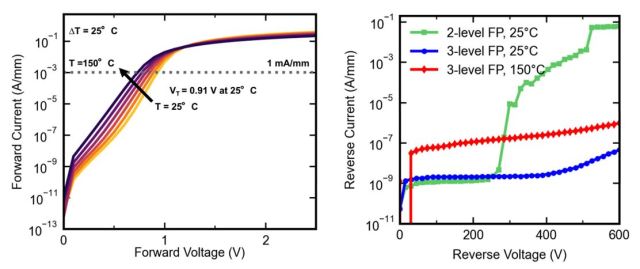

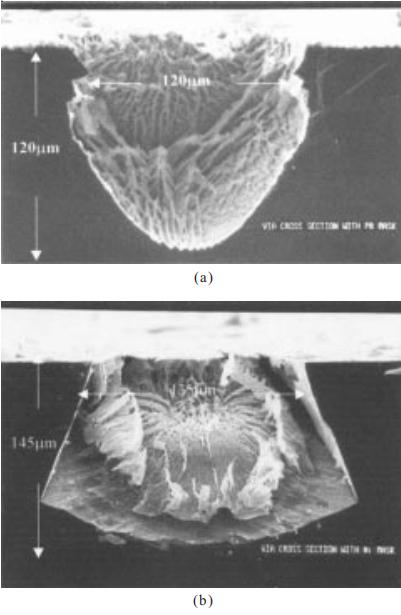

制造肖特基勢壘二極管的挑戰是獲得低導通電壓,同時獲得低泄漏水平。不幸的是,當您瞄準較低的導通電壓時,您最終會遇到一個小的屏障來阻止泄漏電流,而肖特基二極管因泄漏電流高而臭名昭著。與傳統 GaN 肖特基勢壘相比,Imec 專有的柵極邊緣端接肖特基勢壘二極管架構 (GET-SBD) 可實現約 0.8 V 的低開啟電壓,同時將漏電流降低幾個數量級二極管。

?

制造的 GET-SBD 的特性顯示(左)在 25?C 下以半對數刻度顯示 0.91 V 的低開啟電壓和

(右)兩個不同陽極場的低反向漏電流(25?C 時為 2 nA/mm)在

25?C 和 150?C下評估的板配置。

快速開關和高電壓

GaN 是大功率應用的首選材料,因為引起晶體管擊穿的臨界電壓(擊穿電壓)比硅高 10 倍。但由于其卓越的開關速度,GaN 在低功率應用中仍然比硅具有優勢。?

imec 創建的基于 GaN 的 IC 為更小、更高效的 DC/DC 轉換器和負載點 (PoL) 轉換器開辟了道路。例如,智能手機、平板電腦或筆記本電腦包含在不同電壓下工作的芯片,需要 AC/DC 轉換器為電池充電,設備內部需要 PoL 轉換器以產生不同的電壓。這些組件不僅包括開關,還包括變壓器、電容器和電感器。晶體管的開關速度越快,這些組件就會變得越小,最終在相同功率下產生更緊湊和低成本的系統。?

快速電池充電器構成了當今 GaN 的最大市場,其次是用于服務器、汽車行業和可再生能源的電源。預計使用 GaN 的電源在系統級更可靠。它們的外形尺寸和重量更小,從而減少了材料清單,從而降低了成本。?

正在研究的垂直設備

Imec 將專注于提高現有平臺的性能并進行進一步的可靠性測試。該公司目前提供用于原型設計的 200-V 和 650-V 平臺,不久之后將推出 100V。對于具有集成組件的 GaN IC,1,200-V 大功率平臺可能不會產生顯著改進。電壓越高,組件變得越慢。因此,可能沒有必要在芯片上集成驅動程序;模擬將證實這一點。?

Imec 還在尋找分立 1,200-V 器件的替代品,為電動汽車等最高電壓電源應用啟用 GaN 技術。具有橫向拓撲的晶體管是當今占主導地位的 GaN 器件架構。這些器件的三個端子(源極、柵極和漏極)位于同一平面的表面,因此電場是橫向的,跨越 GaN 緩沖層和部分后端(金屬化、氧化物)。在垂直器件中,源極和柵極位于表面,而漏極位于外延疊層的底部。在這種情況下,電場流過整個堆棧。決定器件擊穿電壓的是源漏分離,較大的分離可以保護通道不被擊穿。然而,橫向放置的源極和漏極之間的距離越大,器件越大。由于用于 1,200 V 設備的芯片會變得太大,因此通常建議橫向架構最高達到 650 V。相反,對于垂直器件,使用更高的電壓歸結為創建更厚的外延堆疊,因為源極和漏極位于堆疊的不同端。芯片的表面積不會增加。?

審核編輯:劉清

電子發燒友App

電子發燒友App

評論