先給大家簡(jiǎn)單快速地介紹一下 Vivado 集成設(shè)計(jì)環(huán)境,即 IDE。當(dāng)打開 Vivado 工程后,會(huì)有一個(gè)工程概要,向您介紹工程的設(shè)置、警告和錯(cuò)誤信息以及工程的一般狀態(tài)。

2012-04-25 09:00:43 6406

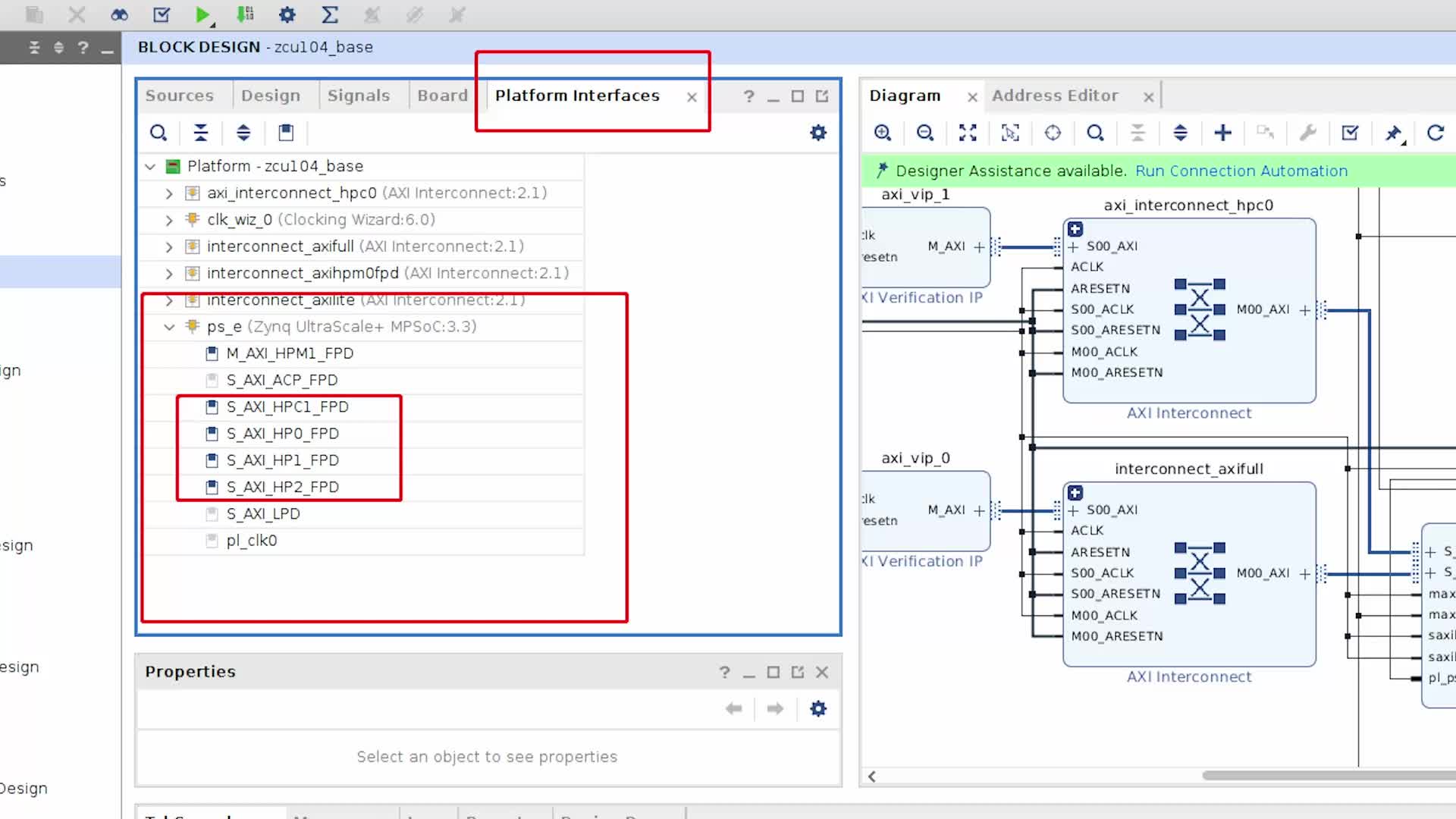

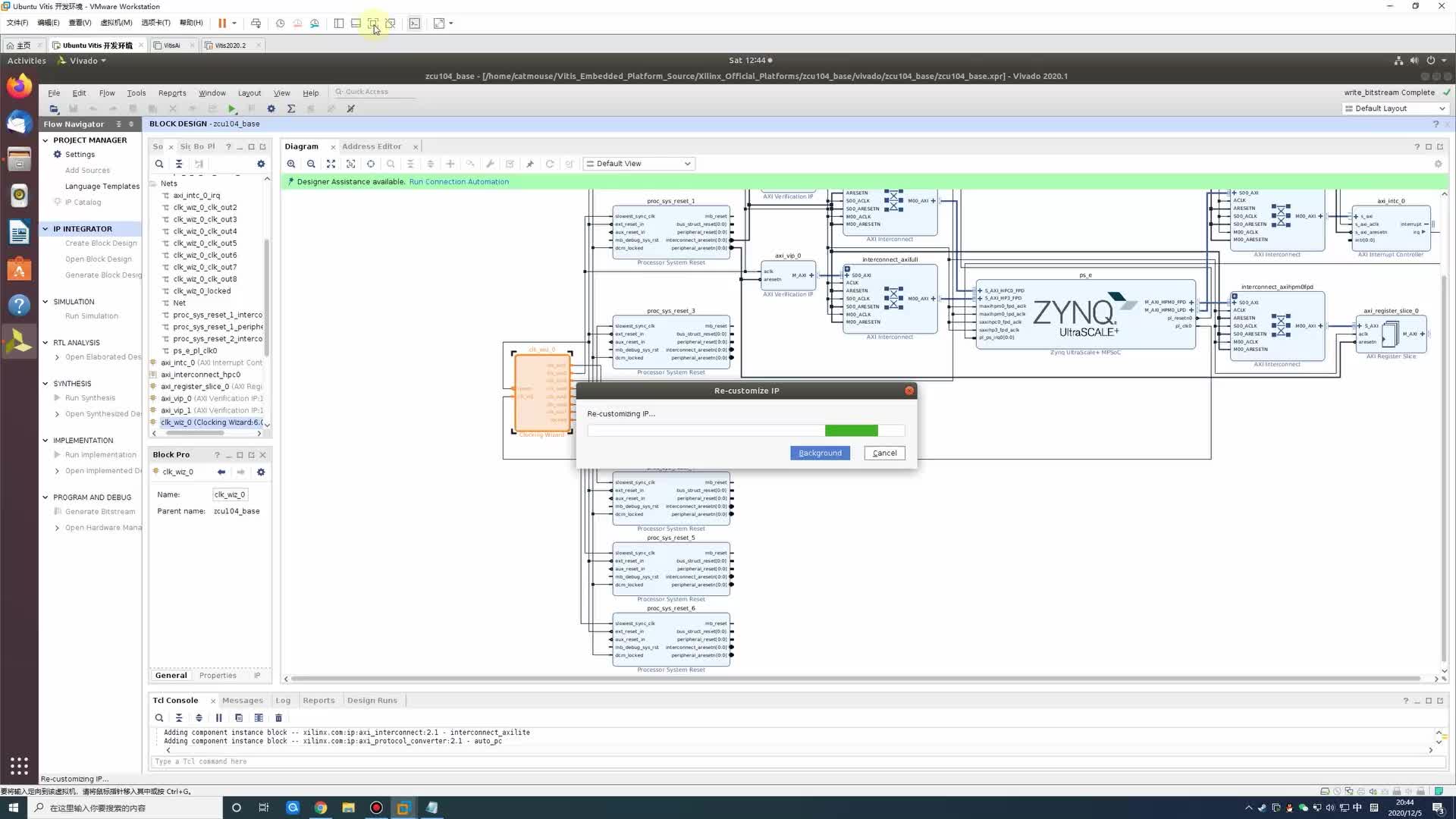

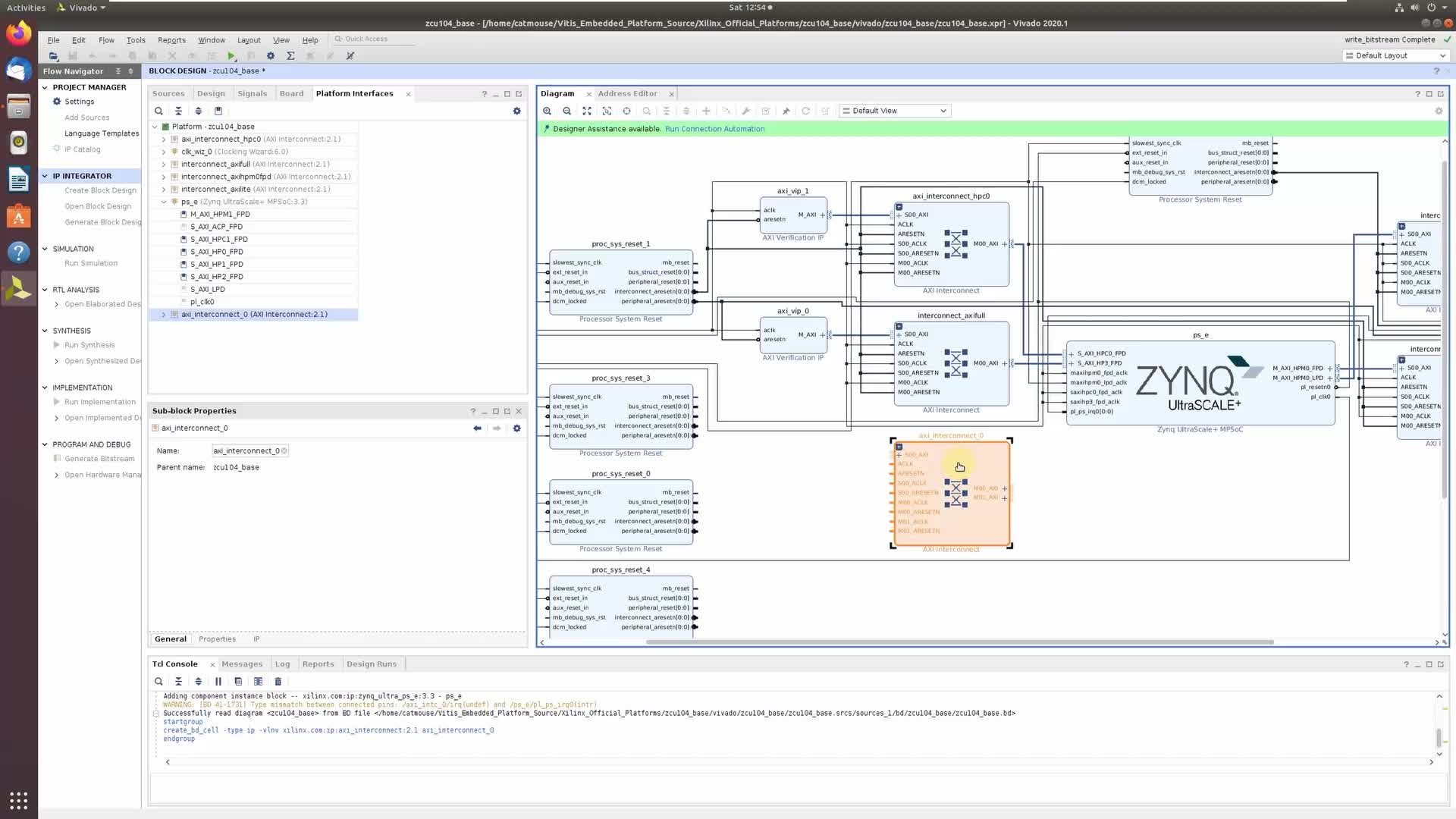

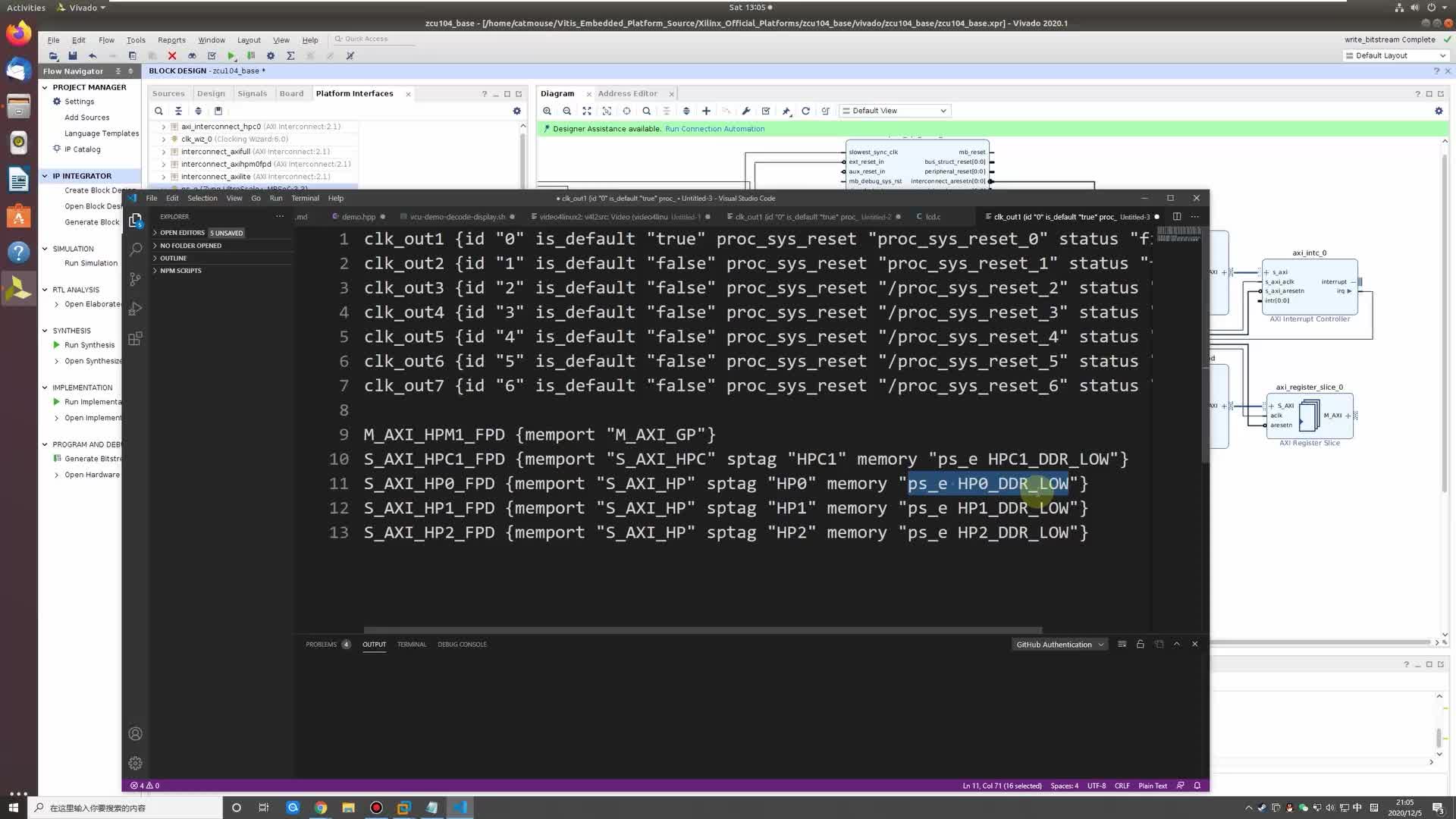

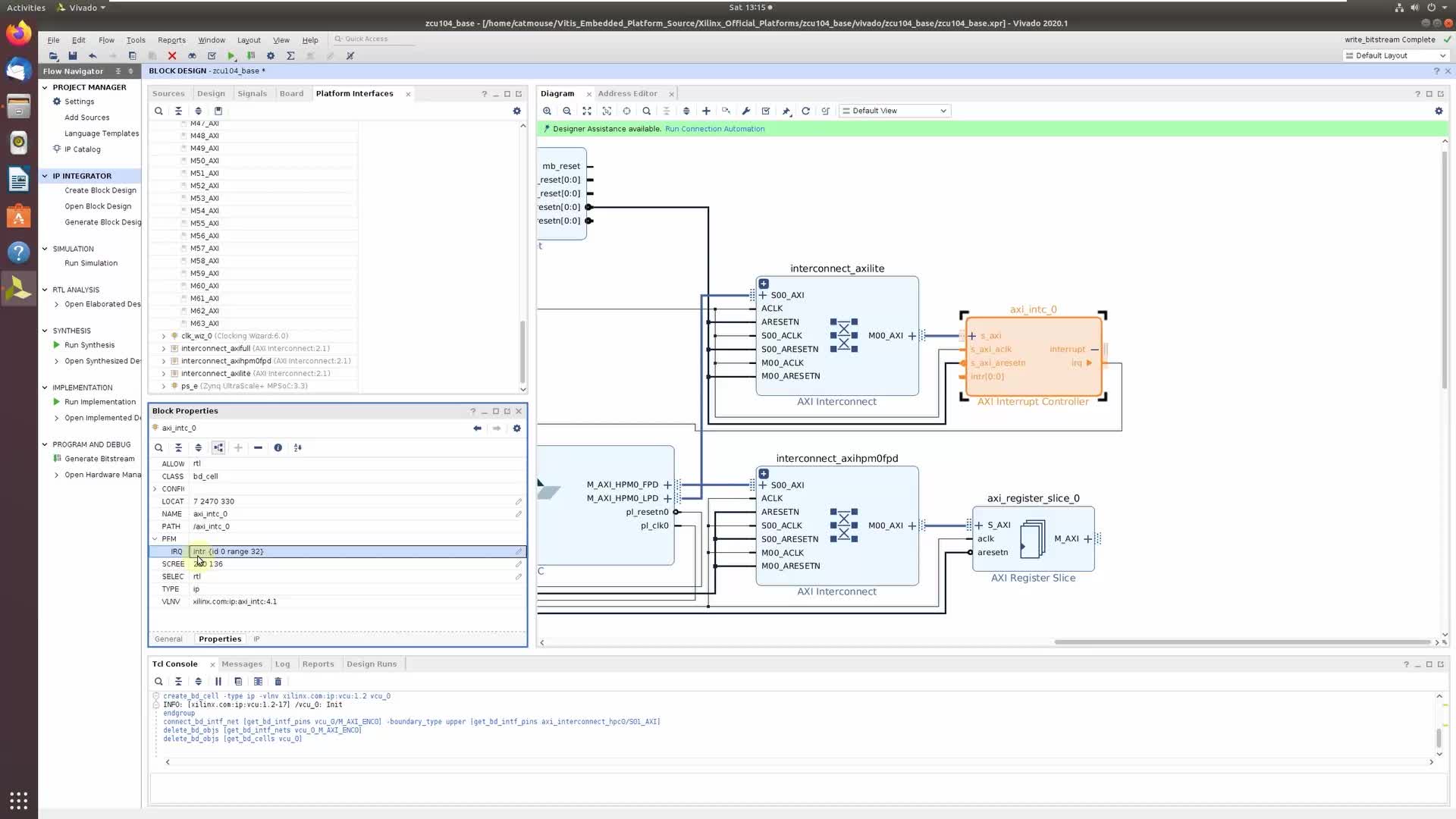

6406 裝加速平臺(tái) ;第 4 部分: 在 Vitis 中測(cè)試定制加速平臺(tái) )。 在本文中,我們將講解如何在 Vivado Design Suite 中完成平臺(tái)準(zhǔn)備工作,以便將其用作為 Vitis 中的加速平臺(tái)。 您既可以采用已確認(rèn)的成熟設(shè)計(jì)作為平臺(tái),這樣只需稍作增強(qiáng)便可靈活運(yùn)用于加速軟件功能,或者也可以采用僅含加速所

2020-09-26 11:29:43 3451

3451

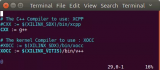

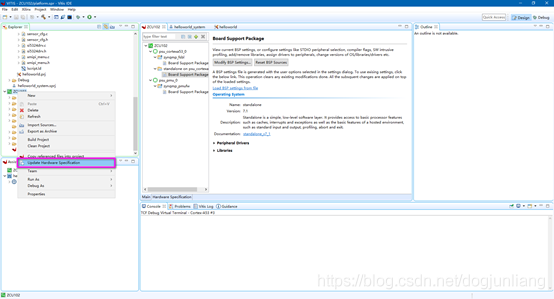

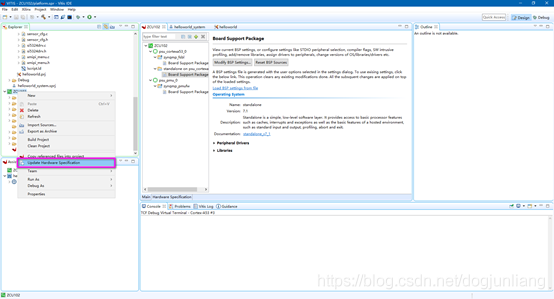

1). Windows 10 2). Vitis 2019.2 3). MicroZed 3. Vivado工程導(dǎo)出XSA文件 在 MicroZed 2019.1 BSP 下載MicroZed的Petalinux BSP。解壓后,使用Vivado 2019

2020-11-04 12:03:25 5065

5065

從 2019.2 版開始,賽靈思 SDK 開發(fā)環(huán)境已統(tǒng)一整合到全功能一體化的 Vitis 統(tǒng)一軟件平臺(tái) 中。 馬上開始將工程從賽靈思 SDK 移植到 Vitis 吧。 Vivado 工程升級(jí) 工程

2020-11-09 16:57:12 2279

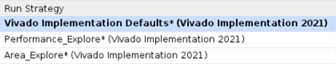

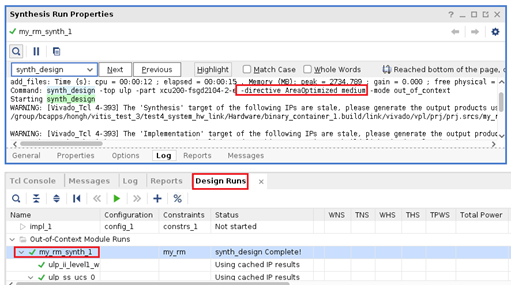

2279 在Vitis完成這個(gè)過(guò)程的底層,實(shí)際調(diào)用的是Vivado。Vitis會(huì)指定默認(rèn)的Vivado策略來(lái)執(zhí)行綜合和實(shí)現(xiàn)的步驟。當(dāng)默認(rèn)的Vivado策略無(wú)法達(dá)到預(yù)期的時(shí)序要求時(shí),我們需要在Vivado中分

2022-08-02 08:03:38 1016

1016

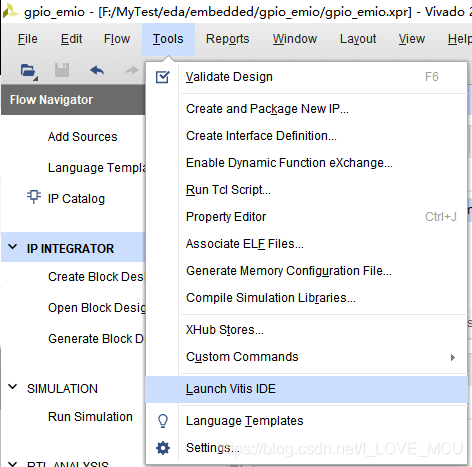

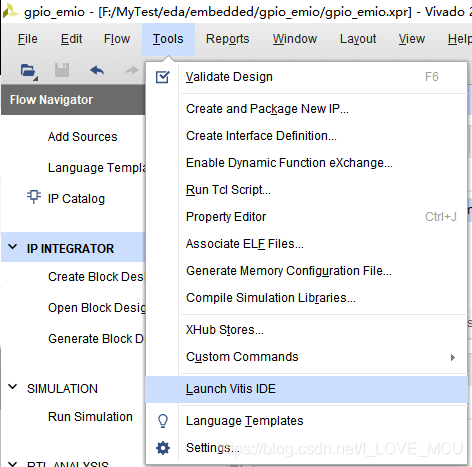

安裝完成了,所以是灰色狀態(tài)。創(chuàng)建platform工程vivado->tools->launch vitis ide選擇工作路徑先創(chuàng)建一個(gè) platform project,填寫工程名選擇

2020-12-23 17:10:37

在學(xué)習(xí)ZYNQ嵌入式開發(fā)的過(guò)程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫一這篇博客,方便后續(xù)查閱。

2021-02-04 07:09:50

在ISE中可以設(shè)置狀態(tài)機(jī)安全模式 safe impementation模式,但是在Vivado中有沒(méi)有類似的設(shè)置?我現(xiàn)在一段代碼中可以跑到else,但是 偶爾會(huì)跑不到ifs_state_4這個(gè)狀態(tài)機(jī)。。有大佬知道是為什么么?

2020-11-09 15:25:41

…。(不同Vivado版本可能Write Tcl菜單位置會(huì)有不同,但是都在File菜單中)彈出的WriteProject to Tcl文件夾,在Output File中設(shè)置當(dāng)前工程路徑,并輸入.tcl為后綴

2020-08-17 08:41:25

源文件,之后Clean,再之后Build(Ctrl + B)。 注:中間會(huì)彈出來(lái)一個(gè)錯(cuò)誤的提示,不用理會(huì),等待工程編譯完成,錯(cuò)誤提示就不存在了。 更改目錄后vitis工程需要重新加載平臺(tái) 在建

2021-01-15 16:46:02

vitis和vivado有什么區(qū)別和聯(lián)系呢

2023-10-16 07:55:35

電源線頂層過(guò)孔到底層,,,頂層的可以,,但到底層了就不可以了,,底層的哪里設(shè)置規(guī)則了嗎???求解。。

2012-11-29 11:36:50

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開源出來(lái)了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

大家好,我在利用ni vision assistant生成的模板匹配界面時(shí),想要將每一個(gè)匹配物體的位置信息導(dǎo)出到word或者Excel,但是他這個(gè)匹配個(gè)數(shù)不確定,怎么樣把匹配到的所有物體信息導(dǎo)出呀?利用哪些編程?謝謝大家了

2024-03-11 20:22:18

STM32F103配置信息的怎樣的?

2021-11-29 06:19:20

TESTSTAND自帶的報(bào)表中有 UUT Result這一項(xiàng)(見下圖),現(xiàn)在需要在自制的excel報(bào)表里用到 UUT Result,想知道它的底層參數(shù)是什么,怎么傳遞的

2015-11-08 20:06:20

【KV260視覺(jué)入門套件試用體驗(yàn)】+02.開發(fā)環(huán)境安裝Vitis/Vivado(zmj)

本篇主要介紹在CentOS-7.9安裝Vitis2022.2(包括Vivado2022.2)的安裝。

注意

2023-08-27 21:22:34

FFT運(yùn)算(Vivado)

四、硬件加速之—使用PL加速矩陣乘法運(yùn)算(Vitis HLS)

五、Vitis AI 構(gòu)建開發(fā)環(huán)境,并使用inspector檢查模型

六、Vitis AI 進(jìn)行模型校準(zhǔn)和來(lái)

2023-10-14 15:34:26

本文將介紹如何使用Vitis-AI加速YOLOX模型實(shí)現(xiàn)視頻中的目標(biāo)檢測(cè),并對(duì)相關(guān)源碼進(jìn)行解讀。由于演示的示例程序源碼是Vitis-AI開源項(xiàng)目提供的,本文演示之前會(huì)介紹所需要的準(zhǔn)備工作。演示之后

2023-10-06 23:32:47

都已編譯到預(yù)構(gòu)建的 Vitis AI 開發(fā)板鏡像中。您可直接運(yùn)行示例。如有新程序,請(qǐng)?jiān)谥鳈C(jī)側(cè)對(duì)其進(jìn)行編譯并將可執(zhí)行程序復(fù)制到目標(biāo)。

1. 使用 scp 命令將

2023-09-26 16:22:43

sample_platedetect.jpg

“Plate Detection”(車牌檢測(cè))庫(kù)使用 DenseBox 神經(jīng)網(wǎng)絡(luò)來(lái)檢測(cè)車牌。輸入是由 SSD 檢測(cè)到的車輛圖片,輸出是包含車牌位置信息的結(jié)構(gòu)

2023-09-26 16:28:10

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開源出來(lái)了。Vitis

2022-09-09 16:45:27

。3.Vitsi 開始調(diào)試在 Vivado 2019.2 中啟動(dòng) Vitis 的方式 與我現(xiàn)在用的 vivado 2017.4 有些不一樣,當(dāng)然這一點(diǎn)也不清楚是在 2019.2 版本中做的改變還是在2018版本

2020-03-06 22:59:12

在我們的設(shè)計(jì)中,Vivado實(shí)現(xiàn)結(jié)果因運(yùn)行而異。我們想要從“最佳”實(shí)現(xiàn)中鎖定兩個(gè)模塊的放置信息。然后將其保存以備將來(lái)運(yùn)行。我們知道這可能與pblock和分層設(shè)計(jì)有關(guān)。但是,分層設(shè)計(jì)文檔并不十分

2018-10-18 14:36:14

我要設(shè)計(jì)一個(gè)四層的PCB板子,底層用于焊接面(全部做成BGA焊盤),也就是底層用作元件的BGA焊盤,焊盤上不想有孔。我暫時(shí)考慮用盲孔,然后用銅填孔$ L& P0 k. m" T8 SI4 m" q, b' @9 E請(qǐng)教大家有什么更好的辦法把頂層或內(nèi)層走線引到底層,謝謝。

2014-10-28 16:27:36

請(qǐng)問(wèn)在vivado中修改了DTCM的大小后,如何在nuclei studio 中對(duì)應(yīng)地修改內(nèi)存的大小?

2023-08-16 06:54:10

在PCB中怎樣快捷地將器件從頂層移到底層,我想移很多元件,目前只會(huì)右鍵點(diǎn)元件,然后在選擇bottomlayer,這種方法只適合單個(gè)元件,我想移很多元件,有沒(méi)有更好的方法?

2014-11-19 10:31:02

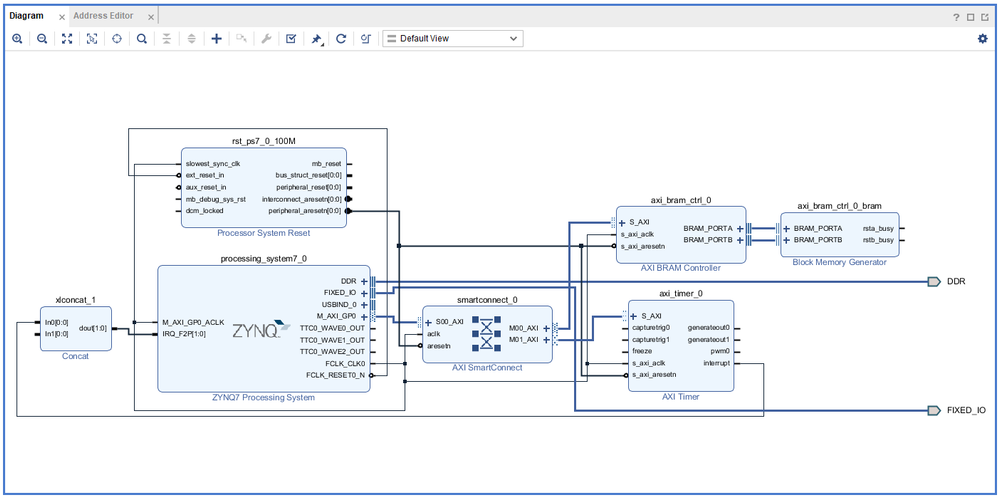

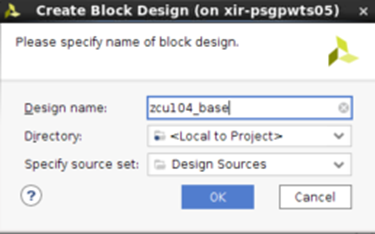

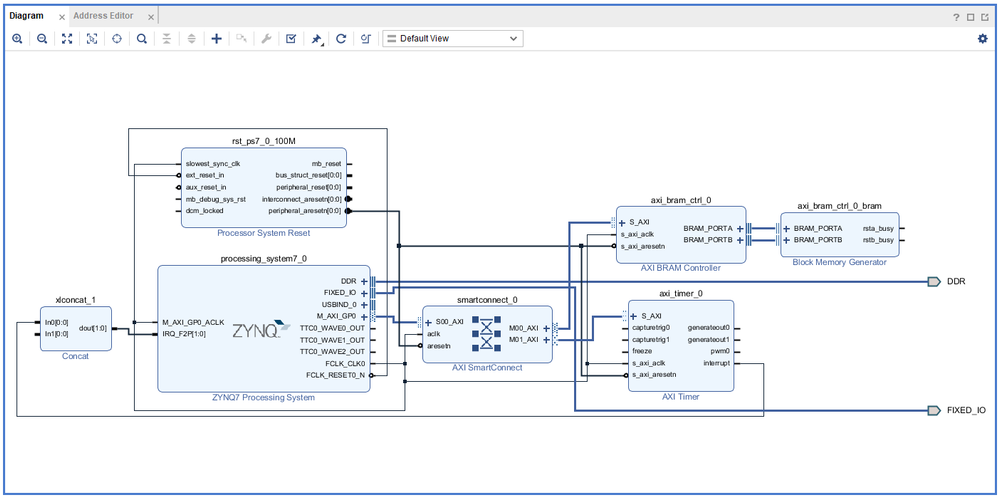

本文介紹如何在 vivado 開發(fā)教程,創(chuàng)建新工程 的基礎(chǔ)上, 使用IP集成器, 創(chuàng)建塊設(shè)計(jì)。

2021-02-23 07:02:27

如何在AudioService中把音量設(shè)置到最小呢?

2022-03-03 06:25:28

當(dāng)我試圖在Ubuntu的Synplify中調(diào)用xilinx for P& R時(shí),它說(shuō)XILINX變量尚未設(shè)置。我把它分配到vivado中的bin文件夾,但似乎是錯(cuò)誤的。看起來(lái)Synplify

2018-12-19 11:04:40

如何在VMware中安裝ubuntu 16.04如何安裝Vitis AI幾個(gè)常見的docker指令

2021-02-24 06:24:00

)IOStandard類型 - I / O端口clk是單端但具有LVDS的IOS標(biāo)準(zhǔn),只能支持差分信息:[Vivado 12-3199] DRC完成了1個(gè)錯(cuò)誤誰(shuí)能讓我了解如何在Virtex 7板上正確設(shè)置用戶時(shí)鐘

2020-03-30 09:51:26

如何在多個(gè)頁(yè)面之間傳遞數(shù)組收錄日期 : 2000-08-21 可以把數(shù)組轉(zhuǎn)化成字符串,作為一個(gè)參數(shù)來(lái)傳遞: - file1.php <

2009-01-11 09:25:19

大家好,我試圖在verilog文件中將命令傳遞給系統(tǒng)。 (在最初的開始循環(huán)中)我嘗試使用$ system命令行。它現(xiàn)在處于verilog標(biāo)準(zhǔn),但它似乎不適用于vivado。誰(shuí)知道怎么做?這是我想要

2020-05-22 15:23:42

你好,我正在使用vivado 2013.3我試圖在zedboard上進(jìn)行VITA傳遞,但是當(dāng)我生成一個(gè)比特流時(shí),我已經(jīng)在這條消息的末尾列出了問(wèn)題(我有一個(gè)視頻評(píng)估許可證)和圖像處理)錯(cuò)誤信息:信息

2020-05-20 12:50:42

,和/libcpu/arm/zynqmp-r5,/src源碼,/include頭文件,以及/components中的必要組件。我正確的設(shè)置了各頭文件的工程路徑,但在Vitis2019.2工程中Build時(shí)報(bào)錯(cuò)大量錯(cuò)誤,大多都是頭文件找不到,變量重復(fù)定義等。

2022-09-15 14:11:28

在cadence17.2中,如何將頂層絲印放置到底層絲印中,器件已經(jīng)放置到底層,但是絲印還是在頂層。

2020-09-28 11:51:57

在布局PCB的時(shí)候 底層需要放置元件 怎樣才能把元件放置到底層

2019-09-29 10:05:21

我想讀取鼠標(biāo)位置信息,求大神賜教

2016-06-28 23:30:47

本帖最后由 lsergao 于 2013-3-29 07:53 編輯

我把一個(gè)貼片元件雙擊選擇放到底層,怎么打印底層沒(méi)有焊盤啊,請(qǐng)高手指點(diǎn),我是一個(gè)新手

2013-03-28 16:39:24

Vivado硬件平臺(tái)更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

傳遞方式 它的信息傳送方式:用戶手機(jī)安裝APP后,掃描共享單車二維碼識(shí)別后,藍(lán)牙芯片通過(guò)共享手機(jī)的GPS定位,獲得共享單車的位置信息,并把信息傳輸給云端平臺(tái)。后臺(tái)管理系統(tǒng)向用戶手機(jī)中安裝的app發(fā)送

2020-08-14 08:00:35

/xlnx/board/crawl_message?board.id=OTHER&message.id=9394)。我想要做的是在Vivado GUI中更改默認(rèn)位置和文

2020-05-12 09:23:20

PROTEL頂層到底層鏡像

圖文解析

2010-09-12 16:34:37 0

0 本期視頻主要介紹了隔離的意義、絕緣的等級(jí)及介質(zhì)、以及如何在兩個(gè)隔離系統(tǒng)間傳遞信息等信息,并總結(jié)了Maxim在數(shù)字隔離方面的技術(shù)。

2018-10-08 03:27:00 4018

4018 了解如何在Vivado中執(zhí)行工程變更單(ECO)。

本視頻將向您介紹ECO的常見用例,我們推薦的完成ECO的流程,優(yōu)勢(shì)和局限性,并將演示功能設(shè)計(jì)的ECO。

2018-11-21 06:40:00 4645

4645

此視頻概述了Vivado Design Suite中的IP加密。

它涵蓋了IP加密工具流程,如何準(zhǔn)備加密IP以及如何在Vivado中運(yùn)行加密工具。

2018-11-20 06:34:00 5948

5948 了解Vivado 2015.1中引入的新儀表板改進(jìn),如何在Vivado Logic Analyzer中使用它們以及使用它們的好處。

2018-11-26 07:07:00 2777

2777 物理優(yōu)化是Vivado實(shí)現(xiàn)流程中更快時(shí)序收斂的重要組成部分。

了解如何在Vivado中應(yīng)用此功能以交換運(yùn)行時(shí)以獲得更好的設(shè)計(jì)性能。

2018-11-23 06:06:00 3726

3726 了解如何使用2014.1中引入的新激活許可為Vivado工具生成許可證。

另外,了解Vivado 2014.1中的許可更改如何影響您,以及如何在激活客戶端中使用新的Vivado License Manager

2018-11-22 07:10:00 2614

2614 Vitis 2019.2 使用 gcc 編譯 C 語(yǔ)言源代碼,使用 Vivado HLS 編譯與 SDAccel 流匹配的加速內(nèi)核。此外,Vitis 也使用與 SDAccel 相同的目標(biāo)平臺(tái)

2020-06-28 10:05:51 2011

2011

在本教程中,我們將來(lái)聊一聊有關(guān)如何在 Vitis HLS 中使用 AXI4-Lite 接口創(chuàng)建定制 IP 的基礎(chǔ)知識(shí)。

2020-09-13 10:04:19 5961

5961

在Vitis HLS下,一個(gè)Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下圖所示。前者最終導(dǎo)出來(lái)

2020-11-05 17:43:16 37060

37060 Linux嵌入式設(shè)計(jì)中最基本的任務(wù)之一是創(chuàng)建用戶應(yīng)用程序。 在本篇博文中,我們將探討如何在 Vitis 中使用 UIO 驅(qū)動(dòng)框架創(chuàng)建簡(jiǎn)單的 Linux 用戶應(yīng)用。 1 硬件設(shè)計(jì) 本次

2020-11-20 14:05:34 3840

3840 這是《創(chuàng)建 Vitis 加速平臺(tái)》系列的第 3 篇博文。在前文中,我們講解了如何創(chuàng)建硬件和軟件工程。在本文中,我們將講解如何在 Vitis 中將所有這些工程封裝在一起。 在 Vitis 中加速軟件

2020-12-26 10:20:54 2465

2465

Vivado硬件平臺(tái)更新后Vitis工程如何快捷更新

2021-01-22 05:51:23 1065

1065

本文介紹如何在 vivado 開發(fā)教程(一) 創(chuàng)建新工程 的基礎(chǔ)上, 使用IP集成器, 創(chuàng)建塊設(shè)計(jì)。

2022-02-08 10:47:39 2089

2089

本文介紹如何一步一步將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis平臺(tái)。

2022-07-25 17:45:48 3057

3057

在學(xué)習(xí)ZYNQ嵌入式開發(fā)的過(guò)程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫一這篇博客,方便后續(xù)查閱。

2022-07-25 18:03:30 3090

3090

Vivado硬件平臺(tái)更新后Vitis工程如何快捷更新

2021-01-28 09:28:18 12

12 本文介紹如何一步一步將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis平臺(tái)。

2021-01-31 08:12:02 8

8 在學(xué)習(xí)ZYNQ嵌入式開發(fā)的過(guò)程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫一這篇博客,方便后續(xù)查閱。

2021-02-21 06:48:51 17

17 以供在 Vivado Design Suite 中使用、如何將其連接到其它 IP 核與處理器以及如何在板上運(yùn)行工程。 本篇博文將分為 3 個(gè)部分: 1. 從 Vitis HLS 導(dǎo)出 IP。 2.

2021-04-26 17:32:26 3506

3506

Vivado 的XDC設(shè)置輸出延時(shí) Vivado 的XDC設(shè)置輸出延時(shí),用于輸出伴隨時(shí)鐘和數(shù)據(jù)的,數(shù)據(jù)是由系統(tǒng)時(shí)鐘125M驅(qū)動(dòng),伴隨時(shí)鐘是由125M經(jīng)過(guò)Pll相位移動(dòng)-90度。 設(shè)置輸出時(shí)鐘

2021-06-09 17:28:01 3888

3888

首先我們看一下如何在Vivado下設(shè)置BITSTREAM配置信息。這可以在綜合之后進(jìn)行。借助如下操作: 打開綜合后的設(shè)計(jì) 依次點(diǎn)擊Tools-》 Edit Device Properties 會(huì)彈

2021-06-15 14:26:18 5395

5395

首先我們看一下如何在Vivado下設(shè)置BITSTREAM配置信息。這可以在綜合之后進(jìn)行。借助如下操作: 打開綜合后的設(shè)計(jì) 依次點(diǎn)擊Tools-》 Edit Device Properties 在這

2021-06-18 10:24:51 1738

1738

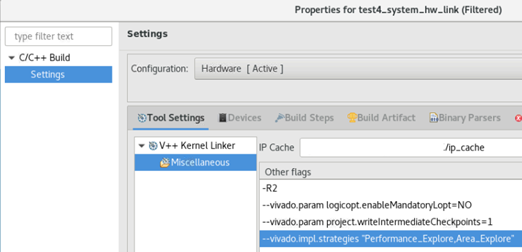

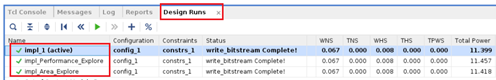

XCLBIN 在Vitis完成這個(gè)過(guò)程的底層,實(shí)際調(diào)用的是Vivado。Vitis會(huì)指定默認(rèn)的Vivado策略來(lái)執(zhí)行綜合和實(shí)現(xiàn)的步驟。當(dāng)默認(rèn)的Vivado策略無(wú)法達(dá)到預(yù)期的時(shí)序要求時(shí),我們需要

2021-07-28 10:12:47 1758

1758

本篇文章來(lái)自賽靈思高級(jí)工具產(chǎn)品應(yīng)用工程師 Hong Han. 本篇博文將繼續(xù)介紹在Vitis中把Settings信息傳遞到底層的Vivado. 對(duì)于Vivado實(shí)現(xiàn)階段策略的指定

2021-08-13 14:35:56 3900

3900 使用Vivado / Vitis工具提供預(yù)安裝的OpenCV版本。盡管Vitis_hls編譯Vision庫(kù)不需要OpenCV,但是用戶測(cè)試驗(yàn)證使用時(shí)OpenCV。

2022-02-16 16:21:38 2015

2015

Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數(shù)硬連線到器件邏輯互連結(jié)構(gòu)和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應(yīng)用加速開發(fā)流程中實(shí)現(xiàn)硬件

2022-05-25 09:43:36 1930

1930 在Kernel Estimate報(bào)告中,可以看到,Target Clock已經(jīng)按要求設(shè)置成200Mhz. 說(shuō)明 Vitis_HLS是按照200Mhz的要求來(lái)綜合Kernel的代碼的.

2022-07-01 09:52:53 36129

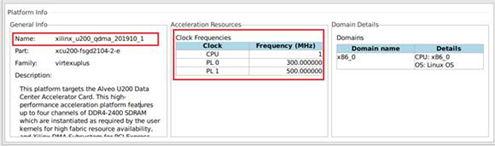

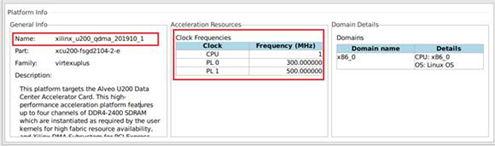

36129 在Vitis 統(tǒng)一軟件平臺(tái)中使用Alveo系列開發(fā)板設(shè)計(jì)加速Kernel時(shí),系統(tǒng)會(huì)自動(dòng)為Kernel的時(shí)鐘設(shè)置默認(rèn)頻率。以 xilinx_u200_qdma_201910_1 平臺(tái)為例,在Vitis中選擇平臺(tái)時(shí)可以看到默認(rèn)的時(shí)鐘頻率是300Mhz和500Mhz。

2022-08-02 10:30:45 514

514

以供在 Vivado Design Suite 中使用、如何將其連接到其它 IP 核與處理器以及如何在板上運(yùn)行工程。

2022-08-02 09:43:05 579

579

對(duì)于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開源出來(lái)了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

2022-09-02 09:06:23 2856

2856 AMD Vitis HLS 工具允許用戶通過(guò)將 C/C++ 函數(shù)綜合成 RTL,輕松創(chuàng)建復(fù)雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統(tǒng)一軟件平臺(tái)(用于所有異構(gòu)系統(tǒng)設(shè)計(jì)和應(yīng)用)高度集成。

2023-04-23 10:41:01 652

652

在本快速入門演示中,將探討如何在 Vitis 中使用 Git 集成以及如何使用團(tuán)隊(duì)操作來(lái)共享 Vitis 工程。

2023-05-12 15:01:00 566

566

本文主要介紹Vivado布線參數(shù)設(shè)置,基本設(shè)置方式和vivado綜合參數(shù)設(shè)置基本一致,將詳細(xì)說(shuō)明如何設(shè)置布線參數(shù)以優(yōu)化FPGA設(shè)計(jì)的性能,以及如何設(shè)置Vivado壓縮BIT文件。

2023-05-16 16:40:45 2956

2956

如果你正在使用Vivado開發(fā)套件進(jìn)行設(shè)計(jì),你會(huì)發(fā)現(xiàn)綜合設(shè)置中提供了許多綜合選項(xiàng)。這些選項(xiàng)對(duì)綜合結(jié)果有著潛在的影響,而且能夠提升設(shè)計(jì)效率。為了更好地利用這些資源,需要仔細(xì)研究每一個(gè)選項(xiàng)的功能。本文將要介紹一下Vivado的綜合參數(shù)設(shè)置。

2023-05-16 16:45:50 1856

1856

今天介紹一下,如何在Vivado中添加時(shí)序約束,Vivado添加約束的方法有3種:xdc文件、時(shí)序約束向?qū)В–onstraints Wizard)、時(shí)序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

Vitis? HLS 2023.1 支持新的 L1 庫(kù)向?qū)В疚膶⒅v解如何下載 L1 庫(kù)、查看所有可用功能以及如何在 Vitis HLS GUI 中使用庫(kù)函數(shù)。

2023-08-16 10:26:16 546

546

AMD Vitis 軟件平臺(tái)是一款開發(fā)環(huán)境,主要用于開發(fā)包括 FPGA 架構(gòu)、Arm 處理器子系統(tǒng)和 AI 引擎在內(nèi)的設(shè)計(jì)。Vitis 工具與 AMD Vivado ML 設(shè)計(jì)套件相結(jié)合,可為

2023-12-20 10:00:02 154

154

Vitis2023.2之前就安裝過(guò)了,vivado 2023.2相比于2023.1區(qū)別不明顯,但嵌入式平臺(tái)vitis2023.2的變化很大,有種vscode的既視感,更符合軟件開發(fā)人員的習(xí)慣。

2024-01-05 09:42:45 379

379

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論