隨著信息數據大爆炸時代的來臨,市場對存儲器的需求持續增長。在芯片成品制造環節中,市場對于傳統打線封裝的依賴仍居高不下。市場對于使用多芯片堆疊技術、來實現同尺寸器件中的高存儲密度的需求也日益增長。這類需求給半導體封裝工藝帶來的不僅僅是工藝能力上的挑戰,也對工藝的管控能力提出了更高的要求。

在這里,我們將向大家介紹長電科技的多芯片堆疊封裝技術的優勢、工藝和管控能力,內容將分為上下兩期呈現。

多芯片堆疊封裝技術優勢

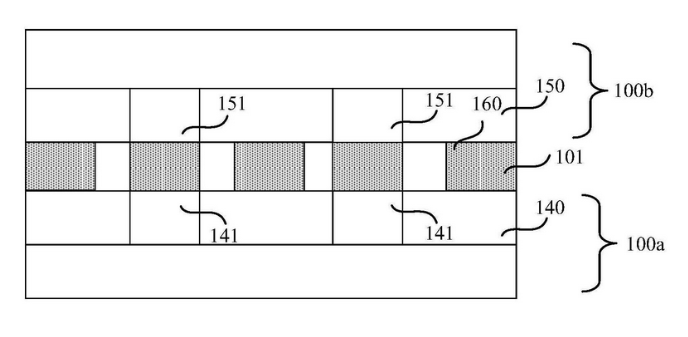

?

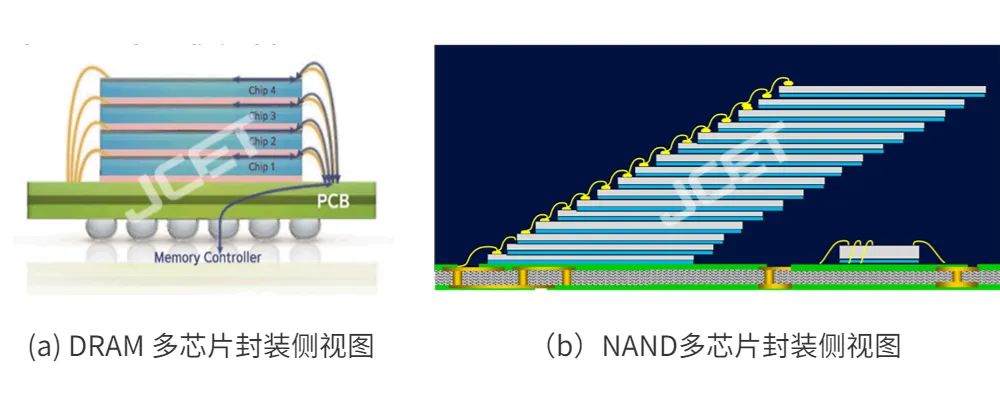

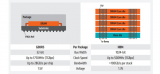

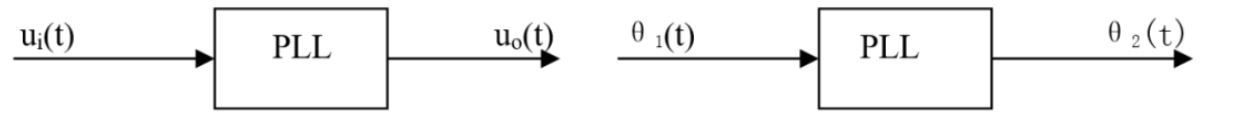

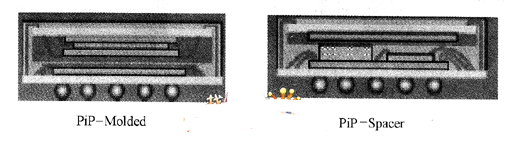

圖1 多芯片封裝側視圖

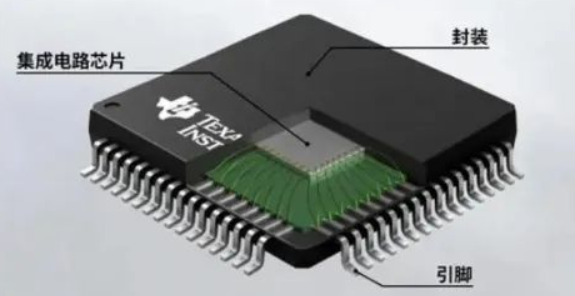

圖1是兩個不同類型的存儲器封裝的側視圖,從其封裝結構我們可以看出,兩個封裝都是由多個芯片堆疊而成,目的是為了減少多芯片封裝占用的空間,從而實現存儲器件尺寸的最小化。其中較關鍵的工藝是芯片減薄、切割,以及芯片貼合。

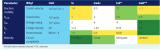

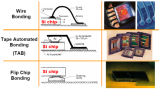

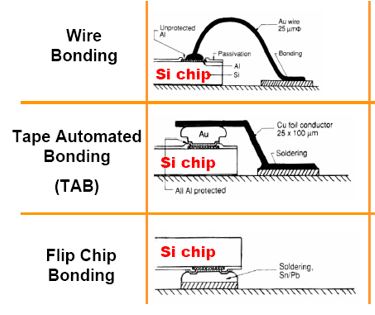

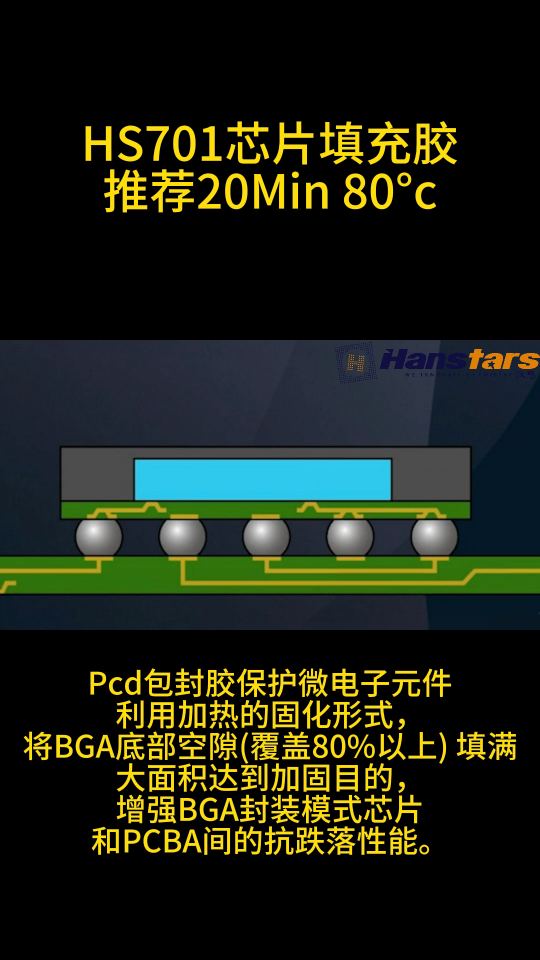

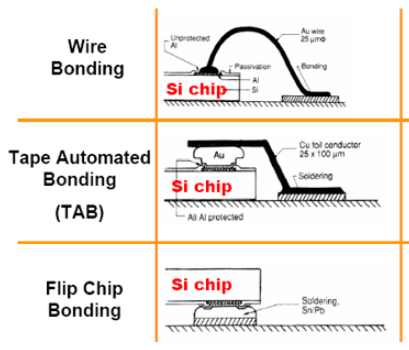

從市場需求來看,倒裝封裝(FC)和硅通孔(TSV),以及晶圓級(wafer level)的封裝形式可以有效地減小器件尺寸的同時,提高數據傳輸速度,降低信號干擾可能。但就目前的消費類市場需求來看,還是基于傳統打線的封裝形式仍占較大比重,其優勢在于成本的競爭力和技術的成熟度。

長電科技目前的工藝能力可以實現16層芯片的堆疊,單層芯片厚度僅為35um,封裝厚度為1mm左右。

多芯片堆疊封裝關鍵工藝?

之芯片減薄、切割

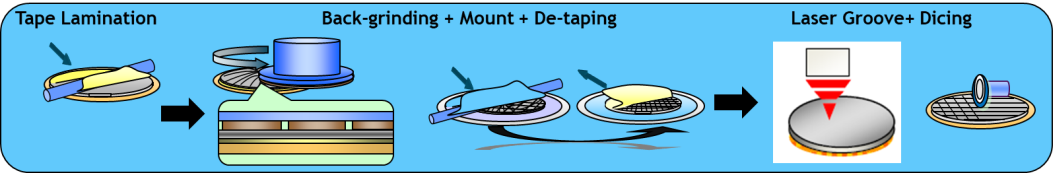

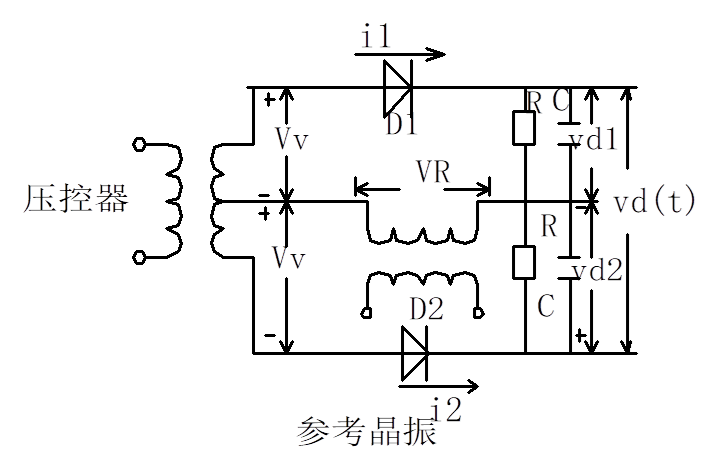

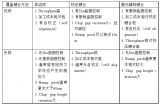

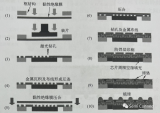

研磨后切割

(Dicing After Grinding,DAG)

主要針對較厚的芯片(厚度需求>60um),屬于較傳統的封裝工藝,成熟穩定。晶圓在貼上保護膜后進行減薄作業,再使用刀片切割將芯片分開。適用于大多數的封裝。

圖2 DAG(來源:DISCO)

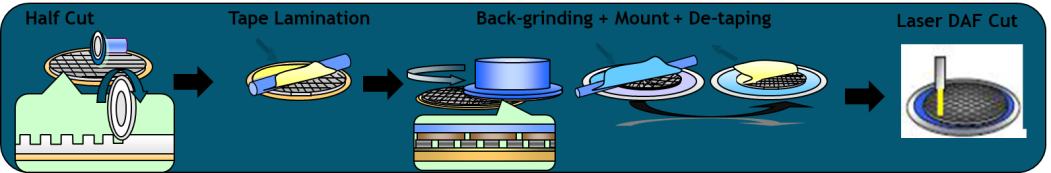

研磨前切割

?(Dicing Before Grinding,DBG)

主要針對38-85um芯片厚度,且芯片電路層厚度>7um,針對較薄芯片的需求和存儲芯片日益增長的電路層數(目前普遍的3D NAND層數在112層以上)。使用刀片先將芯片半切,再進行減薄,激光將芯片載膜 (Die attach film)切透。適用于大部分NAND 芯片,優勢在于可以解決超薄芯片的側邊崩邊控制以及后工序芯片隱裂(die crack)的問題,大大提高了多芯片封裝的可行性和可量產性。

圖3 DBG(來源:DISCO)

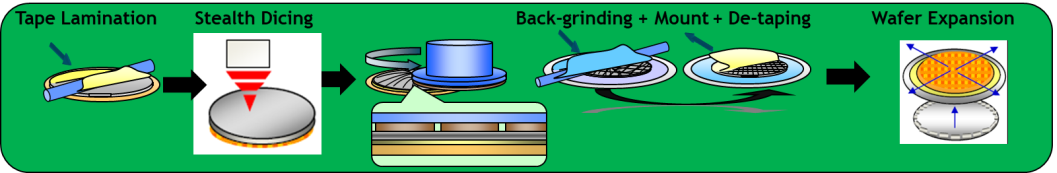

研磨前的隱形切割

(Stealth Dicing Before Grinding,SDBG)

主要針對35-85um芯片厚度,且芯片電路層厚度<7um,主要針對較薄芯片的需求且電路層較少,如DRAM。使用隱形激光先將芯片中間分開,再進行減薄,最后將wafer崩開。適用于大部分DRAM wafer以及電路層較少的芯片,與DBG相比,由于沒有刀片切割機械影響,側邊崩邊控制更佳。芯片厚度可以進一步降低。

圖4 SDBG(來源:DISCO)

?

審核編輯:劉清

?

電子發燒友App

電子發燒友App

評論